A New GaN-Based Device, P-Cascode GaN HEMT, and Its Synchronous Buck Converter Circuit Realization

Abstract

:1. Introduction

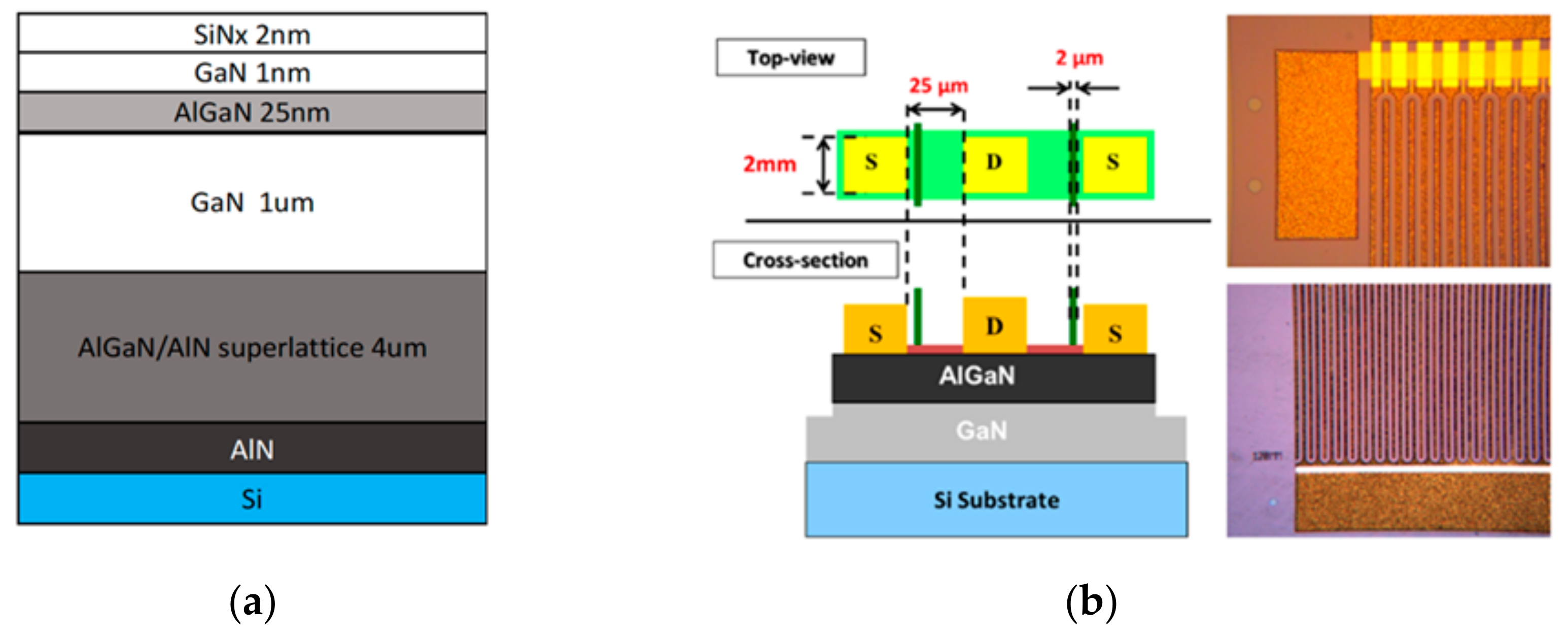

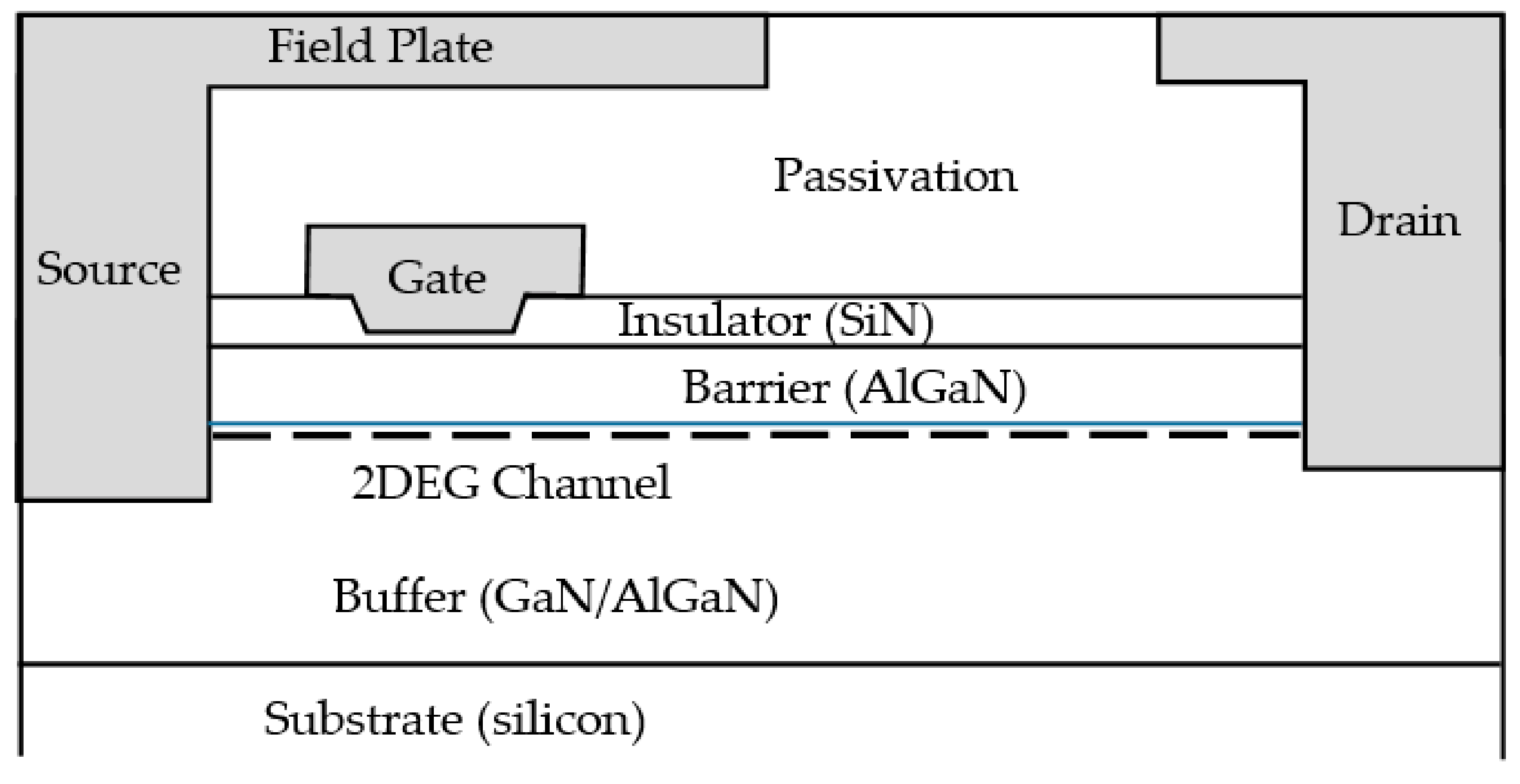

2. Materials and Methods

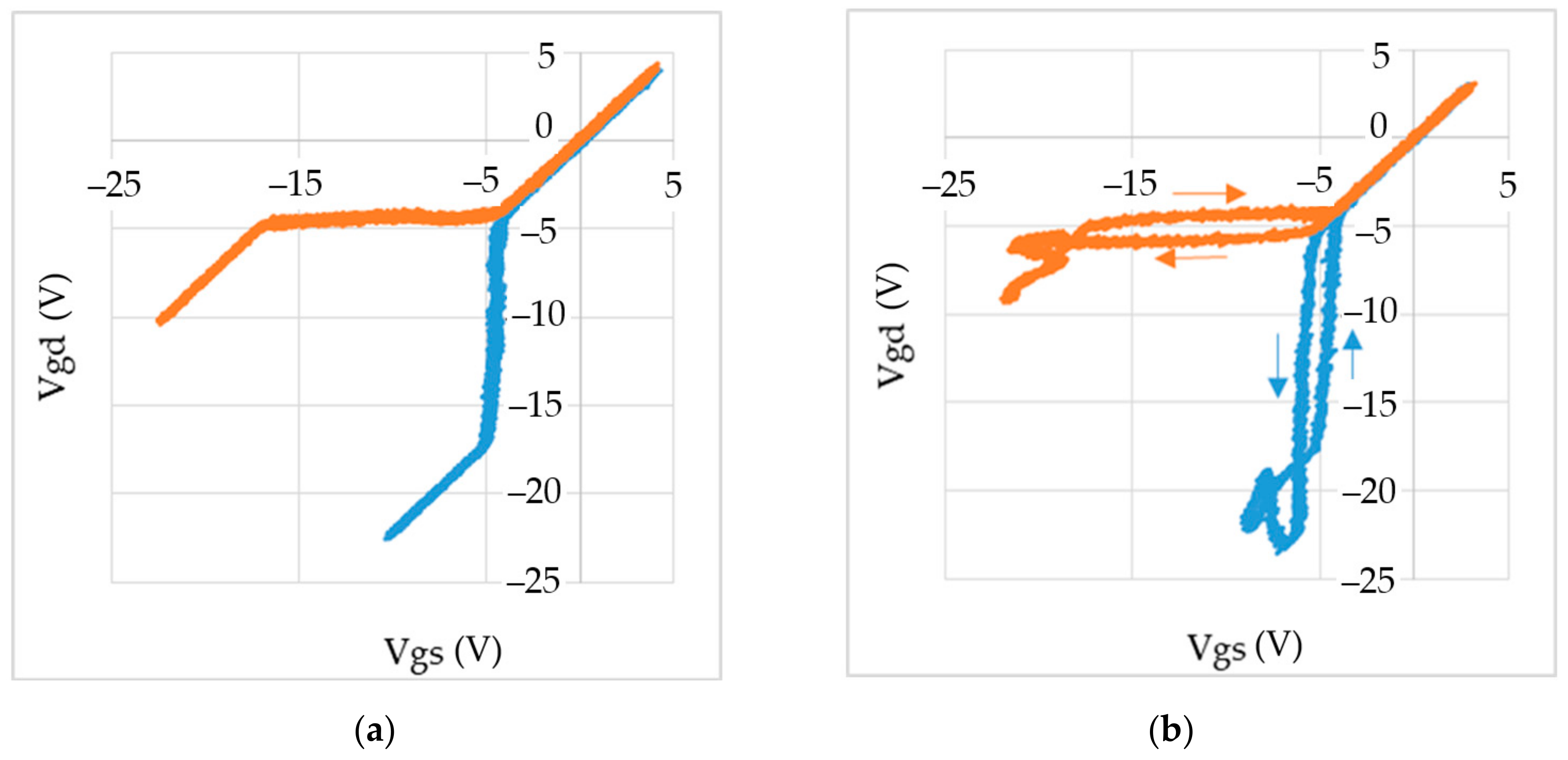

2.1. D-Mode GaN MIS-HEMT Characteristics

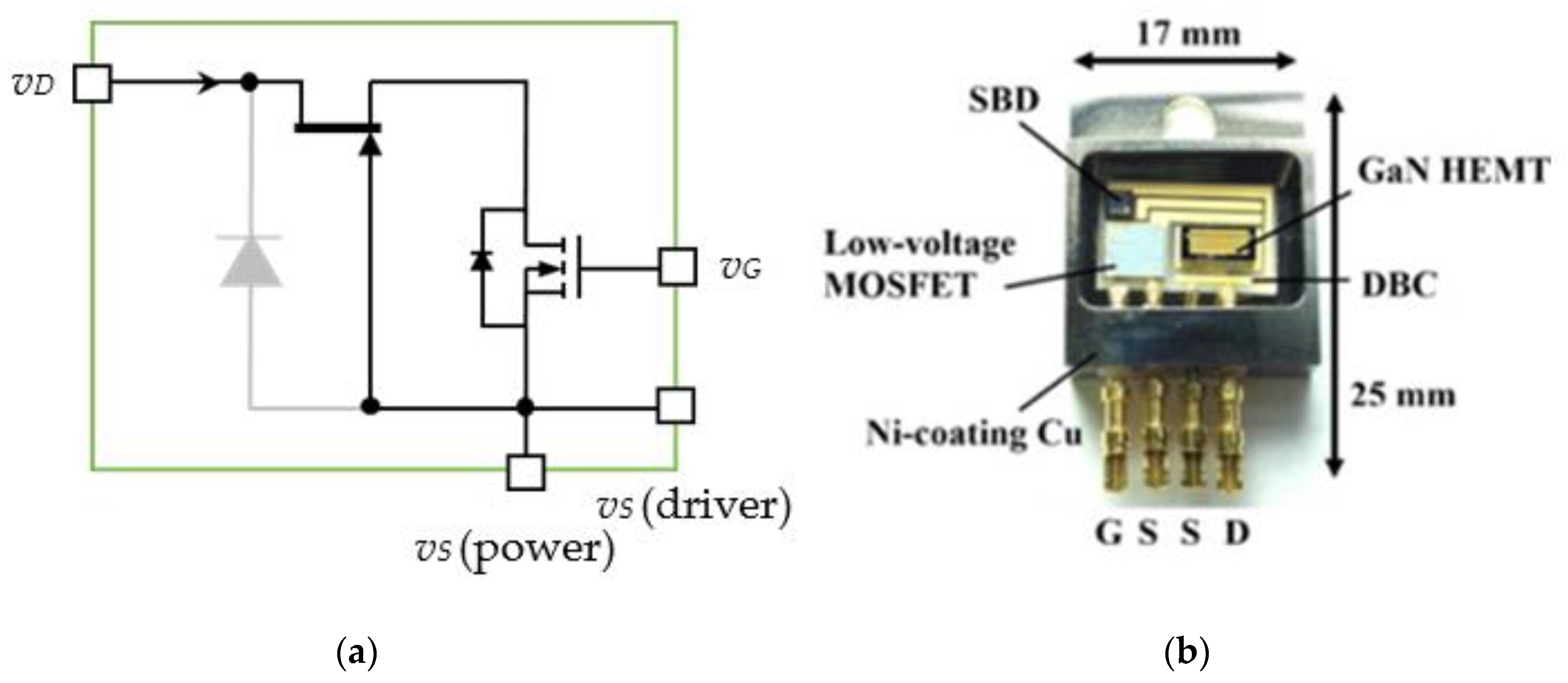

2.2. Cascode GaN HEMT Module as an E-Mode Switch

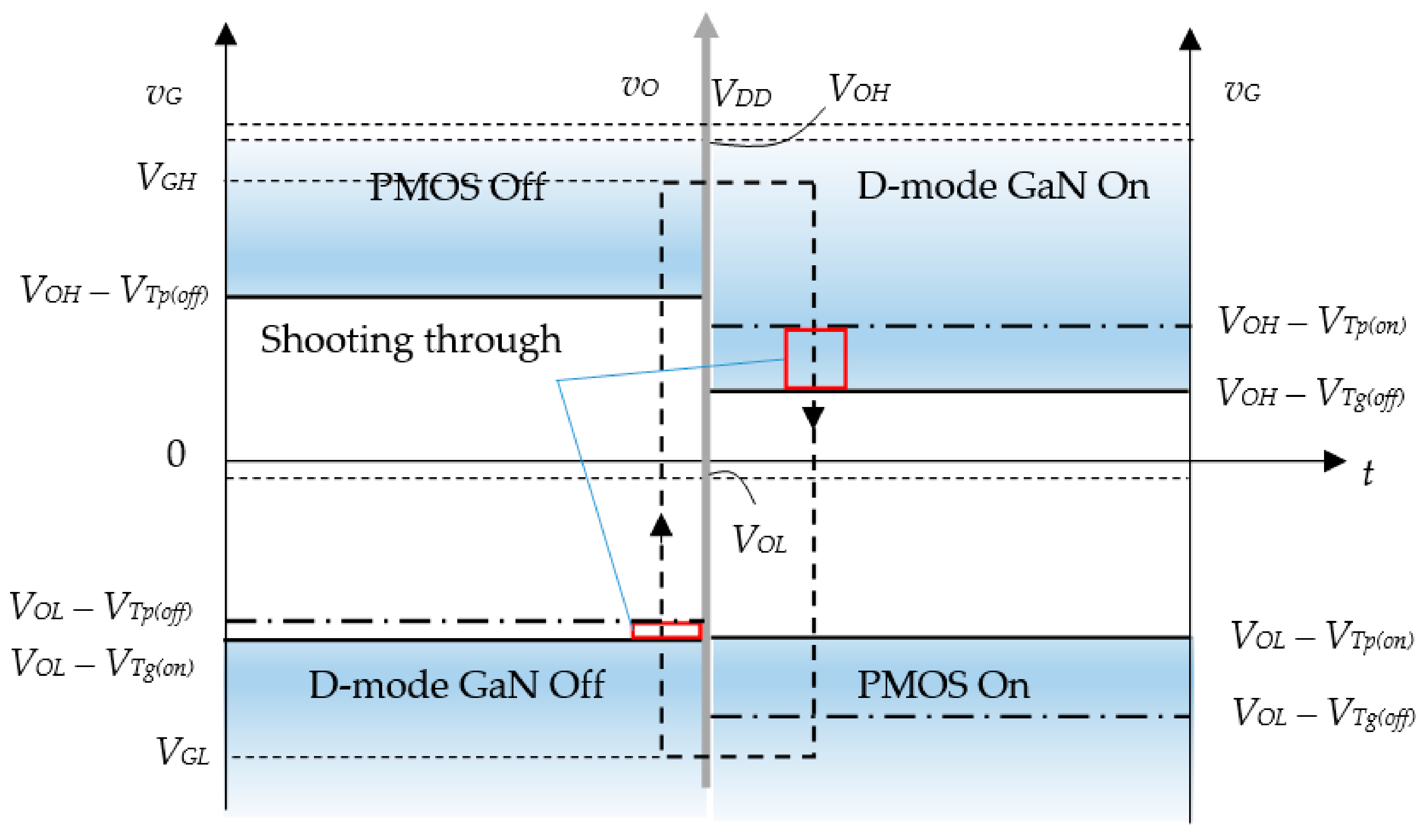

2.3. P-Cascode GaN HEMT Module as a Double Throw Switch

id = 0 else

i2 = 0 else

vO = VOL = vS − i2 ron,PMOS if vOG > VTp

VOL = −io ron,PMOS else

VG,pmos(t) = ρvG(t) else (ρ = CGS/(CG + CGS))

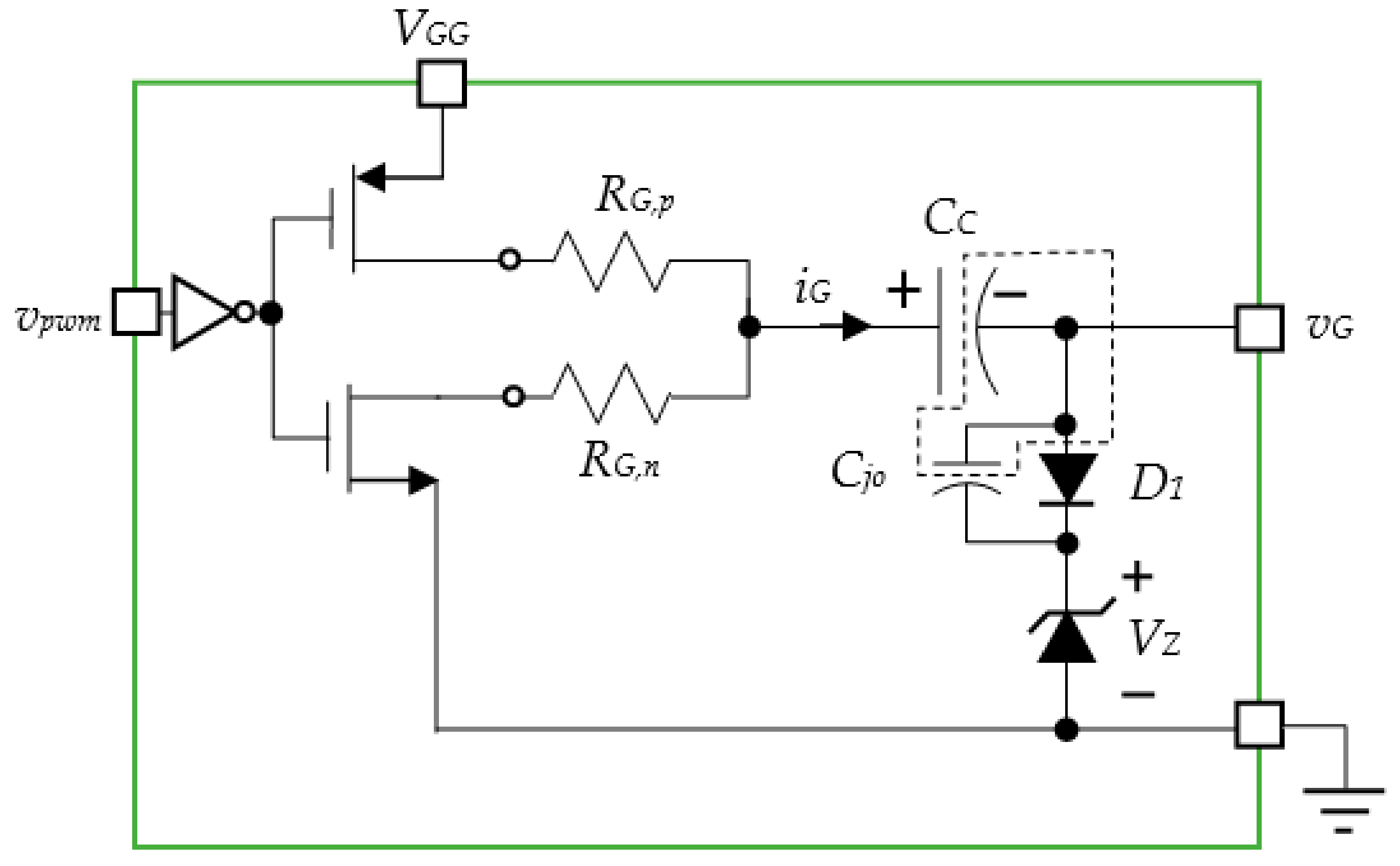

2.4. Biased Charge-Pump Gate Drive Design

vG = vGL = VZ − VGG if vpwm = 0 V

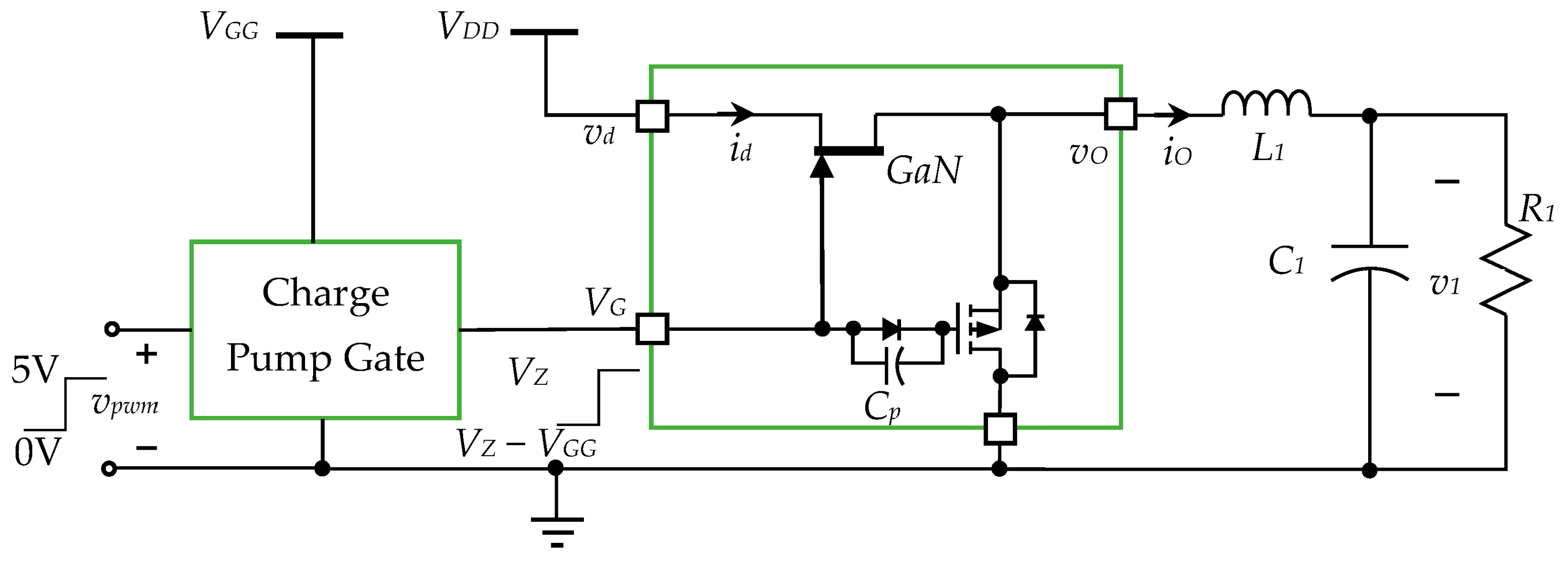

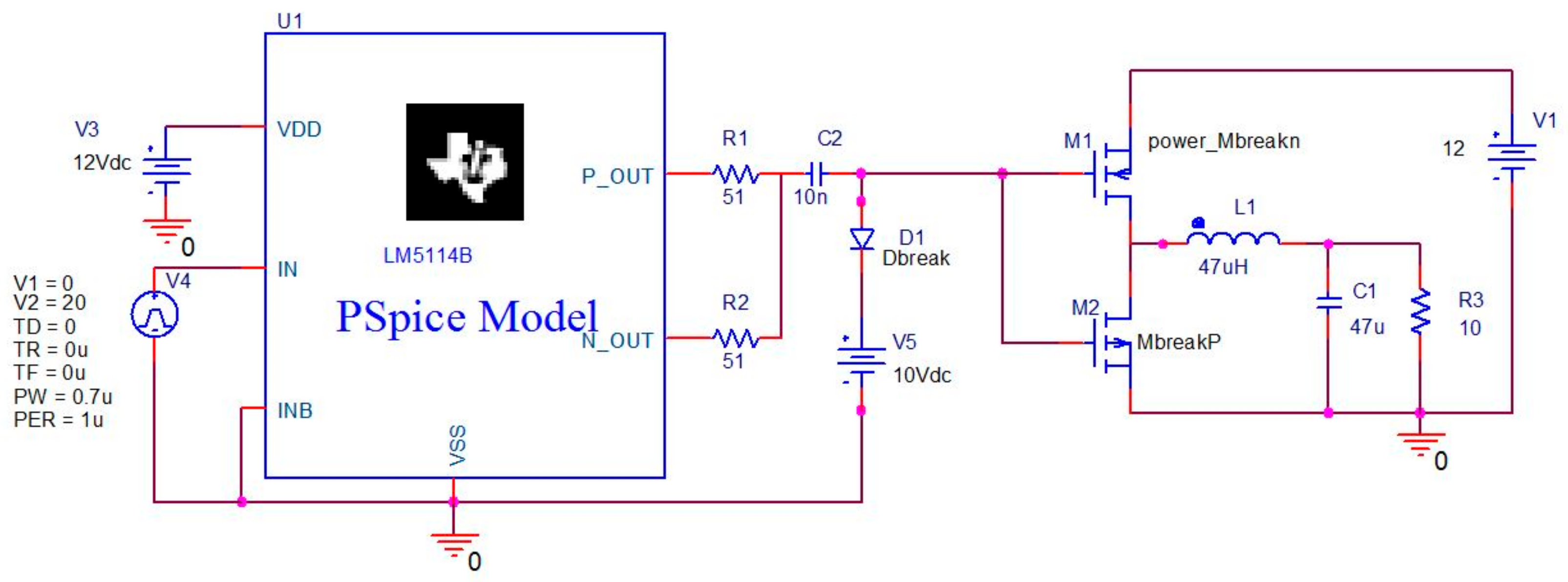

2.5. Synchronous Buck Converter

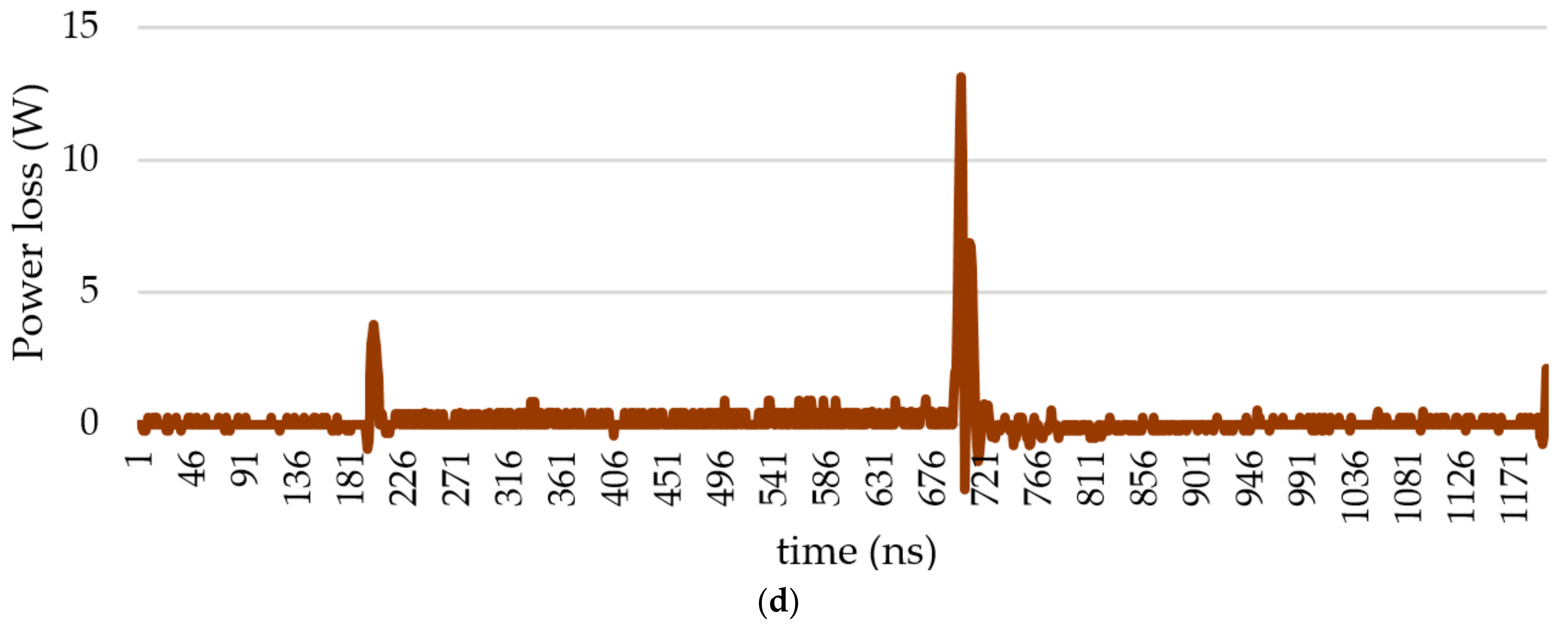

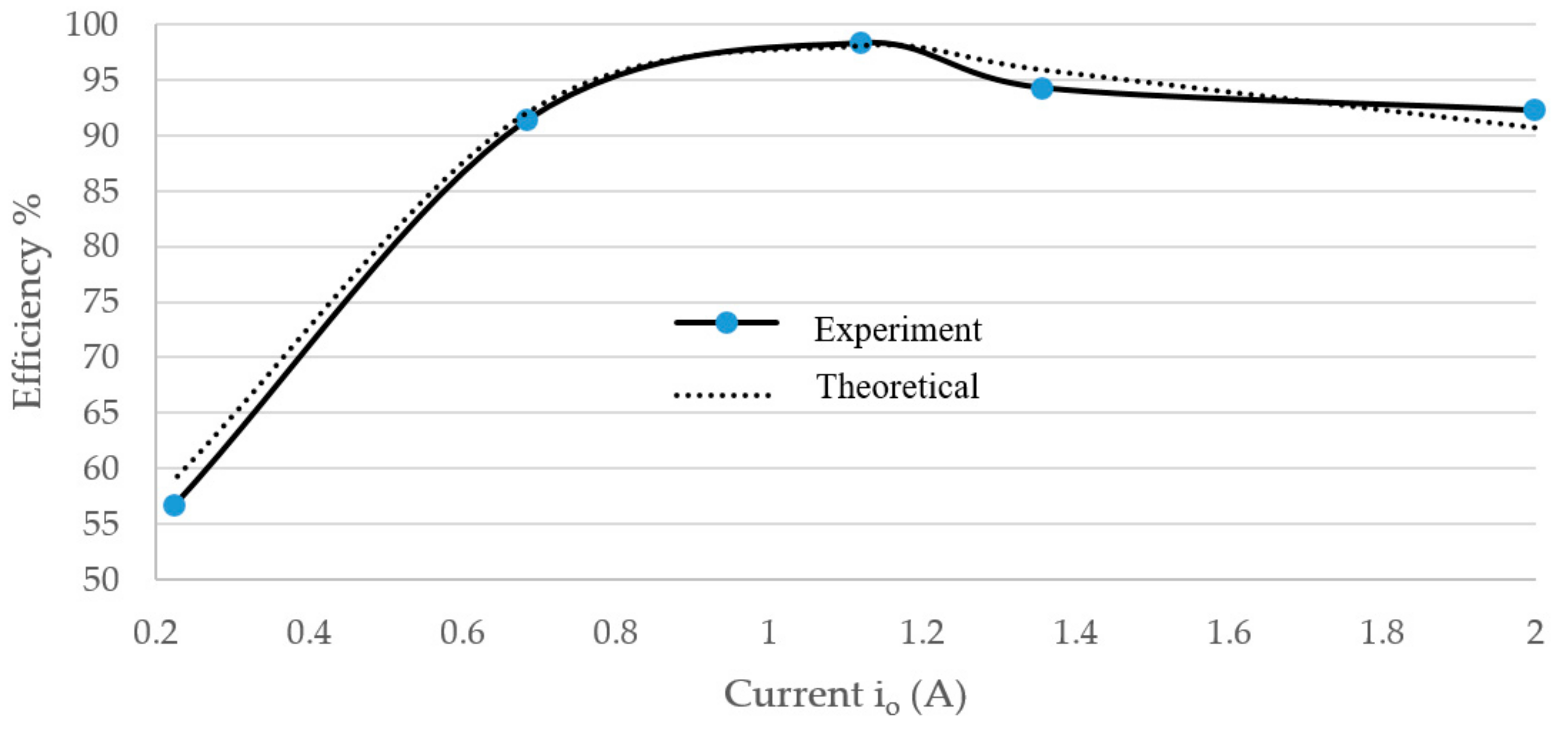

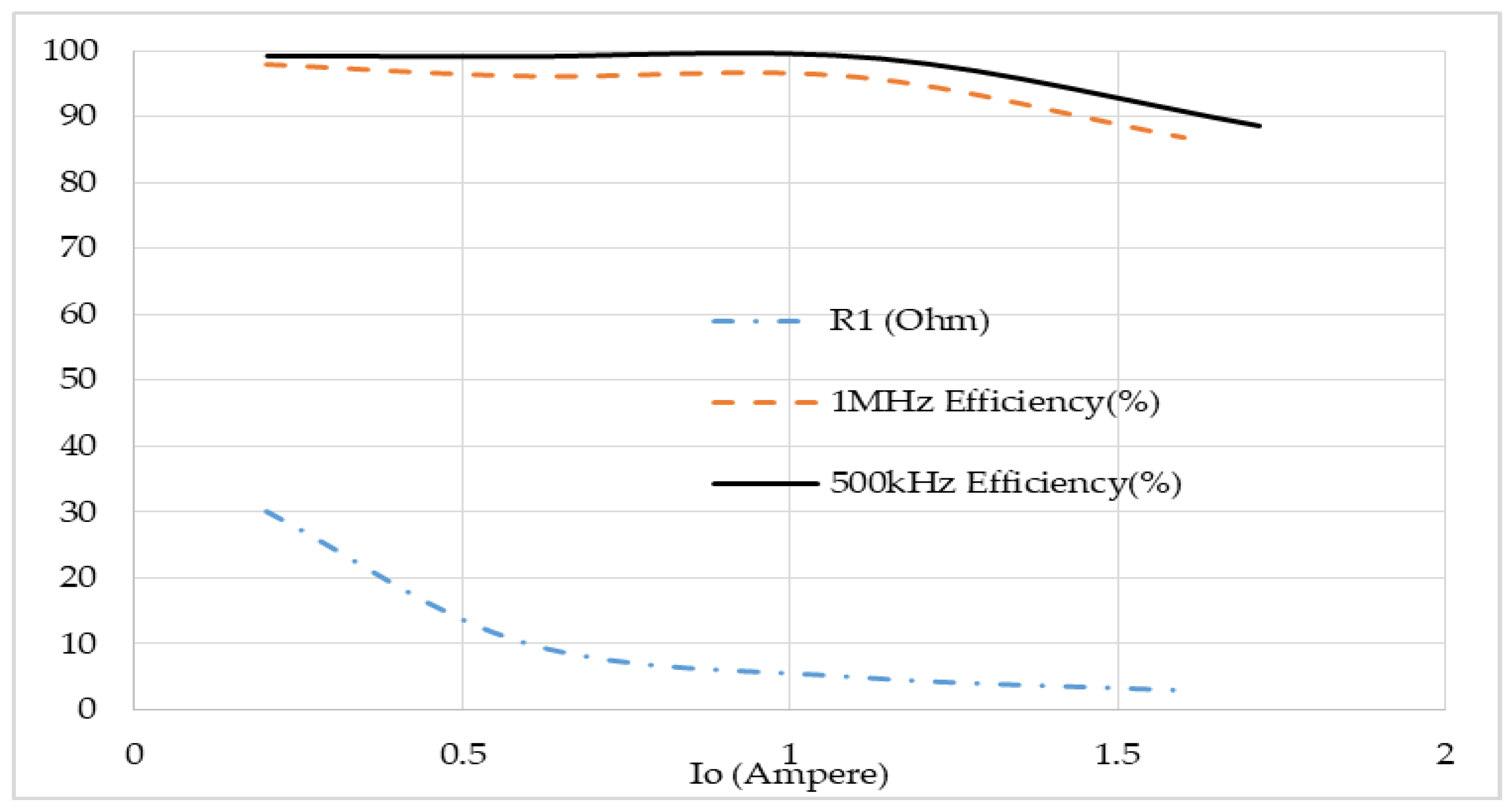

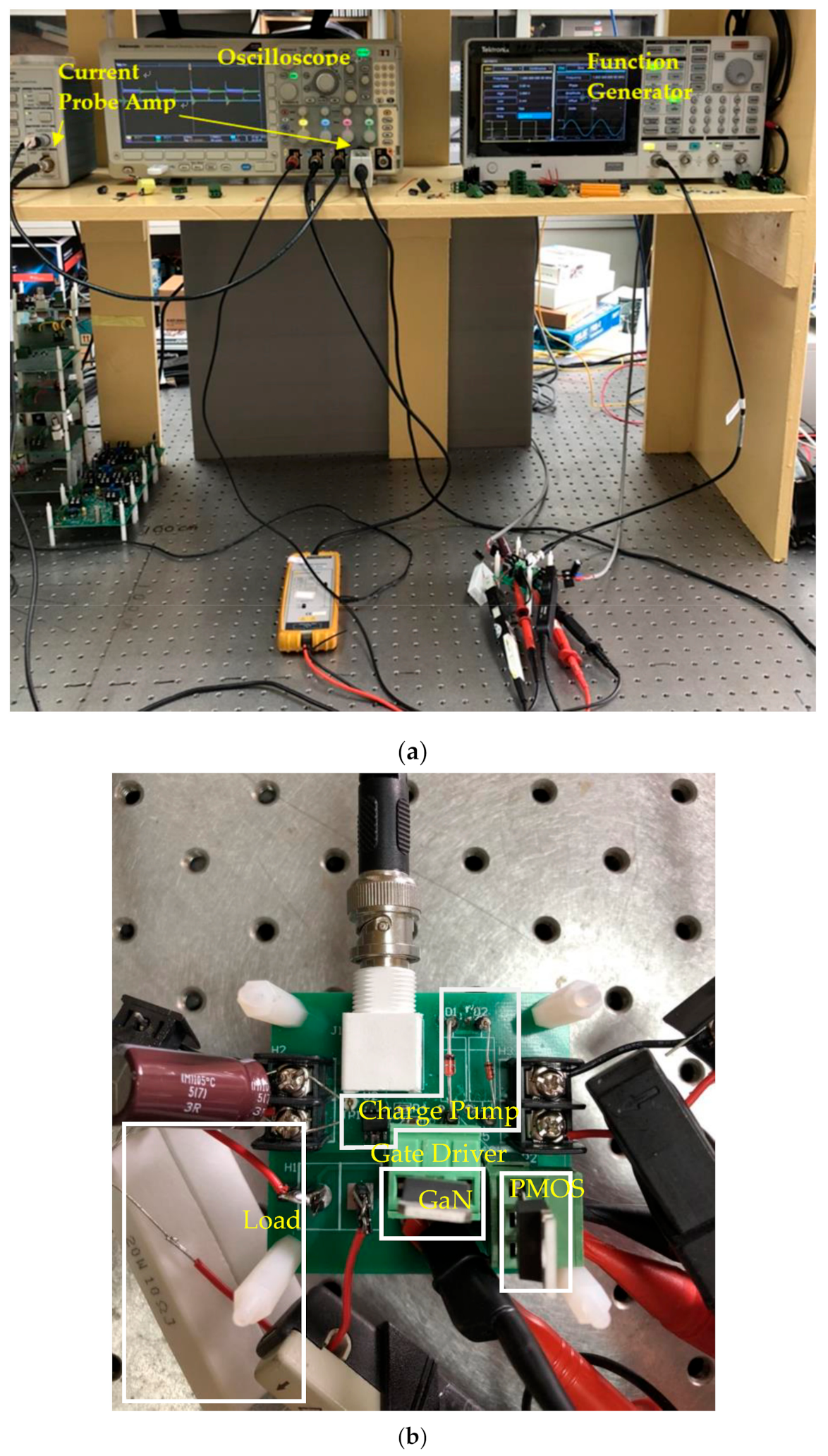

3. Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Abdelrahman, A.S.; Erdem, Z.; Attia, Y.; Youssef, M.Z. Wide bandgap devices in electric vehicle converters: A performance survey. Can. J. Electr. Comput. Eng. 2018, 41, 45–54. [Google Scholar]

- Nan, C.; Ayyanar, R.; Xi, Y. A 2.2-MHz active-clamp buck converter for automotive applications. IEEE Trans. Power Electron. 2017, 33, 460–472. [Google Scholar] [CrossRef]

- He, J.; Cheng, W.C.; Wang, Q.; Cheng, K.; Yu, H.; Chai, Y. Recent Advances in GaN-Based Power HEMT Devices. Adv. Electron. Mater. 2021, 7, 2001045. [Google Scholar] [CrossRef]

- Nikoo, M.S.; Jafari, A.; Perera, N.; Matioli, E. New insights on output capacitance losses in wide-band-gap transistors. IEEE Trans. Power Electron. 2019, 35, 6663–6667. [Google Scholar] [CrossRef]

- Dalla Vecchia, M.; Ravyts, S.; Van den Broeck, G.; Driesen, J. Gallium-Nitride Semiconductor Technology and Its Practical Design Challenges in Power Electronics Applications: An Overview. Energies 2019, 12, 2663. [Google Scholar] [CrossRef] [Green Version]

- Rodriguez, J.; Lamar, D.G.; Roig, J.; Rodriguez, A.; Bauwens, F. Improving the third quadrant operation of superjunction MOSFETs by using the cascode configuration. IEEE Trans. Power Electron. 2018, 34, 2726–2738. [Google Scholar] [CrossRef] [Green Version]

- Xu, J.; Gu, L.; Ye, Z.; Kargarrazi, S.; Rivas-Davila, J.M. Cascode GaN/SiC: A wide-bandgap heterogenous power device for high-frequency applications. IEEE Trans. Power Electron. 2019, 35, 6340–6349. [Google Scholar] [CrossRef]

- Lyu, G.; Wang, Y.; Wei, J.; Zheng, Z.; Sun, J.; Zhang, L.; Chen, K.J. A Normally-off Copackaged SiC-JFET/GaN-HEMT Cascode Device for High-Voltage and High-Frequency Applications. IEEE Trans. Power Electron. 2020, 35, 9671–9681. [Google Scholar] [CrossRef]

- Jiang, S.; Lee, K.B.; Zaidi, Z.H.; Uren, M.J.; Kuball, M.; Houston, P.A. Field Plate Designs in All-GaN Cascode Heterojunction Field-Effect Transistors. IEEE Trans. Electron Devices 2019, 66, 1688–1693. [Google Scholar] [CrossRef]

- Huang, X.; Du, W.; Lee, F.C.; Li, Q.; Liu, Z. Avoiding Si MOSFET avalanche and achieving zero-voltage switching for cascode GaN devices. IEEE Trans. Power Electron. 2015, 31, 593–600. [Google Scholar] [CrossRef]

- Huang, X.; Li, Q.; Liu, Z.; Lee, F.C. Analytical loss model of high voltage GaN HEMT in cascode configuration. IEEE Trans. Power Electron. 2013, 29, 2208–2219. [Google Scholar] [CrossRef]

- Xue, P.; Maresca, L.; Riccio, M.; Breglio, G.; Irace, A. Investigation on the short-circuit oscillation of cascode GaN HEMTs. IEEE Trans. Power Electron. 2019, 35, 6292–6300. [Google Scholar] [CrossRef]

- Chen, Y.; Wang, R.; Liu, X.; Kang, Y. Gate-Drive Power Supply With Decayed Negative Voltage to Solve Crosstalk Problem of GaN Synchronous Buck Converter. IEEE Trans. Power Electron. 2020, 36, 6–11. [Google Scholar] [CrossRef]

- Lyu, G.; Wang, Y.; Wei, J.; Zheng, Z.; Chen, K.J. Dv/Dt-Control of 1200-V Normally-off SiC-JFET/GaN-HEMT Cascode Device. IEEE Trans. Power Electron. 2020, 36, 3312–3322. [Google Scholar] [CrossRef]

- Xie, Y.; Chen, C.; Huang, Z.; Liu, T.; Kang, Y.; Luo, F. High frequency conducted EMI investigation on packaging and modulation for a Sic-based high frequency converter. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1789–1804. [Google Scholar] [CrossRef]

- Chou, P.-C.; Chen, S.-H.; Hsieh, T.-E.; Cheng, S.; Del Alamo, J.A.; Chang, E.Y. Evaluation and Reliability Assessment of GaN-on-Si MIS-HEMT for Power Switching Applications. Energies 2017, 10, 233. [Google Scholar] [CrossRef] [Green Version]

- Elangovan, S.; Cheng, S.; Chang, E.Y. Reliability characterization of gallium nitride MIS-HEMT based cascode devices for power electronic applications. Energies 2020, 13, 2628. [Google Scholar] [CrossRef]

- Chou, P.C.; Hsieh, T.E.; Cheng, S.; Del Alamo, J.A.; Chang, E. Comprehensive dynamic on-resistance assessments in GaN-on-Si MIS-HEMTs for power switching applications. Semicond. Sci. Technol. 2018, 33, 055012. [Google Scholar] [CrossRef] [Green Version]

- Chen, S.H.; Chou, P.C.; Cheng, S. Evaluation of thermal performance of packaged GaN HEMT cascode power switch by transient thermal testing. Appl. Therm. Eng. 2016, 98, 1003–1012. [Google Scholar] [CrossRef]

- Chou, H.P.; Cheng, S. Thermal performance evaluation of cascode Paralleled-GaN-HEMTs packaging for high power switching applications. J. Therm. Sci. Technol. 2017, 12, JTST0022. [Google Scholar] [CrossRef] [Green Version]

- Wu, C.C.; Jeng, S.L. Comparison of Parasitic Capacitances of Packaged Cascode Gallium Nitride Field-effect Transistors. Sens. Mater. 2018, 30, 453–461. [Google Scholar]

- Wu, C.C.; Jeng, S.L. Simulation Model Development for Packaged Cascode Gallium Nitride Field-Effect Transistors. Crystals 2017, 7, 250. [Google Scholar] [CrossRef] [Green Version]

- Lin, Y.C.; Chen, S.H.; Lee, P.H.; Lai, K.H.; Huang, T.J.; Chang, E.Y.; Hsu, H.-T. Gallium Nitride (GaN) High-Electron-Mobility Transistors with Thick Copper Metallization Featuring a Power Density of 8.2 W/mm for Ka-Band Applications. Micromachines 2020, 11, 222. [Google Scholar] [CrossRef] [Green Version]

- Weng, Y.C.; Wu, C.C.; Chang, E.Y.; Chieng, W.H. Minimum Power Input Control for Class-E Amplifier Using Depletion-Mode Gallium Nitride High Electron Mobility Transistor. Energies 2021, 14, 2302. [Google Scholar] [CrossRef]

- Ishibashi, T.; Okamoto, M.; Hiraki, E.; Tanaka, T.; Hashizume, T.; Kikuta, D.; Kachi, T. Experimental validation of normally-on GaN HEMT and its gate drive circuit. IEEE Trans. Ind. Appl. 2014, 51, 2415–2422. [Google Scholar] [CrossRef]

- Yoshida, K.; Ishii, T.; Nagagata, N. Zero voltage switching approach for flyback converter. In Proceedings of the Fourteenth International Telecommunications Energy Conferences, Washington, DC, USA, 4–8 October 1992; pp. 324–329. [Google Scholar]

- Liu, C.Y.; Wang, G.B.; Wu, C.C.; Chang, E.Y.; Cheng, S.; Chieng, W.H. Derivation of the Resonance Mechanism for Wireless Power Transfer Using Class-E. Amplifier. Energies 2021, 14, 632. [Google Scholar] [CrossRef]

- Kolar, J.W.; Krismer, F.; Lobsiger, Y.; Mühlethaler, J.; Nussbaumer, T.; Miniböck, J. Extreme Efficiency Power Electronics. In Proceedings of the International Conference of Integrated Power Electronics Systems (CIPS 2012), Nuremberg, Germany, 6–8 March 2012; pp. 1–22. [Google Scholar]

| Symbol | Unit | Description | Value | vDS | |

|---|---|---|---|---|---|

| 0 V | 12 V | ||||

| vGS,ON (or −VTg) | V | Turn-on voltage (All) | −4 | ||

| Turn-off voltage (800 kHz switching) | −4 | ||||

| Turn-off voltage (1 kHz switching) | −7 | ||||

| CDS | pF | Parasitic capacitance | 75 | 70 | |

| CGD | pF | Parasitic capacitance | 245 | 220 | |

| CGS | pF | Parasitic capacitance | 140 | 140 | |

| VGS,max | V | Maximum gate-source voltage | 8 | ||

| VDS,BD | V | Drain-source breakdown voltage | 35 | ||

| id,max | A | Maximum drain current | 60 | ||

| Ld + Ls | nH | Stray Inductance, drain to source (100 kHz) | 80 | ||

| Ld + Ls | nH | Stray Inductance, source to drain (100 kHz) | 120 | ||

| Symbol | Unit | Description | Value |

|---|---|---|---|

| L1 | μH | Buck Converter | 47 |

| C1 | μF | 47 | |

| R1 | Ω | 5 | |

| PMOS | STD10P6F6 | P-Cascode GaN HEMT Module | - |

| GaN HEMT | NCTU | Table 1 | |

| Cp | pF | 1000 | |

| CG | nF | 100 | |

| RG,p | Ω | Gate driver | 30 |

| RG,n | Ω | 51 | |

| CC | nF | 100 | |

| Zener Vz | V | Gate driver, Break down voltage | 10 |

| VDD | V | Voltage Source | 12 |

| VGG | V | 20 |

| Symbol | Unit | Description | Value | |

|---|---|---|---|---|

| 0 V | 12 V | |||

| Ciss | pF | GaN HEMT | 390 | 270 |

| Ciss | pF | PMOS | 450 | 370 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, C.-C.; Liu, C.-Y.; Wang, G.-B.; Shieh, Y.-T.; Chieng, W.-H.; Chang, E.Y. A New GaN-Based Device, P-Cascode GaN HEMT, and Its Synchronous Buck Converter Circuit Realization. Energies 2021, 14, 3477. https://doi.org/10.3390/en14123477

Wu C-C, Liu C-Y, Wang G-B, Shieh Y-T, Chieng W-H, Chang EY. A New GaN-Based Device, P-Cascode GaN HEMT, and Its Synchronous Buck Converter Circuit Realization. Energies. 2021; 14(12):3477. https://doi.org/10.3390/en14123477

Chicago/Turabian StyleWu, Chih-Chiang, Ching-Yao Liu, Guo-Bin Wang, Yueh-Tsung Shieh, Wei-Hua Chieng, and Edward Yi Chang. 2021. "A New GaN-Based Device, P-Cascode GaN HEMT, and Its Synchronous Buck Converter Circuit Realization" Energies 14, no. 12: 3477. https://doi.org/10.3390/en14123477

APA StyleWu, C.-C., Liu, C.-Y., Wang, G.-B., Shieh, Y.-T., Chieng, W.-H., & Chang, E. Y. (2021). A New GaN-Based Device, P-Cascode GaN HEMT, and Its Synchronous Buck Converter Circuit Realization. Energies, 14(12), 3477. https://doi.org/10.3390/en14123477