Abstract

In this paper a simple PSpice (Personal Simulation Program with Integrated Circuit Emphasis) macro-model was developed, and verified for monolithic power operational amplifiers operated with a single-supply voltage. The proposed macro-model is developed using simplification and build-up techniques for macro-modeling of operational amplifiers and simulates the basic static and dynamic characteristics, including input impedance, small-signal frequency responses at various voltage gains, output power versus supply voltage, slew-rate-limiting, voltage limiting, output offset voltage versus supply voltage ripples, and output resistance. Furthermore, the macro-model also takes into account the ground reference voltage in the amplifier at a single power supply voltage. The model is implemented as a hierarchical structure suitable for the PSpice circuit simulation platform. The sub-circuit is built using standard PSpice components and analog behavioral modeling blocks. The accuracy of the model is verified by extracting the model parameters for single-supply power operational amplifier TDA2005 from ST Microelectronics as example. The effectiveness of the model is validated by comparing the simulation results of the electrical parameters with the corresponding measured values obtained by experimental testing of sample circuits. The comparative analysis shows that the relative error of the modeled large-signal parameters is less than 15%. Moreover, an error of 15% is quite acceptable, considering the technological tolerances of the electrical parameters for this type of analog ICs.

1. Introduction

Despite the growing part of the digital devices in the modern electronic systems, there are still many applications that will always perform by analog circuits. One application of this type is when, for example, a small signal from a microphone or digital-to-analog converter needs to be amplified and to drive an outside load (e.g., actuator, loudspeaker, or wireline). In many cases, the amplifier has to transmit a significant electrical power (e.g., PL ≥ 1 W) to a certain load with high energy efficiency and without significant distortion. According to the value of the higher cutoff frequency fh, the power amplifiers are low-frequency (with fh ≤ 100 kHz) and high-frequency (with fh > 100 kHz) circuits.

The low-frequency monolithic power operational amplifiers are essential building blocks of the audio power amplifiers and the output drivers in many industrial controllers. To take full advantage of the monolithic powerful amplifiers and to provide the process of implementation of new electronic systems, a detailed analysis and evaluation is needed. In the process of circuit design, it is necessary to perform a preliminary evaluation of the various electronic circuit topologies in terms of static and dynamic modes of operation. For example, the achieving a certain operating frequency range at a certain value of the power gain is examined, as well as the ability to provide the output power on a load while maintaining the stability of the circuit. Moreover, the functionality of the designed electronic circuit must be simulated, the values of the passive components has to be adjusted and the obtained structure has to be experimentally tested to prove in advance the fulfillment of the requirements in the technical specification. Conducting accurate analog circuit simulations is conditioned by the simple and accurate models or macro-models of the passive and active components. The majority of the previously developed macro-models of operational amplifiers (op amps), suitable for the PSpice (Personal Simulation Program with Integrated Circuit Emphasis) circuit simulation program, have been intended for low power applications (ranging up to 100 mA) [1,2,3,4,5,6,7,8,9]. Moreover, the description of all models is adapted to the circuit simulators based on the SPICE (Simulation Program with Integrated Circuit Emphasis) program. In [2,6] a midpoint has been realized in the equivalent circuits, for relating all internal voltages to it, and to provide the proper operation of the macro-model at an asymmetrical power supply voltage. Also, in [7,9] through external resistor dividers, it has been possible to work with a single power supply voltage. However, these additional functional blocks do not provide a full possibility for the implementation of class-B and class-AB of the output stages in the power amplifiers, when only a single- supply voltage is used.

In this paper, based on the simulation models, represented in [1,2,7], a simple electrical macro-model was developed, and verified for monolithic power amplifiers operated with a single-supply voltage. The developed macro-model included the basic static and dynamic effect of the real device and it was implemented as a hierarchical structure, suitable for the PSpice circuit simulation program. The paper is an extension of work [10] originally reported in the 28th International Conference on Mixed Design of Integrated Circuits and Systems—MIXDES 2021.

The paper is organized as follows. Section 2 presents the macro-model description—structure of the commercially available monolithic power amplifiers, block diagram of the proposed macro-model and mathematical equations with the corresponding model parameters. Also, in Section 2 are represented the analytical expressions for determination of the modeling parameters of the proposed model. The verification of the developed macro-model is given in Section 3 and is performed by comparing the simulation results with experimental results at frequency and time domain for sample electronic circuits. For verification of the workability and efficiency of the macro-model, the model parameters are extracted for IC TDA2005 from STMicroelectronics as example. Finally, in Section 4 of the paper, the concluding remarks and guidelines for future work are given.

2. Macro-Model Description

2.1. Macromodel Development

The basic technical requirements to the monolithic power amplifiers are: (1) to provide a certain electrical power to an external load, which in the general case has active and reactive components; (2) introduce minimal non-linear distortions into the wave-form of the amplified input signal; (3) to provide high energy efficiency (in this way, the greater economy is ensured, which is essential at high output power); (4) to have large input and small output resistance (this makes it easier to match the load with the output stage of the amplifier and achieves a high value of the power gain); (5) to have protection stages against short circuit or thermal overload of the output transistors. The implementation by the semiconductor manufacturers of the above requirements determines the efficiency and workability of the power amplifiers in a wide range of variations of the input voltage or power supply voltage.

Several semiconductor manufacturers, such as Maxim®, Analog Devices®, Philips®, Sanyo®, Samsung®, SGS Thomson®, ST Microelectronics®, and Texas Instruments® offer commercially available various types of monolithic power amplifiers. Some integrated circuits of the power amplifiers contain only an output stage, but often a preamplifier is included in the chip. Their basic electrical circuit is similar to those with discrete components [11,12,13,14,15]. The passive components that cannot be integrated into the chip (such as, capacitors with high capacitance, coils, and potentiometers) are connected externally to the circuit. One of the basic monolithic integrated power amplifiers is those of the ST Microelectronics from the TDA-series [14,15]. The basic DC and AC parameters and their typical values for the monolithic amplifiers from TDA-series are presented in Table 1.

Table 1.

Basic DC and AC electrical parameters for the monolithic amplifiers from TDA-series.

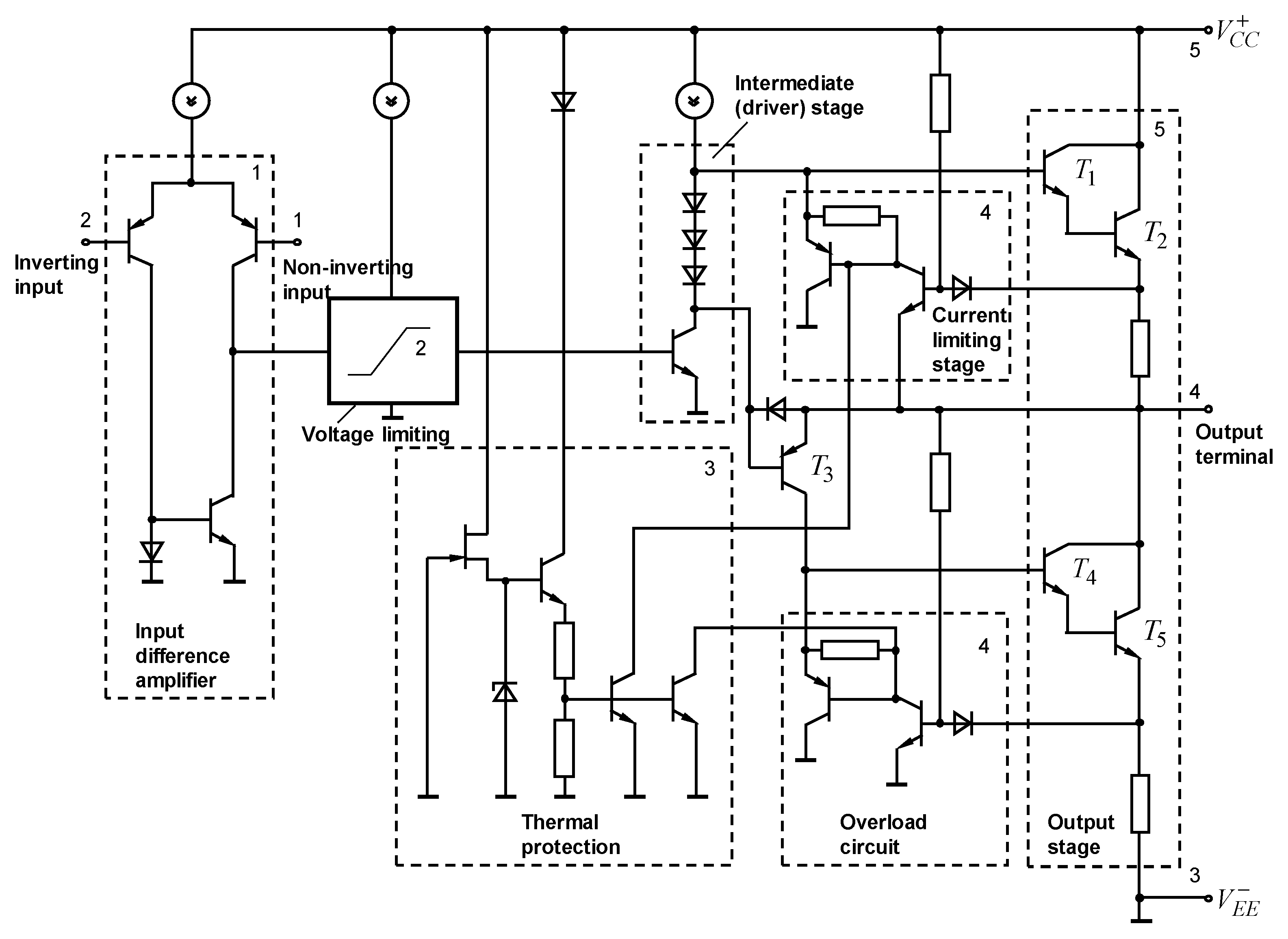

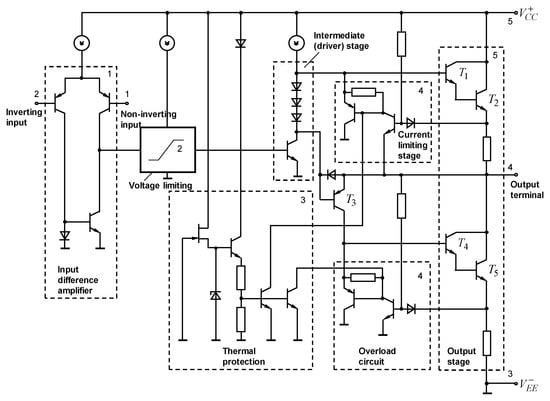

In Figure 1 is a simplified circuit diagram of a TDA2030 power amplifier is given. As can be seen, the electrical circuit is divided into three sections (or stages): input stage, intermediate (or driver) stage and output stage. The input stage is a differential amplifier with a symmetrical input and single-ended output port. It provides the input impedance of the circuit and part of the open-loop voltage gain. The intermediate stage is an active-loaded common emitter amplifier, preceded by a voltage limiting circuit. From the output terminal of the intermediate stage, the signal is applied to the output stage. Its structure is similar to the basic output stage and includes two complementary Darlington transistors. The output stage provides the output voltage swing and output resistance. The transistors , and form the composite NPN-transistor according to the Darlington scheme, and the transistor , together with the Darlington transistors and , form a composite PNP-transistor. In addition to the main amplifier stages, the chip also includes thermal protection and current limiting circuits.

Figure 1.

A simplified circuit diagram of a TDA2030 from TDA-series power amplifiers [14,15].

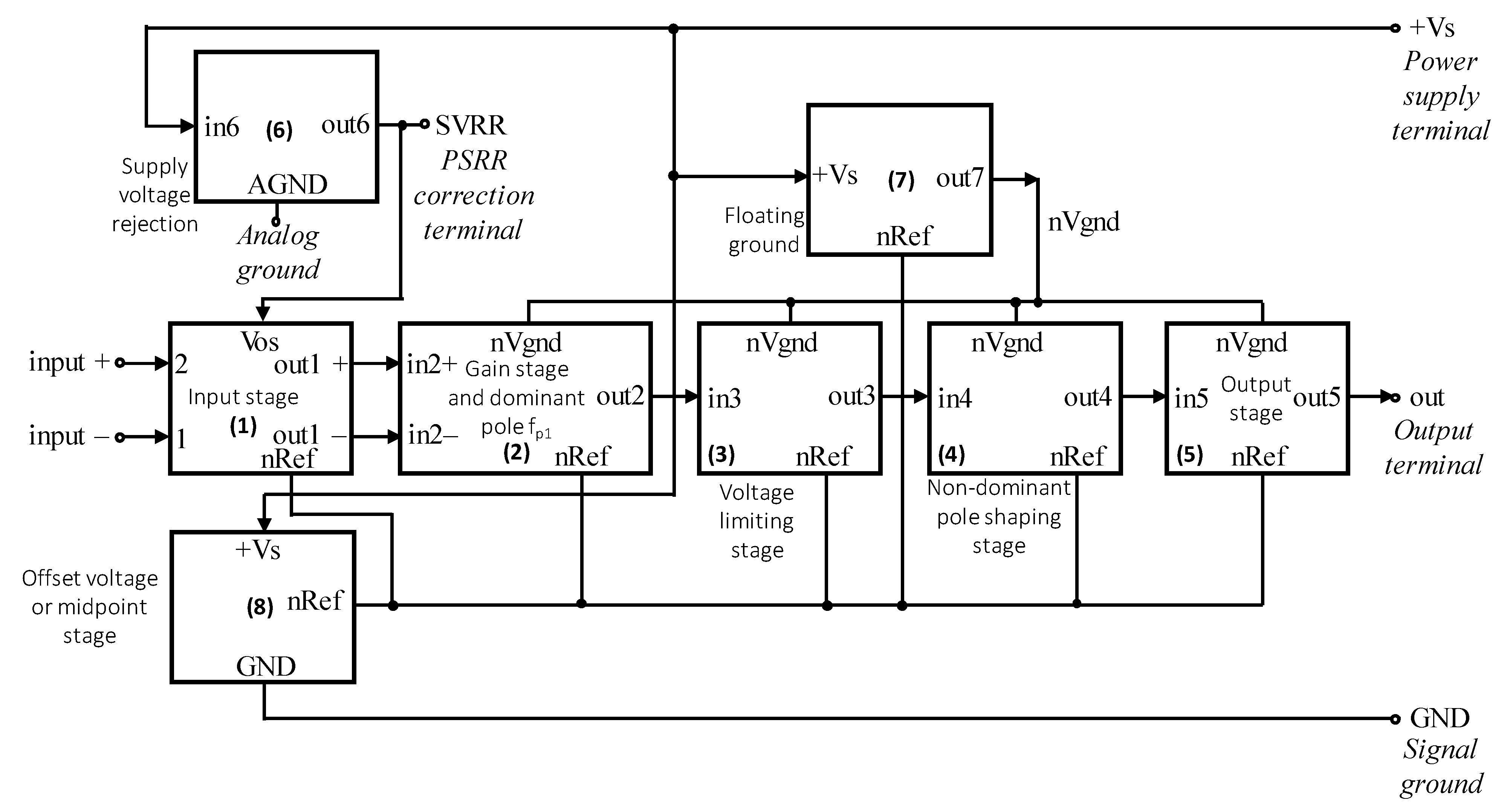

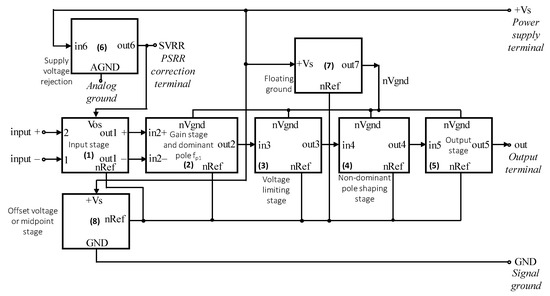

Based on the simplified circuit diagram in Figure 1, a block diagram of the proposed model (Figure 2) is developed. In Figure 2, the block diagram includes basically an input stage, an intermediate (amplifying) stage, and an output stage connected in a cascade structure. Additionally, three blocks are connected to the structure, providing the midpoint of the model, the floating ground, and the supply voltage rejection ratio. According to the complexity of the amplitude-frequency characteristic of a concrete amplifier, the number of frequency-shaping stages can be increased, as well as the structure of the stage modeling the suppression of the pulsations in the supply voltage can be changed.

Figure 2.

Block diagram of the proposed macromodel for power amplifiers.

2.2. PSpice Implementation

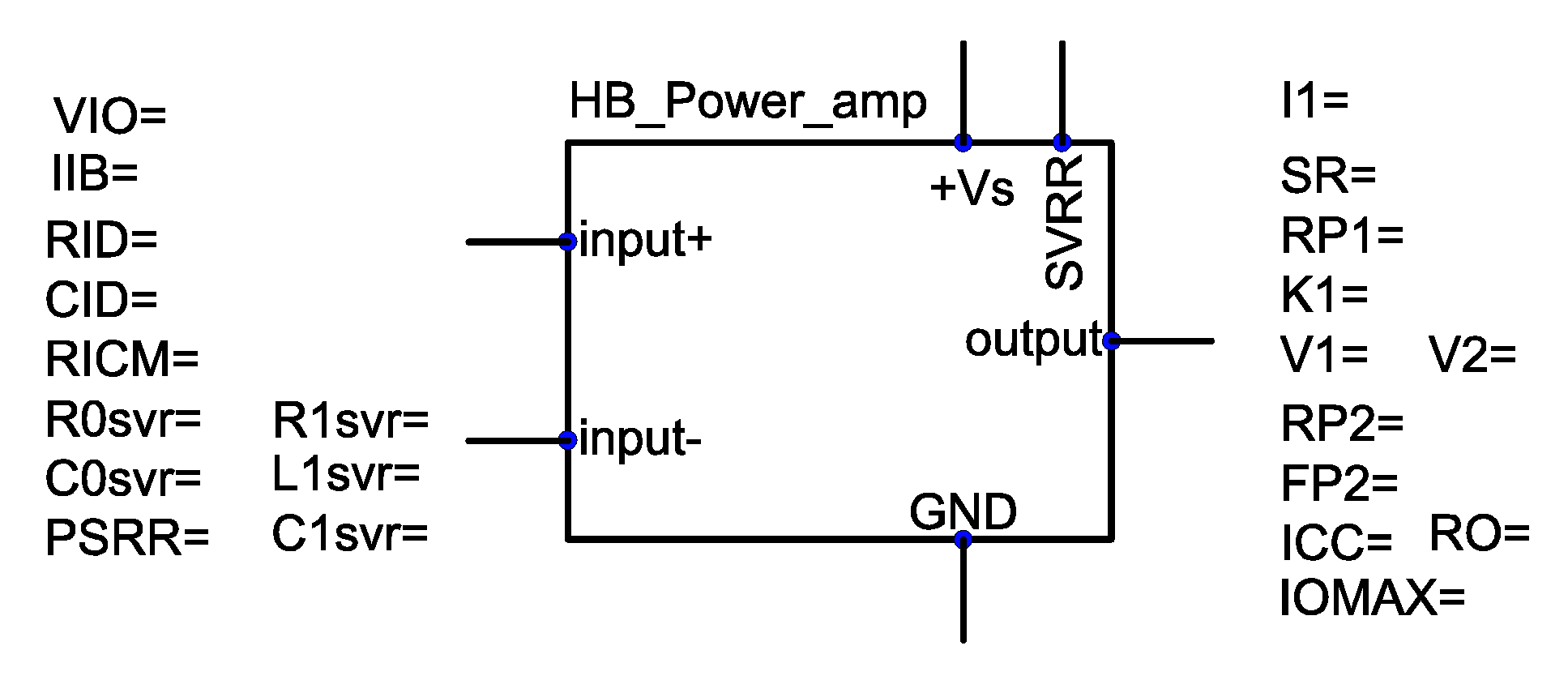

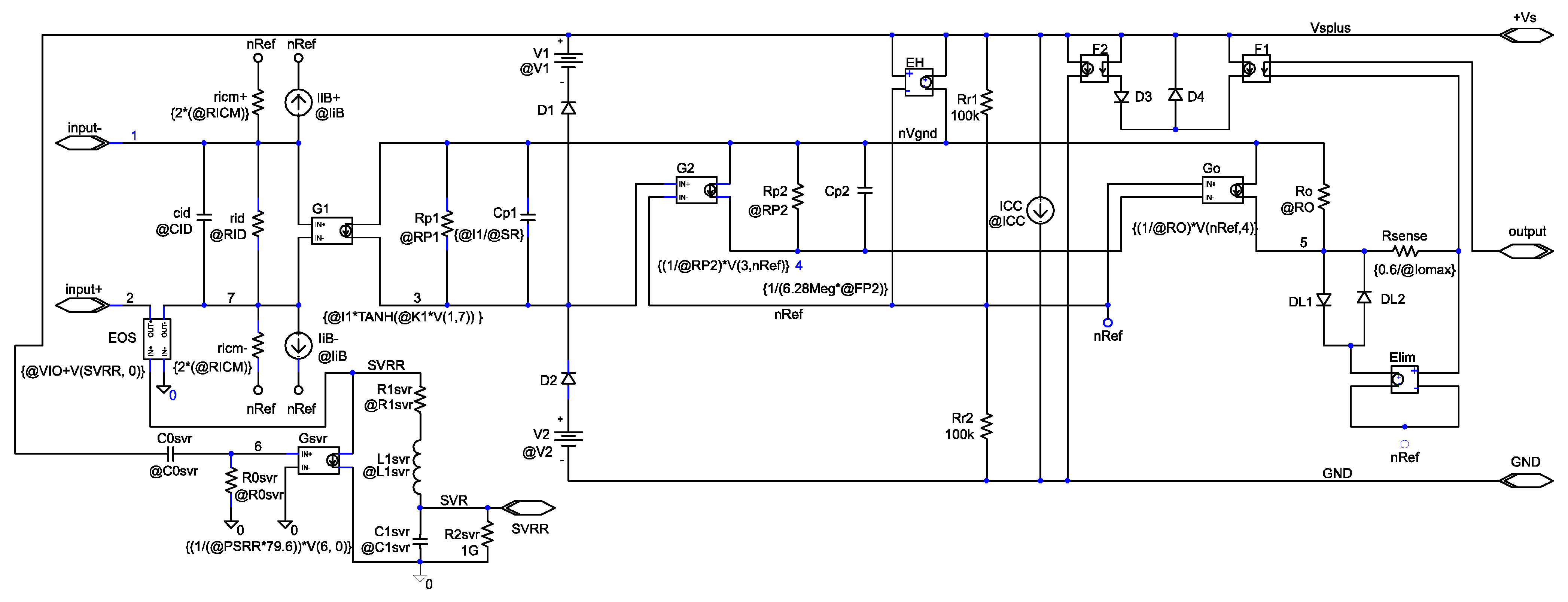

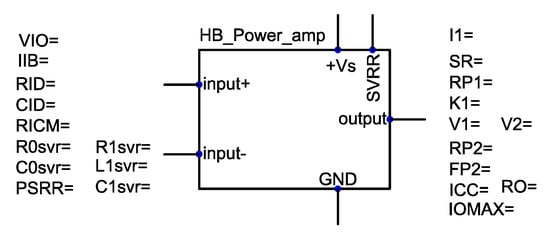

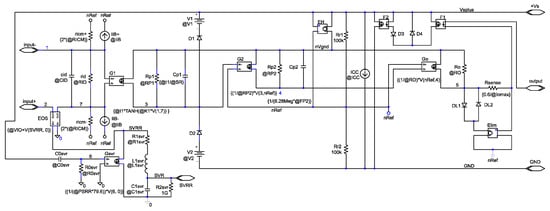

To develop PSpice macro-model for monolithic power amplifiers, simplification and build-up techniques for macro-modeling of operational amplifiers was used [1]. Based on the block diagram, shown in Figure 2, the macro-model was implemented as a two-level hierarchical structure. The higher-level block diagram with the modeling parameters, defined without concrete values, is presented in Figure 3. Depending on the choice of a certain type of amplifier in dialog mode, concrete numerical values can be set for the modeling parameters. The equivalent electrical circuit (the lower level of hierarchy) of the macro-model is given in Figure 4. As can be seen, there is a correspondence between the names of the external terminals (or pins), and also in the description of the block diagram (Figure 3) the name of the equivalent circuit in Figure 4 was set, so that it can be loaded and processed during of the simulation process.

Figure 3.

The higher-level block diagram of the proposed macromodel with the modeling parameters.

Figure 4.

The equivalent electrical circuit of the proposed macro-model for power amplifiers.

In particular, the structure of the equivalent circuit (Figure 4) includes both standard PSpice components and analog behavioral modeling (ABM) blocks. The usage of ABM blocks, such as various controlled sources, provides the implementation of linear and non-linear mathematical functions in the PSpice program. As can be seen, the equivalent electrical circuit is represented as properly connected controlled sources, independently controlled sources, resistors, capacitors, and a small group of ideal diodes. The external interface terminals of the circuit are non-inverting input (input+), inverting input (input–), an output terminal (out), supply voltage ripple rejection terminal (SVRR), positive power supply (+Vs), and analog ground (GND). As can be seen, there is no ground reference in any of the signal-processing blocks. The only exception is the functional block, which simulates the attenuation of the power supply voltage ripples. All internally generated node voltages are referred to as the voltage at node nVgnd, which is the floating ground of the equivalent circuit. The node voltage nVgnd is produced by the VCVS EH controlled by the midpoint and power supply voltage. The midpoint, called nVref in the model, was generated by two equal resistors (Rr1 and Rr2) connected between the supply rail and the external ground reference.

The input stage consists of and , modeling the input resistance and capacitance between the two input terminals (1 and 7) at a small signal. and are the input resistances, reflecting the behavior at a common-mode input signal. The input resistance is defined as the resistance measured directly between the inverting and non-inverting input of the amplifier:

at .

In the case of an amplifier circuit with asymmetric input, a circuit of a non-inverting amplifier with a grounded inverting input and an active non-inverting input are possible, and vice versa—a circuit of an inverting amplifier with a grounded non-inverting input.

The input resistance in these cases is represented by

The input common-mode resistance is represented, according to

For the majority of the amplifiers .

The input bias current was modeled by two ideal current sources ( and ), connected between the two input terminals (1 and 7) and midpoint nVref. The input offset voltage and offset drift as a result of the power supply ripples is represented with a voltage-controlled voltage source (VCVS) , connected between nodes 2 and 7. The offset voltage modelling power supply ripples (PSRR—power-supply rejection ratio), which are accurately referred to the VCVS , come from two separate frequency shaping stages in the model. The first additionally defined stage consisted of a capacitor and a grounded resistor . The is connected between the power supply voltage (node Vsplus) and the input of the second shaping stage. The voltage drop over the presents the voltage at a node 6 that depends on the ripples of the supply voltage (). The transfer function of the stage is expressed by

The second stage consisted of a voltage-controlled current source (VCCS) controlled by the power supply voltage, and the RLC-stage. The current source was chosen to be linear one-port generator, following the equation

The current will flow through the elements , , and (where is an external grounded capacitor, connected to node SVR), towards the internal ground. In such a way, the voltage V(SVR,0) will depend on the amplitude and the frequency of the ripples of the supply line, and the transfer function of the stage can be expressed by

where is DC proportionality constant, is the time-constant of the polynomic in the numerator, is the damping factor, and is the time-constant of the polynomic in the denominator.

From the comparison of the left and right sides of the above equation, the following formulas were obtained for the main parameters: , —time constant determining the minimum in the frequency response, and , where is equivalent series inductance, is equivalent series capacitance, and is equivalent parallel resistance. The proposed stage from Figure 4 provides a serial resonance, determined by the inductance , and the capacitance , with a minimum value of the resonance resistance. The voltage generated at node SVRR is used for the equation of VCVS as follows

The component in Equation (6) determines the input offset voltage constant (), the coefficient presents the change in as a result of changing the supply voltage. Then, will be determined by the following expression

where is the differential voltage gain of the amplifier and is the voltage gain of the ripples in the power supply line.

The intermediate stage of the model consisted of controlled sources and ideal passive components. It simulated the open-loop voltage gain, the frequency resonance, and the output voltage limiting. The value of the open-loop voltage gain of the model is represented by the VCCS , and the resistor . Therefore, the voltage at a node 3 can be determined by

where is the multiplication factor of the stage.

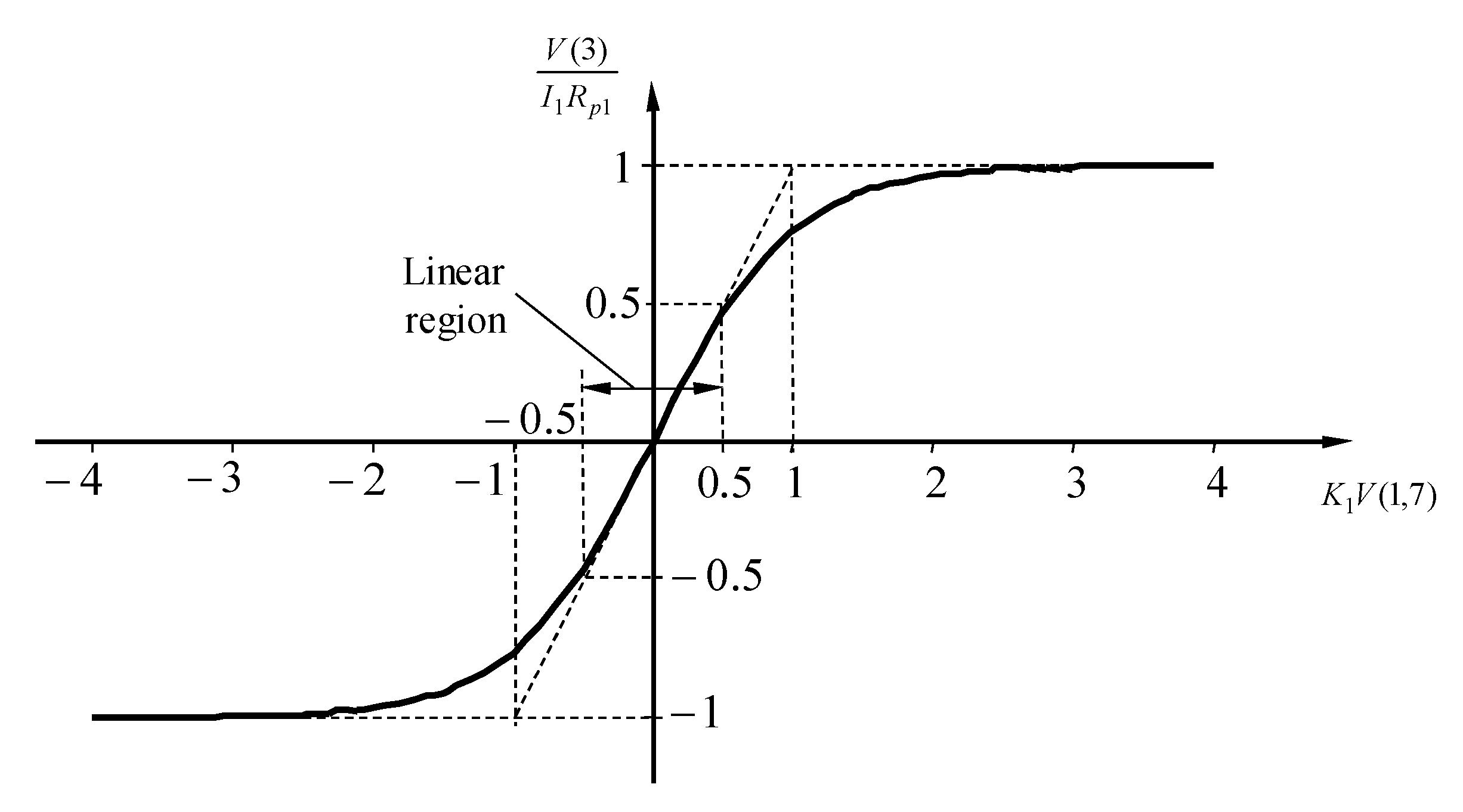

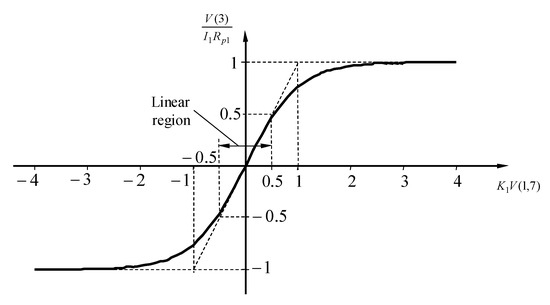

The transfer function (9) is represented in graphical form in Figure 5. Approximately linear region of this function is .

Figure 5.

DC open-loop transfer function of the intermediate stage at large input signal.

The simplification of expression (9) can be performed if the function is decomposed in the Taylor order, i.e.,

at .

If , elements can be taken only up to the third order term in the Taylor series, wherein the formula (9) yields

If , the . The maximum output current charged the capacitor , which created a change of the output voltage per unit time of the amplifier. This rate of change of the voltage per unit time defined the maximum dV/dt (voltage change rate) or slew rate (or SR) of the amplifier:

For the model’s small-signal open-loop DC voltage gain, is obtained

To obtain minimal nonlinear distortions in the waveform of the output voltage (), it is necessary that the input voltage is lower than . Since the mathematical function is symmetric with respect to the origin of the coordinate system, and with respect to the characteristics of the differential pair of transistors in the input stage (transistors have to be as close as possible to technological parameters, which is achieved by applying a single technological process of obtaining the electrical circuit), for the developed macro-model it is possible to obtain smaller values of the nonlinear distortions.

The voltage-limiting network consisted of two ideal diodes ( and ) and two voltage sources ( and ), connected in series. This network limited the voltage at node 3 and the other internal voltages of the macro-model up to values below the power supply voltage during an input-overdrive condition:

where is the thermal voltage and is the saturation current for the two diodes.

The first (dominant) and the second pole frequency are represented in the model by two frequency shaping stages. The dominant pole was modeled by the VCCS , the resistor and the capacitor . The second (non-dominant) pole was modeled by the VCCS , the resistor and the capacitor . The DC voltage gain of the second frequency-shaping block was equal to unity, because the of the VCCS is equal to the reciprocal of the resistance , connected from each node of the VCCS to the floating node of the circuit. In a wide frequency range, the open-loop amplitude-frequency response of the model can be represented by

where is the first pole frequency and is the secondary pole frequency.

The output stage of the model consisted of controlled sources and passive components provided the output signal. It simulated the output resistance and the DC and dynamic of the current consumed by the external power supply device. The VCCS in the output block drives the resistor , connected between the node 5 and the floating ground. The acted as an active current generator and provided the desired voltage drop over its parallel resistor. The DC voltage gain of the output block was equal to unity, because the of the VCCS was equal to the reciprocal of the resistance .

The limitation of the output current was presented in the macro-model through the controlled voltage source , the resistor , and the pair of diodes and [16]. When the voltage drop across the resistor becomes approximately equal to 0.6 V, one of the two diodes ( or ) turns on and the current is limited to .

When there is no load at the output, the model draws only a quiescent current from the power-supply rail by the independent current source in the model, thus behaves similarly to an ideal class-B output stage with a gain equal to unity. When an AC voltage is applied to the input port, as a result of the amplification, the output voltage will have greater amplitude, which is obtained by increasing the power consumption. In the proposed model, the dynamic behavior of the supply current is produced through a pair of current-controlled current sources (CCCSs) ( and ) with unity gain and a pair of ideal diodes ( and ), similar to the op amp models, presented in [2,3,6]. The is controlled by the magnitude of the output current through the load, which in turn generates a current, driving the two diodes. Depending on the magnitude and the direction of the current through the F2, an AC current flows from the power supply to the ground, which average value is proportional to the real consumed current. Another technique for modeling the supply current variations is by using relatively complex high-order (n > 2) nonlinear current source F2 [4].

2.3. Parameter Extraction

Based on the theoretical analysis of the proposed equivalent circuit in this subsection are proposed analytical expressions for determining the modeling parameters of the proposed model (Figure 4) for simulations of monolithic power amplifiers. For better clarity, the expressions are systematized in a table (see Table 2) and they are given separately for each of the individual building blocks. When determining the values of the model parameters, some of them are obtained directly from the datasheet typical values, while others are typical estimated values from device design.

Table 2.

Analytical expressions for the modeling parameters.

3. Results and Discussion

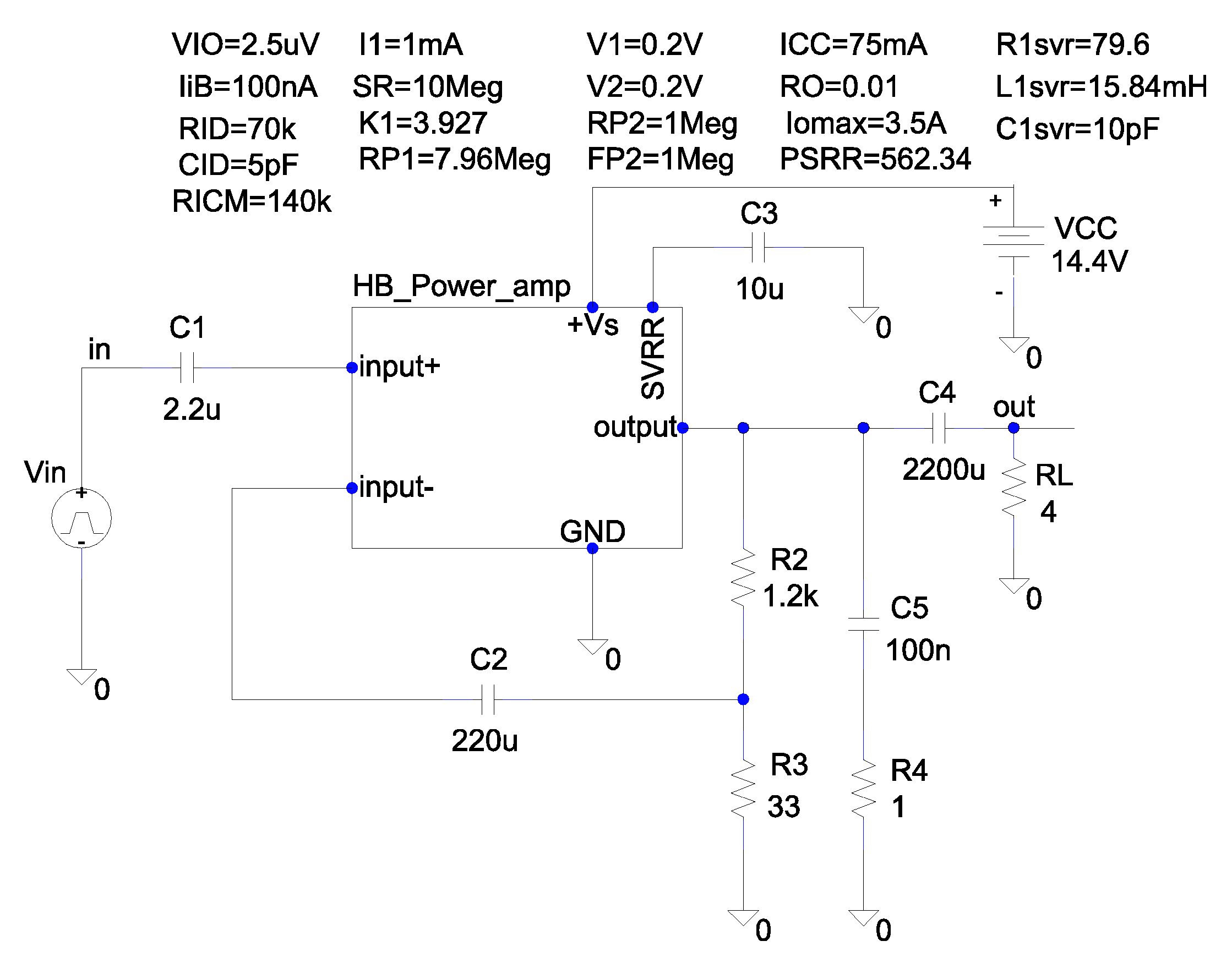

To verify the efficiency of the proposed macro-model the simulation results of the electrical parameters were compared with the corresponding results obtained by the experimental testing of sample analog circuit, using commercially available monolithic power amplifier TDA2005 [17]. The modeling parameters were extracted for TDA2005 by analyzing semiconductor data books and through some characterization measurements. All the modeling parameters for the proposed model that are in good agreement with the experimental results related to the TDA2005 model at , and , are: , , , , , (or 55 dB at ), (at ), , , , , , (at ), (at ), (), , , , , , and .

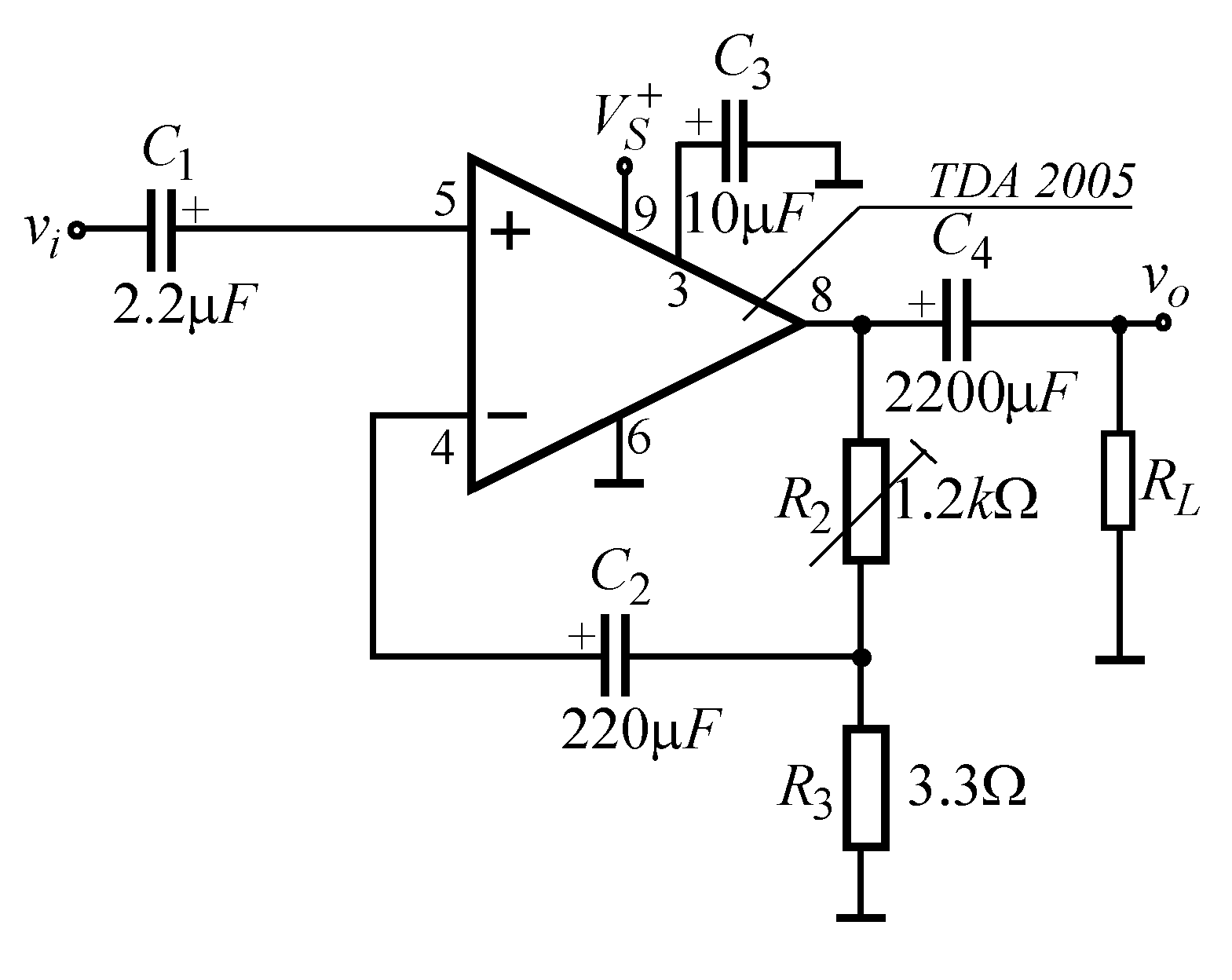

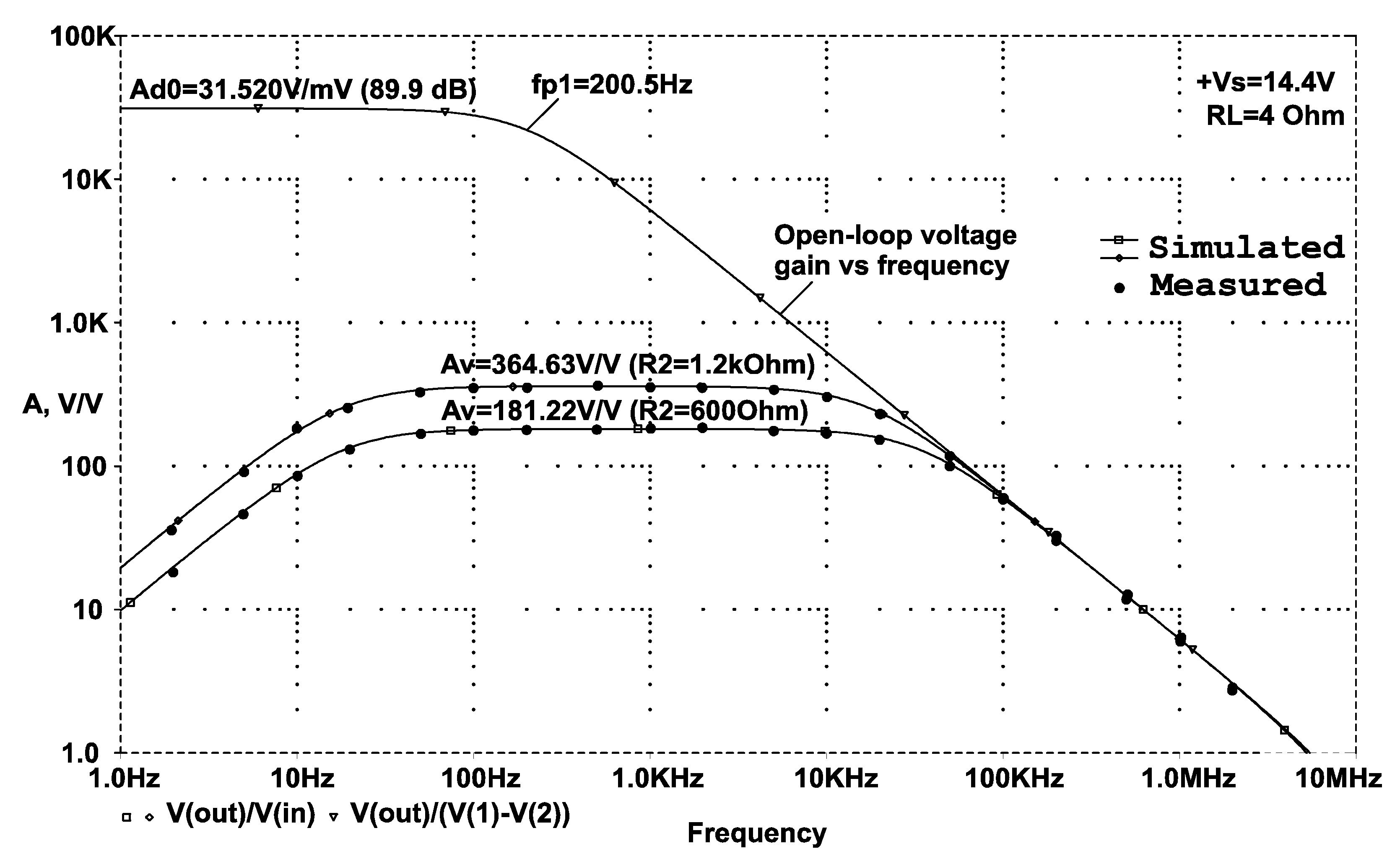

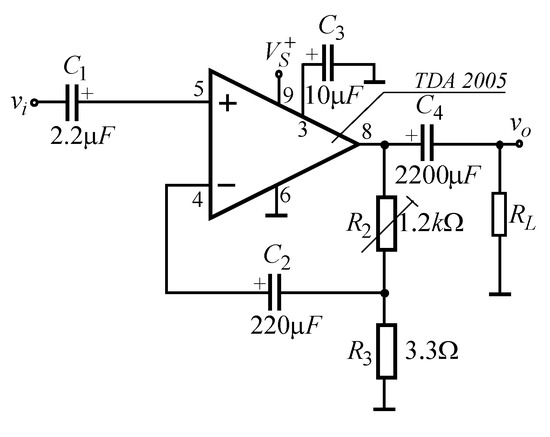

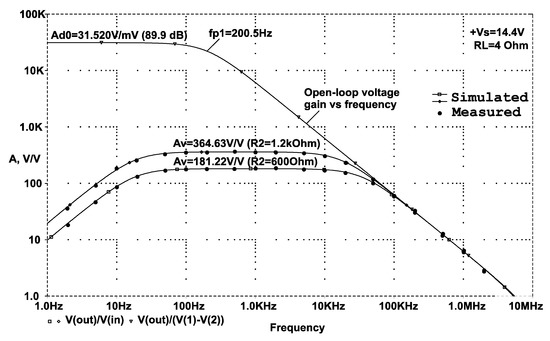

To obtain the amplitude-frequency responses for the various voltage gains, the test circuit, shown in Figure 6 was used. The circuit for the simulation with OrCAD PSpice® 9.0 (previously MSIM® 8) was based on the test condition, given in the datasheet. For the experimental testing, the same circuit was implemented on an FR4 printed circuit board laminate with through-hole device passive components. The recommended area of aluminum plate heatsink was [15], where the junction-to-case thermal resistance is [17]. Figure 7 displays the frequency responses for the two values of the feedback resistor R2, as well as the open-loop voltage gain versus frequency obtained by simulation testing. Thus, the simulated value for the 3-dB cutoff (corner) frequencies were and at , respectively, and the corresponding measured values were —lower cutoff frequency and —upper cutoff frequency, respectively. Also, the simulated values for were , and , and the corresponding measured values were , and . The maximum relative error between the simulation results of the cutoff frequencies and the measured values was not greater than 10%.

Figure 6.

Test circuit [17] for simulation and experimental testing at various voltage gains AV, through the feedback resistor R2.

Figure 7.

Frequency responses of the amplifier circuits at various voltage gains.

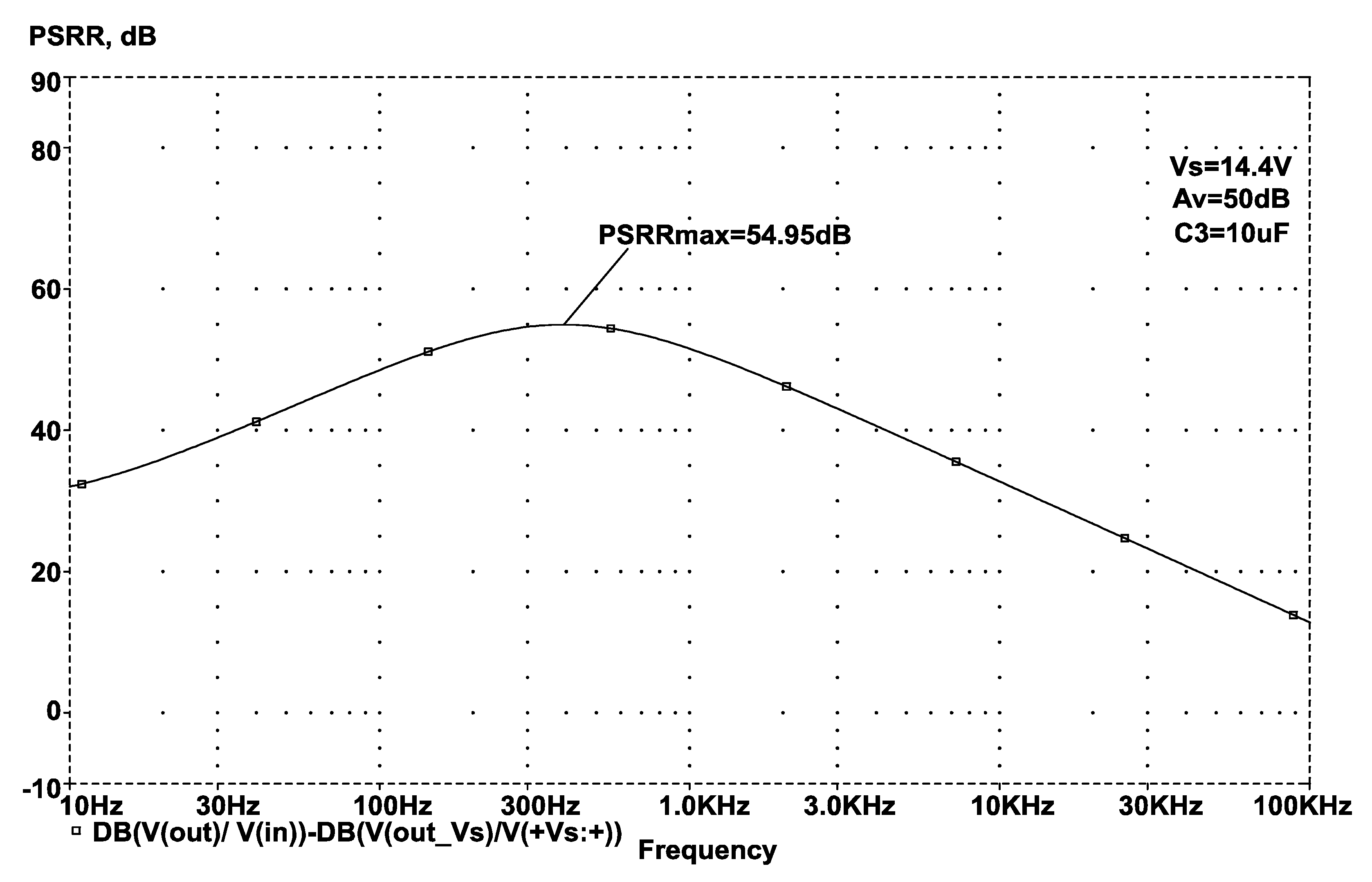

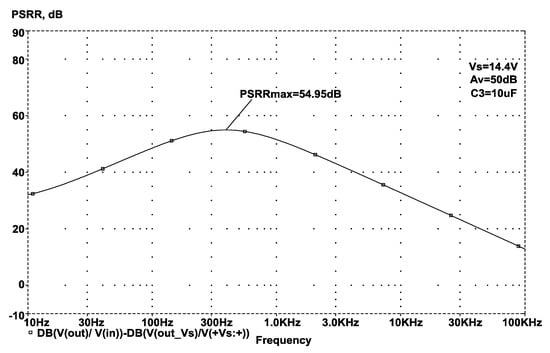

Figure 8 illustrates the frequency response for the simulated PSRR at VS = 14.4 V and RL = 4 Ω. The comparative analysis showed that the simulated response fitted quite closely the actual response [17] (the relative error was below 8%) with correct amount of maximal value of PSRR and the slope of characteristic in the transition area.

Figure 8.

Simulated power supply rejection ratio versus frequency.

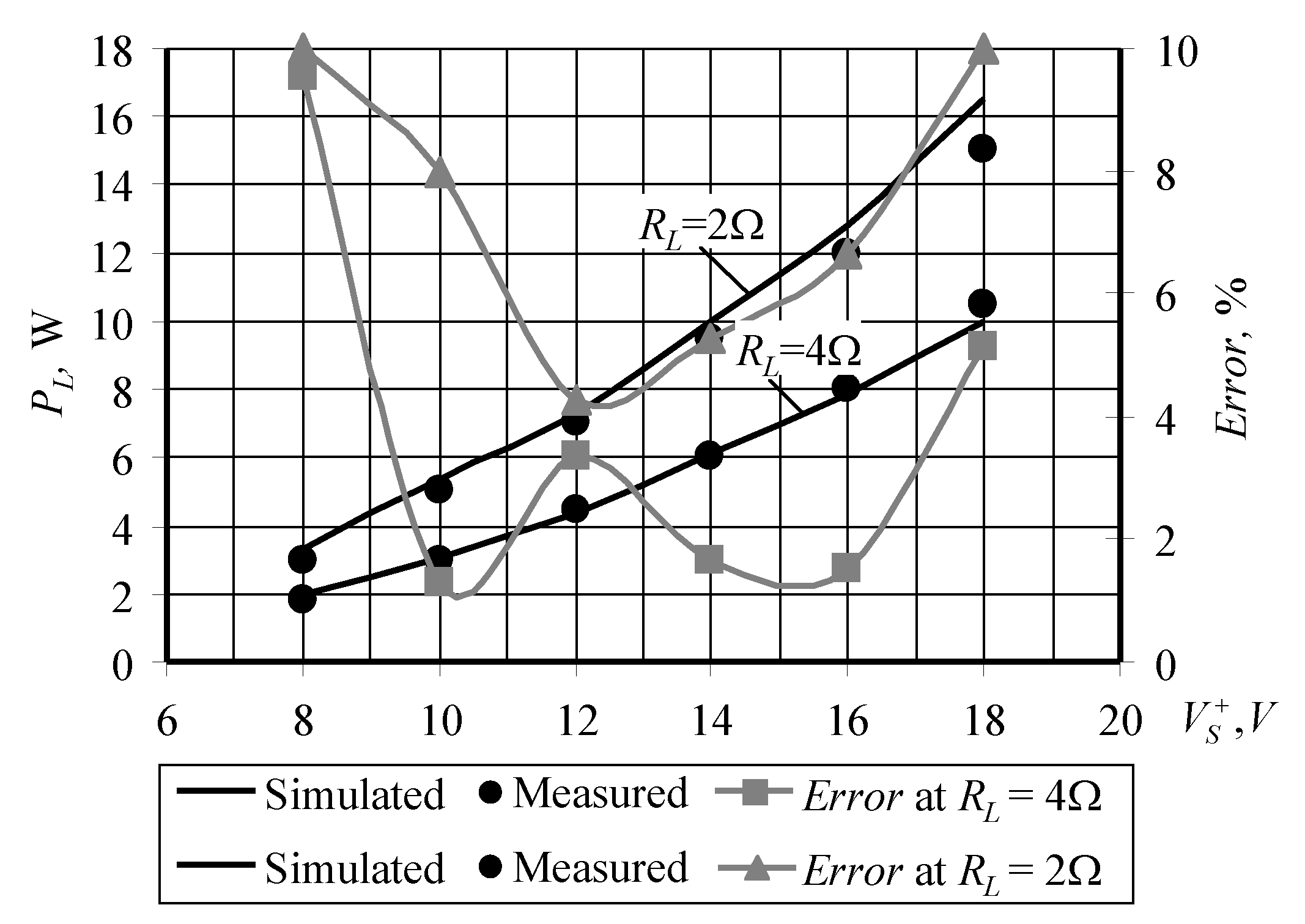

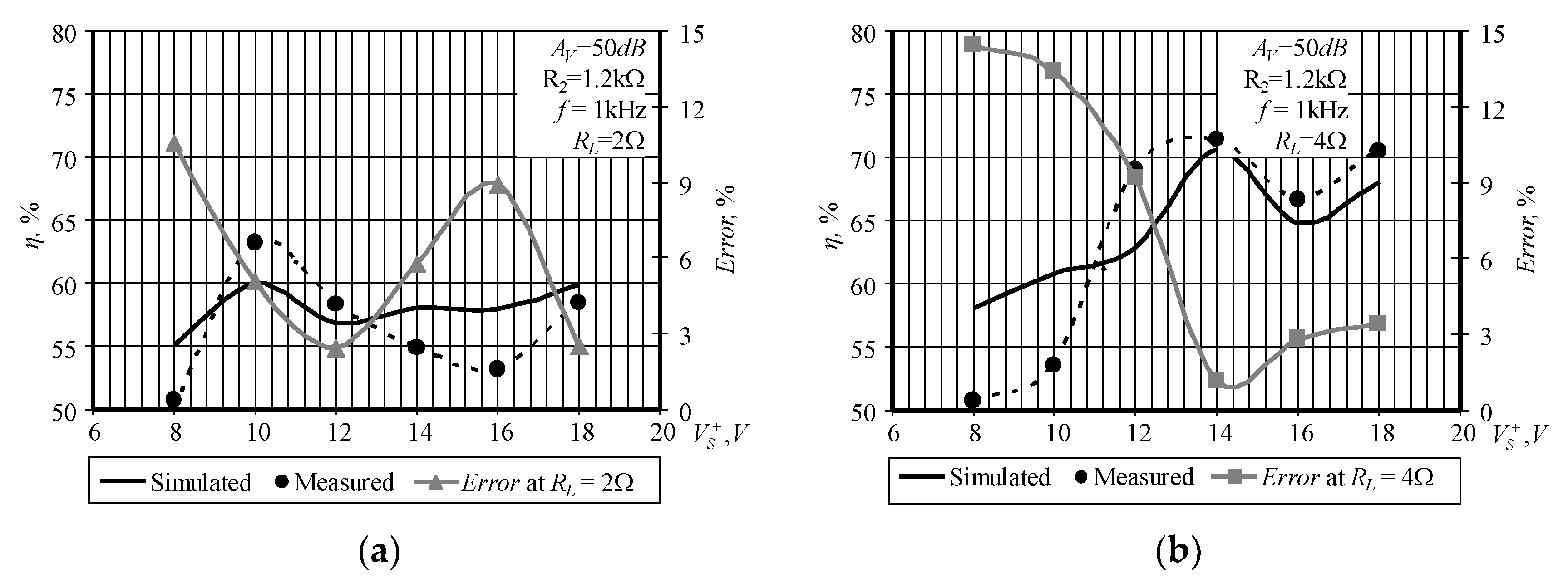

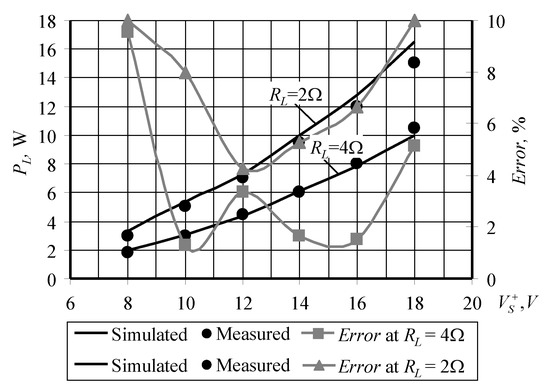

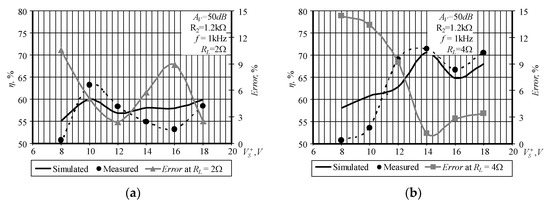

The workability of the proposed macro-model was validated by examining the transient characteristics at a large-signal using the electronic circuits with various external load resistance. For a large-signal, the simulation and experimental results of the energy parameters at RL = 2 Ω ± 5%, and 4 Ω ± 5%, are plotted in Figure 9 and Figure 10. To obtain the electrical parameters, the test circuit with R2 = 1.2 kΩ, given in Figure 6, was used. The sinusoidal input signal with a frequency of 1 kHz was obtained by SFG-2010. The amplitude of the input signal had an amplitude, at which the output signal had no visible non-linear distortions (below 5%). The supply voltage was swept from 8 V to 18 V by using HY3005D-3. The achieved relative error between the measured values for the output power and the simulations for the proposed model, was up to 10%. The error for the energy efficiency (, where is the average value of the supply current) was below 10% (see Figure 10a,b) at Vs > 12 V and RL = 2 Ω and 4 Ω. For Vs ≤ 12 V, and RL = 4 Ω, Figure 10b the supply current had lower value in comparison with the at RL = 2 Ω (Figure 10a), and the error was up to 15% due to the relatively greater influence of the nonlinearities of the volt-ampere characteristics of the transistors.

Figure 9.

Output power PL versus power supply voltage +VS.

Figure 10.

Energy efficiency η versus power supply voltage +VS: (a) at a load resistance equal to 2 Ω; (b) at a load resistance equal to 4 Ω.

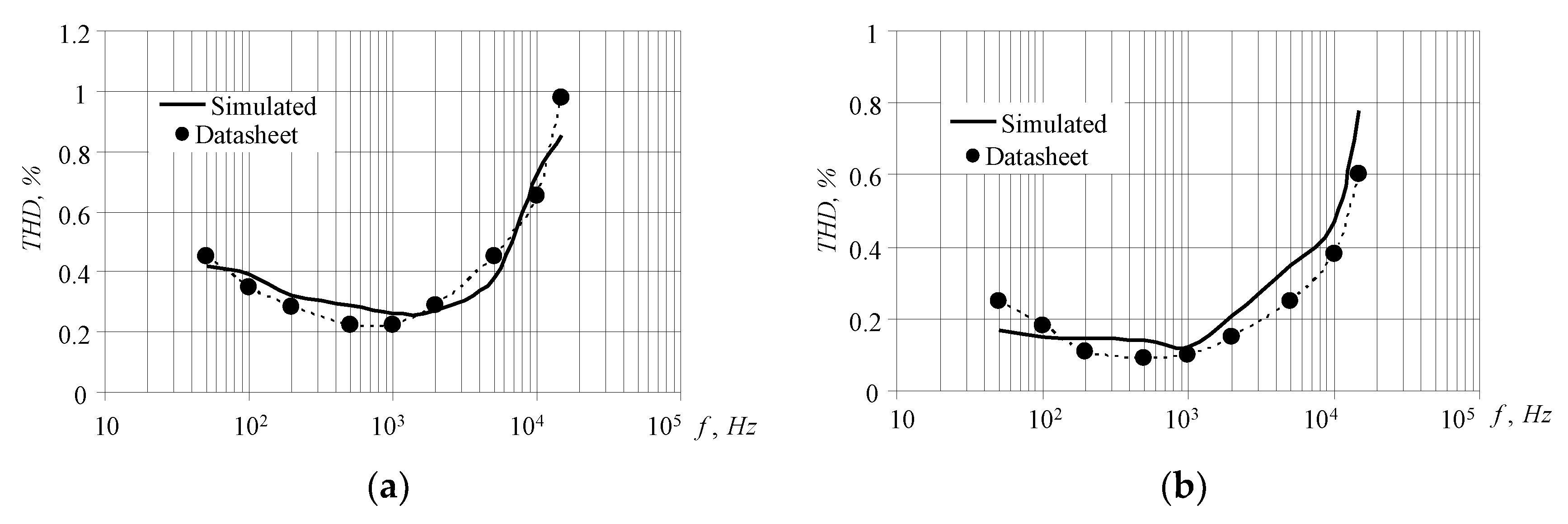

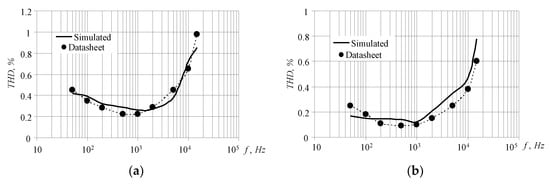

Additionally, at a large signal in Figure 11a,b, the results of a simulation study of the nonlinear distortions at Vs ≤ 14.4 V and () are shown. For this purpose, a transient analysis in combination with a Fourier analysis was performed in the PSpice program environment. An input signal with a sinusoidal form was applied to the input terminals of the circuit to provide approximately the output power for which a value was given for the nonlinear distortions in the datasheet of the real device. For the frequency range from 50 Hz to 15 kHz, a final simulation time equal to 100 ms was selected. In this case, the print step and the step celling had the same values equal to 1 μs. In this way, a waveform of the output signal can be provided with a print step of no more than PERIOD OF THE INPUT SIGNAL/100. As can be seen, the relative error, for some values of the input frequency, was greater than 20% (as the maximum value of the total harmonic distortion (THD) was below 1%), therefore the results showed that the proposed macro-model can simulate the trend of change of nonlinear distortions in the process of preliminary studies of sample electronic circuits. The average value of the absolute deviation (taking into account the algebraic sign for each value of the coefficient) at a load equal to 2 Ω is 13.069%, and at a load equal to 4 Ω is 20.821%. In many practical cases, the modeled direction of change of nonlinear distortions is sufficient, taking into account the technological tolerances of the parameters of the integral and discrete components, as well as the instability of the supply voltage. For the maximum output power with a typical value of 20 W, when bridging two power operational amplifiers, according to the test conditions in the datasheet of the real amplifier, as a result of the simulation study for each of the output voltages a THD was equal to 3.9%. According to the datasheet, the THD was up to 10%.

Figure 11.

Simulated results and datasheet parameters for non-linear distortion versus frequency of the input signal: (a) at a load resistance equal to 2 Ω; (b) at a load resistance equal to 4 Ω.

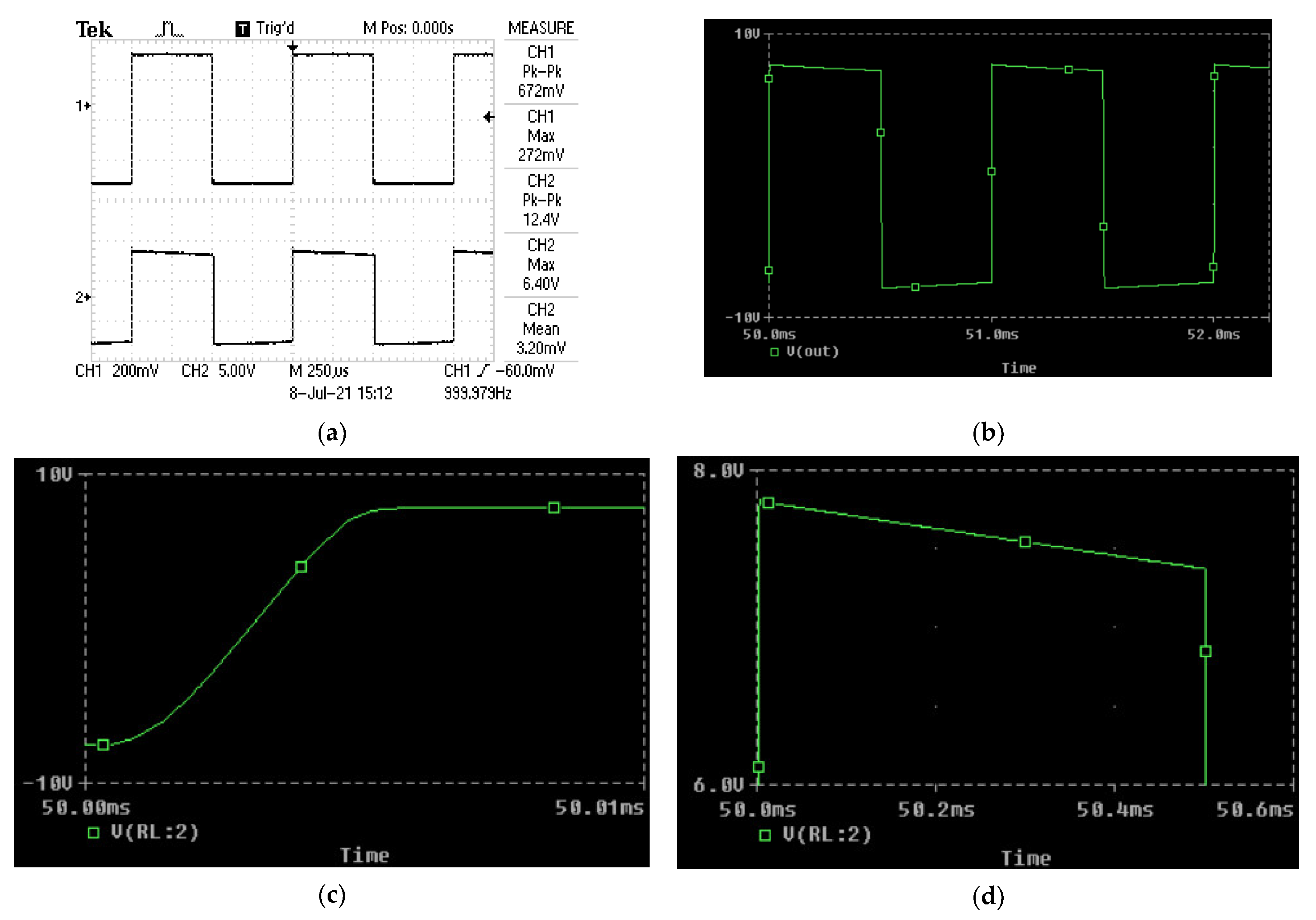

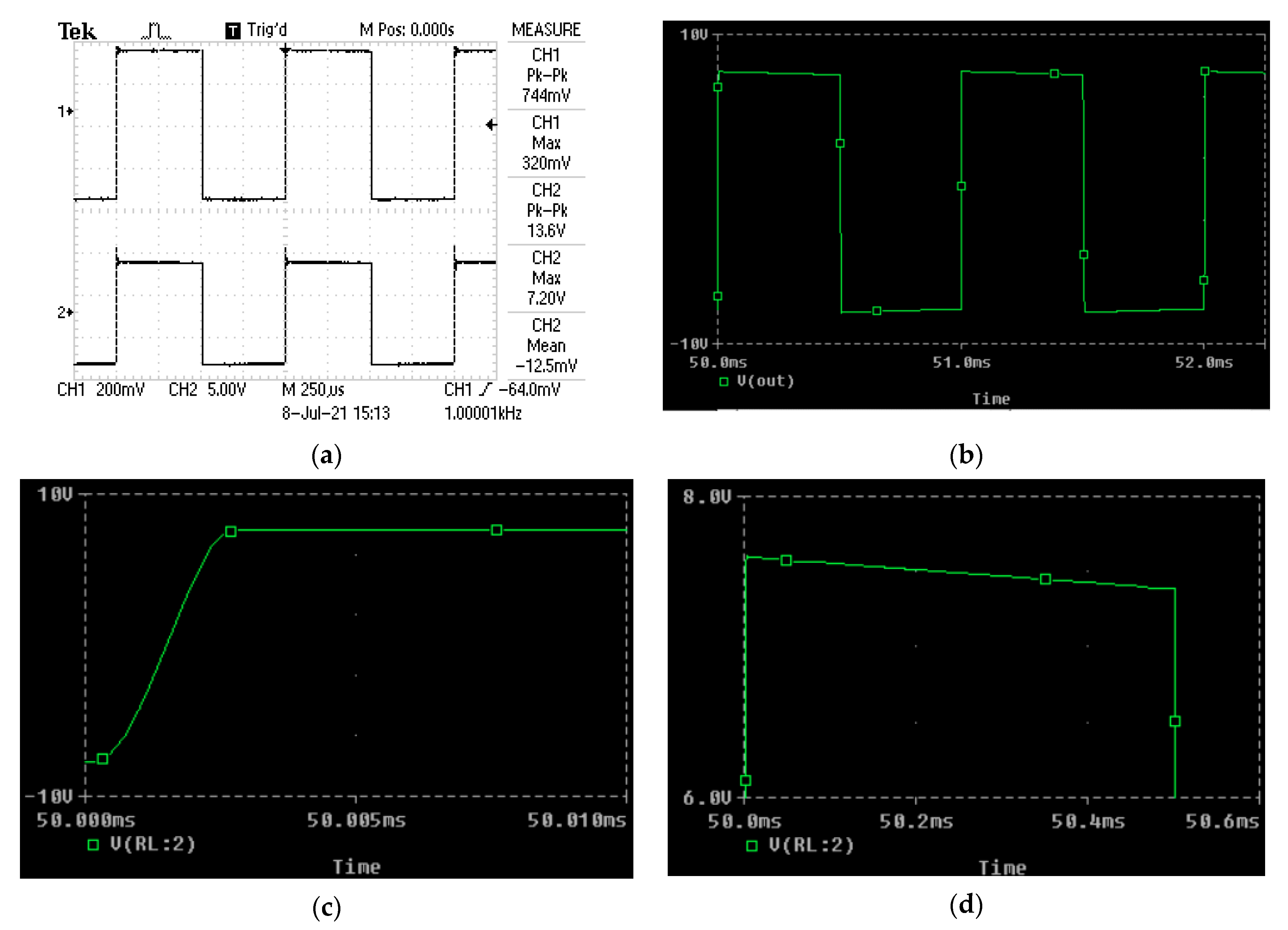

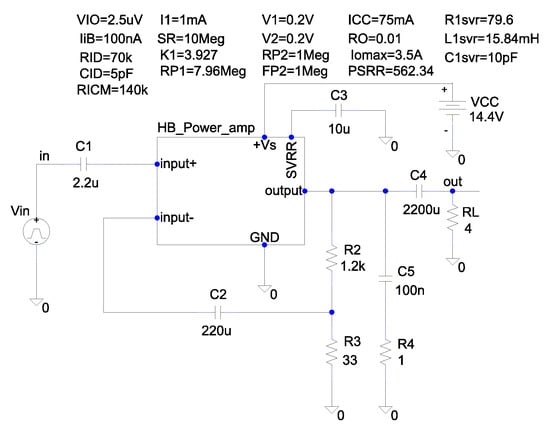

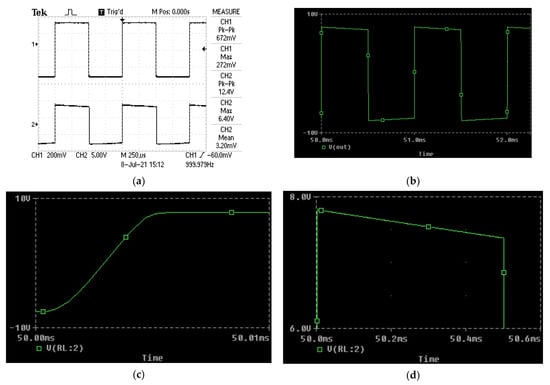

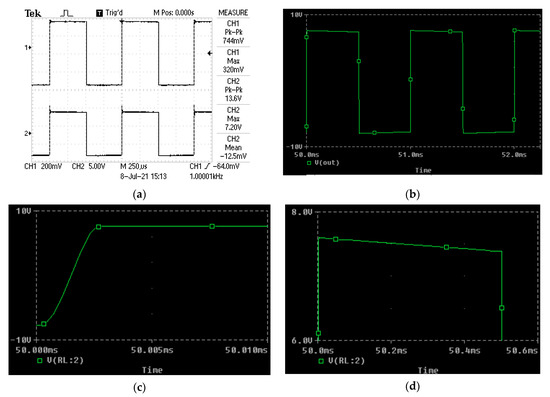

To obtain large-signal transient responses for the various load resistances the test circuit, given in Figure 12 is used. For this purpose, a signal with a pulse form of the voltage and amplitude at which a maximum swing of the output voltage is obtained was applied to the input terminals of the circuit. For the purpose of the simulation study, a transient analysis with a final time of 100 ms (frequency of the input signal 1 kHz and duty cycle 0.5) was set, and the print step and the step celling had the same values equal to 0.1 μs. For the transient response, the simulation and the experimental results of the output signal at RL = 4 Ω ± 5%, and 8 Ω ± 5%, are plotted in Figure 13 and Figure 14. The output signal, obtained from the simulation study, was reported from the beginning of the time moment equal to 50 ms, because due to the influence of the coupling capacitors in the circuit there was a transient process of obtaining the steady-state value of the output voltage’s amplitude. The measured values were — (Figure 13a) and — (Figure 14a), respectively and the corresponding simulated value for the slew rates were at (Figure 13b) and at (Figure 14b), respectively. The simulated results for the positive slew rate at both external load resistances are given in Figure 13c and Figure 14c, respectively. The relative error between the simulation results of the slew rates and the measured values was below 5%. The voltage drop () in the flat region of the output pulse was due to the influence of the coupling capacitors in the input and output network of the circuit, and the value of the load. As can be seen, for a load resistance of , the voltage drop had a smaller value. At the simulated value of the voltage drop was equal to 5.41% (Figure 13d) and the measured value was 4.95%. For , the simulated value was 2.72% (Figure 14d) and the measured value was 2.25%. The maximum value of the relative error was up to 10%, that is acceptable comparing with the manufacturing tolerances, especially for the commercially available coupling capacitors.

Figure 12.

Test circuit for simulation of the large-signal transient response.

Figure 13.

Large-signal transient response for the non-inverting amplifier in Figure 12: (a) measured results of the real device at a load resistance equal to 4 Ω; (b) simulated results of the proposed macro-model at a load resistance equal to 4 Ω; (c) simulated results for the positive slew rate of the macro-model at load 4 Ω; (d) simulated results for the voltage drop of the part of the output signal at 4 Ω.

Figure 14.

Large-signal transient response for the non-inverting amplifier in Figure 12: (a) measured results of the real device at a load resistance equal to 8 Ω; (b) simulated results of the proposed macro-model at a load resistance equal to 8 Ω; (c) simulated results for the positive slew rate at 8 Ω; (d) simulated results for the voltage drop of the part of the output signal at 8 Ω.

Table 3 presents a comparison of the created model with known models of various types of operational amplifiers. As can be seen, all models and macro-models simulate the basic DC and AC parameters, for small signal operation and in most of them at dual power supply voltage from symmetrical external voltage source. When working with high output current and voltage, and single-supply voltage, for some of the macro-models [7,9] are added external stages and function blocks allowing modeling of nonlinear distortions and the floating ground at the single-supply voltage without simulating simultaneous effects at large-signal on the operational amplifiers.

Table 3.

Comparison with other simulation models.

4. Conclusions

An electrical macro-model for monolithic power amplifiers was developed, implemented, and verified. The proposed model is intended for the PSpice-based simulation platform. The proposed model showed a good agreement between the simulation and the experimental testing, and the relative error for the basic static and dynamic small-signal parameters was below 10%. The maximum value of the relative error for the energy efficiency at a large signal was up to 15% (for supply voltages between 8 and 12 V) and below 10% at Vs > 12 V, which guarantees a sufficient degree of accuracy, considering the technological tolerances of the electrical parameters of the components and some variations of the power supply voltage. Further, the also takes into account the internal floating ground with midpoint, offset drift as a result of the power supply ripples, dynamic behavior of the supply current, nonlinear distortion, and internal voltage- and current- limiting networks. This makes the developed model especially useful for analog single-supply processing circuit design at a block level, as thereby to use for predicting and optimize the values of the passive components for the performance of the functional blocks; for instance, to define and analyze the energy parameters, according to the power dissipation.

One possible direction for future work of the author is to develop a behavioral model by using VHDL-AMS or Verilog-A languages. As a result, the created models will allow describing the structure of the model with a smaller number of passive elements and con-trolled sources, as well as a smaller number of nodes. For example, one possible advantage of using VHDL-AMS is that the complete set of equations, that represent the behavior of the real device, can be implemented by combining behavioral elements and structural description as a net-list. By using this technique, the obtained behavioral models can have better convergence during the computation process, especially to simulate the transient responses at a large signal.

Funding

This research received no external funding.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Some or all data, model generated, or used during the study are available in a repository or online.

Conflicts of Interest

The author declare no conflict of interest.

References

- Boyle, G.R.; Pederson, D.O.; Cohn, B.M.; Solomon, J.E. Macromodeling of integrated circuit operational amplifiers. IEEE J. Solid-State Circuits 1971, 9, 353–364. [Google Scholar] [CrossRef]

- Aleksander, M.; Bowers, D. SPICE-compatible op amp Macro-Models. Analog Dev., AN-138. 1990. Available online: https://www.analog.com/media/en/technical-documentation/application-notes/AN-138.pdf (accessed on 9 July 2021).

- Feijes, J.H.A.; Hogervorst, R.; Huijsing, J.H. Macromodelling operational amplifiers. In Proceedings of the IEEE International Symposium on Circuits and Systems—ISCAS ’94, London, UK, 30 May–2 June 1994. [Google Scholar]

- Maxim, A.; Andreu, D. A unified high accuracy behavioral SPICE macromodel of operational amplifiers featuring the frequency, temperature and power supply influences and the Monte Carlo simulation. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Geneva, Switzerland, 28–31 May 2000. [Google Scholar]

- Luo, R.; Yang, H.; Shen, Y.; Wang, H. A macromodel for operational amplifiers with adjustable offset voltage. In Proceedings of the IEEE 2002 International Conference on Communications, Circuits and Systems and West Sino Expositions, Chengdu, China, 29 June–1 July 2002. [Google Scholar]

- AN-840 Development of an Extensive SPICE Macromodel for “Current-Feedback” Amplifiers; SNOA247B; Texas Instruments: Dallas, TX, USA, 2013; Available online: https://www.ti.com (accessed on 9 July 2021).

- Oyama, T.; Hiroki, A.; Sano, T. Macromodeling of operational amplifiers for sound effect circuit design. In Proceedings of the 2014 IEEE International Meeting for Future of Electron Devices, Kansai, Kyoto, Japan, 19–20 June 2014. [Google Scholar] [CrossRef]

- Sanchez-Lopez, C.; Carrasco-Aguilar, M.A.; Morales-Lopez, F.E.; Ochoa-Montiel, R.; Ilhuicatzi-Roldan, R. Spice-compatible nonlinear Op Amp and CFOA macro-models. In Proceedings of the 2014 IEEE Central America and Panama Convention, Panama City, Panama, 12–14 November 2014. [Google Scholar] [CrossRef]

- Yamatoya, Y.; Hiroki, A.; Oda, H. Macromodeling of operational amplifiers for overdrive circuit design. In Proceedings of the 2015 IEEE International Meeting for Future of Electron Devices, Kansai, Kyoto, Japan, 4–5 June 2015. [Google Scholar] [CrossRef]

- Pandiev, I. Development of PSpice Macromodel for Monolithic Single-Supply Power Amplifiers. In Proceedings of the 28th International Conference on Mixed Design of Integrated Circuits and Systems—MIXDES 2021, Wroclaw, Poland, 24–26 June 2021. [Google Scholar]

- Gray, P.R. A 15-W monolithic power operational amplifier. IEEE J. Solid-State Circuits 1972, 7, 474–480. [Google Scholar] [CrossRef]

- Long, F. A dual monolithic power operational amplifier. In Proceedings of the IEEE International Solid-State Circuits Conference, Philadelphia, PA, USA, 14–16 February 1973. [Google Scholar] [CrossRef]

- Widlar, R.J.; Yamatake, M. A monolithic power op amp. IEEE J. Solid-State Circuits 1988, 23, 527–535. [Google Scholar] [CrossRef] [Green Version]

- Automotive Audio Power Amplifiers; STMicroelectronics: Geneva, Switzerland, 2021; Available online: https://www.st.com/en/automotive-infotainment-and-telematics/automotive-audio-power-amplifiers.html (accessed on 7 July 2021).

- Seifart, M. Endstufen (Leistungsstufen) in Analoge Schaltungen, 6th ed.; Verlag Technik: Berlin, Germany, 2003; Chapter 7; pp. 170–210. [Google Scholar]

- Siegl, J. Linearverstärker in Schaltungstechnik—Analog und Gemischt Analog/Digital, 2nd ed.; Springer: Berlin/Heidelberg, Germany, 2005; Chapter 4; pp. 223–241. [Google Scholar]

- TDA2005 20 W Bridge/Stereo Amplifier for Car Radio—Datasheet; STMicroelectronics: Geneva, Switzerland, 2013; Available online: https://www.st.com/content/st_com/en/products/automotive-infotainment-and-telematics/automotive-audio-power-amplifiers/automotive-class-ab-audio-power-amplifiers/tda2005.html (accessed on 7 July 2021).

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).