DC-Link Capacitor Diagnosis in a Single-Phase Grid-Connected PV System

Abstract

:1. Introduction

2. Electrolytic Capacitor Modeling

- is the ideal capacitance.

- is the parallel resistance, which represents all the losses in the dielectric and the leakage between the two electrodes.

- is the connection and electrode serial resistance.

- is the connection and winding equivalent series inductance.

- D diode represents the rectifying property of the oxide dielectric, which is similar to the PN junction in semiconductor devices.

- is the inherent dielectric absorption.

- is the dielectric loss due to dielectric absorption and molecular polarization.

Capacitor Parameters Estimation Methods

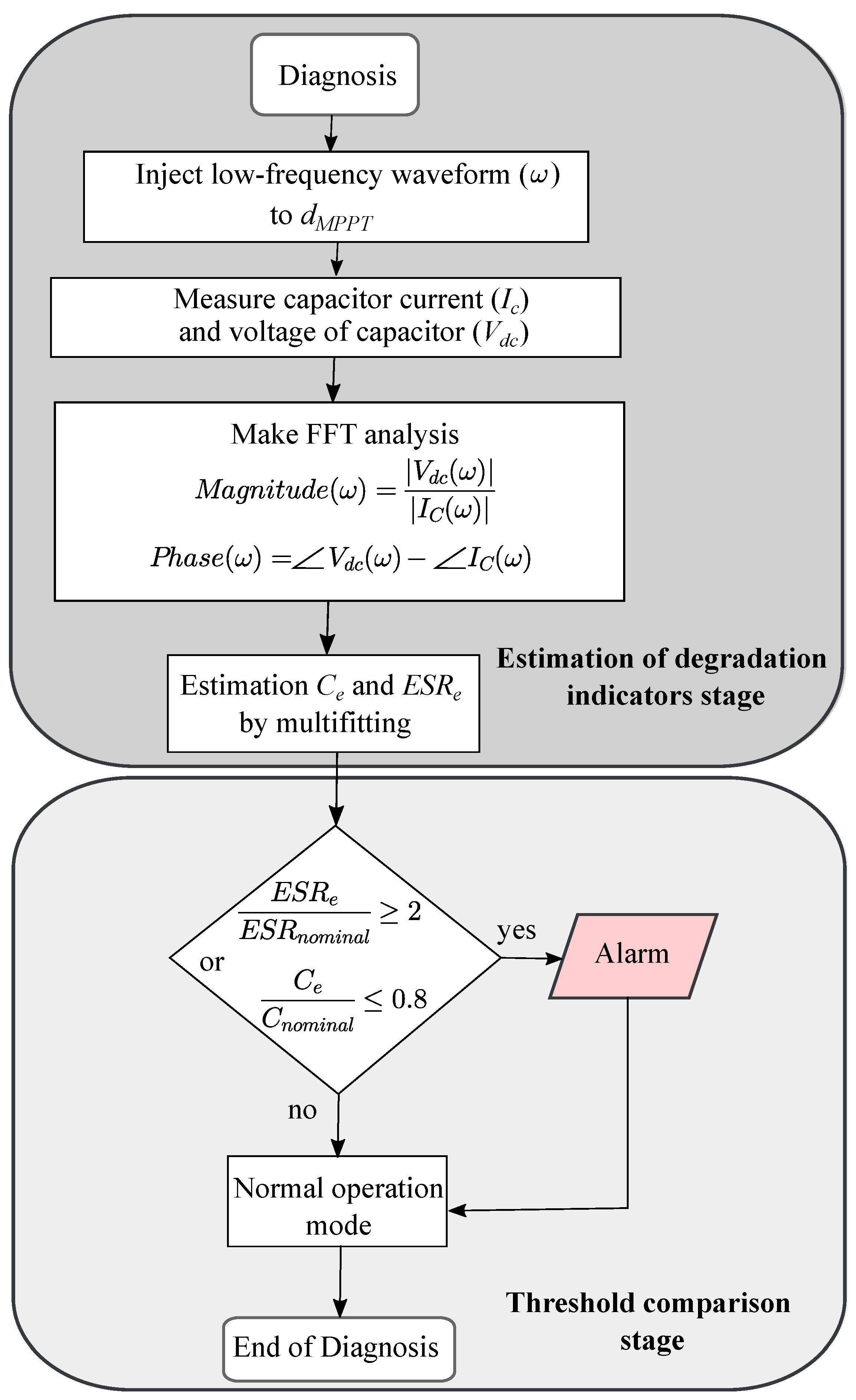

3. DC Link Capacitor Diagnosis by Means of Electrochemical Impedance Spectroscopy (EIS) and Data Multi-Fitting

- is the duty cycle of the MPPT control.

- is the perturbation amplitude.

- is the low-frequency component.

4. Validation and Implementation Issues

4.1. System Description and Parameters Configuration

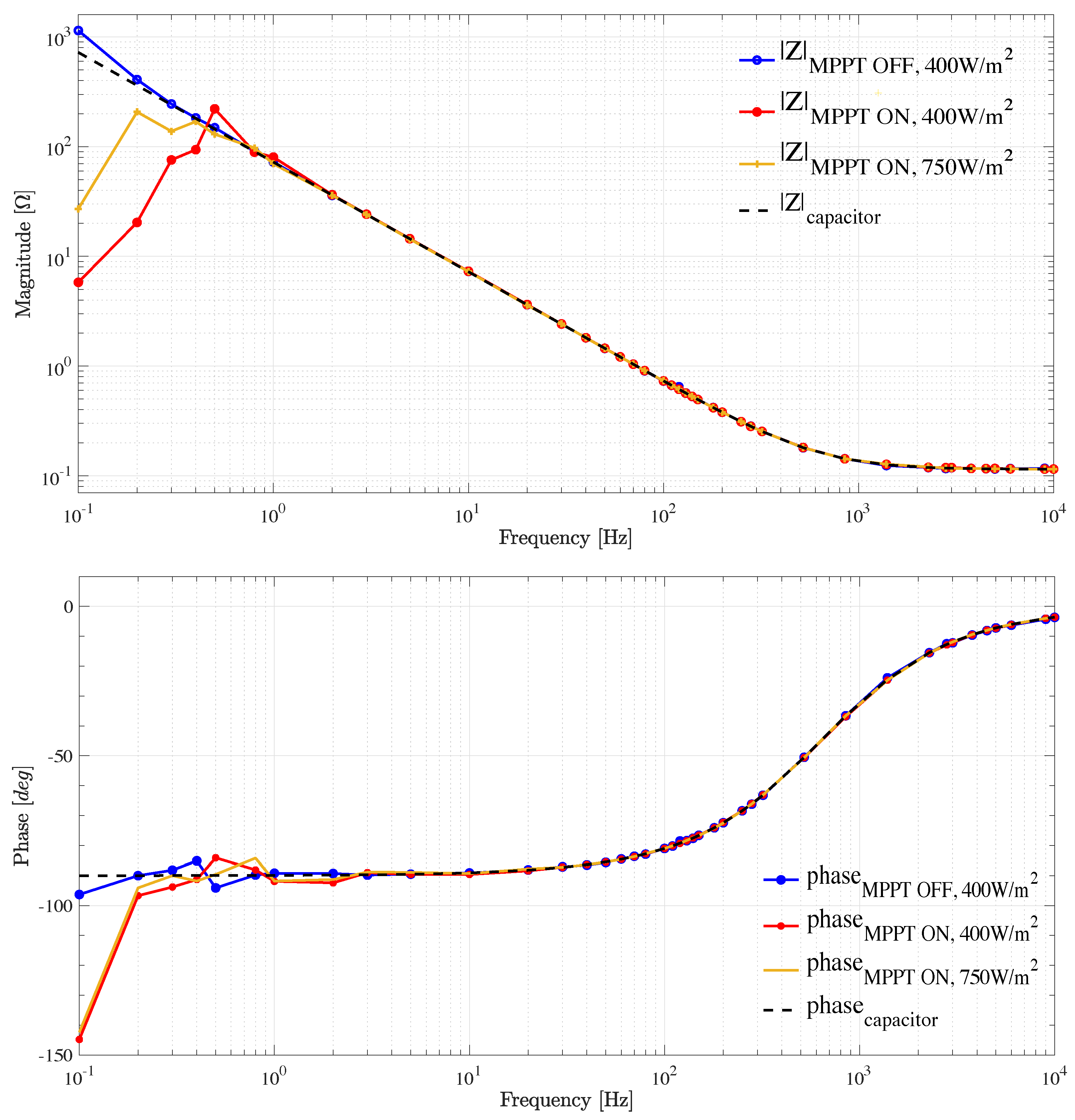

- From t = 0 s to t = 0.5 s, the duty-cycle of the boost converter was fixed at D = 0.4. In order to ensure a stable state of DC-link, the MPPT algorithm was disabled.

- At t = 0.5 s, MPPT was enabled. The MPPT algorithm varies the duty-cycle to extract maximum power. The PV array output power was 694 W at 400 W/m2 and 25 °C. It observed the regulation of DC-link voltage.

- At 2.5 s, the irradiance was changed to 750 W/m2, and the temperature remained at 25 °C. The power developed by the system was increased to 1312 W. The DC-link voltage and the duty-cycle, which are controlled by the MPPT algorithm, were subjected to a transient.

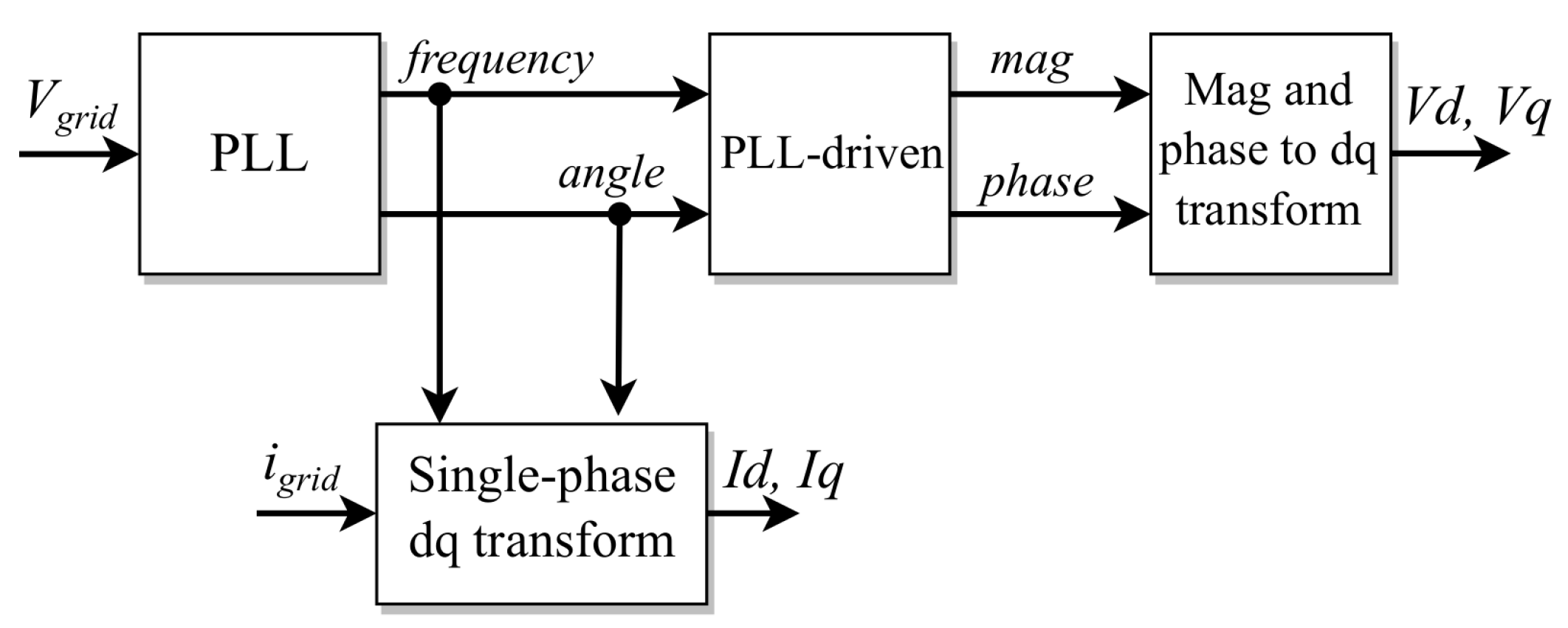

4.2. Injection of Sweep-Frequency into PWM of Boost Converter to Develop the EIS Test

4.3. Multiple Curve Fitting Algorithm to Determine C and ESR

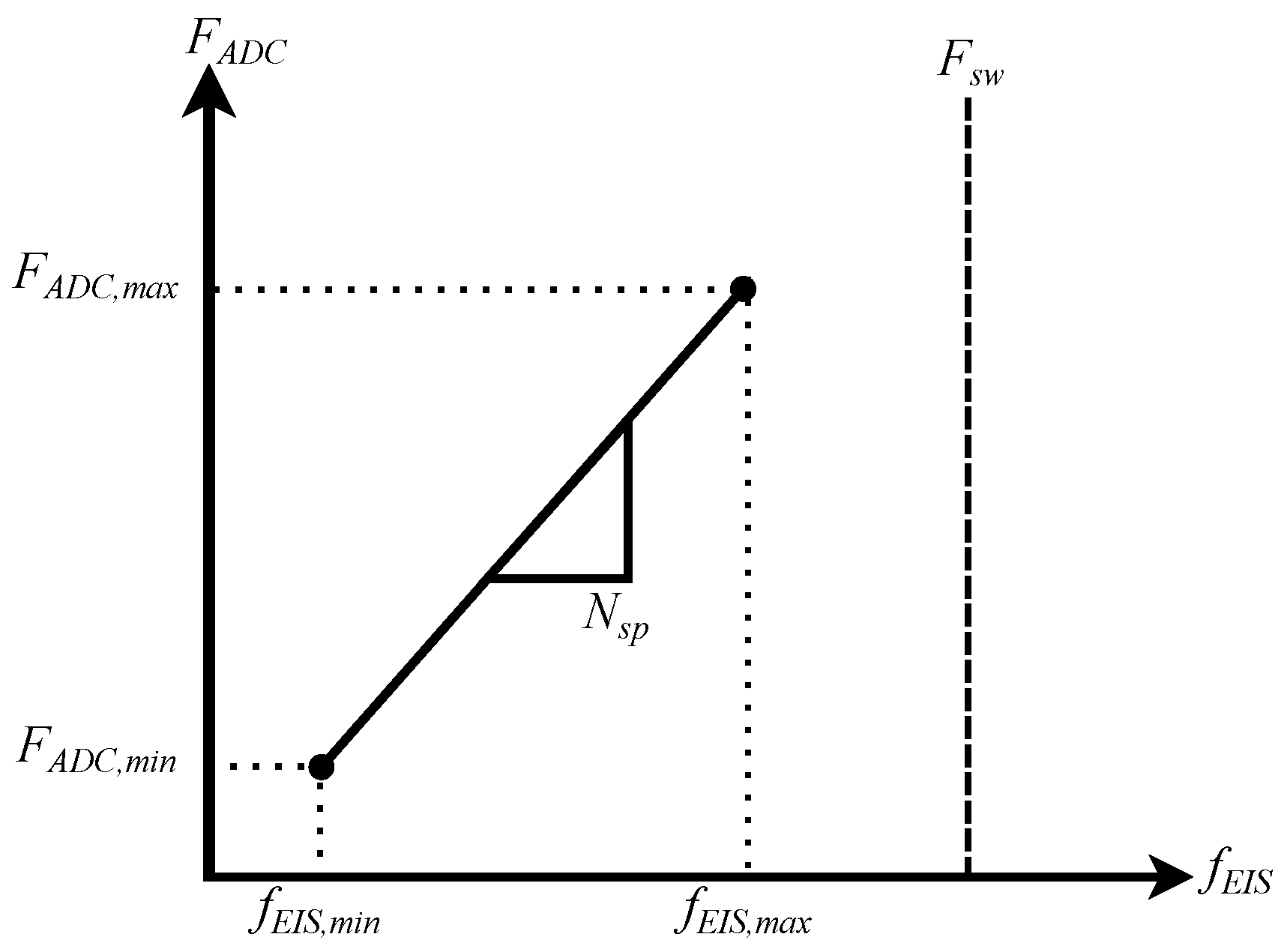

4.4. Hardware Requirements for Implementing the EIS Method

- First step: to define the number of samples .

- Second step: to establish the range limited by the switching frequency , the ADC capabilities, and the samples per period .

- Third step: to define the number of periods to be acquired.

- Fourth step: using the previous results, to verify that the range, the , and the are within the ADC range.

5. Discussion

5.1. Analysis of Estimation Errors of C and ESR Indicators by Using the EIS Approach

5.2. Analysis of Measurement Requirements

5.3. Analysis of Signal Processors to Develop the FFT

5.4. Comparison of the Proposed EIS Technique with Online Diagnostic Methods Proposed in the Literature

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| ADC | Analog–digital converter |

| DSP | Digital signal processor |

| EIS | Electrochemical impedance spectroscopy |

| ESR | Equivalent series resistance |

| ADC frequency | |

| Perturbation frequency | |

| Switching frequency | |

| FFT | Fast-Fourier transform |

| MSE | Mean square error |

| Number of samples | |

| Number of periods | |

| Samples per period | |

| PV | Photovoltaic |

References

- Qaedi, R.; Samet, H. Evaluation of Various Fault Detection Methods in non-Isolated Single Switch DC-DC Converters. In Proceedings of the 2018 IEEE International Conference on Environment and Electrical Engineering and 2018 IEEE Industrial and Commercial Power Systems Europe (EEEIC/I&CPS Europe), Palermo, Italy, 12–15 June 2018; pp. 1–5. [Google Scholar] [CrossRef]

- Gupta, A.; Yadav, O.P.; DeVoto, D.; Major, J. A Review of Degradation Behavior and Modeling of Capacitors. In Proceedings of the ASME 2018 International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems, Taipei, Taiwan, 24–26 October 2018. [Google Scholar] [CrossRef] [Green Version]

- Soliman, H.; Wang, H.; Blaabjerg, F. A Review of the Condition Monitoring of Capacitors in Power Electronic Converters. IEEE Trans. Ind. Appl. 2016, 52, 4976–4989. [Google Scholar] [CrossRef]

- Wang, H.; Blaabjerg, F. Reliability of Capacitors for DC-Link Applications in Power Electronic Converters—An Overview. IEEE Trans. Ind. Appl. 2014, 50, 3569–3578. [Google Scholar] [CrossRef] [Green Version]

- Jano, R.; Pitica, D. Accelerated ageing tests for predicting capacitor lifetimes. In Proceedings of the 2011 IEEE 17th International Symposium for Design and Technology in Electronic Packaging (SIITME), Timisoara, Romania, 20–23 October 2011; pp. 63–68. [Google Scholar] [CrossRef]

- Zhao, Z.; Davari, P.; Lu, W.; Wang, H.; Blaabjerg, F. An Overview of Condition Monitoring Techniques for Capacitors in DC-Link Applications. IEEE Trans. Power Electron. 2021, 36, 3692–3716. [Google Scholar] [CrossRef]

- Lipnicki, P.; Lewandowski, D.; Orkisz, M.; Tresch, A. The effect of change in DC link series resistance on the AC/AC converter operation: Power converters embedded diagnostics. In Proceedings of the 2013 IEEE 1st International Conference on Condition Assessment Techniques in Electrical Systems (CATCON), Kolkata, India, 6–8 December 2013; pp. 122–127. [Google Scholar] [CrossRef]

- Wang, H.; Nielsen, D.A.; Blaabjerg, F. Degradation testing and failure analysis of DC film capacitors under high humidity conditions. Microelectron. Reliab. 2015, 55, 2007–2011. [Google Scholar] [CrossRef]

- Ren, L.; Gong, C.; Zhao, Y. An Online ESR Estimation Method for Output Capacitor of Boost Converter. IEEE Trans. Power Electron. 2019, 34, 10153–10165. [Google Scholar] [CrossRef]

- Farjah, E.; Givi, H.; Ghanbari, T. Application of an Efficient Rogowski Coil Sensor for Switch Fault Diagnosis and Capacitor ESR Monitoring in Nonisolated Single-Switch DC–DC Converters. IEEE Trans. Power Electron. 2017, 32, 1442–1456. [Google Scholar] [CrossRef]

- Kai, Y.; Wenbin, H.; Weijie, T.; Jianguo, L.; Jingcheng, C. A novel online ESR and C identification method for output capacitor of buck converter. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; Volume 2, pp. 3476–3482. [Google Scholar] [CrossRef]

- Yao, K.; Tang, W.; Bi, X.; Lyu, J. An Online Monitoring Scheme of DC-Link Capacitor’s ESR and C for a Boost PFC Converter. IEEE Trans. Power Electron. 2016, 31, 5944–5951. [Google Scholar] [CrossRef]

- Sun, Q.; Wang, Y.; Jiang, Y.; Wu, Y. On-line component-level soft fault diagnostics for power converters. In Proceedings of the 2016 Prognostics and System Health Management Conference (PHM-Chengdu), Chengdu, China, 19–21 October 2016; pp. 1–5. [Google Scholar] [CrossRef]

- Meng, J.; Chen, E.X.; Ge, S.J. Online E-Cap Condition Monitoring Method Based on State Observer. In Proceedings of the 2018 IEEE International Power Electronics and Application Conference and Exposition (PEAC), Shenzhen, China, 4–7 November 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Ertasgin, G.; Whaley, D.M.; Ertugrul, N.; Soong, W.L. Analysis of DC Link Energy Storage for Single-Phase Grid-Connected PV Inverters. Electronics 2019, 8, 601. [Google Scholar] [CrossRef] [Green Version]

- Hannonen, J.; Honkanen, J.; Ström, J.P.; Korhonen, J.; Silventoinen, P.; Räisänen, S. Capacitance measurement method using sinusoidal voltage injection in isolating phase-shifted full-bridge DC–DC converter output stage. IET Power Electron. 2016, 9, 2543–2550. [Google Scholar] [CrossRef]

- Pu, X.S.; Nguyen, T.H.; Lee, D.C.; Lee, K.B.; Kim, J.M. Fault Diagnosis of DC-Link Capacitors in Three-Phase AC/DC PWM Converters by Online Estimation of Equivalent Series Resistance. IEEE Trans. Ind. Electron. 2013, 60, 4118–4127. [Google Scholar] [CrossRef]

- Agarwal, N.; Ahmad, M.W.; Anand, S. Condition monitoring of dc-link capacitor utilizing zero state of solar PV H5 inverter. In Proceedings of the 2016 10th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), Bydgoszcz, Poland, 29 June–1 July 2016; pp. 174–179. [Google Scholar] [CrossRef]

- Arya, A.; Ahmad, M.W.; Agarwal, N.; Anand, S. Capacitor impedance estimation utilizing dc-link voltage oscillations in single phase inverter. IET Power Electron. 2017, 10, 1046–1053. [Google Scholar] [CrossRef]

- Gupta, Y.; Ahmad, M.W.; Narale, S.; Anand, S. Health Estimation of Individual Capacitors in a Bank With Reduced Sensor Requirements. IEEE Trans. Ind. Electron. 2019, 66, 7250–7259. [Google Scholar] [CrossRef]

- Miao, W.; Lam, K.H.; Pong, P.W.T. Online Monitoring of Aluminum Electrolytic Capacitors in Photovoltaic Systems by Magnetoresistive Sensors. IEEE Sens. J. 2020, 20, 767–777. [Google Scholar] [CrossRef]

- Ahmad, M.W.; Agarwal, N.; Kumar, P.N.; Anand, S. Low-Frequency Impedance Monitoring and Corresponding Failure Criteria for Aluminum Electrolytic Capacitors. IEEE Trans. Ind. Electron. 2017, 64, 5657–5666. [Google Scholar] [CrossRef]

- Aeloiza, E.; Jang-Hwan, K.; Enjeti, P.; Ruminot, P. A Real Time Method to Estimate Electrolytic Capacitor Condition in PWM Adjustable Speed Drives and Uninterruptible Power Supplies. In Proceedings of the IEEE 36th Conference on Power Electronics Specialists, Dresden, Germany, 16 June 2005; pp. 2867–2872. [Google Scholar] [CrossRef]

- Wang, G.; Guan, Y.; Zhang, J.; Wu, L.; Zheng, X.; Pan, W. ESR estimation method for DC-DC converters based on improved EMD algorithm. In Proceedings of the IEEE 2012 Prognostics and System Health Management Conference (PHM-2012 Beijing), Beijing, China, 23–25 May 2012; pp. 1–6. [Google Scholar] [CrossRef]

- Yu, Y.; Zhou, T.; Zhu, M.; Xu, D. Fault Diagnosis and Life Prediction of DC-link Aluminum Electrolytic Capacitors Used in Three-phase AC/DC/AC Converters. In Proceedings of the 2012 Second International Conference on Instrumentation, Measurement, Computer, Communication and Control, Harbin, China, 8–10 December 2012; pp. 825–830. [Google Scholar] [CrossRef]

- Dubilier, C. Aluminum Electrolytic Capacitor Application Guide; Technical Report 864; Cornell Dubilier: South Plainfield, NJ, USA, 2011. [Google Scholar]

- Czarkowski, D. DC-DC Converters. In Power Electronics Handbook, 4th ed.; Rashid, M.H., Ed.; Elsevier: Amsterdam, The Netherlands, 2018; Chapter DC-DC Conv; pp. 275–288. [Google Scholar] [CrossRef]

- Abdennadher, K.; Venet, P.; Rojat, G.; Retif, J.M.; Rosset, C. A Real-Time Predictive-Maintenance System of Aluminum Electrolytic Capacitors Used in Uninterrupted Power Supplies. IEEE Trans. Ind. Appl. 2010, 46, 1644–1652. [Google Scholar] [CrossRef] [Green Version]

- Vogelsberger, M.A.; Wiesinger, T.; Ertl, H. Life-Cycle Monitoring and Voltage-Managing Unit for DC-Link Electrolytic Capacitors in PWM Converters. IEEE Trans. Power Electron. 2011, 26, 493–503. [Google Scholar] [CrossRef]

- Venet, P.; Perisse, F.; El-Husseini, M.; Rojat, G. Realization of a smart electrolytic capacitor circuit. IEEE Ind. Appl. Mag. 2002, 8, 16–20. [Google Scholar] [CrossRef]

- Lasia, A. Electrochemical Impedance Spectroscopy and its Applications; Springer: New York, NY, USA, 2014. [Google Scholar] [CrossRef]

- Varnosfaderani, M.A.; Strickland, D. Online Electrochemical Impedance Spectroscopy (EIS) estimation of a solar panel. Vacuum 2017, 139, 185–195. [Google Scholar] [CrossRef] [Green Version]

- Femia, N.; Petrone, G.; Spagnuolo, G.; Vitelli, M. Optimization of Perturb and Observe Maximum Power Point Tracking Method. IEEE Trans. Power Electron. 2005, 20, 963–973. [Google Scholar] [CrossRef]

- Abo-Khalil, A.; Lee, D.-C. DC-Link Capacitance Estimation in AC/DC/AC PWM Converters Using Voltage Injection. IEEE Trans. Ind. Appl. 2008, 44, 1631–1637. [Google Scholar] [CrossRef]

- Chen. Multiple Curve Fitting with Common Parameters Using NLINFIT. Available online: https://www.mathworks.com/matlab-central/fileexchange/40613-multiple-curve-fitting-with-common-parameters-using-nlinfit (accessed on 7 July 2020).

- United Chemi-Con, I. U36D Series Capacitor. Available online: https://www.micro-semiconductor.com/datasheet/de-E36D750HPN682QA79M.pdf (accessed on 7 October 2020).

- Texas Instruments. Using DSPLIB FFT Implementation for Real Input and Without Data Scaling; Technical Report; Texas Instruments: Dallas, TX, USA, 2019. [Google Scholar]

- Roh, J.C.; Aridhi, S. Optimizing Modern Radar Systems Using Low-Latency, High-Performance FFT Coprocessors; Texas Instruments: Dallas, TX, USA, 2016. [Google Scholar]

- Petrone, G.; Zamboni, W.; Spagnuolo, G.; Dessi, R. EIS Method for the On-Board Evaluation of the Fuel Cell Impedance. In Proceedings of the 2018 IEEE 4th International Forum on Research and Technology for Society and Industry (RTSI), Palermo, Italy, 10–13 September 2018; pp. 1–6. [Google Scholar] [CrossRef]

- LEM International SA. Voltage Transducer LV 25-P. Available online: https://www.lem.com/en/lv-25p (accessed on 5 February 2019).

- Allegro MicroSystems. ACS37002 High Accuracy Current Sensor. Available online: https://www.allegromicro.com/en/product-s/sense/current-sensor-ics/zero-to-fifty-amp-integrated-conductor-sensor-ics/acs37002 (accessed on 2 October 2021).

- STMicroelectronics. Library 62- Fast Fourier Transform (FFT) for STM32F4xx. Available online: www.ST.com (accessed on 2 October 2021).

- Silicon Labs. CMSIS DSP Software Library. Available online: https://docs.silabs.com/cmsis/latest/dsp/api-index (accessed on 2 October 2021).

- STMicroelectronics. Digital Signal Processing for STM32 Microcontrollers Using CMSIS. Available online: https://www.st.com/co-ntent/ccc/resource/technical/document/application_note/group0/c1/ee/18/7a/f9/45/45/3b/DM00273990/files/DM002739-90.pdf/jcr:content/translations/en.DM00273990.pdf (accessed on 2 October 2021).

| Reference Number | {C, ESR} Estimation Error | Comments |

|---|---|---|

| [16] | C: 2.5–4% | Technique customized for a phase-shift full-bridge DC–DC converter. |

| [17] | ESR: 3.2% | Needs the injection of a current stimulus. Operates in no-load condition. |

| [18] | C: 1.5% | Technique customized for the H5 inverter. |

| [19] | Z: 17.2% | Does not provide C and ESR separate estimations. |

| [20] | ESR: 2.14% C: 0.19%. | Requires LCR meter to provide initial values of C and ESR of each capacitor of a bank. |

| Parameter | Variable | Value | Units |

|---|---|---|---|

| Switching frequency of boost | 20 | kHz | |

| Carrier frequency of inverter | Fc | 3780 | Hz |

| Inductor | L | 5 | mH |

| Output capacitor | C | 2200 | F |

| Equivalent series resistor | 114.5 | m | |

| Input capacitor | 100 | F | |

| Resistor of inductance (LCL filter) | 8.23 | m | |

| Inductor (LCL filter) | 2.18 | mH | |

| Resistor of capacitance (LCL filter) | 2.193 | ||

| Capacitor (LCL filter) | 24 | F |

| Nominal | Degraded | |||||

|---|---|---|---|---|---|---|

| ESReN (mΩ) | CeN (μF) | MSEN | ESReD (mΩ) | CeD (μF) | MSED | |

| MPPT OFF, 400 W/m2 | 114.07 ± 0.719 | 2188 ± 10.99 | 1.030 | 228.78 ± 0.709 | 1759 ± 4.69 | 1.028 |

| MPPT ON, 400 W/m2 | 114.80 ± 0.767 | 2183 ± 11.64 | 1.0301 | 228.76 ± 1.25 | 1758 ± 8.28 | 1.0281 |

| MPPT ON, 750 W/m2 | 114.66 ± 0.036 | 2201 ± 5.57 | 1.0308 | 228.96 ± 1.20 | 1757 ± 7.97 | 1.030 |

| Expected Values | 114.5 | 2200 | 229 | 1760 | ||

| Parameter | Type or Value |

|---|---|

| Method | NonLinearLeastSquares |

| Weight function for robust fitting | Bisquare |

| DeviStep | |

| MaxIter | 200 |

| TolFun | |

| TolX |

| FADC,max = 144 kHz | FADC,min = 0.039 kHz | |

|---|---|---|

| Nsp | fEIS,max | fEIS,min |

| 8 | 18,000 | 4.87 |

| 16 | 9000 | 2.43 |

| 32 | 4500 | 1.21 |

| 64 | 2250 | 0.60 |

| 128 | 1125 | 0.30 |

| 256 | 562.5 | 0.15 |

| 512 | 281.2 | 0.076 |

| Nsp = 8 | Nsp = 64 | Nsp = 128 | ||

|---|---|---|---|---|

| NFFT | Np | Tw,max [s] | ||

| 1024 | 128 | 16 | 8 | 26.25 |

| 2048 | 256 | 32 | 16 | 52.51 |

| 4096 | 512 | 64 | 32 | 105.02 |

| 8192 | 1024 | 128 | 64 | 210.05 |

| Parameters | Value or Range |

|---|---|

| Samples per period and | |

| {8, 64, 128} | |

| {1024, 2048, 4096, 8192} | |

| Frequency range | |

| range | Hz for Hz for |

| Hz for Hz for Hz for | |

| total range | {80 Hz to 128 kHz} |

| 1024 | 2048 | 4096 | 8192 | ||

| 128 | 256 | 512 | 1024 | ||

| ESR | 2.98 | 1.65 | 1.92 | 1.13 | |

| C | 5.13 | 9.18 | 10.18 | 10.04 | |

| 16 | 32 | 64 | 128 | ||

| ESR | 24.52 | 3.49 | 3.49 | 1.05 | |

| C | 30.31 | 0.18 | 0.50 | 5.18 | |

| 8 | 16 | 32 | 64 | ||

| ESR | 20.32 | 15.80 | 6.46 | 5.58 | |

| C | 26.40 | 19.09 | 10.68 | 10.36 |

| 1024 | 2048 | 4096 | 8192 | ||

| 128 | 256 | 512 | 1024 | ||

| ESR | 6.15 | 5.81 | 2.53 | 2.80 | |

| C | 9.77 | 9.24 | 6.39 | 7.60 | |

| 16 | 32 | 64 | 128 | ||

| ESR | 21.28 | 3.93 | 0.53 | 2.29 | |

| C | 19.86 | 3.99 | 0.37 | 2.39 | |

| 8 | 16 | 32 | 64 | ||

| ESR | 3.78 | 11.01 | 4.42 | 2.37 | |

| C | 2.32 | 11.72 | 3.88 | 0.11 |

| Reference Number | Number and Type of Sensors | Signal Processor | Fundamental Strategy | Type of Processing Algorithm |

|---|---|---|---|---|

| [16] | Two current sensors and one voltage sensor, unspecified reference. | DSP, unspecified reference | Perturbing capacitor voltage reference at 50 Hz | None. Estimation of C based on measurements and analytical expression. |

| [17] | Three current sensors LA-25 NP and one voltage sensor LV-25 NP. | DSP TMS320VC33 | Perturbing AC current reference at 30 Hz | Estimation of ESR by RLS method |

| [18] | One current and one voltage sensors, unspecified reference. | Unspecified reference | Estimation of capacitor current and measuring voltage variation in zero state of transistor. | None. Estimation of C by analytical expression |

| [19] | Two current sensors LA-25P and one voltage sensor, unspecified reference. | DSP TMS320F2808 | Extracted the second harmonic ripple of current, and voltage appeared in DC-link capacitor. | None. Estimation of Z by reconstructing capacitor current and measuring capacitor voltage |

| [20] | Two current sensors and one voltage sensor, unspecified reference. | DSP TMS320F2808 | Estimation of current capacitor during switching period, and temperature estimation. | Estimate C and ESR, in a PoF model, by LMS and extended Kalman filter |

| Proposed method | One current sensor ACS37002 and one voltage sensor LV25-P. | ARM-microcontroller STM32f427VGT6 | Perturbing PWM signal by sweep frequency | Estimation of C and ESR by Multifitting |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Plazas-Rosas, R.A.; Orozco-Gutierrez, M.L.; Spagnuolo, G.; Franco-Mejía, É.; Petrone, G. DC-Link Capacitor Diagnosis in a Single-Phase Grid-Connected PV System. Energies 2021, 14, 6754. https://doi.org/10.3390/en14206754

Plazas-Rosas RA, Orozco-Gutierrez ML, Spagnuolo G, Franco-Mejía É, Petrone G. DC-Link Capacitor Diagnosis in a Single-Phase Grid-Connected PV System. Energies. 2021; 14(20):6754. https://doi.org/10.3390/en14206754

Chicago/Turabian StylePlazas-Rosas, Ramiro Alejandro, Martha Lucia Orozco-Gutierrez, Giovanni Spagnuolo, Édinson Franco-Mejía, and Giovanni Petrone. 2021. "DC-Link Capacitor Diagnosis in a Single-Phase Grid-Connected PV System" Energies 14, no. 20: 6754. https://doi.org/10.3390/en14206754

APA StylePlazas-Rosas, R. A., Orozco-Gutierrez, M. L., Spagnuolo, G., Franco-Mejía, É., & Petrone, G. (2021). DC-Link Capacitor Diagnosis in a Single-Phase Grid-Connected PV System. Energies, 14(20), 6754. https://doi.org/10.3390/en14206754