Combined Operation Analysis of a Saturated Iron-Core Superconducting Fault Current Limiter and Circuit Breaker for an HVDC System Protection

Abstract

:1. Introduction

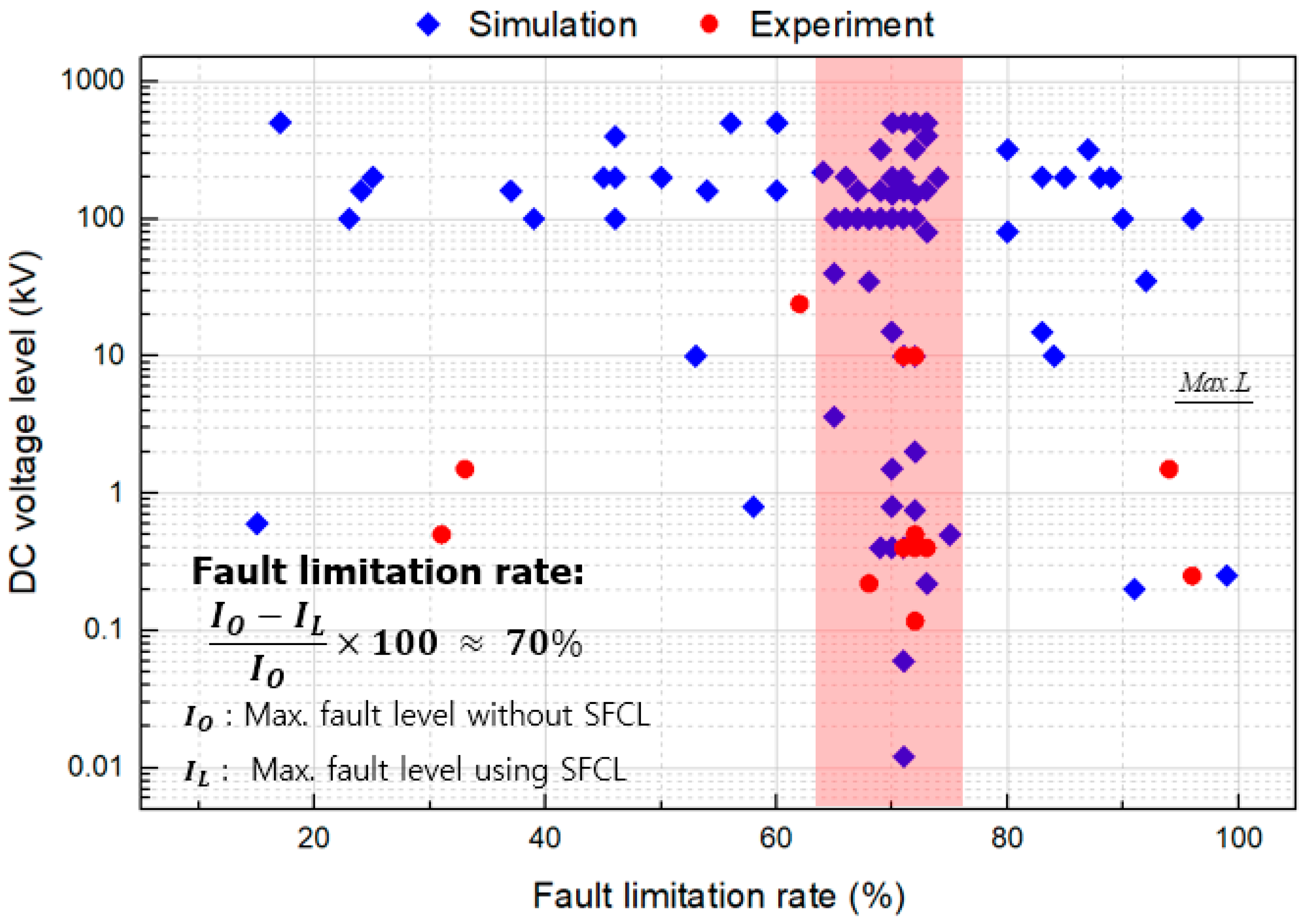

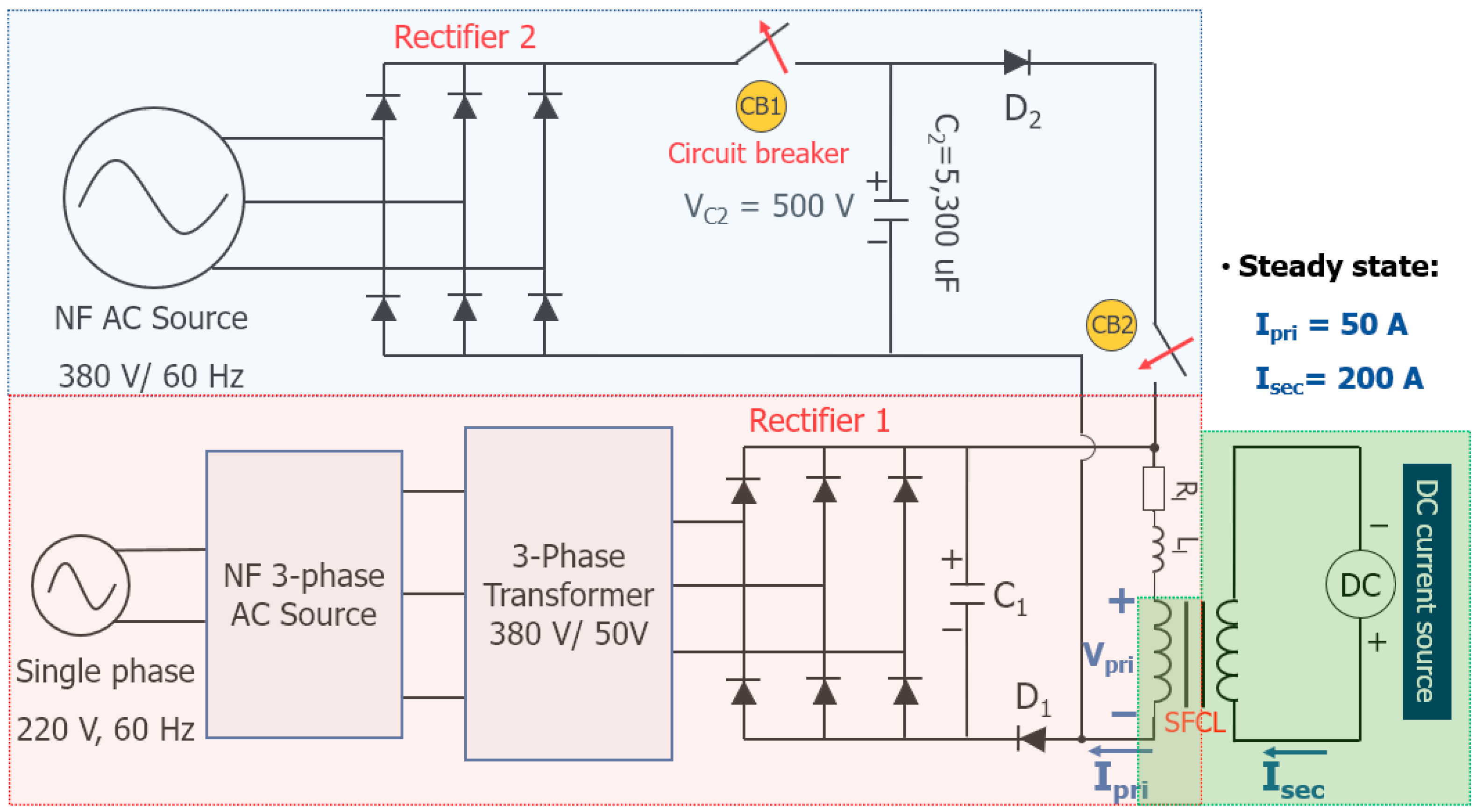

2. Design and Performance Analysis of a Lab-Scale SI-SFCL

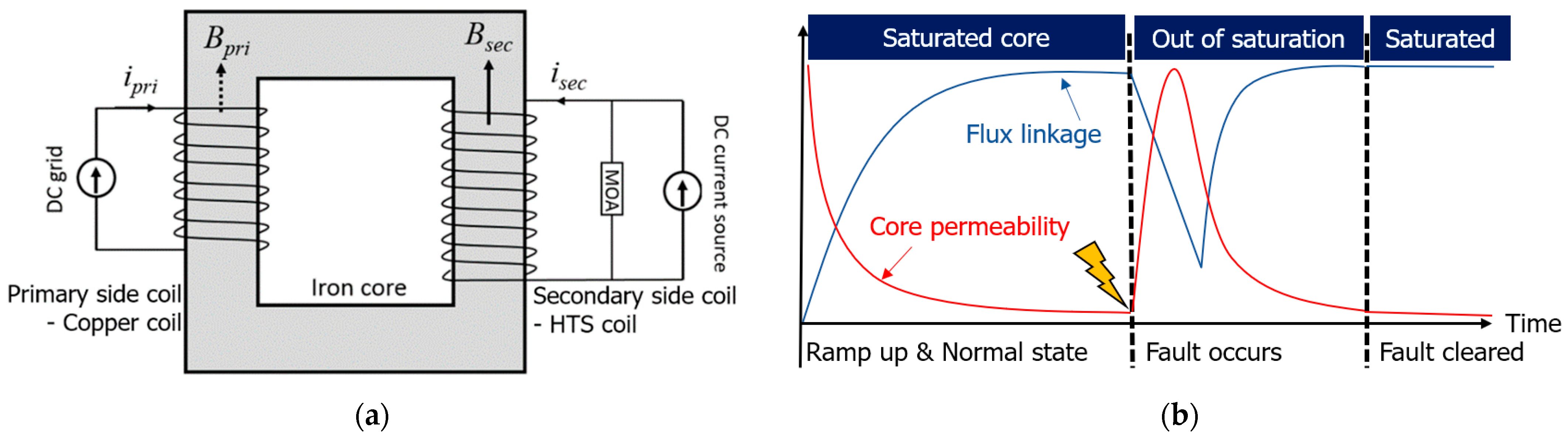

2.1. Operating Principle of the SI-SFCL

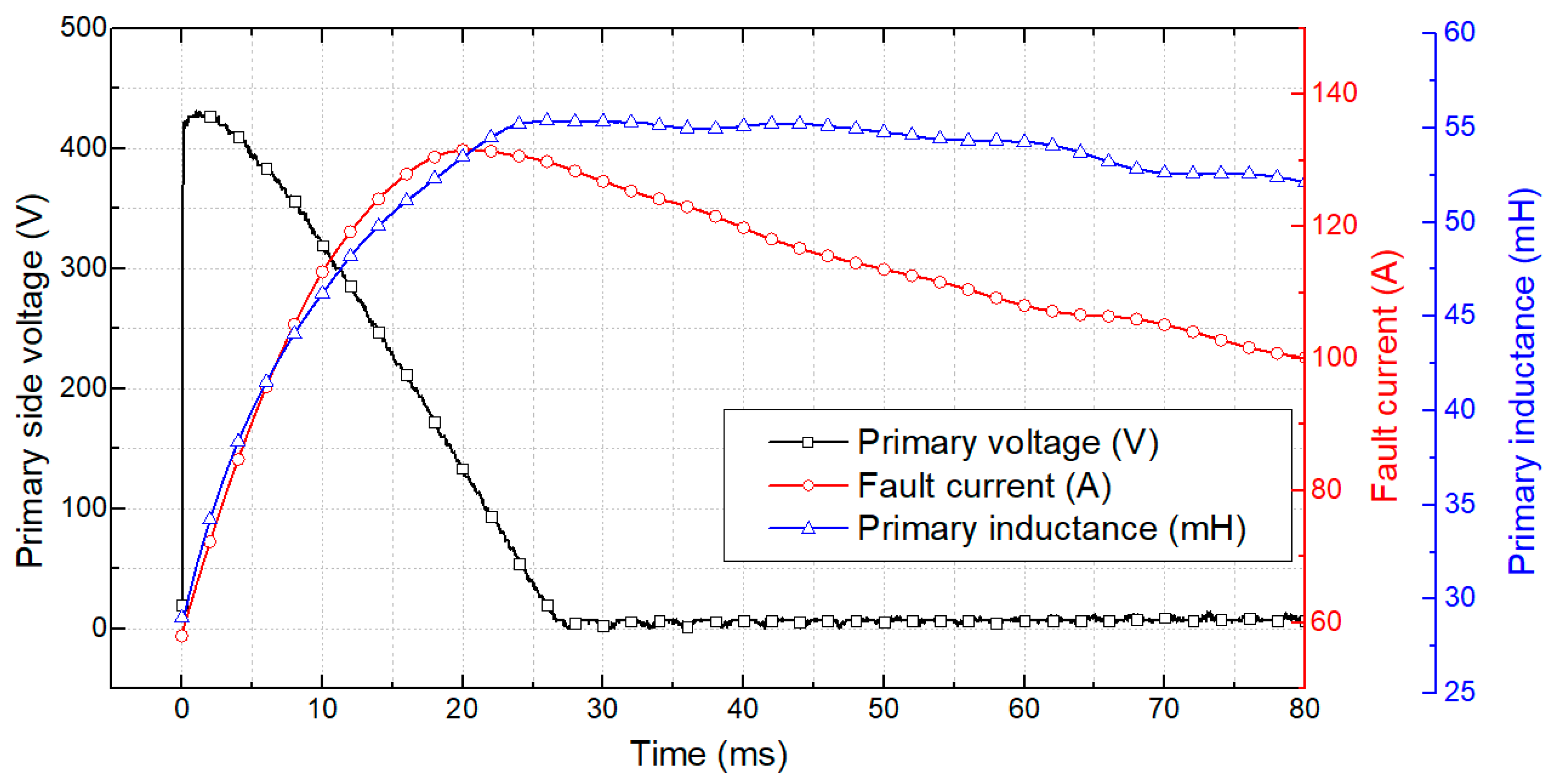

2.2. Nonlinear Dynamic Inductance Measurement Method of SI-SFCL

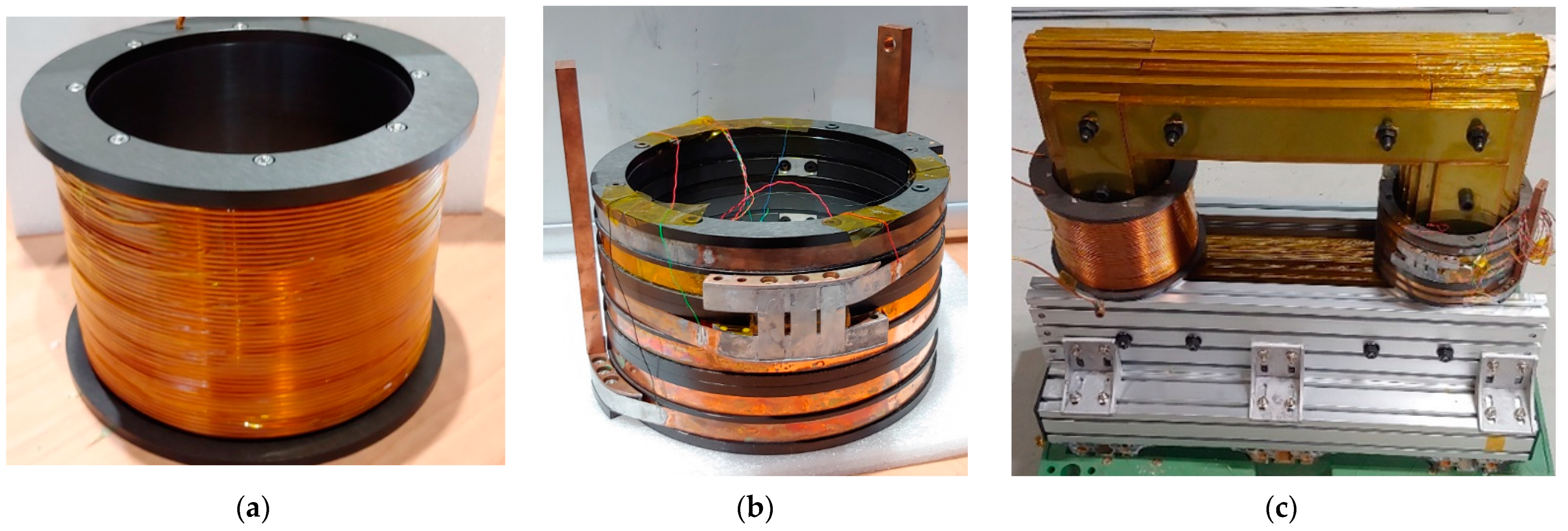

2.3. Design and Fabrication of the Lab-Scale SI-SFCL for DC Power System

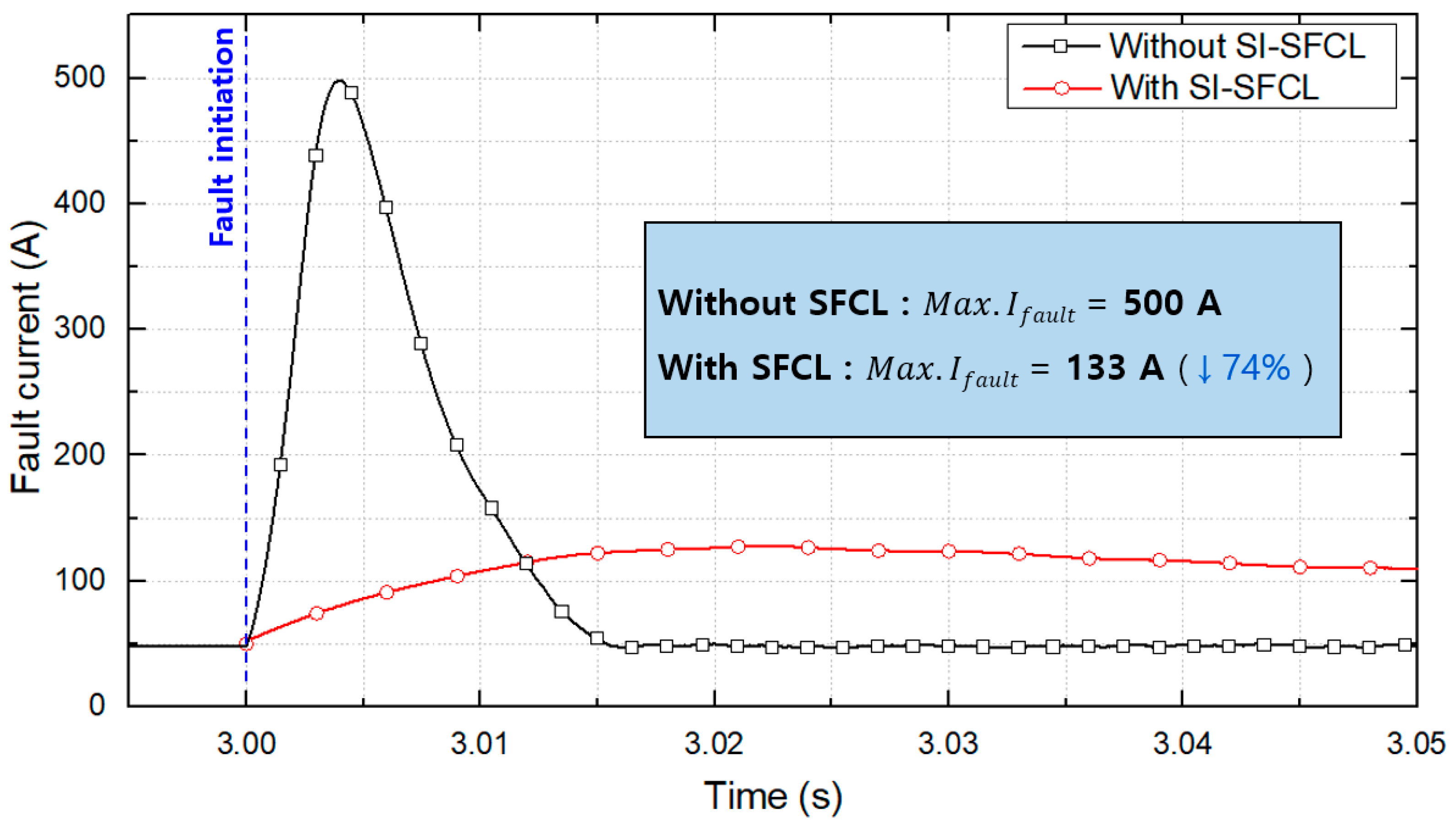

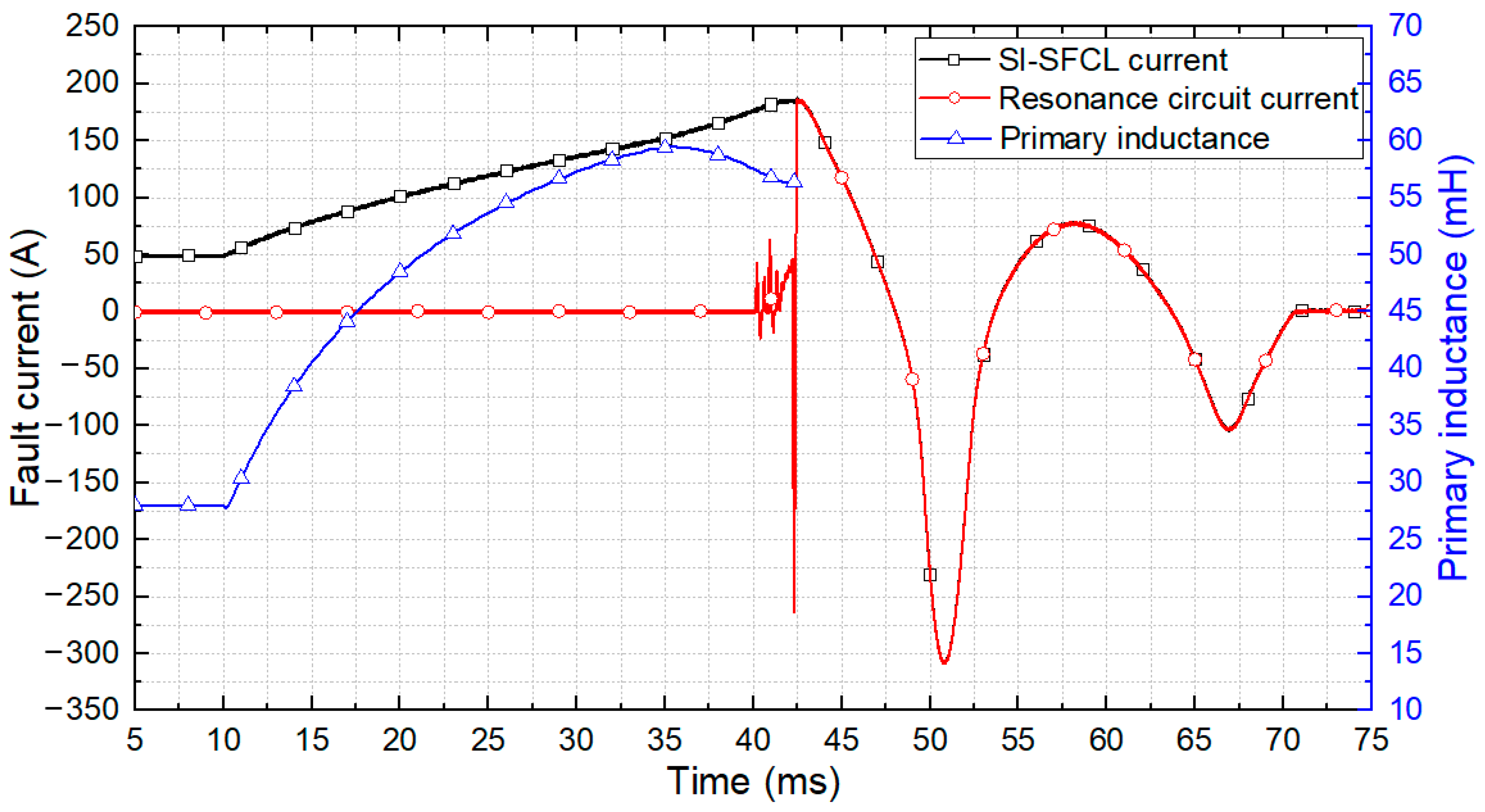

2.4. Independent Performance Test Results of the SI-SFCL

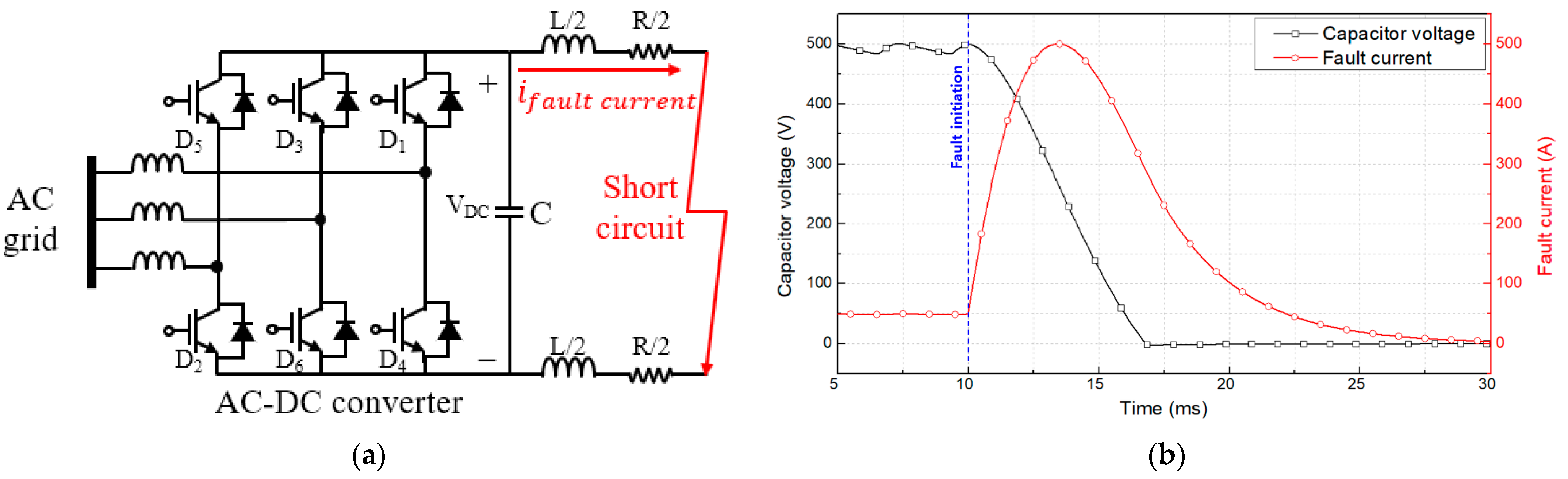

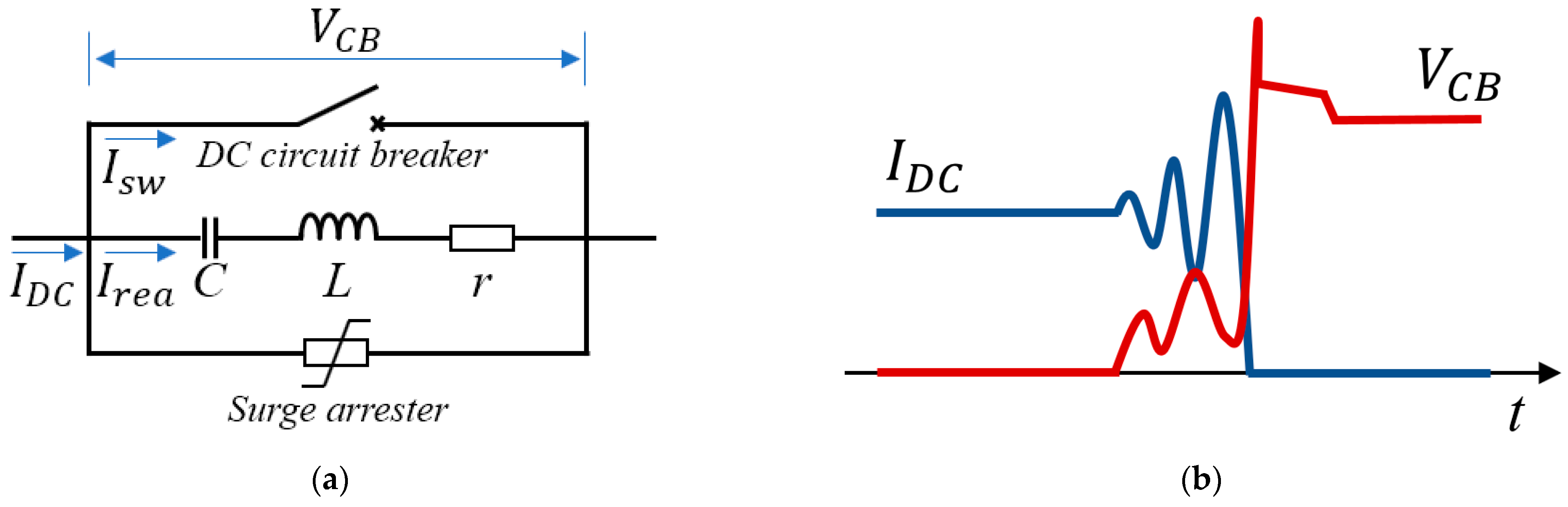

3. Construction and Design of a Mechanical DC Circuit Breaker

4. Construction and Testing of a Protection System Combining a SI-SFCL and a DCCB

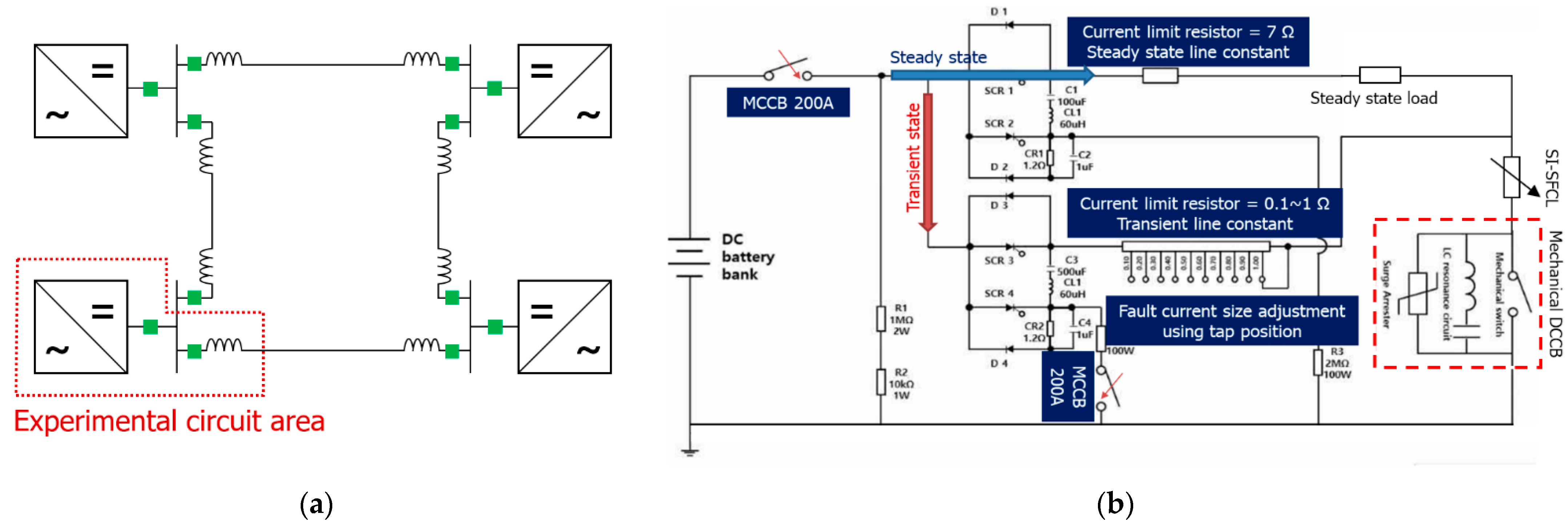

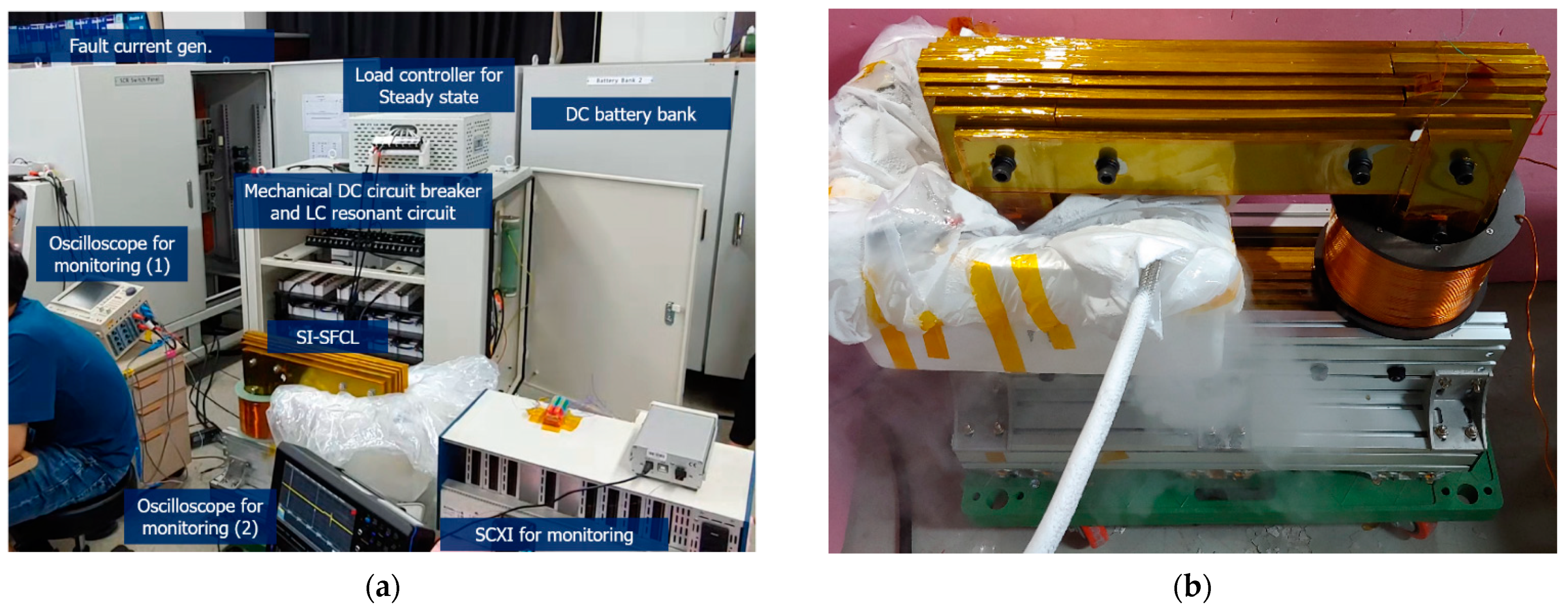

4.1. Experimental Circuit Configuration and the Testing Process

4.2. Experimental Circuit Configuration and the Testing Process

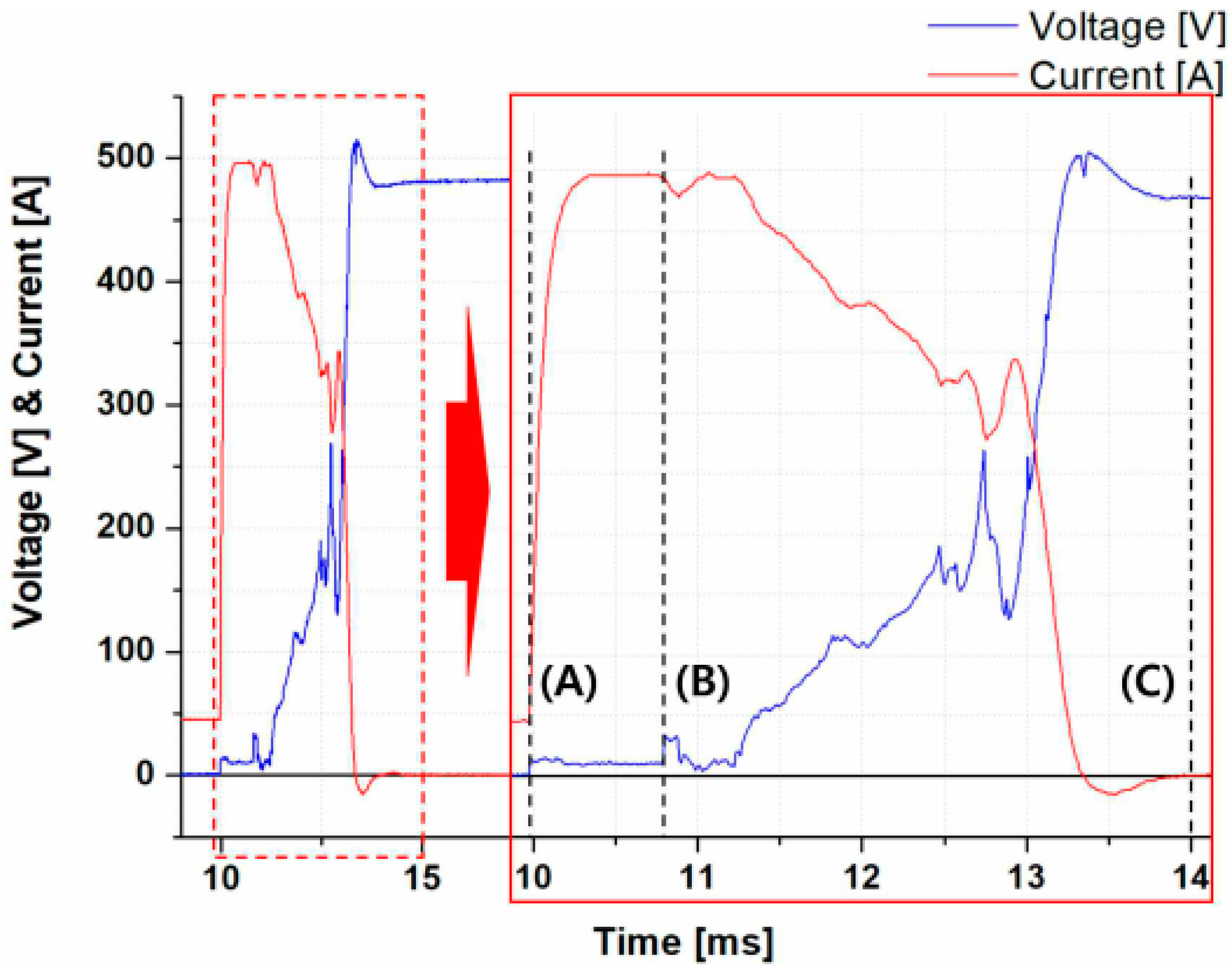

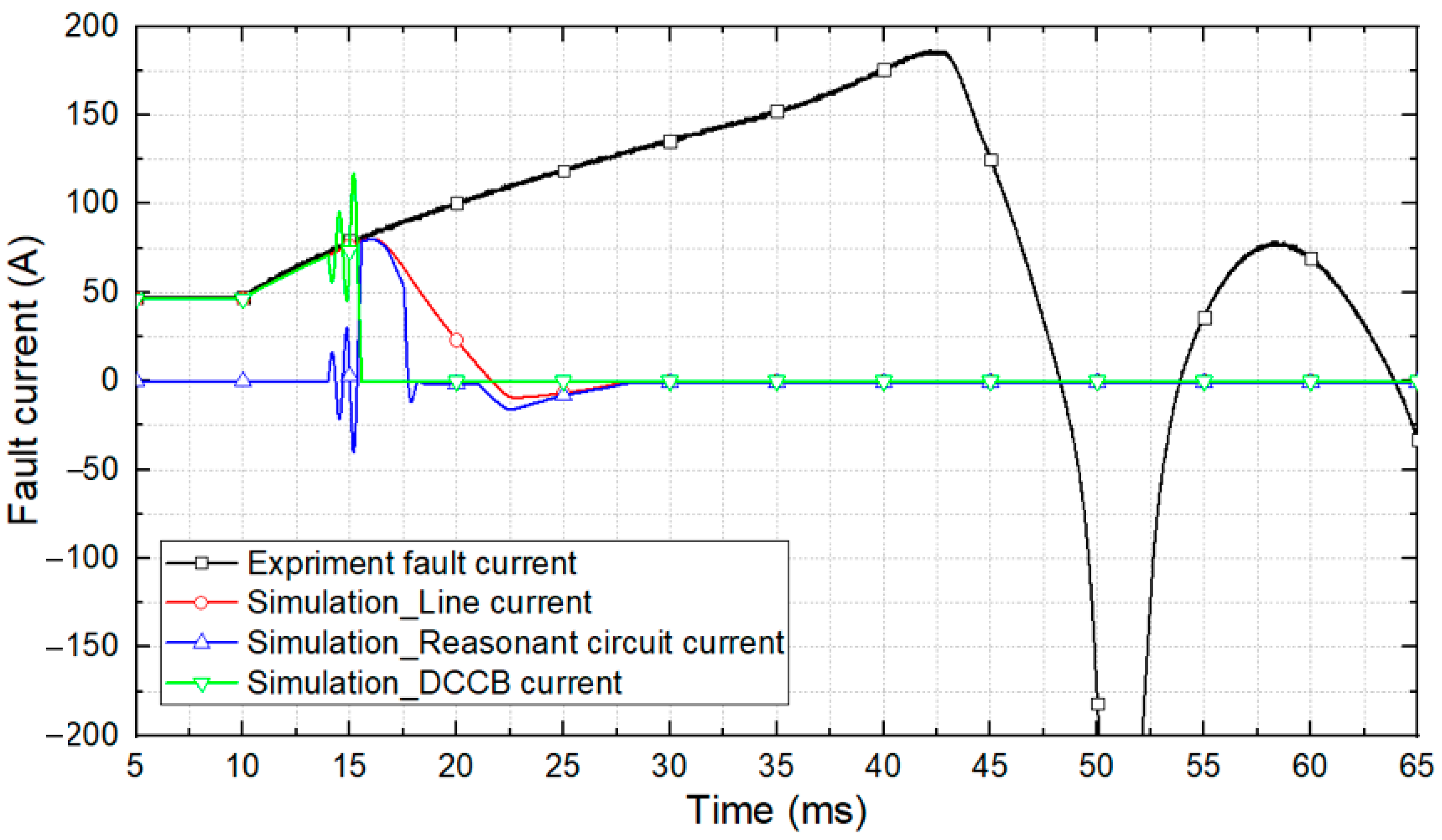

4.3. Experimental Results and Analysis

5. Suggestion of a Fault Current Detection Scheme to Improve the Protection Coordination with a SI-SFCL

- Fast fault detection is required to compensate for the slow operation of the DCCB;

- It should not be affected by the line constant changed by the SI-SFCL operation.

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Alassi, A.; Bañales, S.; Ellabban, O.; Adam, G.; MacIver, C. HVDC transmission: Technology review, market trends and future outlook. Renew. Sustain. Energy Rev. 2019, 112, 530–554. [Google Scholar] [CrossRef]

- Meah, K.; Ula, S. Comparative evaluation of HVDC and HVAC transmission systems. In Proceedings of the 2007 IEEE Power Engineering Society General Meeting, Tampa, FL, USA, 24–28 June 2007; IEEE: Tampa, FL, USA, 2007; pp. 1–5. [Google Scholar]

- Flourentzou, N.; Agelidis, V.G.; Demetriades, G.D. VSC-based HVDC power transmission systems: An overview. IEEE Trans. Power Electron. 2009, 24, 592–602. [Google Scholar] [CrossRef]

- Candelaria, J.; Park, J.D. VSC-HVDC system protection: A review of current methods. In Proceedings of the 2011 IEEE/PES Power Systems Conference and Exposition, Phoenix, AZ, USA, 20–23 March 2011; IEEE: Phoenix, AZ, USA, 2011; pp. 1–7. [Google Scholar]

- Ong, C.M.; Hamzei-Nejad, A. A general-purpose multiterminal DC load-flow. IEEE Trans. Power Appar. Syst. 1981, PAS-100, 3166–3174. [Google Scholar] [CrossRef]

- Fudeh, H.; Ong, C.M. A simple and efficient AC-DC load-flow method for multiterminal DC systems. IEEE Trans. Power Appar. Syst. 1981, PAS-100, 4389–4396. [Google Scholar] [CrossRef]

- Leterme, W.; Van Hertem, D. Classification of Fault Clearing Strategies for HVDC Grids; CIGRE: Lund, Sweden, 2015. [Google Scholar]

- Yang, J.; Fletcher, J.E.; O’Reilly, J. Short-circuit and ground fault analyses and location in VSC-based DC network cables. IEEE Trans. Ind. Electron. 2011, 59, 3827–3837. [Google Scholar] [CrossRef] [Green Version]

- Liu, Z.; Mirhosseini, S.S.; Popov, M.; Audichya, Y.; Colangelo, D.; Jamali, S.; Palensky, P.; Hu, W.; Chen, Z. Protection Testing for Multiterminal High-Voltage dc Grid: Procedures and Procedures and Assessment. IEEE Ind. Electron. Mag. 2020, 14, 46–64. [Google Scholar]

- Tahata, K.; El Oukaili, S.; Kamei, K.; Yoshida, D.; Kono, Y.; Yamamoto, R.; Ito, H. HVDC circuit breakers for HVDC grid applications. In Proceedings of the 11th IET International Conference on AC and DC Power Transmission, Birmingham, UK, 10–12 February 2015; IET: Birmingham, UK, 2015; pp. 1–9. [Google Scholar]

- Mokhberdoran, A.; Carvalho, A.; Leite, H.; Silva, N. A review on HVDC circuit breakers. In Proceedings of the 3rd Renewable Power Generation Conference (RPG 2014), Naples, Italy, 24–25 September 2014; IET: Naples, Italy, 2014; pp. 1–6. [Google Scholar]

- Franck, C.M. HVDC circuit breakers: A review identifying future research needs. IEEE Trans. Power Deliv. 2011, 26, 998–1007. [Google Scholar] [CrossRef] [Green Version]

- Xin, Y.; Gong, W.Z.; Hong, H.; Gao, Y.Q.; Niu1, X.Y.; Zhang, J.Y.; Sun, Y.W.; Ren, A.L.; Wang, H.Z.; Zhang, L.F.; et al. Development of 220 kV/300 MVA superconductive fault current limiter. Supercond. Sci. Technol. 2007, 25, 105011. [Google Scholar] [CrossRef]

- Eckroad, S. Superconducting Power Equipment—Technology Watch; Electric Power Research Institute: Palo Alto, CA, USA, 2012. [Google Scholar]

- Noe, M.; Steurer, M. High-temperature superconductor fault current limiters: Concepts applications and development status. Supercond. Sci. Technol. 2007, 20, R15–R29. [Google Scholar] [CrossRef]

- Kim, H.R.; Yang, S.E.; Yu, S.D.; Kim, H.; Park, B.J.; Han, Y.H.; Yu, J. Development and grid operation of superconducting fault current limiters in KEPCO. IEEE Trans. Appl. Supercond. 2014, 24, 1–4. [Google Scholar]

- Jin, J.X.; Tang, Y.J.; Xiao, X.Y.; Du, B.X.; Wang, Q.L.; Wang, J.H.; Zhu, J.G. HTS power devices and systems: Principles, characteristics, performance, and efficiency. IEEE Trans. Appl. Supercond. 2016, 26, 1–26. [Google Scholar] [CrossRef]

- Chen, L.; Chen, H.; Shu, Z.; Zhang, G.; Xia, T.; Ren, L. Comparison of inductive and resistive SFCL to robustness improvement of a VSC-HVDC system with wind plants against DC fault. IEEE Trans. Appl. Supercond. 2016, 26, 1–8. [Google Scholar] [CrossRef]

- Lee, S.R.; Ko, E.Y.; Lee, J.J.; Dinh, M.C. Development and HIL Testing of a Protection System for the Application of 154-kV SFCL in South Korea. IEEE Trans. Appl. Supercond. 2019, 29, 1–4. [Google Scholar] [CrossRef]

- Barzegar-Bafrooei, M.R.; Foroud, A.A.; Ashkezari, J.D.; Niasati, M. On the advance of SFCL: A comprehensive review. IET Gener. Transm. Distrib. 2019, 13, 3745–3759. [Google Scholar] [CrossRef]

- Yazdani-Asrami, M.; Staines, M.; Sidorov, G.; Davies, M.; Bailey, J.; Allpress, N.; Gholamian, S.A. Fault current limiting HTS transformer with extended fault withstand time. Supercond. Sci. Technol. 2019, 32, 035006. [Google Scholar] [CrossRef]

- Yazdani-Asrami, M.; Staines, M.; Sidorov, G.; Eicher, A. Heat transfer and recovery performance enhancement of metal and superconducting tapes under high current pulses for improving fault current-limiting behavior of HTS transformers. Supercond. Sci. Technol. 2020, 33, 095014. [Google Scholar] [CrossRef]

- Song, W.; Pei, X.; Xi, J.; Zeng, X. A novel helical superconducting fault current limiter for electric propulsion aircraft. IEEE Trans. Transp. Electrif. 2020, 7, 276–286. [Google Scholar] [CrossRef]

- Lee, J.G.; Khan, U.A.; Lee, H.Y.; Lee, B.W. Impact of SFCL on the four types of HVDC circuit breakers by simulation. IEEE Trans. Appl. Supercond. 2016, 26, 1–6. [Google Scholar] [CrossRef]

- Garcia, W.R.L.; Tixador, P.; Raison, B.; Bertinato, A.; Luscan, B.; Creusot, C. Technical and economic analysis of the R-type SFCL for HVDC grids protection. IEEE Trans. Appl. Supercond. 2017, 27, 1–9. [Google Scholar] [CrossRef]

- Jiang, Z.; Yu, Z. Analysis of the MTDC System Protection Strategy based on Resistive DC SFCL. In Proceedings of the 2020 IEEE International Conference on Applied Superconductivity and Electromagnetic Devices (ASEMD), Tianjin, China, 16–18 October 2020; IEEE: Tianjin, China, 2020; pp. 1–2. [Google Scholar]

- Garcia, W.L.; Bertinato, A.; Tixador, P.; Raison, B.; Luscan, B. Full-selective protection strategy for MTDC grids based on R-type superconducting FCLs and mechanical DC circuit breakers. In Proceedings of the 5th IET International Conference on Renewable Power Generation (RPG), London, UK, 21–23 September 2016; IET: London, UK, 2016; pp. 1–7. [Google Scholar]

- Rahman, M.H.; Xu, L.; Yao, L. Protection of large partitioned MTDC networks using DC-DC converters and circuit breakers. Prot. Control. Mod. Power Syst. 2016, 1, 1–9. [Google Scholar] [CrossRef] [Green Version]

- Chang, B.; Cwikowski, O.; Pei, X.; Barnes, M. Impact of fault current limiter on VSC-HVDC dc protection. In Proceedings of the 12th IET International Conference on AC and DC Power Transmission (ACDC 2016), Beijing, China, 28–29 May 2016; pp. 1–6. [Google Scholar]

- Li, B.; Jing, F.; Li, B.; Wen, W. Research on the parameter matching between active SI-SFCL and DC circuit breaker in DC systems. IEEE Trans. Appl. Supercond. 2019, 29, 1–5. [Google Scholar] [CrossRef]

- Li, B.; Jing, F.; Li, B.; Chen, L. Research of the application of active saturated iron-core superconductive fault current limiters in the VSCHVDC system. IEEE Trans. Appl. Supercond. 2018, 28, 5602906. [Google Scholar] [CrossRef]

- Li, B.T.; Jia, J.F.; Li, B.; Zhang, Y.K. Fault analysis of VSC-HVDC system with saturated iron-core superconductive fault current limiter. In Proceedings of the 2015 IEEE International Conference on Applied Superconductivity and Electromagnetic Devices (ASEMD), Shanghai, China, 20–23 November 2015; pp. 388–390. [Google Scholar]

- Li, B.; Jing, F.; Jia, J.; Li, B. Research on Saturated Iron-Core Superconductive Fault Current Limiters Applied in VSC-HVDC Systems. IEEE Trans. Appl. Supercond. 2016, 26, 1–5. [Google Scholar] [CrossRef]

- Grover, F.W. Inductance calculations: Working Formulas and Tables; Courier Corporation: Chelmsford, MA, USA, 2004. [Google Scholar]

- Jovcic, D. High Voltage Direct Current Transmission: Converters, Systems and DC Grids; John Wiley & Sons: Hoboken, NJ, USA, 2019. [Google Scholar]

- Dao, V.Q.; Lee, J.; Kim, C.-S.; Park, M. Conceptual Design of a Saturated Iron-Core Superconducting Fault Current Limiter for a DC Power System. IEEE Trans. Appl. Supercond. 2020, 30, 1–5. [Google Scholar] [CrossRef]

- Dao, V.Q.; Lee, J.I.; Kim, C.S.; Park, M.; Melaccio, U. Design and Performance Analysis of a Saturated Iron-Core Superconducting Fault Current Limiter for DC Power Systems. Energies 2020, 13, 6090. [Google Scholar] [CrossRef]

- Mackey, L.; Rachi, M.R.K.; Peng, C.; Husain, I. Optimization and control of a z-source, ultrafast mechanically switched, high-efficiency dc circuit breaker. IEEE Trans. Ind. Appl. 2020, 56, 2871–2879. [Google Scholar] [CrossRef]

- Corzine, K.A.; Ashton, R.W. A new Z-source DC circuit breaker. IEEE Trans. Power Electron. 2011, 27, 2796–2804. [Google Scholar] [CrossRef]

- Li, Z.; He, Y.; Zhang, T.Q.; Zhang, X.P. Universal Power Flow Algorithm for Bipolar Multi-Terminal VSC-HVDC. Energies 2020, 13, 1053. [Google Scholar] [CrossRef] [Green Version]

- Qi, L.L.; Antoniazzi, A.; Raciti, L.; Leoni, D. Design of solid-state circuit breaker-based protection for DC shipboard power systems. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 5, 260–268. [Google Scholar] [CrossRef]

- Psaras, V.; Emhemed, A.; Adam, G.; Burt, G. Review and evaluation of the state of the art of DC fault detection for HVDC grids. In Proceedings of the 2018 53rd International Universities Power Engineering Conference (UPEC), Glasgow, UK, 4–7 September 2018; IEEE: Glasgow, UK, 2018; pp. 1–6. [Google Scholar]

- Kunlun, H.; Zexiang, C.; Yang, L. Study on protective performance of HVDC transmission line protection with different types of line fault. In Proceedings of the 2011 4th International Conference on Electric Utility Deregulation and Restructuring and Power Technologies (DRPT), Weihai, China, 6–9 July 2011; IEEE: Weihai, China, 2011; pp. 358–361. [Google Scholar]

- Johannesson, N.; Norrga, S.; Wikström, C. Selective wave-front based protection algorithm for MTDC systems. In Proceedings of the 13th International Conference on Development in Power System Protection 2016 (DPSP), Edinburgh, UK, 7–10 March 2016; IET: Edinburgh, UK, 2016; pp. 1–6. [Google Scholar]

- Naidoo, D.; Ijumba, N.M. A protection system for long HVDC transmission lines. In Proceedings of the 2005 IEEE Power Engineering Society Inaugural Conference and Exposition in Africa, Durban, South Africa, 11–15 July 2005; IEEE: Durban, South Africa, 2005; pp. 150–155. [Google Scholar]

- Descloux, J.; Raison, B.; Curis, J.B. Protection algorithm based on differential voltage measurement for MTDC grids. In Proceedings of the 12th IET International Conference on Developments in Power System Protection (DPSP 2014), Copenhagen, Denmark, 31 March–3 April 2014. [Google Scholar]

- Shuo, Z.; Yongli, L. Simulation and analysis of HVDC line protection under the single pole to ground fault with high transition resistance. In Proceedings of the 2011 4th International Conference on Electric Utility Deregulation and Restructuring and Power Technologies (DRPT), Weihai, China, 6–9 July 2011; IEEE: Weihai, China, 2011; pp. 926–929. [Google Scholar]

- Kobet, G.; Kasztenny, B.; Allen, M.; Buanno, A.; Darlington, A.N.; Deronja, A.; DoCarmo, H.; Finley, J.; Gresko, G.; Henriksen, L.; et al. Justifying pilot protection on transmission lines. In Proceedings of the 2010 63rd Annual Conference for Protective Relay Engineers, College Station, TX, USA, 29 March–1 April 2010; IEEE: College Station, TX, USA, 2010; pp. 1–31. [Google Scholar]

- de Kerf, K.; Srivastava, K.; Reza, M.; Bekaert, D.; Cole, S.; van Hertem, D.; Belmans, R. Wavelet-based protection strategy for DC faults in multi-terminal VSC HVDC systems. IET Gener. Transm. Distrib. 2011, 5, 496–503. [Google Scholar] [CrossRef]

| Item | Values |

|---|---|

| Normal voltage of DC power system, VDC | 500 V |

| Normal current of DC power system, IDC | 50 A |

| Rated power of DC power system, PDC | 25 kW |

| Fault current without SFCL | 500 A |

| Target of fault current limiting rate | 70% |

| Cross-sectional area of the core, Acore | 0.01 m2 |

| Length of the iron-core yoke, lyoke | 60 cm |

| Length of the iron-core limb, llimb | 50 cm |

| Length of the magnetic path in the core, lcore | 160 cm |

| Number of turns in the PW, Npri | 198 turns |

| Number of turns in the SW, Nsec | 150 turns |

| Saturated magnetic flux in the PW, Φsat | 3.2 Wb |

| Operating current of the SW, Isec | 200 A |

| Air core inductance of the PW, Lair | 6 mH |

| Item | 285 Hz | 500 Hz | 1000 Hz | 1500 Hz | 2000 Hz |

|---|---|---|---|---|---|

| L (μH) | 55 | 55 | 55 | 55 | 55 |

| C (μF) | 5670 | 1850 | 462 | 205 | 115 |

| Cut-off (ms) | 24.9 | 9.6 | 4.8 | 4.0 | 4.2 |

| No. | Method | Claimed Operation Time | Measuring Signal | Main/Backup Protection | Use of Reactor | Use of Comms | Refs. |

|---|---|---|---|---|---|---|---|

| 1 | Overcurrent | <2 ms—Low Z <5 ms—High Z | Part of main or Back-up | To limit fault current | No | [42] | |

| 2 | Undervoltage | <1 ms | Part of main or Back-up | For selectivity | No | [43] | |

| 3 | Travelling waves | <1 ms | Initial wave front of voltage and current | Main or part of main | To define boundaries | No | [44] |

| 4 | dV/dt (ROCOV) | <0.1 ms | Main or part of main | To define boundaries | No | [45] | |

| 5 | dI/dt (ROCOC) | <0.1 ms (Solid Fault) <0.2 ms—Low/High Impedance Fault | Main or part of main | To define boundaries | No | [46] | |

| 6 | Current differential | <2 ms +comms delay time | Main or busbar protection | Not needed | Yes | [47] | |

| 7 | Directional protection | <1 ms +comms delay time | Directional detection | Probably not main | Not needed | Yes | [48] |

| 8 | Wavelet Transform | <0.1 ms | dV/dt, dI/dt Wavelet transform | Main or part of main | To define boundaries | No | [49] |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, J.-I.; Dao, V.Q.; Dinh, M.-C.; Lee, S.-j.; Kim, C.S.; Park, M. Combined Operation Analysis of a Saturated Iron-Core Superconducting Fault Current Limiter and Circuit Breaker for an HVDC System Protection. Energies 2021, 14, 7993. https://doi.org/10.3390/en14237993

Lee J-I, Dao VQ, Dinh M-C, Lee S-j, Kim CS, Park M. Combined Operation Analysis of a Saturated Iron-Core Superconducting Fault Current Limiter and Circuit Breaker for an HVDC System Protection. Energies. 2021; 14(23):7993. https://doi.org/10.3390/en14237993

Chicago/Turabian StyleLee, Jae-In, Van Quan Dao, Minh-Chau Dinh, Seok-ju Lee, Chang Soon Kim, and Minwon Park. 2021. "Combined Operation Analysis of a Saturated Iron-Core Superconducting Fault Current Limiter and Circuit Breaker for an HVDC System Protection" Energies 14, no. 23: 7993. https://doi.org/10.3390/en14237993

APA StyleLee, J.-I., Dao, V. Q., Dinh, M.-C., Lee, S.-j., Kim, C. S., & Park, M. (2021). Combined Operation Analysis of a Saturated Iron-Core Superconducting Fault Current Limiter and Circuit Breaker for an HVDC System Protection. Energies, 14(23), 7993. https://doi.org/10.3390/en14237993