Technical Assessment of Hybrid HVDC Circuit Breaker Components under M-HVDC Faults

Abstract

:1. Introduction

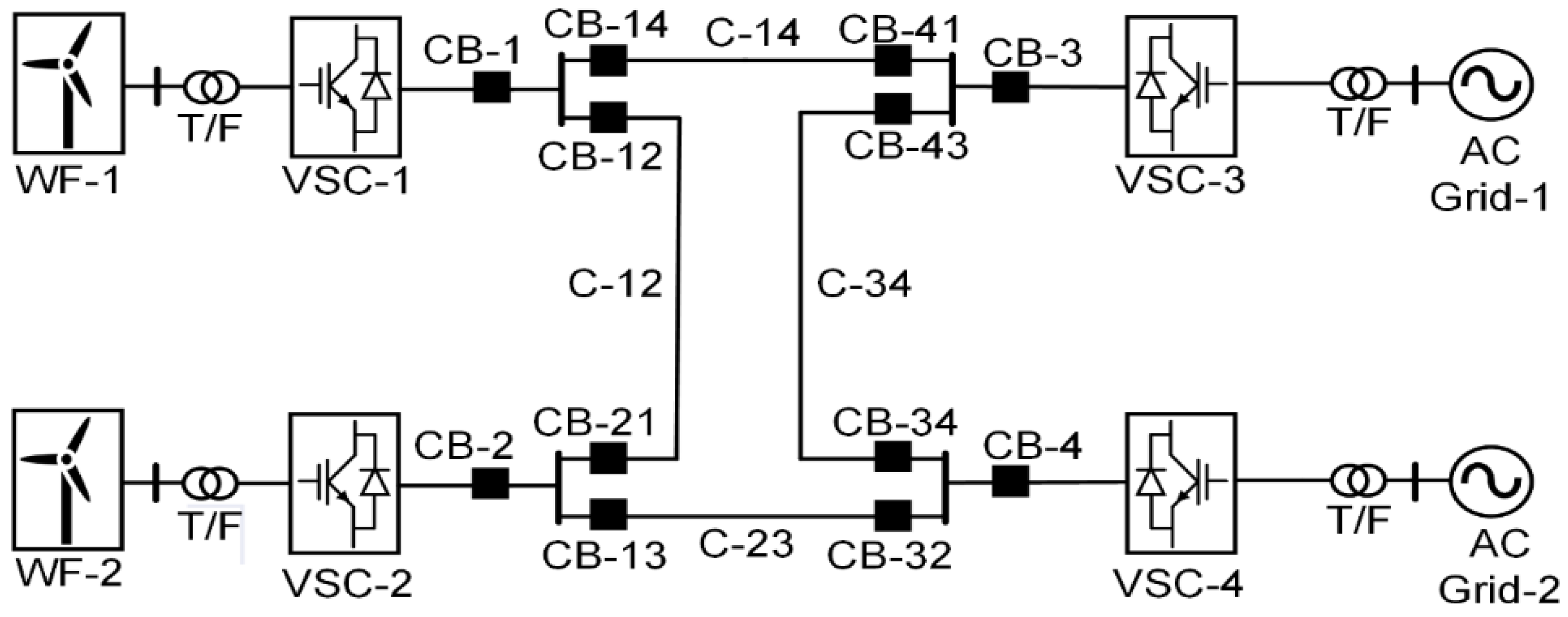

2. M-HVDC Test System Model

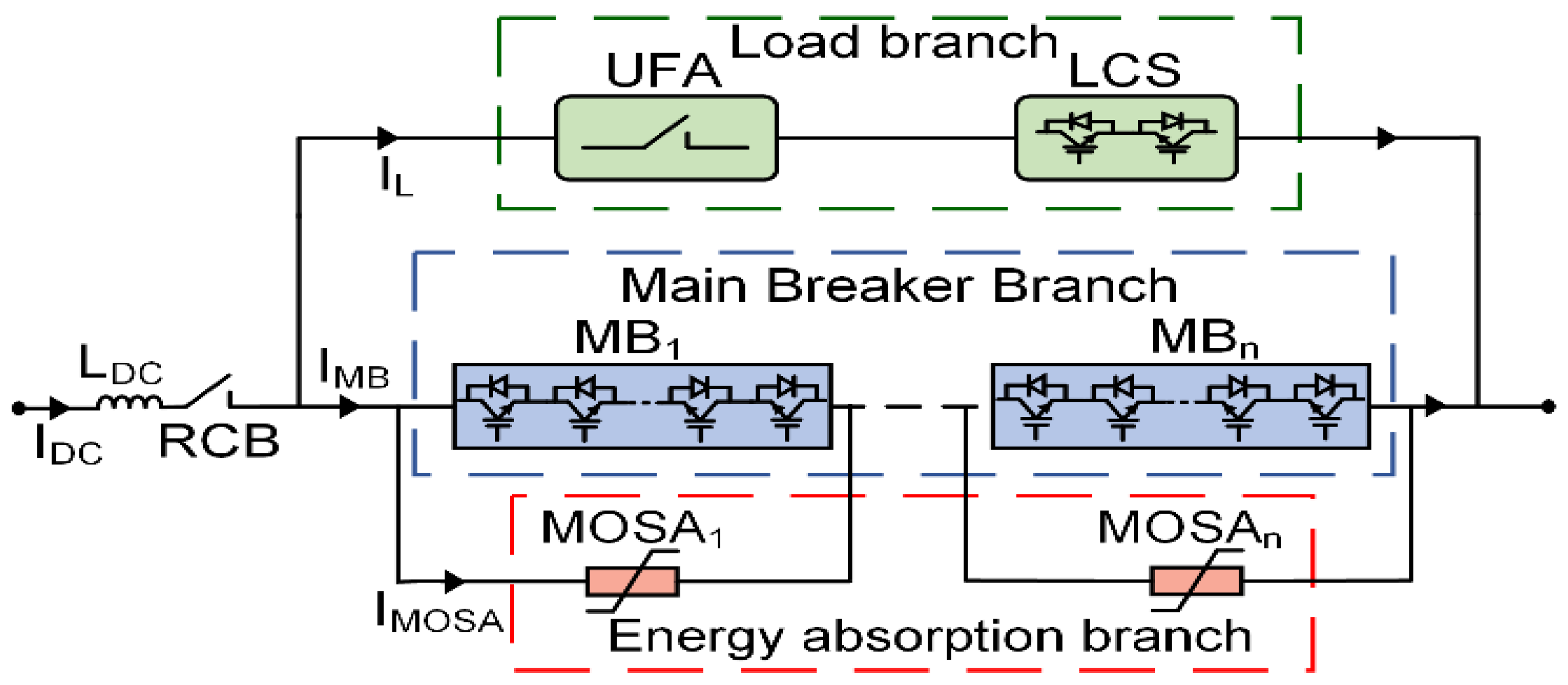

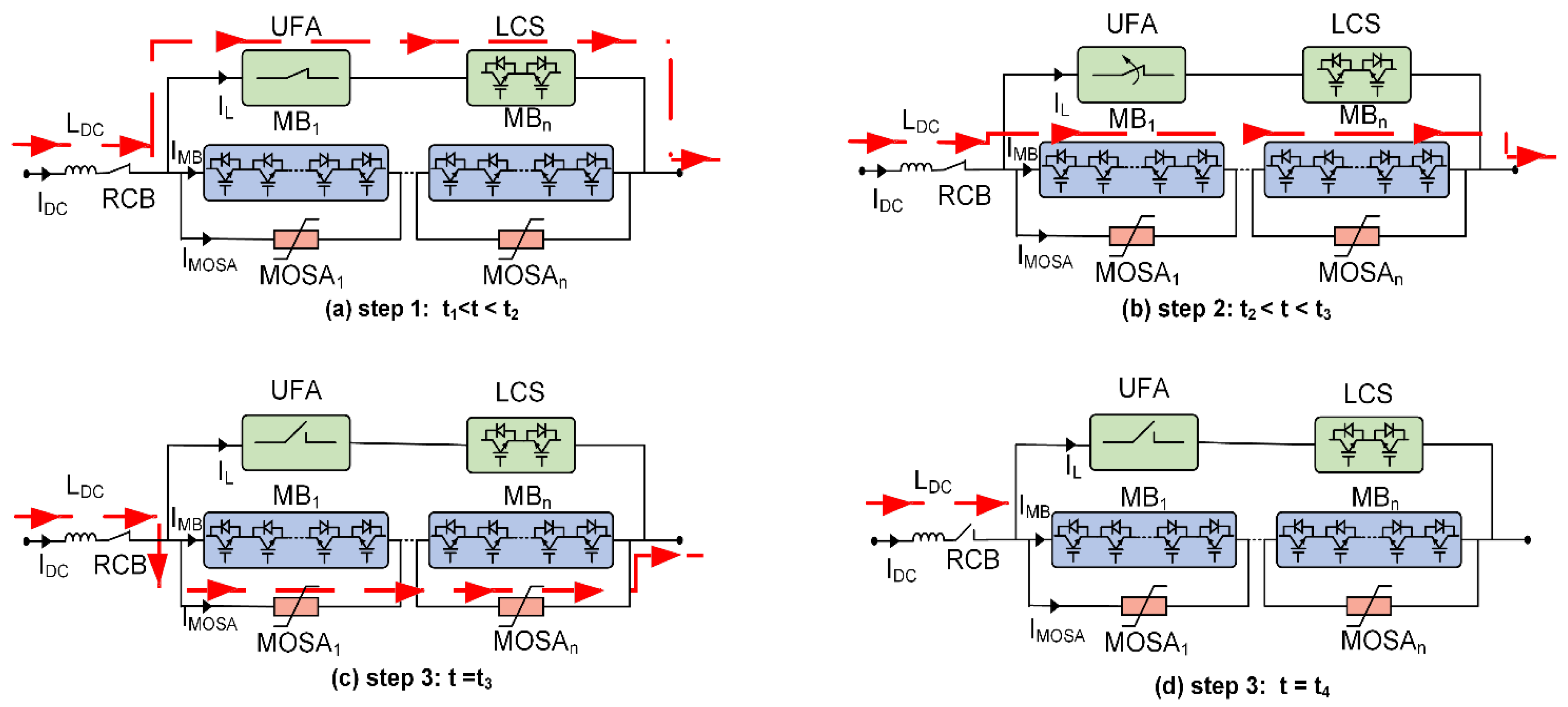

3. H-DCCB Proposed by the ABB

4. H-DCCB Protection Flow Chart

5. Stress Analysis during DC Fault

5.1. Voltage and Current Stresses

5.2. MOSA Energy Absorption Stress

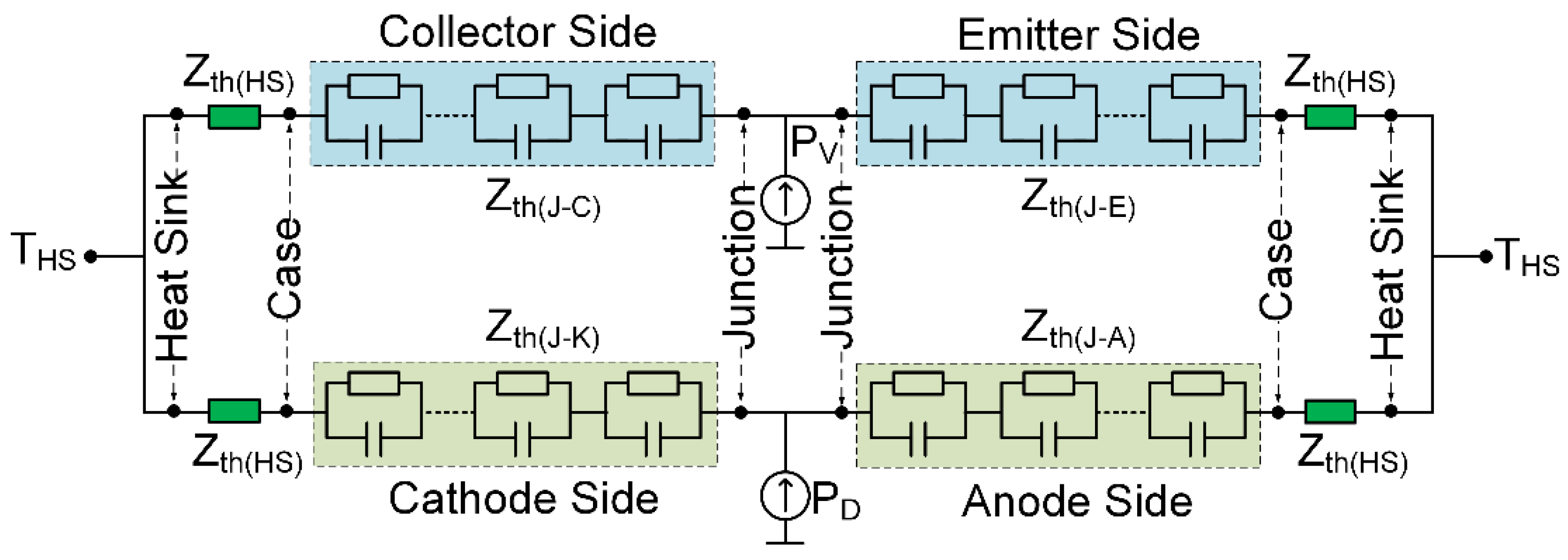

5.3. Thermal Stresses on Press-Pack IGBT Module

6. Results and Discussion

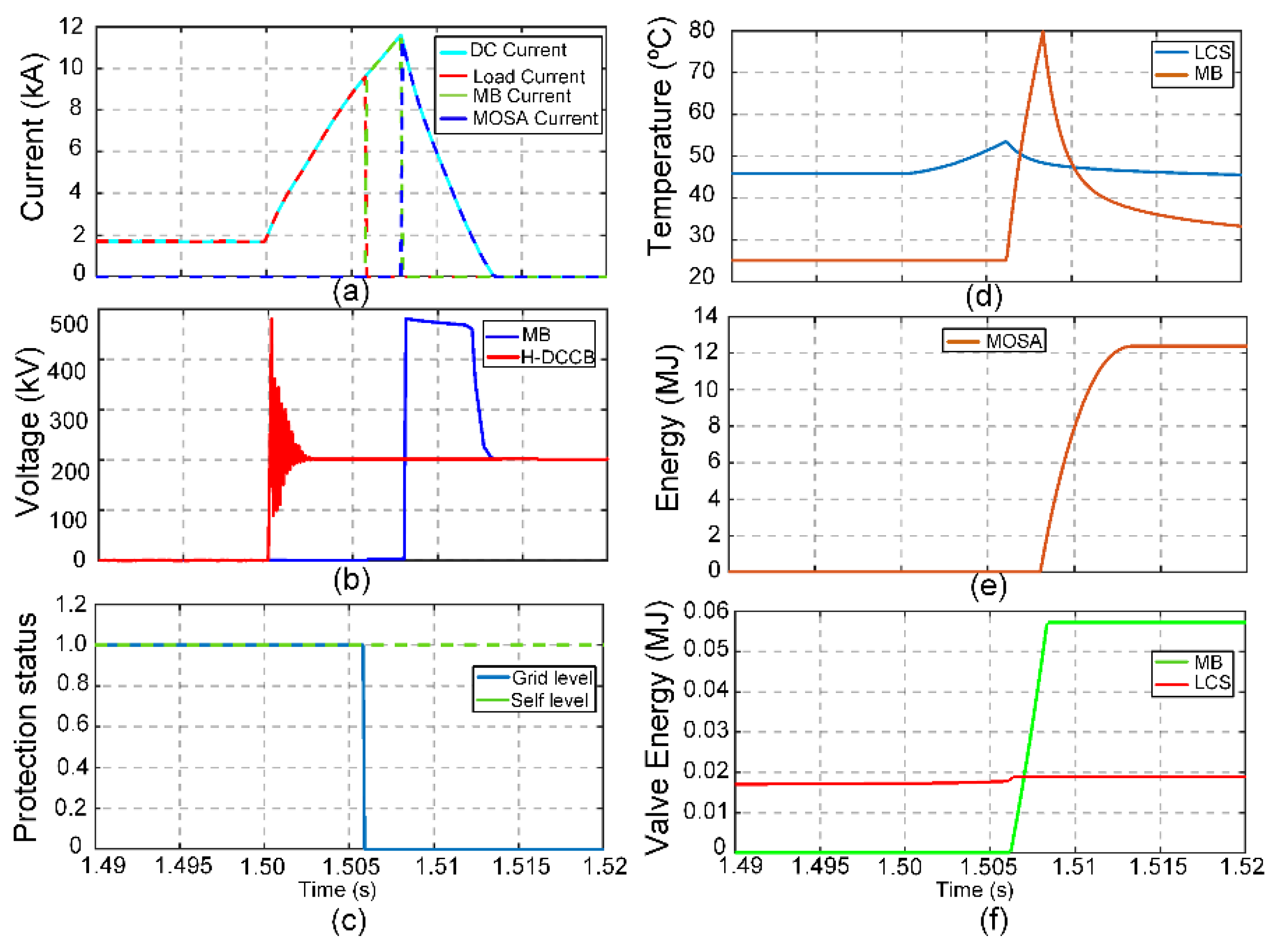

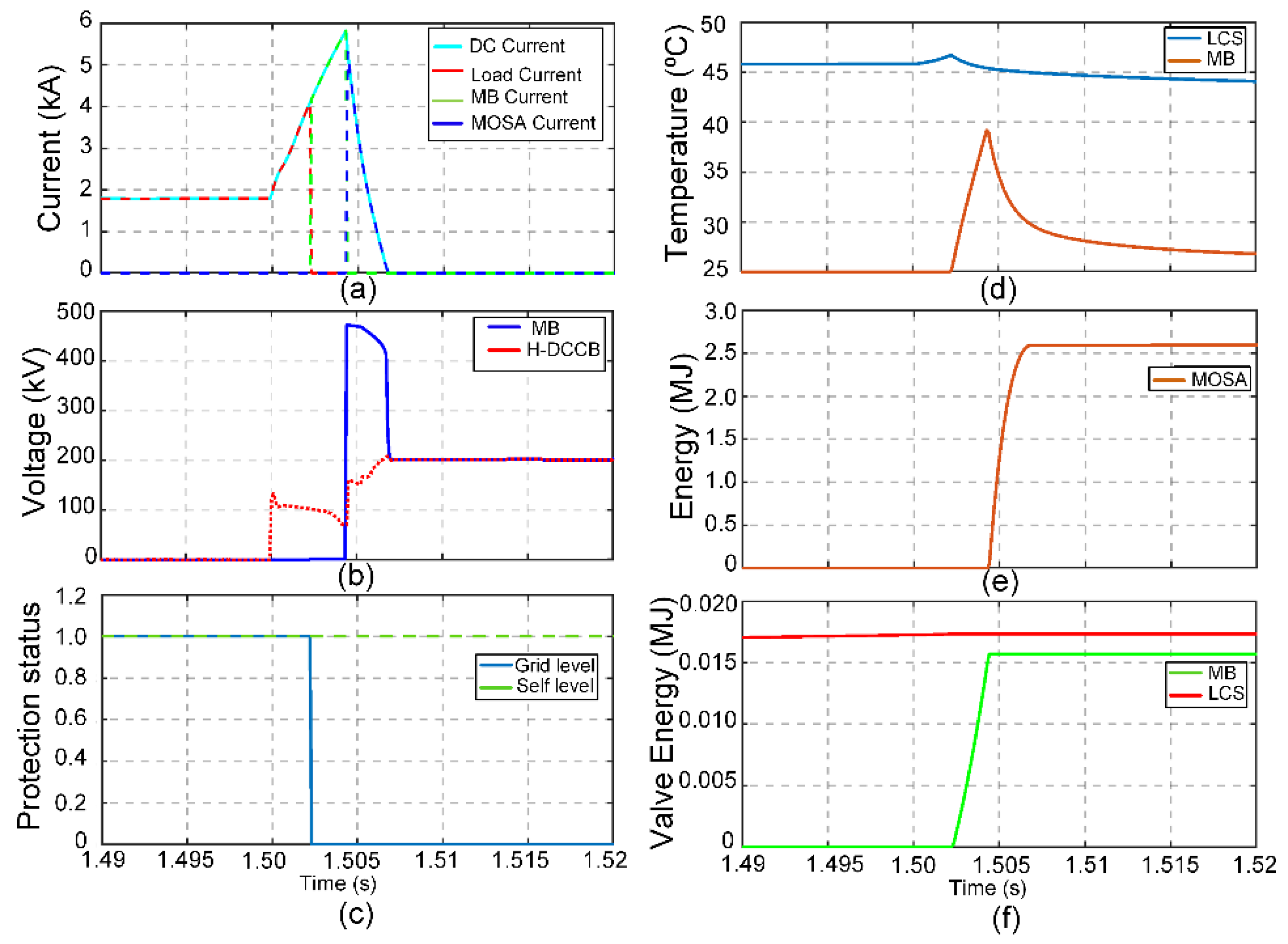

6.1. Grid-Level Protection

6.1.1. Low Impedance Fault Current Interruption

6.1.2. High Impedance Fault Current Interruption

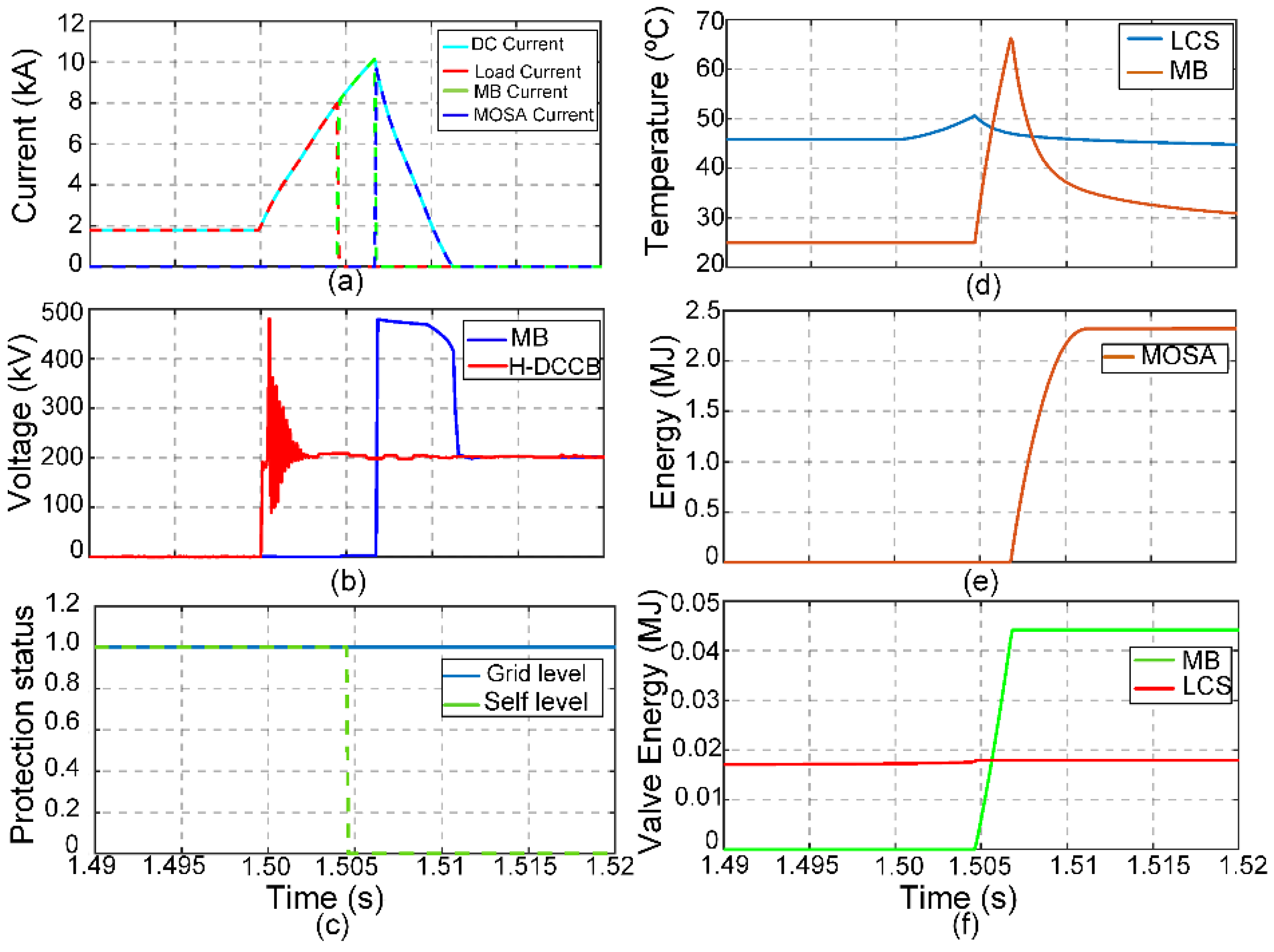

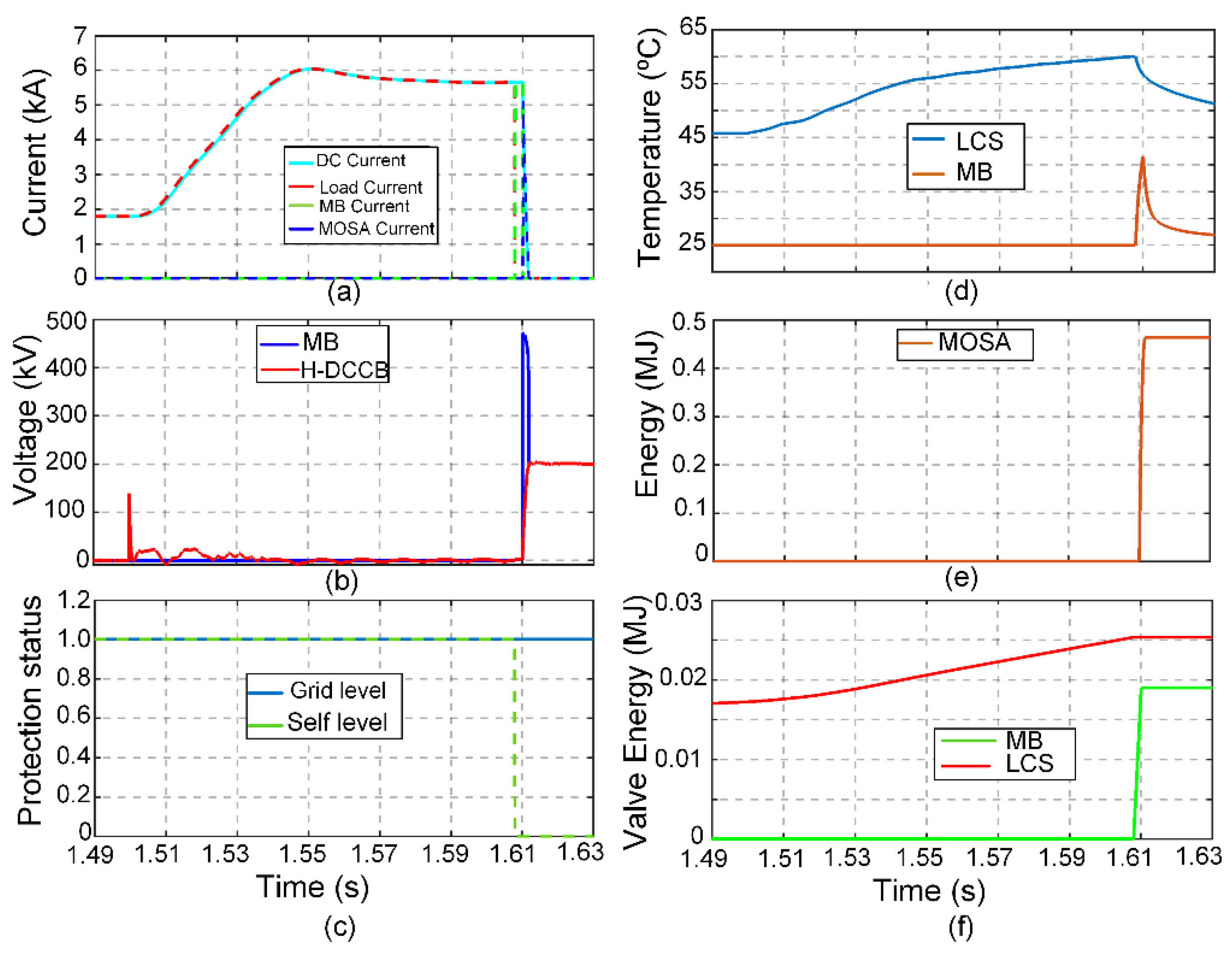

6.2. Self-Level Protection

6.2.1. Low Impedance Fault Current Interruption

6.2.2. High Impedance Fault Current Interruption

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Raza, A.; Akhtar, A.; Jamil, M.; Abbas, G.; Gilani, S.O.; Yuchao, L.; Khan, M.N.; Izhar, T.; Dianguo, X.; Williams, B.W.; et al. A Protection Scheme for Multi-Terminal VSC-HVDC Transmission Systems. IEEE Access 2018, 6, 3159–3166. [Google Scholar] [CrossRef]

- Muniappan, M. A comprehensive review of DC fault protection methods in HVDC transmission systems. Prot. Control Mod. Power Syst. 2021, 6, 1–20. [Google Scholar] [CrossRef]

- Barnes, M.; Vilchis-Rodriguez, D.S.; Pei, X.; Shuttleworth, R.; Cwikowski, O.; Smith, A.C. HVDC Circuit Breakers—A Review. IEEE Access 2020, 8, 211829–211848. [Google Scholar] [CrossRef]

- Liu, Y.; Jin, Y.; Li, Z.; Liu, Y.; Li, B.; Duan, Z. Mechanical DC Breakers and Hybrid MMC Based Coordinated Strategy for MMC-HVDC DC Fault Riding Through. IEEE J. Emerg. Sel. Top. Power Electron. 2021. [Google Scholar] [CrossRef]

- Liu, F.; Liu, W.; Zha, X.; Yang, H.; Feng, K. Solid-State Circuit Breaker Snubber Design for Transient Overvoltage Suppression at Bus Fault Interruption in Low-Voltage DC Microgrid. IEEE Trans. Power Electron. 2017, 32, 3007–3021. [Google Scholar] [CrossRef]

- Stumpe, M.; Tünnerhoff, P.; Dave, J.; Schnettler, A.; Ergin, D.; Schoen, A.; Würflinger, K.; Schettler, F. DC fault protection for modular multi-level converter-based HVDC multi-terminal systems with solid-state circuit breakers. IET Gener. Trans. Distrib. 2018, 12, 3013–3020. [Google Scholar] [CrossRef]

- Ludin, G.A.; Amin, M.A.; Matayoshi, H.; Rangarajan, S.S.; Hemeida, A.M.; Takahashi, H.; Senjyu, T. Solid-State DC Circuit Breakers and Their Comparison in Modular Multilevel Converter Based-HVDC Transmission System. Electronics 2021, 10, 1204. [Google Scholar] [CrossRef]

- Hafner, J.; Jacobson, B. Proactive hybrid HVDC breakers—A key innovation for reliable HVDC grid. In Proceedings of the Electric Power System of the Future-Integrating Supergrids and Microgrids, Cigre Symposium, Bologna, Italy, 13–15 September 2011; pp. 264–272. [Google Scholar]

- Zhou, W.; Wei, X.; Zhang, S.; Tang, G.; He, Z.; Zheng, J.; Dan, Y.; Gao, C. Development and test of a 200kV full-bridge based hybrid HVDC breaker. In Proceedings of the 17th European Conference on Power Electronics and Applications (EPE’15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015; pp. 1–7. [Google Scholar]

- Bösche, D.; Wilkening, E.; Köpf, H.; Kurrat, M. Hybrid DC Circuit Breaker Feasibility Study. IEEE Trans. Compon. Packag. Manuf. Technol. 2017, 7, 354–362. [Google Scholar] [CrossRef]

- Rao, H.; Zhou, Y.; Zou, C.; Xu, S.; Li, Y.; Yang, L.; Huang, W. Design aspects of hybrid HVDC system. CSEE J. Power Energy Syst. 2021, 7, 644–653. [Google Scholar]

- Abedrabbo, M.; Leterme, W.; Hertem, D.V. Impact of operational parameters on HVDC circuit breaker requirements. In Proceedings of the CIGRE-IEC 2019 Conference on EHV and UHV (AC & DC), Hakodate, Japan, 23–26 April 2019; p. 9. [Google Scholar]

- Raza, A.; Mustafa, A.; Alqasemi, U.; Rouzbehi, K.; Muzzammel, R.; Guobing, S.; Abbas, G. HVdc Circuit Breakers: Prospects and Challenges. Appl. Sci. 2021, 11, 5047. [Google Scholar] [CrossRef]

- Xiao, H.; Xu, Z.; Xiao, L.; Gan, C.; Xu, F.; Dai, L. Components Sharing Based Integrated HVDC Circuit Breaker for Meshed HVDC Grids. IEEE Trans. Power Deliv. 2020, 35, 1856–1866. [Google Scholar] [CrossRef]

- Callavik, M.; Blomberg, A.; Hafner, J.; Jacobson, B. Break-through! ABB’s hybrid HVDC breaker, an innovation breakthrough enabling reliable HVDC grids. Abb. Rev. 2012, 2, 7–13. [Google Scholar]

- Grieshaber, W.; Dupraz, J.-P.; Panache, D.-L.; Violleau, L. Development and test of a 120 kV direct current circuit breaker. CIGRE Paris 2014, 1–11, Paper B4–301. [Google Scholar]

- Zheng, X.; Jia, R.; Gong, L.; Zhang, G.; Pei, X. An optimized coordination strategy between line main protection and hybrid dc breaker for VSC-based dc grid using overhead transmission line. Energies 2002, 12, 1462. [Google Scholar] [CrossRef] [Green Version]

- An, T.; Tang, G.; Wang, W. Research and application on multi-terminal and DC grids based on VSC-HVDC technology in China. High Volt. 2017, 2, 1–10. [Google Scholar] [CrossRef]

- Smeets, R. Safeguarding the Supergrid. IEEE Spectr. 2015, 52, 38–43. [Google Scholar] [CrossRef]

- Shukla, A.; Demetriades, G.D. A Survey on Hybrid Circuit-Breaker Topologies. IEEE Trans. Power Deliv. 2014, 30, 627–641. [Google Scholar] [CrossRef]

- Belda, N.A.; Smeets, R.P.P. Test Circuits for HVDC Circuit Breakers. IEEE Trans. Power Deliv. 2016, 32, 285–293. [Google Scholar] [CrossRef]

- Tokuyama, S.; Arimatsu, K.; Yoshioka, Y.; Kato, Y.; Hirata, K. Development and Interrupting Tests on 250KV 8KA HVDC Circuit Breaker. IEEE Trans. Power Appar. Syst. 1985, 104, 2452–2459. [Google Scholar] [CrossRef]

- Tamura, S.; Shimada, R.; Kito, Y.; Kanai, Y.; Koike, H.; Ikeda, H.; Yanabu, S. Parallel Interruption of Heavy Direct Current by Vacuum Circuit Breakers. IEEE Trans. Power Appar. Syst. 1980, 3, 1119–1129. [Google Scholar] [CrossRef]

- Belda, N.A.; Plet, C.A.; Smeets, R.P.P. Full-Power Test of HVDC Circuit-Breakers with AC Short-Circuit Generators Operated at Low Power Frequency. IEEE Trans. Power Deliv. 2019, 34, 1843–1852. [Google Scholar] [CrossRef]

- Gao, C.; Ding, X.; Tang, G.; Wang, G.; Qiu, P. Key stress extraction and equivalent test method for hybrid DC circuit breaker. Glob. Energy Interconnect. 2018, 1, 29–38. [Google Scholar]

- Xu, Z.; Xiao, H.; Xu, Y. Two basic ways to realize DC circuit breakers. J. Eng. 2019, 2019, 3098–3105. [Google Scholar] [CrossRef]

- Hofmann, G.; LaBarbera, G.; Reed, N.; Shillong, L.; Long, W.; Melvold, D. Field test of HVDC circuit breaker: Load break and fault clearing on the Pacific intertie. IEEE Trans. Power Appar. Syst. 1976, 95, 829–838. [Google Scholar] [CrossRef]

- Melvold, D.; Shockley, P.; Long, W.; Hingorani, N. Three terminal operations of the Pacific HVDC intertie for dc circuit breaker testing. IEEE Trans. Power Appar. Syst. 1976, 95, 1287–1296. [Google Scholar] [CrossRef]

- Yanabu, S.; Tamagawa, T.; Irokawa, S.; Horiuchi, T.; Tomimuro, S. Development of HVDC Circuit Breaker and its Interrupting Test. IEEE Trans. Power Appar. Syst. 1982, 101, 1958–1965. [Google Scholar] [CrossRef]

- Shimada, R.; Tani, K.; Kishimoto, H.; Tamura, S.; Ikeda, H.; Tamagawa, T.; Yanabu, S.; Matsushita, T. Synthetic test methods of high-direct-current circuit breaker. Proc. Inst. Electr. Eng. 1979, 126, 965–970. [Google Scholar] [CrossRef]

- Sheng, B. A synthetic test circuit for current switching tests of HVDC circuit breakers. In Proceedings of the IEEE/PES Transmission and Distribution Conference and Exposition, Chicago, IL, USA, 21–24 April 2008. [Google Scholar]

- Du, C.; Wang, C. Review of DC Circuit Breaker Technology for HVDC Application. In Proceedings of the 22nd International Conference on Electrical Machines and Systems (ICEMS), Harbin, China, 11–14 August 2019; pp. 1–6. [Google Scholar]

- Leterme, W.; Ahmed, N.; Beerten, J.; Ängquist, L.; Hertem, D.V.; Norrga, S. A new HVDC grid test system for HVDC grid dynamics and protection studies in EMT-type software. In Proceedings of the 11th IET International Conference on AC and DC Power Transmission, Birmingham, UK, 10–12 February 2015. [Google Scholar]

- Raza, A.; Dianguo, X.; Yuchao, L.; Xunwen, S.; Williams, B.W.; Cecati, C. Coordinated Operation and Control of VSC Based Multiterminal High Voltage DC Transmission Systems. IEEE Trans. Sustain. Energy 2016, 7, 364–373. [Google Scholar] [CrossRef] [Green Version]

- Hock, P.; Belda, N.; Hinrichsen, V.; Smeets, R. Investigations on Metal-Oxide Surge Arresters for HVDC Circuit Breaker Applications. In Proceedings of the INMR World Congress, Tucson, AZ, USA, 20–23 October 2019. [Google Scholar]

- Hesami, M.; Bakhshi, A.; Mousavi, S.; Rouzbehi, K.; Escaño, J.M. HVDC Breaker Power Loss Reduction by Bridge-Type Hybrid Breakers. Energies 2021, 14, 1526. [Google Scholar] [CrossRef]

- Lin, W.; Jovcic, D.; Nguefeu, S.; Saad, H. Modelling of high-power hybrid DC circuit breaker for grid-level studies. IET J. Power Electron. 2016, 9, 237–246. [Google Scholar] [CrossRef]

- Promotion EU Project. WP6, Deliverable 6.3. Develop a Real-Tme Component Level Model for Hybrid DC CB; PROMOTioN: Arnhem, The Netherlands, 2016. [Google Scholar]

- Ito, H. HVDC Switching Equipment; CIGRE Green Books; Springer: Cham, Switzerland, 2019. [Google Scholar] [CrossRef]

- Weiss, D.; Drack, N.; Maibach, P.; Kirchhoff, F.; Hassanpoor, A. Surge Arrester based Load Commutation Switch for Hybrid HVDC Breaker and MV DC Breaker; PCIM Europe: Nuremberg, Germany, 2018. [Google Scholar]

- Hassanpoor, A.; Häfner, J.; Jacobson, B. Technical Assessment of Load Commutation Switch in Hybrid HVDC Breaker. IEEE Trans. Power Electron. 2015, 30, 5393–5400. [Google Scholar] [CrossRef]

- Data Sheet. Doc. No. 5SYA 1431-02 01-2018. Available online: https://library.e.abb.com/public/8d0f218db8df4641a4bf7c978dd2d239/5SNA%202000K450300%205SYA%201431-02%2001-2018.pdf (accessed on 1 January 2021).

- Simpson, R.; Plumpton, A.; Varley, M.; Tonner, C.; Taylor, P.; Dai, X. Press-pack IGBTs for HVDC and FACTs. CSEE J. Power Energy Syst. 2017, 3, 302–310. [Google Scholar] [CrossRef]

- Belda, N.A.; Plet, C.A.; Smeets, R.P.P. Analysis of Faults in Multiterminal HVDC Grid for Definition of Test Requirements of HVDC Circuit Breakers. IEEE Trans. Power Deliv. 2018, 33, 403–411. [Google Scholar] [CrossRef]

- Sneath, J.; Rajapakse, A.D. Fault Detection and Interruption in an Earthed HVDC Grid Using ROCOV and Hybrid DC Breakers. IEEE Trans. Power Deliv. 2016, 31, 973–981. [Google Scholar] [CrossRef]

- Geebelen, B.; Leterme, W.; Hertem, D.V. Analysis of DC breaker requirements for different HVDC grid protection schemes. In Proceedings of the 11th IET International Conference on AC and DC Power Transmission, Birmingham, UK, 10–12 February 2015. [Google Scholar]

- Yu, A.P.; Guo, B.X.; Wang, C.L.; Zhou, D.Z.; Wang, E.G.; Zhang, F.Z. Lifetime estimation for hybrid HVDC breakers. Int. J. Electr. Power Energy Syst. 2020, 120, 106035. [Google Scholar] [CrossRef]

- Xiang, W.; Yang, S.; Xu, L.; Zhang, J.; Lin, W.; Wen, J. A Transient Voltage-Based DC Fault Line Protection Scheme for MMC-Based DC Grid Embedding DC Breakers. IEEE Trans. Power Deliv. 2019, 34, 334–345. [Google Scholar] [CrossRef] [Green Version]

- Liu, J.; Ta, N.; Fan, C. Transient-Voltage-Based Protection Scheme for DC Line Faults in the Multiterminal VSC-HVDC System. IEEE Trans. Power Deliv. 2017, 32, 1483–1494. [Google Scholar] [CrossRef]

- Wang, Y.; Hao, Z.; Zhang, B.; Kong, F. A Pilot Protection Scheme for Transmission Lines in VSC-HVDC Grid Based on Similarity Measure of Traveling Waves. IEEE Access 2019, 7, 7147–7158. [Google Scholar] [CrossRef]

| Side | Parameter | Value |

|---|---|---|

| DC | M-HVDC grid voltage | 400 kV |

| Length of DC-cable 12 | 100 km | |

| Length of DC-cable 14 | 300 km | |

| Length of DC-cable 23 | 300 km | |

| Length of DC-cable 34 | 100 km | |

| AC | Line-Line system voltage | 240 kV |

| Rated power VSC-1 | 400 MW | |

| Rated power VSC-2 | 800 MW | |

| Rated power VSC-3 | −500 MW | |

| Rated power VSC-4 | −700 MW |

| Parameter | Value |

|---|---|

| Rated DC voltage (Vdc-R) | 400 kV |

| Rated DC current (Idc-R) | 1.80 kA |

| Rated breaking current (Idc-B) | 11.5 kA |

| Current limiting reactor | 150 mH |

| Number of series × parallel IGBT in LCS | 3 × 3 |

| Number of series IGBT in MB (Ns) | 200 |

| Rated breaking current for RCB and UFA | 0.01 kA |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Khalid, S.; Raza, A.; Alqasemi, U.; Sobahi, N.; Yousaf, M.Z.; Abbas, G.; Jamil, M. Technical Assessment of Hybrid HVDC Circuit Breaker Components under M-HVDC Faults. Energies 2021, 14, 8148. https://doi.org/10.3390/en14238148

Khalid S, Raza A, Alqasemi U, Sobahi N, Yousaf MZ, Abbas G, Jamil M. Technical Assessment of Hybrid HVDC Circuit Breaker Components under M-HVDC Faults. Energies. 2021; 14(23):8148. https://doi.org/10.3390/en14238148

Chicago/Turabian StyleKhalid, Saqib, Ali Raza, Umar Alqasemi, Nebras Sobahi, Muhammad Zain Yousaf, Ghulam Abbas, and Mohsin Jamil. 2021. "Technical Assessment of Hybrid HVDC Circuit Breaker Components under M-HVDC Faults" Energies 14, no. 23: 8148. https://doi.org/10.3390/en14238148