High-Performance 3-Phase 5-Level E-Type Multilevel–Multicell Converters for Microgrids

Abstract

1. Introduction

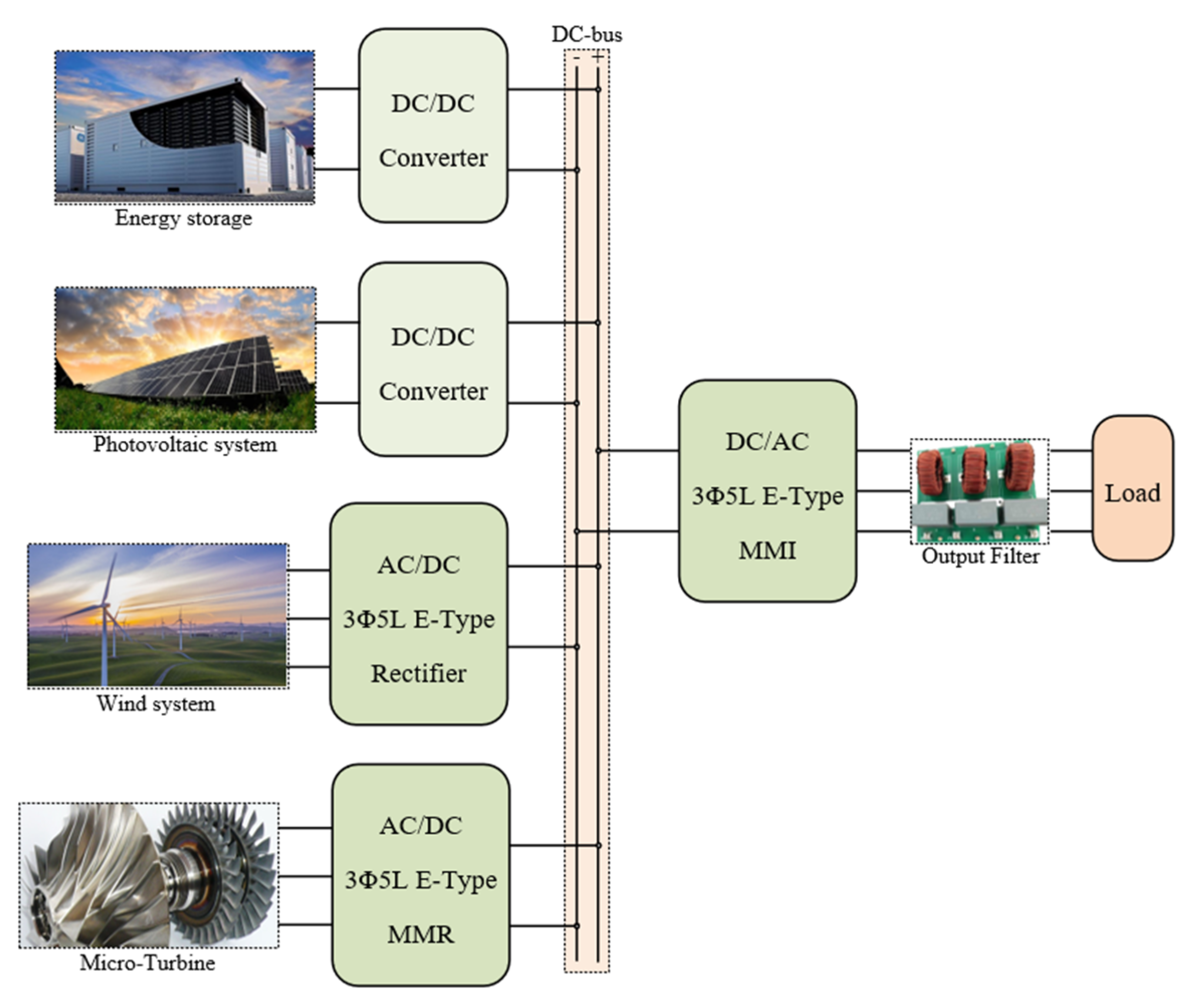

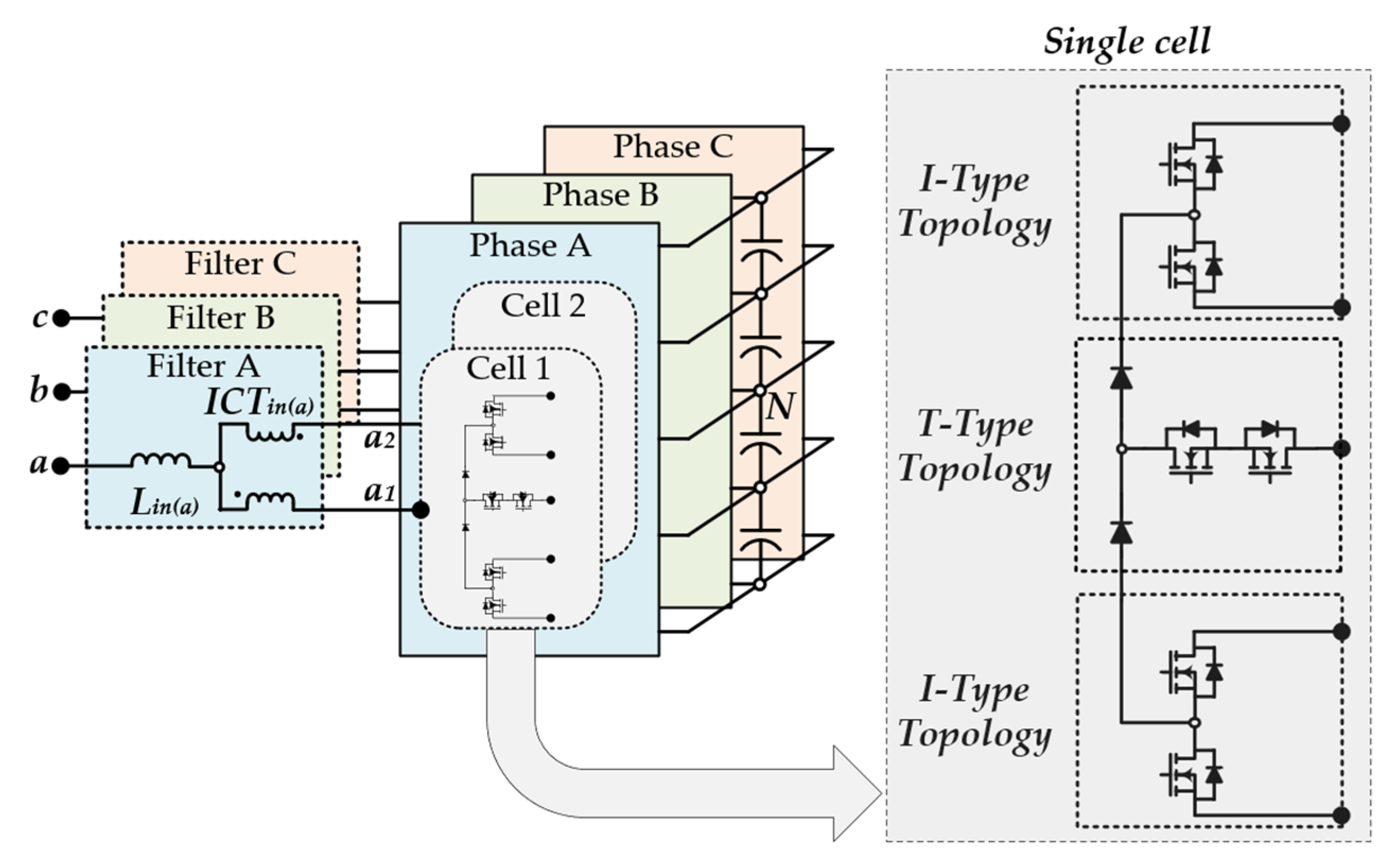

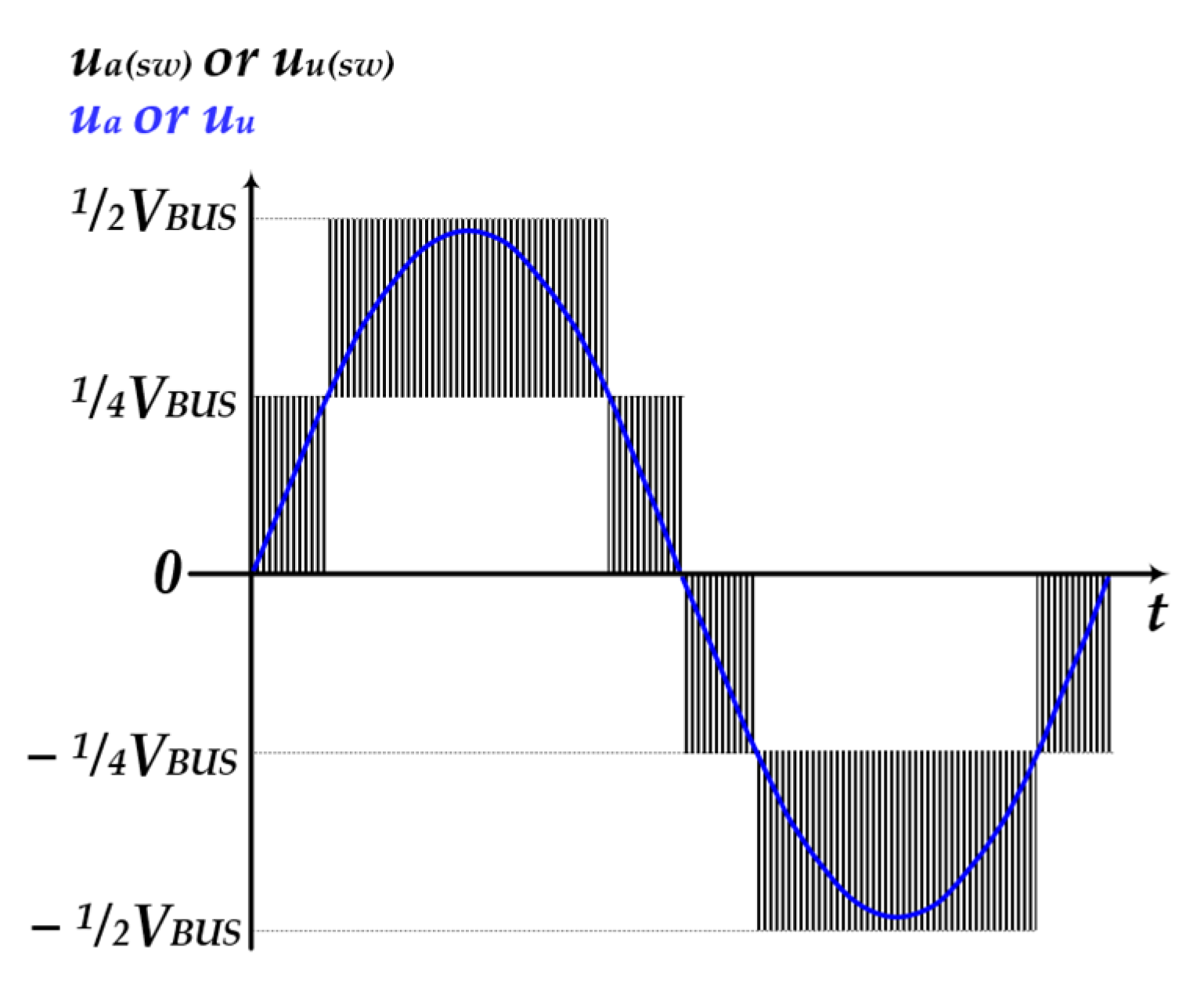

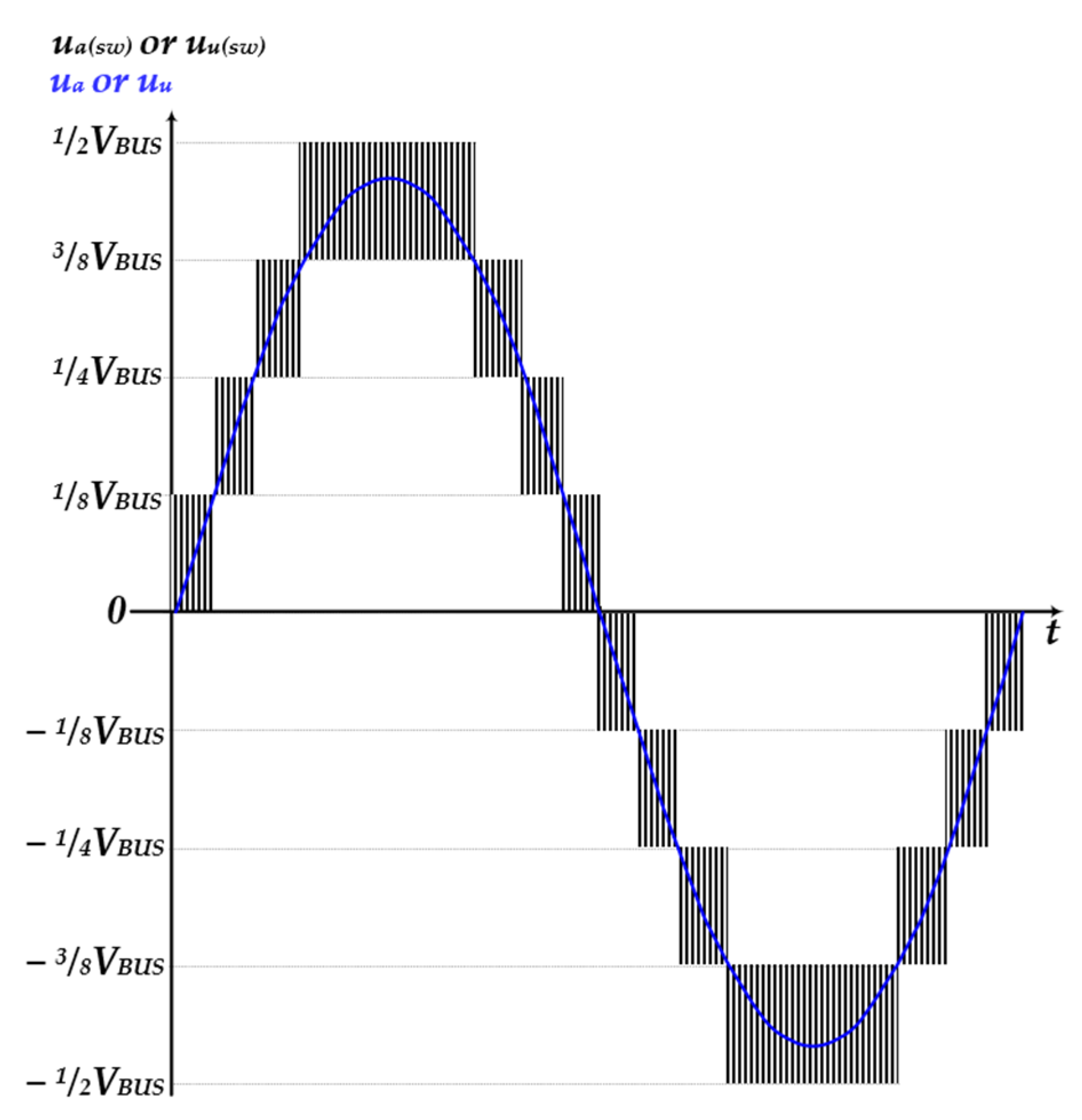

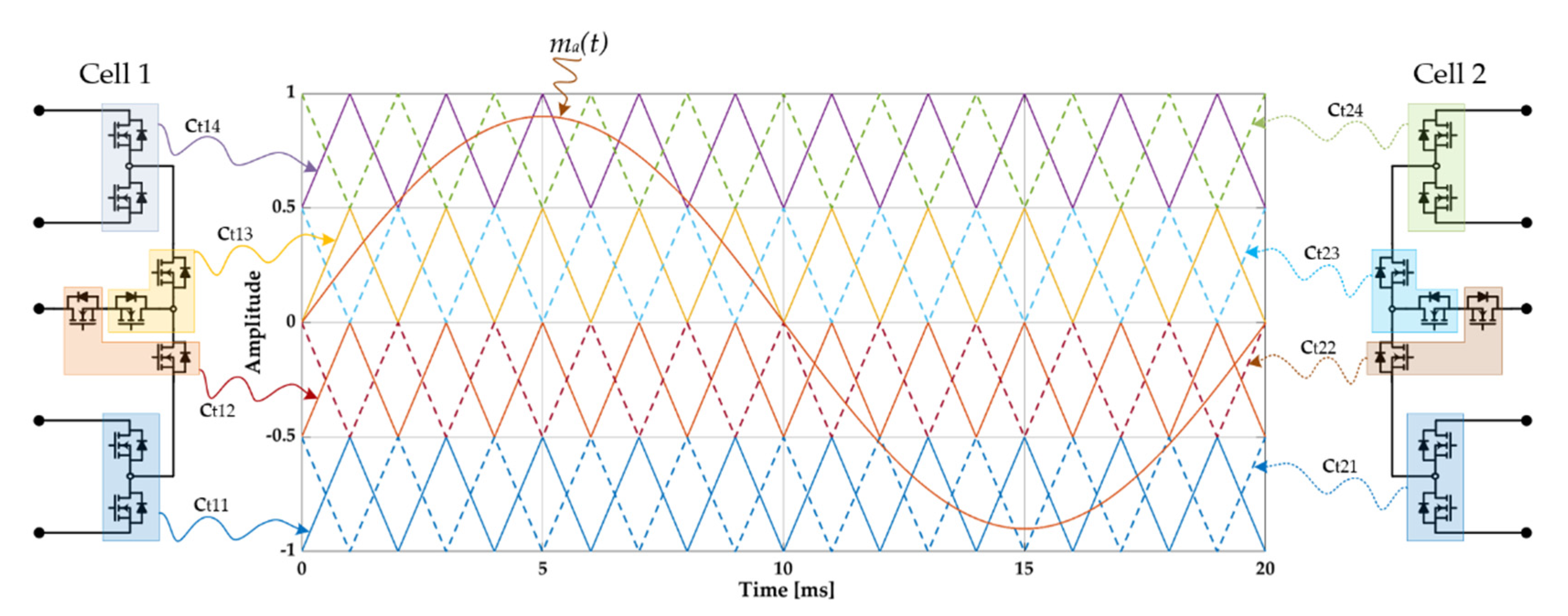

2. Operation Structure of 3-Phase 5-Level E-Type MMC

2.1. 3Φ5L E-Type MMR and MMI

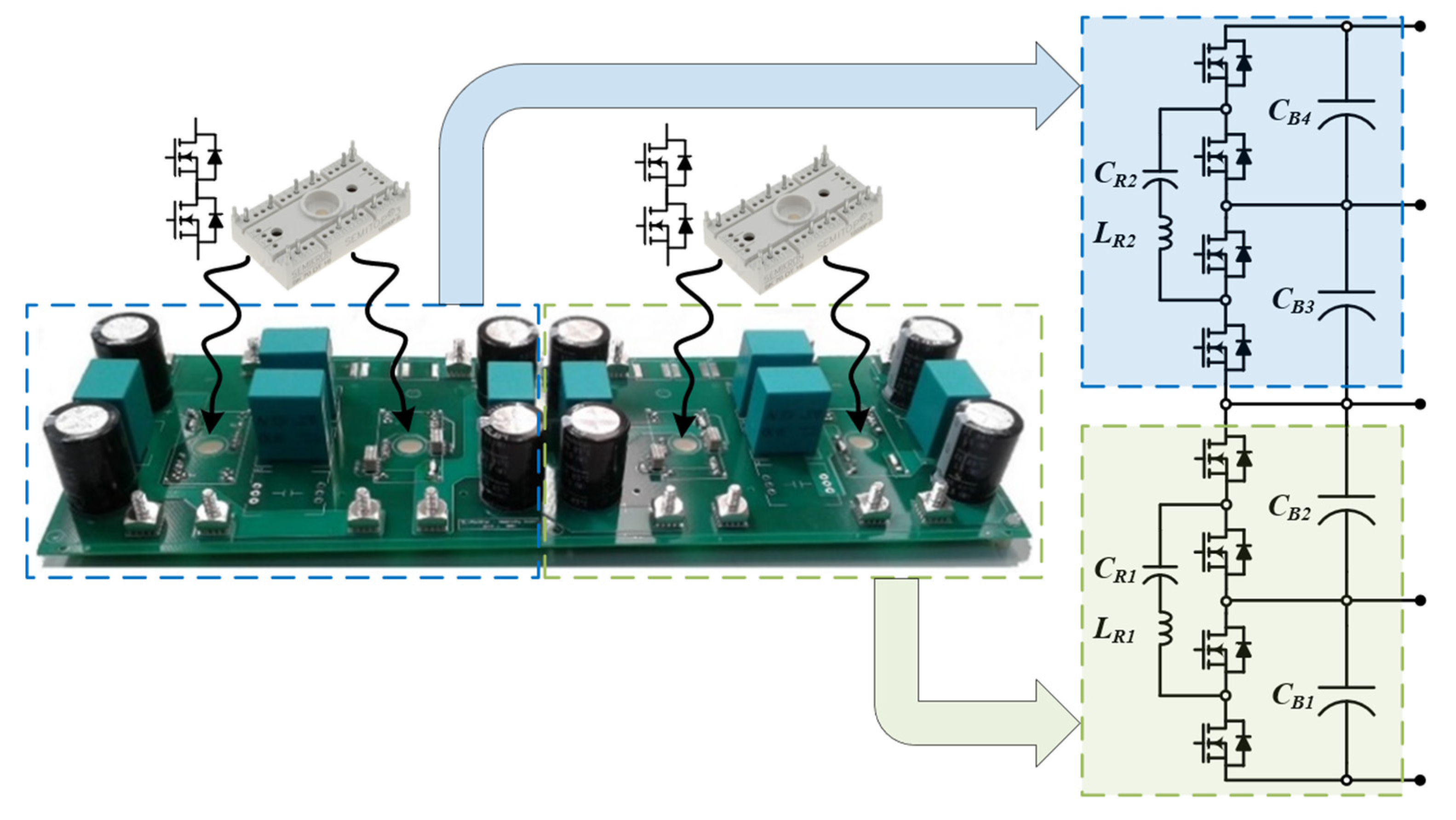

2.2. Balancing Circuit

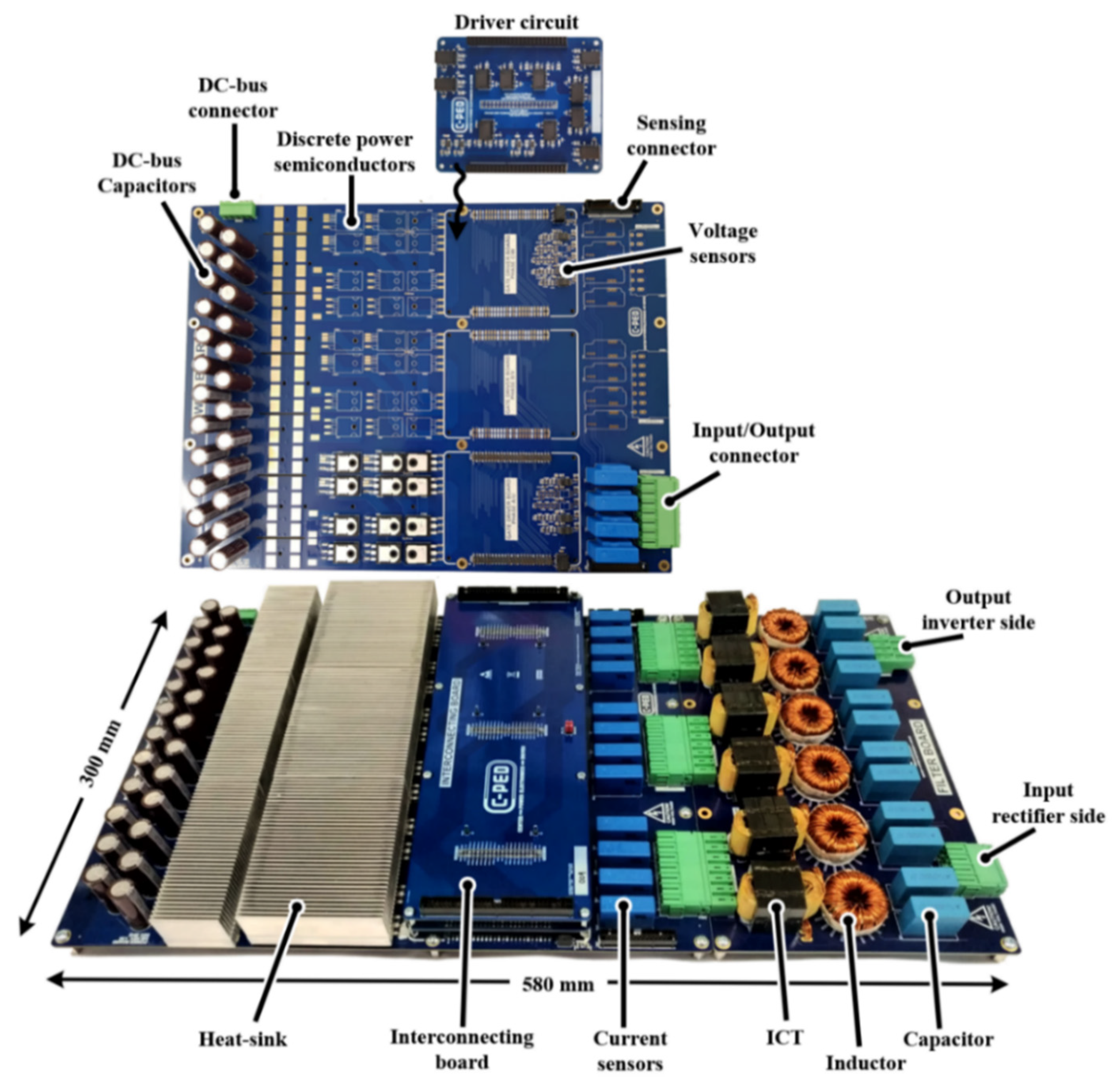

3. Hardware Design and Prototype of E-Type Topology

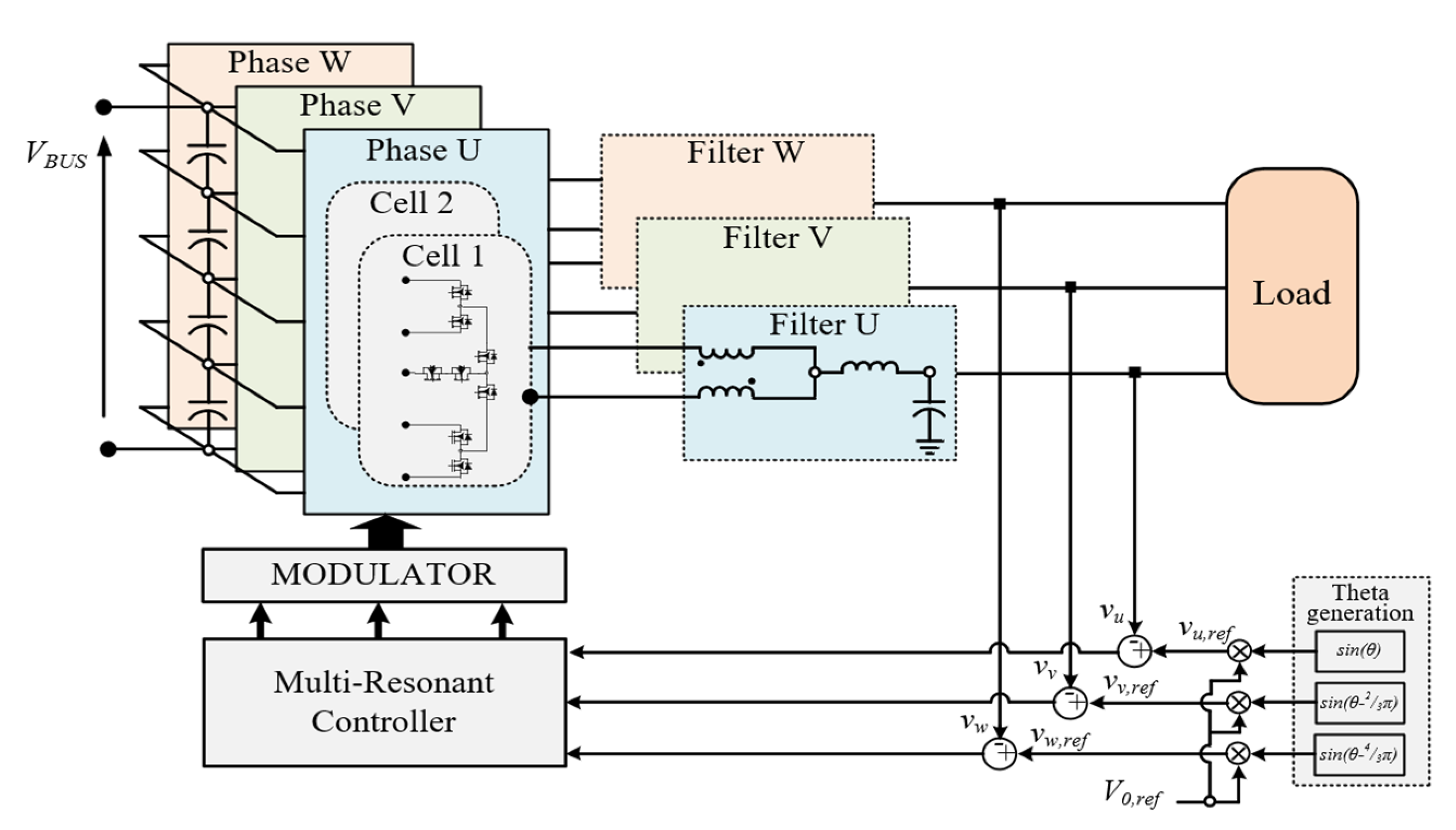

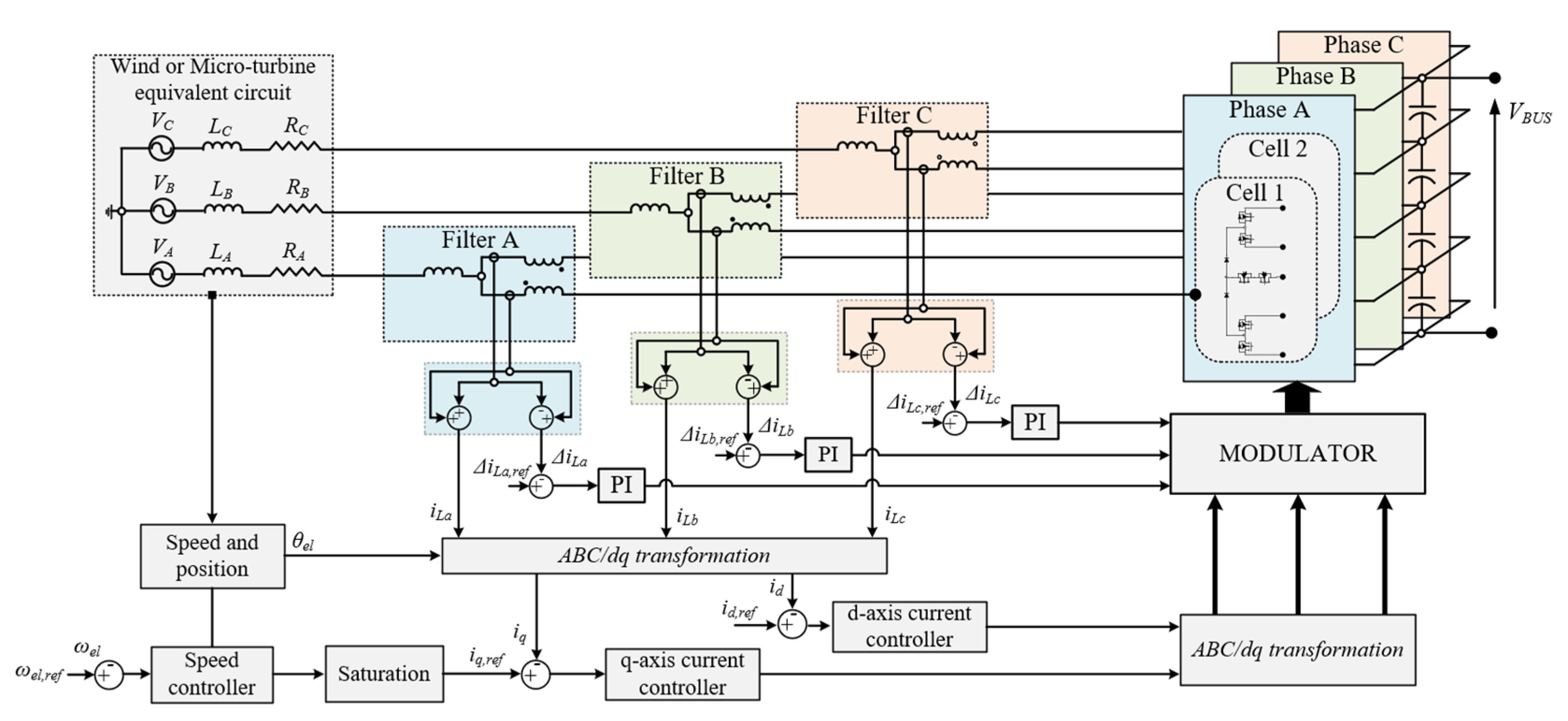

4. Control Interface

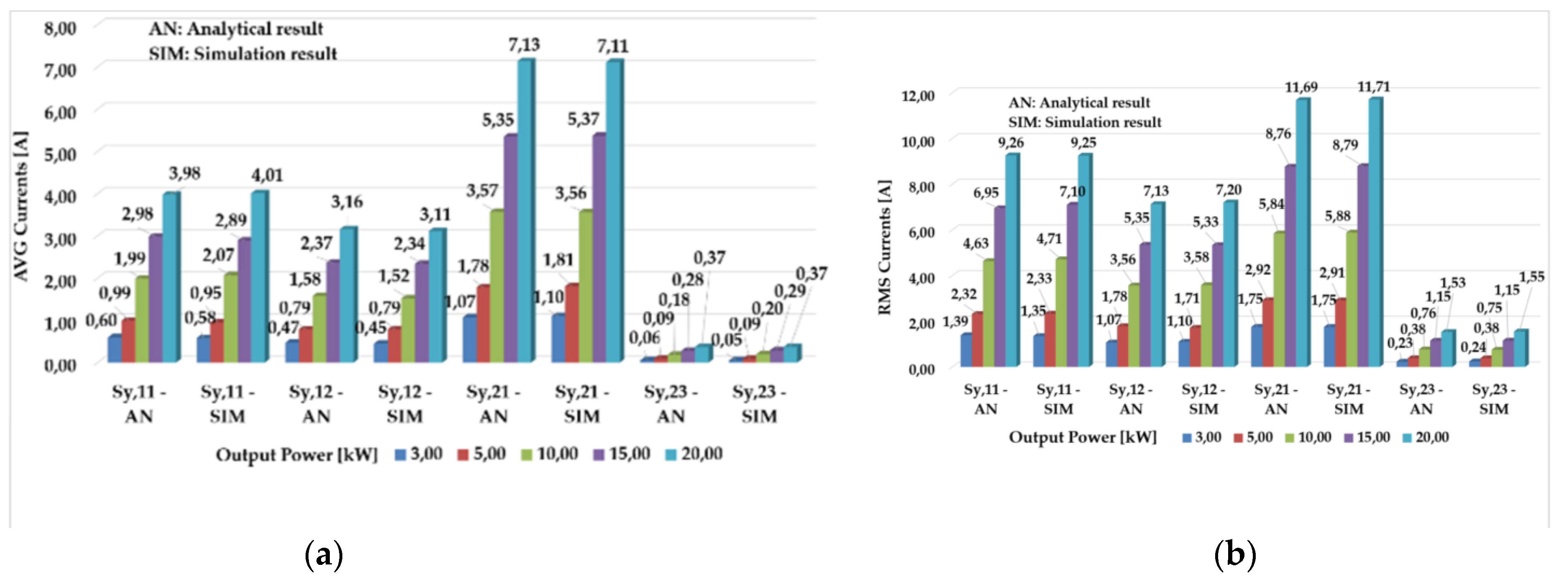

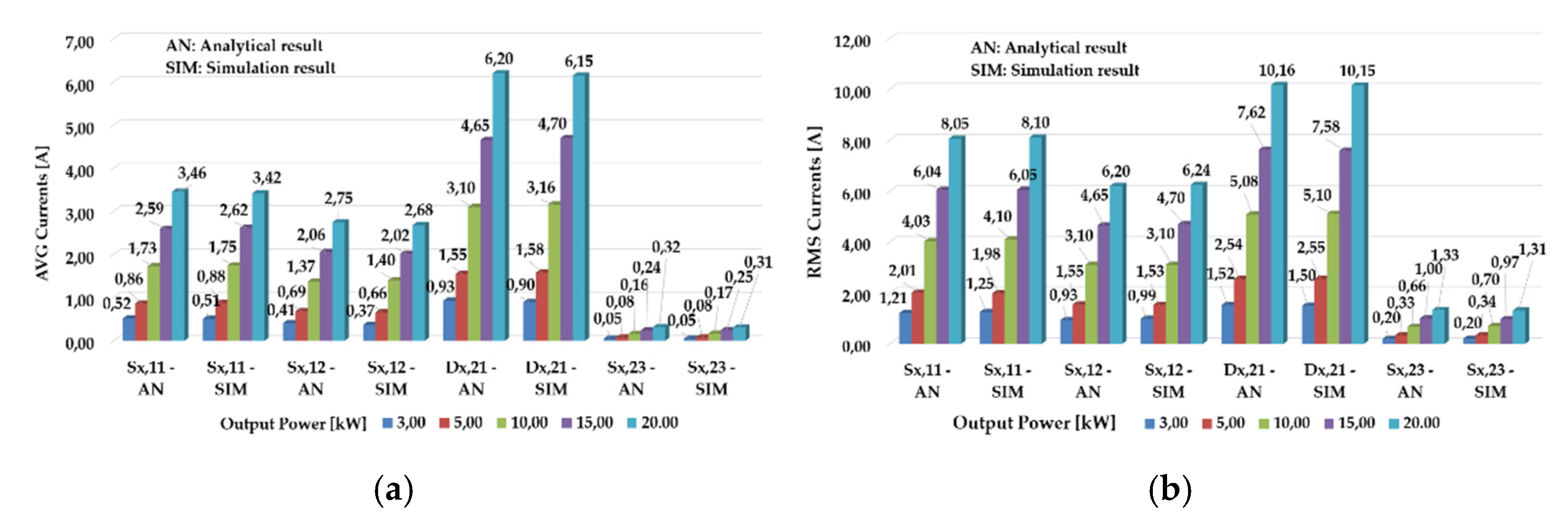

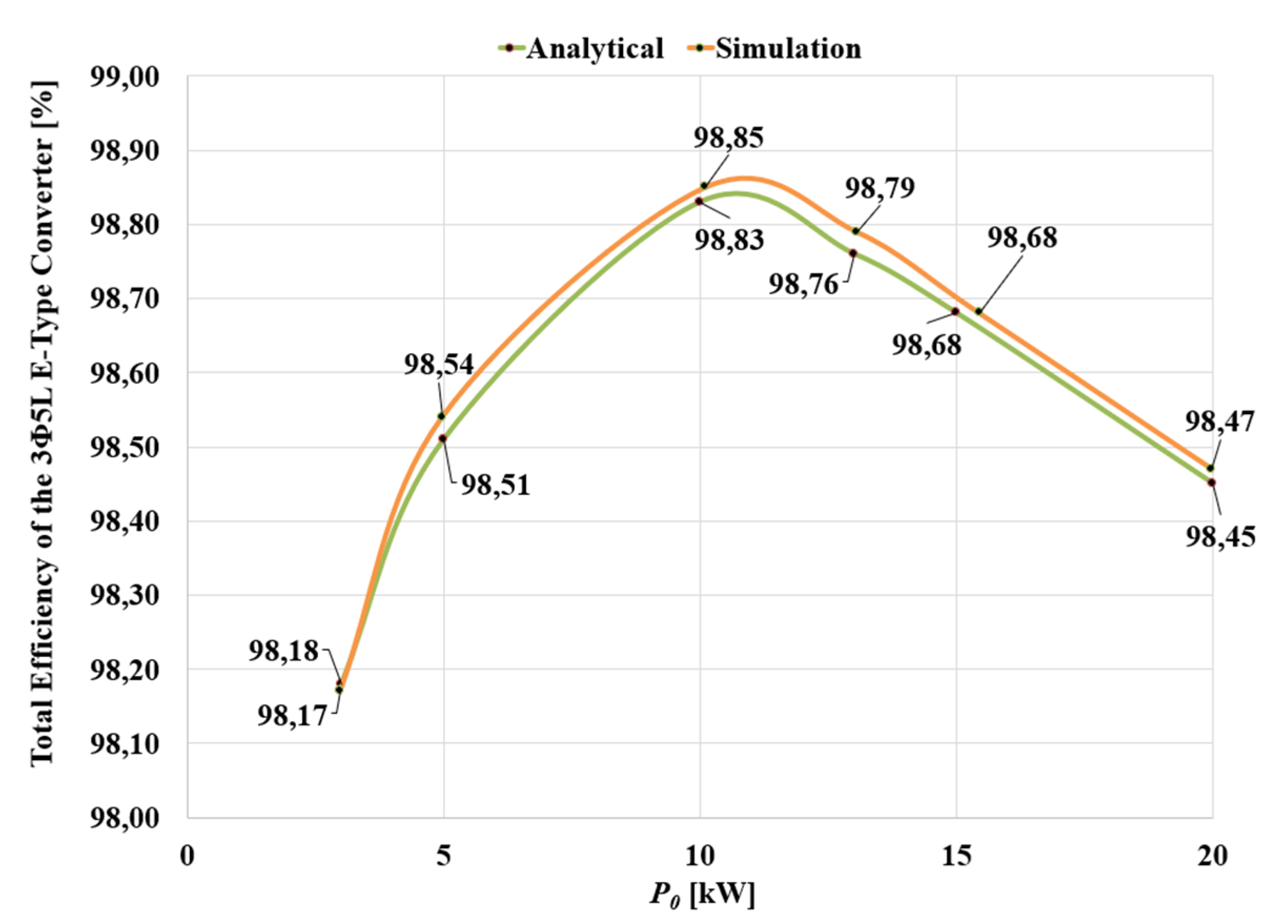

5. Simulation Results

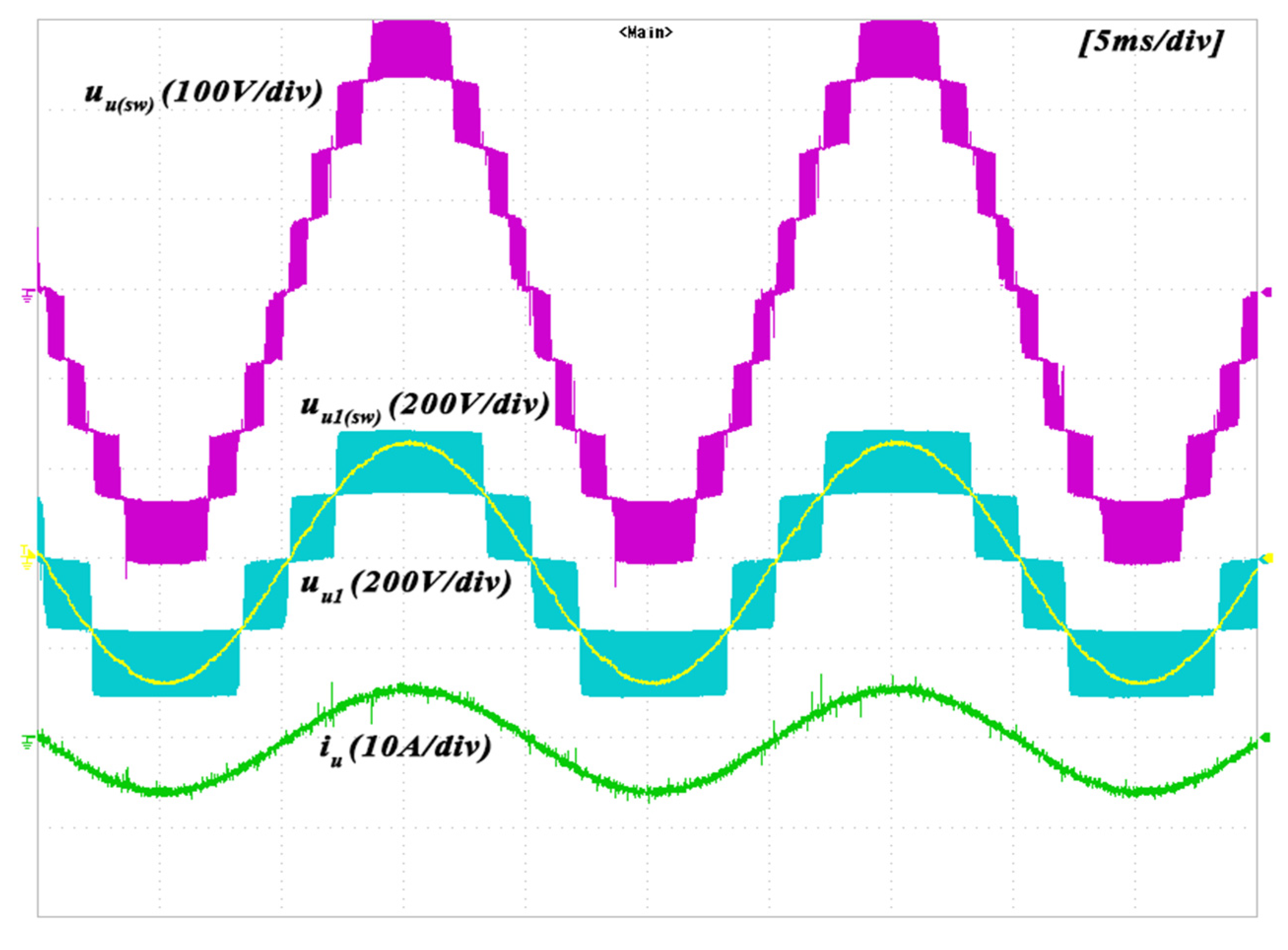

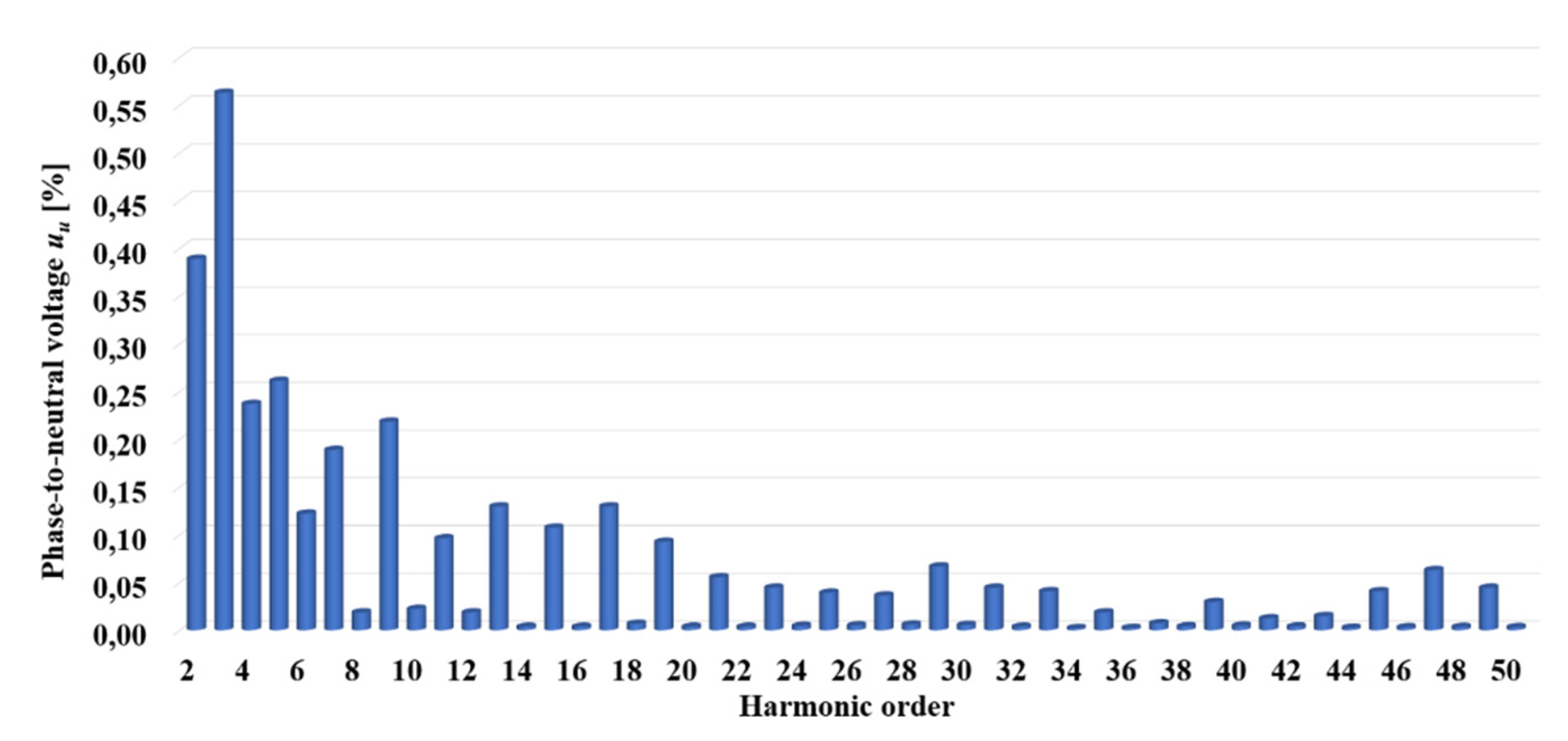

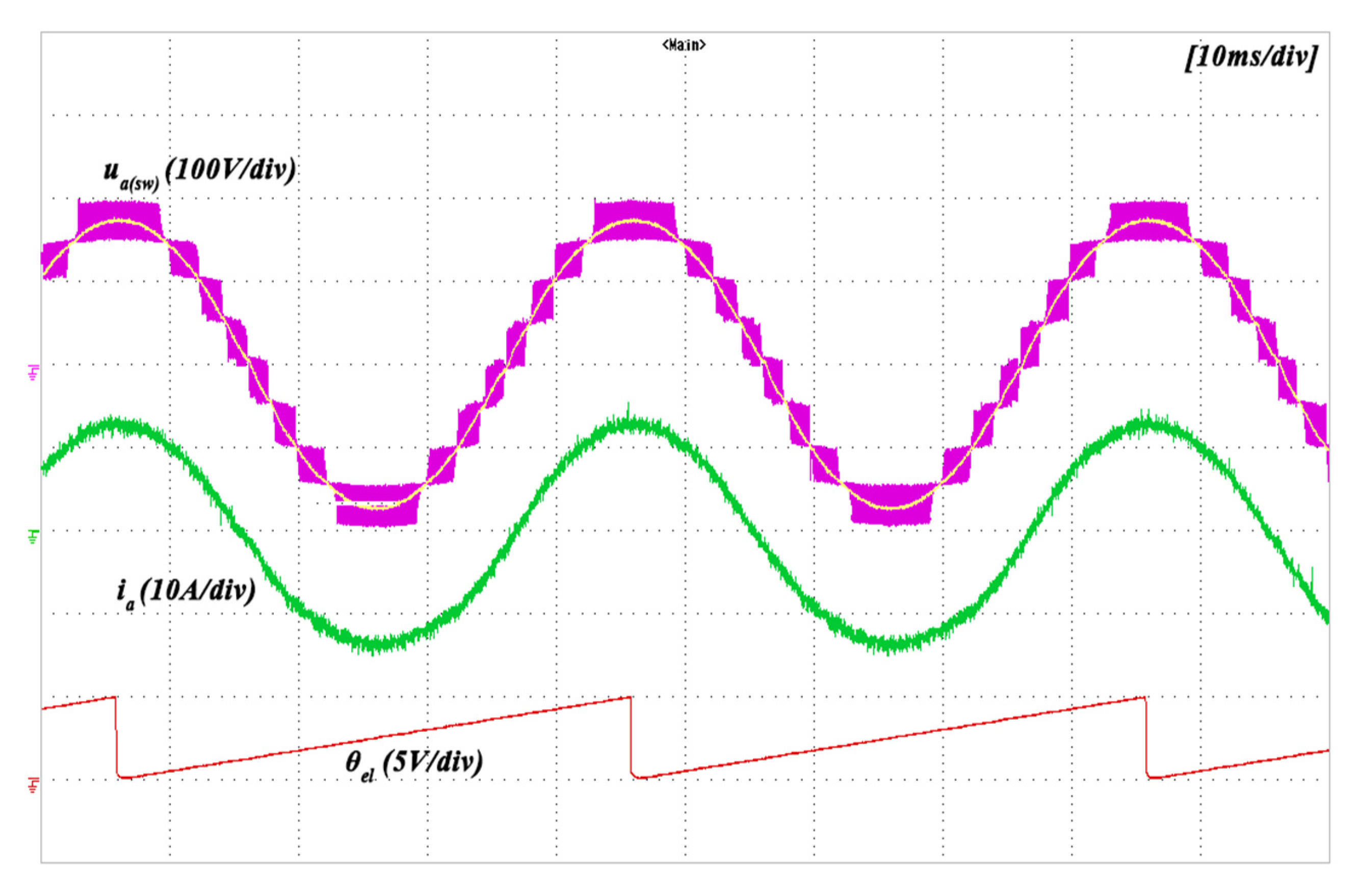

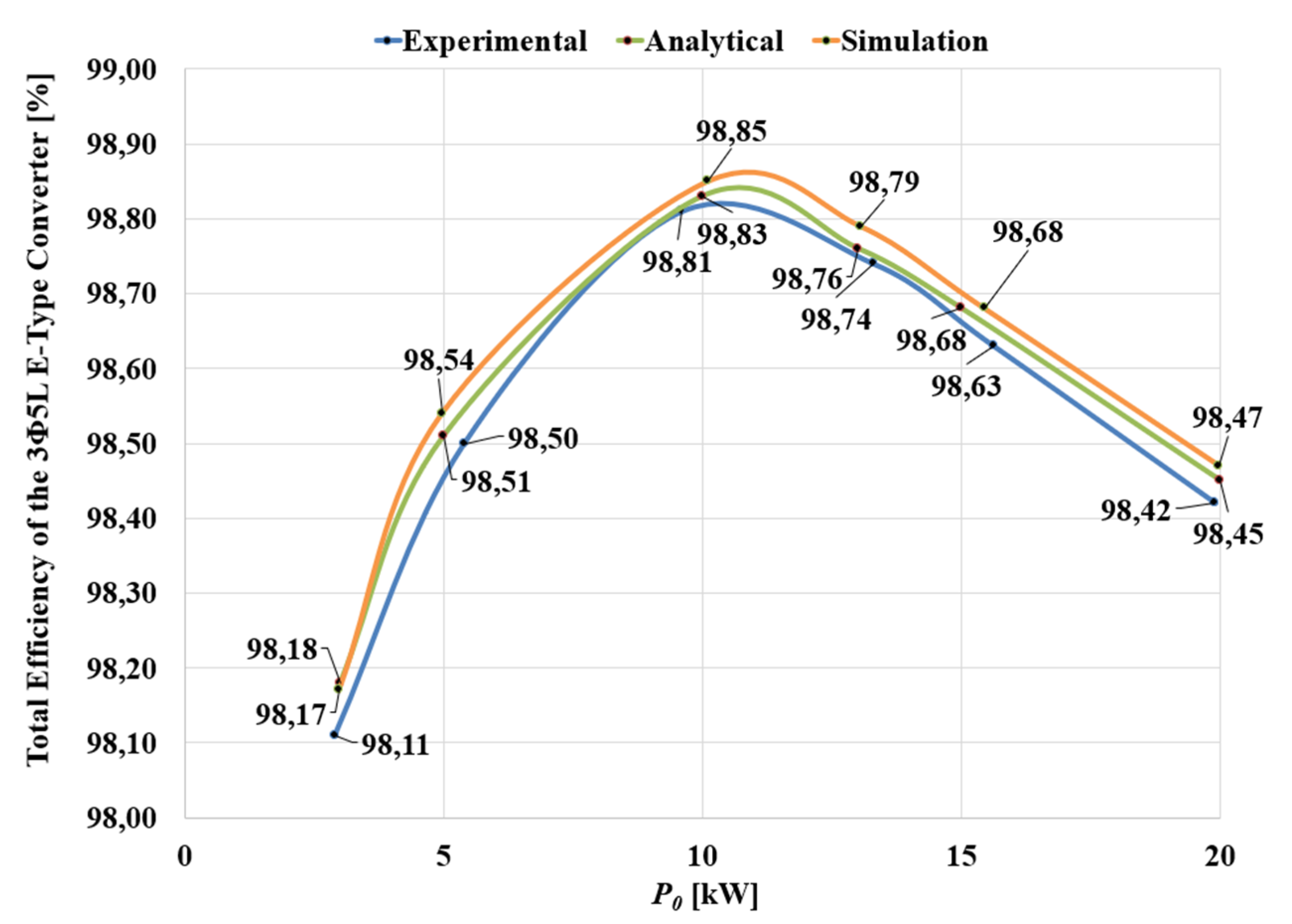

6. Experimental Results

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Appendix A

| i | Power Semiconductor | Coefficients |

|---|---|---|

| 1 | Dx,21, Dx,22 | |

| 2 | Sx,11, Sx,32 | |

| 3 | Sx,12, Sx,31 | |

| 4 | Sx,23, Sx,24 |

| i | Power Semiconductor | Coefficients |

|---|---|---|

| 1 | Sy,21, Sy,22 | |

| 2 | Sy,11, Sy,32 | |

| 3 | Sy,12, Sy,31 | |

| 4 | Sy,23, Sy24 |

References

- Elavarasan, R.M.; Shafiullah, G.M.; Padmanaban, S.; Kumar, N.M.; Annam, A.; Vetrichelvan, A.M.; Mihet-Popa, L.; Holm-Nielsen, J.B. A Comprehensive Review on Renewable Energy Development, Challenges, and Policies of Leading Indian States with an International Perspective. IEEE Access 2020, 8, 74432–74457. [Google Scholar] [CrossRef]

- Ganesan, S.; Subramaniam, U.; Ghodke, A.A.; Elavarasan, R.M.; Raju, K.; Bhaskar, M.S. Investigation on Sizing of Voltage Source for a Battery Energy Storage System in Microgrid with Renewable Energy Sources. IEEE Access 2020, 8, 188861–188874. [Google Scholar] [CrossRef]

- Kesavan, T.; Sheebarani, S.; Gomathy, V.; Kavin, R.; Sivaranjani, S. Renewable Energy Based on Energy Conservation and Crossover System. In Proceedings of the 2020 6th International Conference on Advanced Computing and Communication Systems (ICACCS), Coimbatore, India, 6–7 March 2020; pp. 155–157. [Google Scholar]

- Guo, Z.; Wei, W.; Chen, L.; Dong, Z.; Mei, S. Impact of Energy Storage on Renewable Energy Utilization: A Geometric Description. IEEE Trans. Sustain. Energy 2020, 1. [Google Scholar] [CrossRef]

- Panigrahi, R.; Mishra, S.K.; Srivastava, S.C.; Srivastava, A.K.; Schulz, N.N. Grid Integration of Small-Scale Photo-voltaic Systems in Secondary Distribution Network—A Review. IEEE Trans. Ind. Appl. 2020, 56, 3178–3195. [Google Scholar] [CrossRef]

- Puchalapalli, S.; Tiwari, S.K.; Singh, B.; Goel, P.K. A Microgrid Based on Wind-Driven DFIG, DG, and Solar PV Ar-ray for Optimal Fuel Consumption. IEEE Trans. Sustain. Energy 2020, 56, 4689–4699. [Google Scholar]

- Salman, U.T.; Al-Ismail, F.S.; Khalid, M. Optimal Sizing of Battery Energy Storage for Grid-Connected and Isolated Wind-Penetrated Microgrid. IEEE Access 2020, 8, 91129–91138. [Google Scholar] [CrossRef]

- Mendola, M.L.; di Benedetto, M.; Lidozzi, A.; Solero, L.; Bifaretti, S. Four-Port Bidirectional Dual Active Bridge Converter for EVs Fast Charging. In Proceedings of the 2019 IEEE Energy Conversion Congress and Exposition (ECCE), Baltimore, MD, USA, 29 September–3 October 2019; pp. 1341–1347. [Google Scholar]

- di Benedetto, M.; Lidozzi, A.; Solero, L.; Crescimbini, F.; Bifaretti, S. Hardware design of SiC-based Four-Port DAB Converter for Fast Charging Station. In Proceedings of the 2020 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 11–15 October 2020; pp. 1231–1238. [Google Scholar]

- Ebrahimzadeh, E.; Blaabjerg, F.; Wang, X.; Bak, C.L. Optimum Design of Power Converter Current Controllers in Large-Scale Power Electronics Based Power Systems. IEEE Trans. Ind. Appl. 2018, 55, 2792–2799. [Google Scholar] [CrossRef]

- Xu, Q.; Jiang, W.; Blaabjerg, F.; Zhang, C.; Zhang, X.; Fernando, T. Backstepping Control for Large Signal Stability of High Boost Ratio Interleaved Converter Interfaced DC Microgrids with Constant Power Loads. IEEE Trans. Power Electron. 2019, 35, 5397–5407. [Google Scholar] [CrossRef]

- Lazarević, V.Ž.; Zubitur, I.; Vasić, M.; Oliver, J.A.; Alou, P.; Patchin, G.; Eltze, J.; Cobos, J.A. High-Efficiency High-Bandwidth Four-Quadrant Fully Digitally Controlled GaN-Based Tracking Power Supply System for Linear Power Amplifiers. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 664–678. [Google Scholar] [CrossRef]

- Yuan, X.; Laird, I.D.; Walder, S. Opportunities, Challenges, and Potential Solutions in the Application of Fast-Switching SiC Power Devices and Converters. IEEE Trans. Power Electron. 2021, 36, 3925–3945. [Google Scholar] [CrossRef]

- Liang, G.; Tafti, H.D.; Farivar, G.G.; Pou, J.; Townsend, C.D.; Konstantinou, G.; Ceballos, S. Analytical Derivation of Intersubmodule Active Power Disparity Limits in Modular Multilevel Converter-Based Battery Energy Storage Systems. IEEE Trans. Power Electron. 2021, 36, 2864–2874. [Google Scholar] [CrossRef]

- Ebrahimi, J.; Karshenas, H. N-Tuple Flying Capacitor Multicell Converter—A Generalized Modular Hybrid Topology. IEEE Trans. Ind. Electron. 2019, 66, 5004–5014. [Google Scholar] [CrossRef]

- Meraj, M.; Bhaskar, M.S.; Iqbal, A.; Al-Emadi, N.; Rahman, S. Interleaved Multilevel Boost Converter with Minimal Voltage Multiplier Components for High-Voltage Step-up Applications. IEEE Trans. Power Electron. 2020, 35, 12816–12833. [Google Scholar] [CrossRef]

- McNeill, N.; Yuan, X.; Anthony, S.P. High-Efficiency NPC Multilevel Converter Using Super-Junction MOSFETs. IEEE Trans. Ind. Electron. 2015, 63, 25–37. [Google Scholar] [CrossRef]

- McNeill, N.; Yuan, X.; Jin, B. A Super-Junction MOSFET-Based 99%+ Efficiency T-Type Multilevel Converter. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018; pp. 5643–5650. [Google Scholar]

- Shi, Y.; Shi, Y.; Wang, L.; Xie, R.; Li, H. A 50 kW high power density paralleled-five-level PV converter based on SiC T-type MOSFET modules. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–8. [Google Scholar]

- Schrittwieser, L.; Leibl, M.; Haider, M.; Thöny, F.; Kolar, J.W.; Soeiro, T.B. 99.3% Efficient Three-Phase Buck-Type All-SiC SWISS Rectifier for DC Distribution Systems. IEEE Trans. Power Electron. 2019, 34, 126–140. [Google Scholar] [CrossRef]

- Zhang, L.; Zheng, Z.; Li, C.; Ju, P.; Wu, F.; Gu, Y.; Chen, G. A Si/SiC Hybrid Five-Level Active NPC Inverter with Improved Modulation Scheme. IEEE Trans. Power Electron. 2019, 35, 4835–4846. [Google Scholar] [CrossRef]

- Di Benedetto, M.; Lidozzi, A.; Solero, L.; Crescimbini, F.; Grbovic, P.J. Reliability and Real-Time Failure Protection of the Three-Phase Five-Level E-Type Converter. IEEE Trans. Ind. Appl. 2020, 56, 6630–6641. [Google Scholar] [CrossRef]

- Deng, F.; Lu, Y.; Liu, C.; Heng, Q.; Yu, Q.; Zhao, J. Overview on submodule topologies, modeling, modulation, control schemes, fault diagnosis, and tolerant control strategies of modular multilevel converters. Chin. J. Electr. Eng. 2020, 6, 1–21. [Google Scholar] [CrossRef]

- Pires, V.F.; Cordeiro, A.; Foito, D.; Pires, A.; Martins, J.; Chen, H. A Multilevel Fault-Tolerant Power Converter for a Switched Reluctance Machine Drive. IEEE Access 2020, 8, 21917–21931. [Google Scholar] [CrossRef]

- Omer, P.; Kumar, J.; Surjan, B.S. A Review on Reduced Switch Count Multilevel Inverter Topologies. IEEE Access 2020, 8, 22281–22302. [Google Scholar] [CrossRef]

- Benedetto, M.D.; Lidozzi, A.; Solero, L.; Crescimbini, F.; Grbovic, P.J. Low-Frequency State-Space Model for the Five-Level Unidirectional T-Rectifier. IEEE Trans. Ind. Appl. 2017, 53, 1127–1137. [Google Scholar] [CrossRef]

- Benedetto, M.D.; Lidozzi, A.; Solero, L.; Crescimbini, F.; Grbovic, P.J. Small-Signal Model of the Five-Level Unidirec-tional T-Rectifier. IEEE Trans. Power Electron. 2017, 32, 5741–5751. [Google Scholar] [CrossRef]

- Di Benedetto, M.; Solero, L.; Crescimbini, F.; Lidozzi, A.; Grbović, P.J. 5-Level E-type back to back power converters—A new solution for extreme efficiency and power density. In Proceedings of the 2017 13th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Giardini Naxos, Italy, 12–15 June 2017; pp. 341–344. [Google Scholar]

- Di Benedetto, M.; Lidozzi, A.; Solero, L.; Crescimbini, F.; Grbovic, P.J. Five-level back to back E-Type converter for high speed gen-set applications. In Proceedings of the IECON 2016—42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016; pp. 3409–3414. [Google Scholar]

- Di Benedetto, M.; Lidozzi, A.; Solero, L.; Crescimbini, F.; Grbovic, P.J. Low Volume and Low Weight 3-Phase 5-Level Back to Back E-Type Converter. IEEE Trans. Ind. Appl. 2019, 55, 7377–7388. [Google Scholar] [CrossRef]

- Di Benedetto, M.; Lidozzi, A.; Solero, L.; Grbovic, P.J.; Bifaretti, S. ISOP DC-DC converters equipped 5-level unidirec-tional T-Rectifier for aerospace applications. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 1694–1700. [Google Scholar]

- Cui, D.; Ge, Q. A Novel Hybrid Voltage Balance Method for Five-Level Diode-Clamped Converters. IEEE Trans. Ind. Electron. 2018, 65, 6020–6031. [Google Scholar] [CrossRef]

- Lin, H.; Shu, Z.; Yao, J.; Yan, H.; Zhu, L.; Luo, D.; He, X. A Simplified 3-D NLM-Based SVPWM Technique with Voltage-Balancing Capability for 3LNPC Cascaded Multilevel Converter. IEEE Trans. Power Electron. 2020, 35. [Google Scholar] [CrossRef]

- Di Benedetto, M.; Lidozzi, A.; Solero, L.; Crescimbini, F.; Grbovic, P.J. Five-Level E-Type Inverter for Grid-Connected Applications. IEEE Trans. Ind. Appl. 2018, 54, 5536–5548. [Google Scholar] [CrossRef]

- Lidozzi, A.; Di Benedetto, M.; Bifaretti, S.; Solero, L.; Crescimbini, F. Resonant Controllers with Three Degrees of Freedom for AC Power Electronic Converters. IEEE Trans. Ind. Appl. 2015, 51, 4595–4604. [Google Scholar] [CrossRef]

- Di Benedetto, M.; Lidozzi, A.; Solero, L.; Crescimbini, F.; Grbovic, P.J. Performance assessment of the 5-level 3-phase back to back E-type converter. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017; pp. 2106–2113. [Google Scholar]

| Device | Part Number | Voltage Rating | Current Rating | Technology | Manufacturer |

|---|---|---|---|---|---|

| 3Φ5L E-Type MMR | |||||

| Sx,11, Sx,12Sx,31, Sx,32 | IPT210N25NFD | 250 V | 69 A | OptiMOSTM 3 | Infineon |

| Dx,21, Dx,22 | IDP30E120 | 1200 V | 30 A | Si Diode | Infineon |

| Sx,23, Sx,24 | IPL60R104C7 | 650 V | 20 A | CoolMOSTMC7 | |

| 3Φ5L E-Type MMI | |||||

| Sy,11, Sy,12, Sy,31, Sy,32 | IPT210N25NFD | 250 V | 69 A | OptiMOSTM 3 | Infineon |

| Sy,21, Sy,22 | IKW40N120H3 | 1200 V | 40 A | IGBT H3 | Infineon |

| Sy,23, Sy,24 | IKW20N60T | 600 V | 20 A | Trenchstop™ IGBT | Infineon |

| 3Φ5L E-Type MMR | 3Φ5L E-Type MMI | |

|---|---|---|

| DC-Bus voltage | VBUS = 600 V | VBUS = 600 V |

| Switching frequency | fsw = 20 kHz | fsw = 20 kHz |

| Fundamental frequency | fin = 100 Hz | f0 = 50 Hz |

| Modulation depth | M0R = 0.93 | M0I = 0.93 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

di Benedetto, M.; Lidozzi, A.; Solero, L.; Crescimbini, F.; Grbović, P.J. High-Performance 3-Phase 5-Level E-Type Multilevel–Multicell Converters for Microgrids. Energies 2021, 14, 843. https://doi.org/10.3390/en14040843

di Benedetto M, Lidozzi A, Solero L, Crescimbini F, Grbović PJ. High-Performance 3-Phase 5-Level E-Type Multilevel–Multicell Converters for Microgrids. Energies. 2021; 14(4):843. https://doi.org/10.3390/en14040843

Chicago/Turabian Styledi Benedetto, Marco, Alessandro Lidozzi, Luca Solero, Fabio Crescimbini, and Petar J. Grbović. 2021. "High-Performance 3-Phase 5-Level E-Type Multilevel–Multicell Converters for Microgrids" Energies 14, no. 4: 843. https://doi.org/10.3390/en14040843

APA Styledi Benedetto, M., Lidozzi, A., Solero, L., Crescimbini, F., & Grbović, P. J. (2021). High-Performance 3-Phase 5-Level E-Type Multilevel–Multicell Converters for Microgrids. Energies, 14(4), 843. https://doi.org/10.3390/en14040843