1. Introduction

Due to excellent soft switching characteristics such as primary-side zero-voltage switching (ZVS) and secondary-side zero-current switching (ZCS),

LLC resonant converters are widely used in many areas such as electric vehicles, servers, uninterruptible power supplies, and TV power adapters. Furthermore, with regard to an

LLC resonant converter operating at a high switching frequency, the power density can be greatly improved due to the reduction in the size of the passive element [

1,

2]. However, because the output voltage is controlled through frequency variations, a wide range of frequency sweeps is required in a wide input/load variation system, making it difficult to design optimal passive devices [

3]. In addition, because most resonant converters developed thus far are based on a frequency-controlled two-level topology, they are not widely used in high-power systems with very high input voltages, such as railroad vehicles, due to the limited endurance voltage of the switching devices. Currently, as part of the effort to replace the existing low-frequency transformers, resonance topology-based power converters are widely applied to the auxiliary power systems of railway vehicles, with most being composed of two stages. One type is an

LLC resonant converter controlled in an open loop with a fixed operating frequency, and the other is a constant-voltage regulator connected before or after the

LLC converter, which also serves to provide proper voltage for the normal operation of the

LLC resonant converter. This complicates the overall system configuration [

4,

5].

Meanwhile, multilevel converters have been studied extensively in an effort to overcome the limitations of the two-level topology [

6,

7,

8,

9,

10]. The multilevel converter, as exemplified by the diode-clamped method, the flying capacitor method, and the cascaded H-bridge, can be applied to a high-voltage, high-power system with devices with low withstand voltages. It also has the advantage of a low harmonic content and low

dv/

dt generation. Among these three, in a system that receives power from a single external power supply line such as a railroad vehicle, the diode-clamped topology with a simple power stage configuration is suitable. However, with diode-clamped topologies, it is not easy to balance the DC link capacitor voltages to ensure equal voltage sharing and good performance, especially for level four and higher. Over the past three decades, numerous researchers have attempted to find appropriate modulation strategies to solve the voltage balance problem in a three-phase diode-clamped multilevel converter [

11,

12,

13,

14]. The addition of an external circuit to compensate for voltage deviations and a hybrid method that utilizes a diode-clamped circuit and a flying capacitor together both complicate the system and are not cost effective [

15,

16,

17]. Recently, the voltage imbalance problem of a three-phase diode-clamped DC/AC inverter with three or more levels was resolved using a virtual vector scheme [

18,

19,

20]. The voltage imbalance was eliminated by combining reference vectors whose associated current sum is zero with the aid of a virtual reference vector. However, in a three-phase system, the amount of calculation is increased because the phase angle as well as the magnitude of the reference voltage must be considered. In addition, it is not easy to find an optimal switching pattern due to the considerable redundancy of the switching pairs. The increased switching loss compared to the general space vector pulse-width modulation (SVPWM) scheme is another issue. Recently, carrier-overlapped PWM (COPWM) applicable to diode-clamped multilevel inverters was proposed [

21]. With multiple carrier-based modulation, it can control capacitor voltage deviation while maintaining volt-second balance in a diode-clamped multilevel inverter with four or more levels. However, this method is effective under ideal conditions and requires a little complex closed-loop control under non-ideal conditions and increases switching losses compared to the conventional single-carrier method [

22]. As previously discussed, most of the multilevel topologies known to date have been applied to three-phase inverter systems. Therefore, in order to apply the diode-clamped multilevel topology to the single-phase DC/DC converter, a new switching modulation technique is required that can effectively eliminate voltage deviations in series-connected DC link capacitors while simultaneously controlling the output voltage simply in a closed-loop control manner.

A multi-phase, multi-level

LLC converter with a two-level topology-based modular structure has been proposed for high-voltage and high-power systems [

23]. Because it is based on the existing frequency modulation method, it is difficult to optimally design passive components under wide input/load variation conditions. Additionally, a separate resonance tank is required for each sub-module, increasing the required number of passive elements. A suitable solution for voltage deviation between series-connected DC link capacitors has not been proposed. Input-series-output-parallel (ISOP) topology based on a two-level DAB converter can handle high voltage and high power [

24]. However, the ISOP topology requires an additional passive element for each sub-module, which complicates the overall system. An additional control algorithm to guarantee a stable operation and an adequate input voltage distribution is also mandatory.

On the other hand, a fixed-frequency three-level full-bridge

LLC resonant converter has been proposed [

25]. The output voltage can be controlled by modulating the magnitude of the fundamental wave component of the voltage input to the resonance tank. However, since it does not operate as a typical diode-clamped topology, it is difficult to control because each switch must be duty-controlled separately. In addition, there is no mention of a DC link voltage deviation problem. Although various modulation techniques have been proposed for the

LLC resonant converter, a suitable method for a diode-clamped multilevel converter with four levels or more has not yet been reported [

26].

Meanwhile, single-phase diode-clamped multilevel AC/DC and DC/AC converters based on MNRV DPWM were proposed recently [

27,

28]. This MNRV DPWM is characterized by the presence of several adjacent reference vectors with different capacitor charging/discharging characteristics depending on the position of the command voltage in order to offset the voltage deviation of series-connected DC link capacitors and to match the magnitude of the command voltage on average. However, because AC/DC and DC/AC converters use a relatively low fundamental frequency to utilize a commercial grid or drive a motor, they use a relatively high frequency modulation index (

mf) to reduce capacitor voltage fluctuations due to the limited capacitance. To apply this MNRV DPWM to a DC/DC converter, some modifications of the modulation strategy are required, as in [

29].

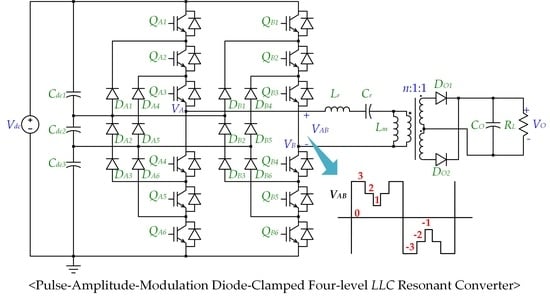

Based on [

29], this paper presents a novel switching modulation scheme suitable for single-phase full-bridge diode-clamped multilevel

LLC resonant converters with an addition of detailed circuit analysis, various types according to the carrier deformation, loss analysis, and experimental results. By using the linear amplitude modulation characteristics of the proposed diode-clamped multilevel converter, an

LLC resonant converter based on voltage amplitude modulation with a fixed switching frequency at the resonant point is proposed, thus enabling an optimal passive device design and ensuring stable operation over a wide operating range. In addition, capacitor voltage deviation compensation is implemented using only

mf = 2 owing to the high fundamental switching frequency of the DC/DC converter. The proposed method utilizes only the clamped switching pair based on DPWM to facilitate the design of the switching pattern and reduce the switching losses. This paper briefly introduces a modified MNRV DPWM suitable for DC/DC converters, analyzes the operating characteristics of the proposed voltage-magnitude-modulation-based diode-clamped multilevel

LLC resonant converter, and presents design guidelines. In addition, various types of

LLC resonant converters are examined according to the deformation of the carrier. The performance and feasibility of the proposed converter are verified through simulations and experiments.

2. General Approach: Multi-Neighboring Reference Vector Discontinuous PWM (MNRV DPWM)

Figure 1 shows the circuit diagram of the single-phase diode-clamped four-level PWM converter. The AC voltage source

VS supplies input power to the full-bridge switching stack through boost inductor

LB with an equivalent series resistance of

RB. The full-bridge switching stage is composed of the switches

QA1~

QA6 and

QB1~

QB6 and the clamping diodes

DA1~

DA6 and

DB1~

DB6. The output DC link stage consists of three series-connected capacitors,

Cdc1,

Cdc2, and

Cdc3.

RL implies output load resistance.

Figure 2a shows the switching pairs of A and B legs and the capacitor charging/discharging status according to the position of the command voltage

VC* of the single-phase diode-clamped four-level PWM converter. In the full-bridge four-level topology,

0,

E, 2

E, and 3

E imply reference vectors representing each step voltage that can be output as a leg-to-leg voltage. The numbers in parentheses refer to switching pairs (AB) that can express the reference vectors, and

C and

D positioned to the right of them are the charging and discharging states of the capacitor, respectively. For example, if

VC* is located at ②, in carrier-based sinusoidal pulse-width modulation (CB-SPWM), adjacent reference vectors are

E and 2

E, and (AB) expressing

E has redundancy via (10), (21), and (32). With regard to (10), the charging/discharging state of the three capacitors connected in series as the top capacitor (

Cdc1), intermediate capacitor (

Cdc2), and bottom capacitor (

Cdc3) is

DDC, which means that that

Cdc1 and

Cdc2 are discharging and

Cdc3 is charging. For CB-PWM, which is widely used in single-phase AC/DC converters, two reference vectors adjacent to

VC* are selected and their duration is adjusted to satisfy the magnitude of

VC* and generate a symmetrical PWM pattern to minimize the ripple, as shown in

Figure 2b. However, from level 4 or higher, a voltage imbalance inevitably occurs due to the limited selectable reference vectors capable of actively controlling the charging/discharging state of the capacitors. In particular, when the unity power factor is controlled as in the PWM converter, the voltage of the middle capacitor among the capacitors constituting the DC link stage is excessively charged compared to the other capacitors. This occurs because the charging/discharging behavior cannot be actively controlled with only two adjacent reference vectors.

When (AB) is (20), (30), and (31), the capacitor charging/discharging states are

DCC,

CCC, and

CCD, respectively, and it can be confirmed that

Cdc2 is always in the charged state. In particular, for a PWM converter in which the phase difference between

VC* and the input current is small, the capacitor charging current is largest when

VC* is located in ① (large vector region (LRV)); moreover, even if

VC* is located in different regions such as ② and ③ (the small vector region (SVR)), this overcharged state is not overcome, and the voltage deviation intensifies. Due to the characteristics of the diode-clamped multilevel converter, if the switching state is implemented by selecting two adjacent vectors as in the conventional CB-SPWM, the voltage deviation of the capacitor cannot be eliminated.

Figure 3 shows the voltage imbalance problem of the PWM converter when applying CB-SPWM.

VS is the input voltage source;

IS is the input current; and

Vdc1,

Vdc2, and

Vdc3 are the terminal voltages of

Cdc1,

Cdc2, and

Cdc3, respectively.

VAB is the switching leg voltage. As expected, the middle capacitor voltage

Vdc2 increases continually after applying CB-SPWM.

Meanwhile, total harmonic distortion (THD) of the switching leg voltage VAB was analyzed under the following conditions of VS = 220Vrms(60 Hz ac), output voltage Vdc = 500 V, output power PO = 30 kW, source frequency fS = 60 Hz, mf = 55, LB = 4 mH, and RB = 1 mΩ. THD results were 0.23 and 0.43 for the CB-SPWM and the proposed MNRV DPWM, respectively, which reveals the much-increased high-frequency harmonic components of VAB in the proposed method. However, the CB-SPWM-based multilevel converter corresponds to an ideal case that is difficult to implement in practice due to a voltage imbalance problem. When compared with the existing two-level converter, the THD value of MNRV DPWM was reduced by 0.15. On the other hand, the multilevel topology enables the use of the low withstand voltage devices with lower switching losses than higher withstand voltage devices. Therefore, in the proposed method, switching frequency can be further increased, thereby reducing the size of filter for harmonic reduction and facilitating its design.

In order to solve the voltage deviation problem of the single-phase diode-clamped multilevel converter, MNRV DPWM was proposed [

27].

Figure 2c shows the reference vectors selected according to the location of

VC* and the switching pairs that can represent them, also showing the capacitor charging and discharging states according to the clamping mode (CM). When

VC* is located in LVR,

E, 2

E, and 3

E are selected as reference vectors. If

E is selected, which was not chosen in CB-SPWM, (10) and (32) can be utilized, and these switching pairs can serve to discharge

C2 (

DDC,

CDD). Therefore, if

E is used as a reference vector along with 2

E and 3

E, the voltage increase of

C2 can be suppressed, and if the duration times of reference vectors

E, 2

E, and 3

E are properly adjusted, the magnitude of

VC* can be tracked on average. In this paper, to reduce the switching redundancy and minimize the switching loss, the clamped switching states in ±180° DPWM are employed [

30]. This means that only (3×), (×3), (0×), and (×0) are used among all switching pairs that can represent the reference vectors. (3×) and (×3) indicate that legs A or B, respectively, are clamped with a positive DC rail, called the upper clamping mode (UCM), where CM = 1. Similarly, (0×) and (×0) indicate the clamping of legs A or B, respectively, to the negative DC rail, called the lower clamping mode (LCM), where CM = −1. The generation of multiple references to eliminate voltage deviations among DC link capacitors in [

21] is similar to the proposed method. However, MNRV DPWM is used, since

VC* is clamped to the positive or negative DC rail during every half cycle, resulting in the advantage of reducing the switching redundancy and minimizing the switching loss. Meanwhile, in the UCM and LCM, the symmetry of the charging and discharging patterns for the same reference vector are horizontally opposite to each other. For example, (31) and (20) are switching pairs expressing reference vector 2

E in the UCM and LCM, respectively, but the capacitor charging/discharging patterns are symmetric in those opposite to each other as

CCD and

DCC. As a symmetrical characteristic, the charging/discharging characteristics when

VC* is negative are identical to the case when

VC* is positive.

The procedure for calculating the duration time of the MNRV based on the reduced capacitor voltage deviation is as follows. First, Vdc1, Vdc2, and Vdc3 are input. Between Vdc1 and Vdc3, which are the top and bottom capacitor voltages, respectively, we select a voltage with a large absolute difference from the reference value, Vdc_ref/3, which is the target voltage of the unit capacitor. If the selected voltage is Vdc1 and Vdc_ref/3 − Vdc1 is greater than zero, the UCM is selected. On the other hand, if the difference is less than zero, the LCM is selected. If the selected voltage is Vdc3 and Vdc_ref/3 − Vdc3 is greater than zero, we select the LCM, and if the difference is less than zero, we select the UCM, because when the charging/discharging behavior of the capacitor according to CM is analyzed, for the UCM, Vdc1 tends to increase and Vdc3 decrease, and vice versa in the LCM. When CM is selected, the compensation controller calculates the duty compensation values for the reference vectors proportional to the voltage deviations among the capacitors. In a four-level converter, three capacitors and two voltage-deviation compensators are needed. There are several methods for configuring the controllers implementing the two voltage deviation compensators. Here, two controllers, one compensating for the difference between (Vdc1 + Vdc2)/2 and Vdc3 and the other compensating for that between Vdc1 and (Vdc2 + Vdc3)/2, are used. These design methods are natural charging/discharging characteristics of reference voltage vectors and easy to expand to a general high-dimensional multilevel converter.

As shown in Equation (1), the two compensation controllers output

dcomp12_3 and

dcomp1_23, which are used to compensate for the voltage difference between (

Vdc1 +

Vdc2)/2 and

Vdc3 and the voltage difference between

Vdc1 and (

Vdc2 +

Vdc3)/2, respectively. In Equation (1),

KP and

KI mean the proportional and integral gains of the PI controller, respectively. According to the position of

VC* and CM, the duties of the each MNRV are calculated as follows. If

VC* belongs to the LVR, we select

E, 2

E, and 3

E as the MNRV. Here, with

E as a basic vector for the duty calculation, the duties of the

E, 2

E, and 3

E vectors are calculated as Equation (2). Here,

dE,

d2E, and

d3E are the duties of

E, 2

E, and 3

E, respectively.

VE,

V2E, and

V3E are the voltage levels of

E, 2

E, and 3

E, respectively, meaning

Vdc_ref/3,

Vdc_ref∙2/3, and

Vdc_ref. Equation (2) is applied differently depending on CM, and its meaning is as follows. The duties of the MNRVs must basically satisfy the magnitude of

VC*. At the same time, the voltage deviations among all capacitors are reduced by applying two controller outputs (

dcomp12_3 and

dcomp1_23) differently according to CM. For example, if (

Vdc1 +

Vdc2)/2 >

Vdc3 in the UCM,

dcomp12_3 increases and

d2E decreases. In the UCM,

d2E is the duty of the switching pair (31), which serves to increase

Vdc1 and

Vdc2 and decrease

Vdc3. Therefore,

Vdc1 and

Vdc2 decrease and

Vdc3 increases due to the reduced

d2E. According to the negative feedback,

dcomp12_3 is stabilized and the capacitor voltage deviations are also reduced. The same can be explained in the LCM. Using the previously calculated duties of each reference vector, the PWM command values of each of the switches in the LRV are determined via Equation (3). Here,

Nmax refers to the maximum value at the period of a single carrier considering the DSP implementation. For a positive

VC*, leg A is clamped to the positive DC rail in the UCM and leg B is clamped to the negative DC rail in the LCM.

On the other hand, when VC* is located in the SVR, 0, E, 2E, and 3E are selected as reference vectors for a similar principle. To achieve a smooth transition at the moment of a region change, the range of the reference vectors in SVR must be wider than that of the LVR to increase the common reference vectors between the LVR and SVR. Each duty is calculated as in Equation (4). Here, d0 is the duty of the 0 vector. Using the calculated duties of each reference vector, the PWM command values of each of the switches in the SRV are determined as in Equation (5).

Using the symmetric characteristic of the full-bridge topology, the duties of the MNRVs when

VC* is negative are determined to be identical to those in the positive

VC* case except for the interchange of legs A and B.

The MNRV DPWM applied to a single-phase diode-clamped four-level converter can be expanded to a general diode-clamped

N-level converter as follows. Based on the analysis of the voltage fluctuation characteristics of the DC link capacitors of the reference step voltage vectors, appropriate MNRVs are selected according to the position of

VC* and the capacitor voltage deviation compensation parameters are designed. MNRV selections applied to the five-level, six-level, and general

N-level diode-clamped topologies are shown in

Figure 4.

The general rule for selecting MNRVs according to the VC* position is as follows. Compensation parameters for controlling the voltage deviations of capacitors are N − 2 in the N − level case. First, the charging/discharging states of the capacitors according to the reference step voltage are analyzed as follows. In the N-level case, the maximum step voltage is (N − 1)∙E, and the capacitor charging/discharging state is CC…CC regardless of CM. Because all capacitors are charged with the same amount of current, there is no voltage deviation. The step voltage one step lower is (N − 2)∙E and the capacitor charging/discharging states are CC…CD and DC…CC in the UCM and LCM, respectively. The outermost capacitor is changed to the discharge mode. In the UCM, the capacitor located at the bottom of the DC link stage, and in the LCM, the capacitor located at the top of the DC link stage, change from charging to discharging mode. The next step voltage is (N − 3)∙E, and the capacitor charging/discharging states are CC…CDD and DDC…CC in the UCM and LCM, respectively. That is, whenever the step voltage decreases by one step, it can be seen that the capacitor charging/discharging states change from charging to discharging from the lower end of the DC link stage in the UCM and from the upper end of the DC link stage in the LCM. Applying this to all step voltages, the following rule can be found. The total number of different charging/discharging states of capacitors is 2(N − 2). At this time, there are step voltage pairs in which the sum of two step voltages is (N − 1)∙E, and the capacitor charging/discharging states in the UCM and LCM of these two step voltages are related to the same capacitor voltage compensation parameters with opposite signs. The two step voltages in this case are cross oppositely coupled to each other; therefore, there are N−2 independent capacitor charging/discharging states in the overall step voltage. Thus, N−2 independent dcomp parameters can be generated, i.e., dcomp1_2...(N−1), dcomp12_3...(N−1),..., dcomp1...(N−2)_(N−1). In order to control the capacitor voltage deviation completely regardless of the position of VC*, the MNRV should be selected so that all independent compensation parameters are included. For every VC* location, it is sufficient to set the MNRV such that N−2 independent duty compensation parameters are included in order to eliminate the voltage deviations of all capacitors. However, large fluctuations in the duty compensation value may adversely affect normal operation; i.e., the duty of a particular reference vector can be negative or greater than one due to the addition of duty-compensation parameters. Accordingly, it is better to include all different charging/discharging states of the capacitors for more reliable operation by limiting the duty-compensation effort. Including all capacitor charging and discharging states is good for stable operation but increases the switching losses. However, as will be described later, by designing an appropriate carrier, a voltage-deviation-compensation operation may occur in the ZVS region, thereby minimizing an increase in the switching loss. Because the outermost vectors (0, (N − 1)∙E) do not affect the capacitor voltage deviation, the capacitor-voltage-deviation-compensation parameters are designed from independent capacitor charging/discharging states of the remaining intermediate reference vectors.

In the five-level case, for example, there are three independent charging/discharging states: CDDD(DCCC), CCDD(DDCC), and CCCD(DDDC). The capacitor charging/discharging states of the reference voltages E in the UCM and 3E in the LCM are CDDD and DCCC, respectively. They both can be used to control the voltage deviation between Vdc1 and (Vdc2 + Vdc3 + Vdc4)/3. It can be seen that the charging/discharging states of 2E in the UCM and LCM are CCDD and DDCC, respectively, and are related to the voltage deviations between (Vdc1 + Vdc2)/2 and (Vdc3 + Vdc4)/2. Similarly, the charge/discharge states of 3E in the UCM and E in the LCM are CCCD and DDDC, respectively, and they can be utilized to control the voltage deviation between (Vdc1 + Vdc2 + Vdc3)/3 and Vdc4 with opposite signs. Therefore, in the five-level case, three independent compensation parameters are required to control the capacitor voltage deviation: dcomp1_234, dcomp12_34, and dcomp123_4. They are related to the voltage differences between Vdc1 and (Vdc2 + Vdc3 + Vdc4)/3, (Vdc1 + Vdc2)/2 and (Vdc3 + Vdc4)/2, and (Vdc1 + Vdc2 + Vdc3)/3 and Vdc4, respectively. Therefore, if VC* belongs to the LVR, the range of the MNRV should be E ~ 4E in order to utilize all six different charging/discharging states of the capacitors. On the other hand, if VC* is located in the SVR, the MNRV range should be 0 ~ 3E for the same reason. In addition, when VC* moves between the LVR and SVR, the duties of the reference voltage vectors may suddenly change, which is a factor that degrades the linearity of the output voltage. Therefore, in order to minimize duty changes of the reference voltage vectors and thus ensure smooth transitions between the LRV and SRV, the minimum reference voltage in the LVR and the maximum reference voltage in the SVR should be selected as the basic vector for the MNRV.

In this way, by selecting the MNRV according to the positions of

VC* and designing compensation parameters for the deviations of the capacitor voltages, extension to a high-dimensional

N-level diode-clamped converter is possible. For a general

N-level case, the LRV and SRV range from roundup{(

N − 1)/2}∙

E to (

N − 1)∙

E and from

0 to roundup{(

N − 1)/2}∙

E, respectively. The corresponding MNRVs are from

E to (

N − 1)∙

E and from

0 to (

N − 2)∙

E, as shown in

Figure 4. It should be noted that thus far MNRV DPWM has been described based on the incoming current to the switching legs, as in a PWM converter. Therefore, the charging/discharging states and CM selection should be reversed in DC/DC owing to the reversed reference current direction.