1. Introduction

The demand for step-down DC–DC converters with high power density, high efficiency, lower cost, and volume has progressively increased [

1]. In this scenario, the development of these structures has been driven mainly by the evolution of electric and hybrid vehicles [

2,

3], electric aircraft [

4], the implementation of smart grids [

5], and application in equipment such as voltage regulator modules for microprocessors and data centers [

6,

7], battery chargers [

8] and light-emitting diode lamps [

9,

10]. Although the classic step-down converters have a relatively simple structure and control system, in higher power processing applications, there is a significant current ripple, an increase in semiconductor conduction and switching losses, and a consequent reduction in the overall efficiency of the topology. In this context, researchers have focused on proposing alternatives to overcome the limitations of classic step-down converters, working mainly on the development of non-isolated architectures that, compared to isolated topologies, have the advantage of having higher power density, greater ease of adaptation to different loads and greater efficiency [

11].

Therefore, the interleaved buck converters have been applied for point-of-load (POL), operating normally in hard-switching at low voltage and high current. These converters feature high power density and efficiency, fast transient response, reduced cost, and high reliability. Such advantages result from reducing the components’ current stress and cancelling current ripple in input EMI and output filters [

12,

13,

14].

Despite the advantages mentioned, interleaved buck converters have high sensitivity to the phase errors present in interleaving control, which causes the current imbalance in the converter phases, resulting in the non-elimination of the current fundamental component from the switched operation and in the increase of the volume of the EMI filters. Closed-loop interleaving control can ensure current balance, but it requires that the compensators control the currents of each phase, increasing the control system’s complexity and the converter cost [

13,

14,

15,

16]. In open-loop interleaving control, the compensator regulates the current in one phase, and the same duty cycle and frequency control the other phase. This implementation is simpler, but small parametric variations between the circuit components, including those resulting from the layout design, cause imbalanced average currents in the phases [

16].

Similar to interleaving solutions, the three-state switching cell (3SSC) was introduced in [

17], being an interesting solution for increasing power density with a high-efficiency level and without the need for special control strategies. Since the 3SSC was proposed, a variety of topologies for DC–DC, AC–DC, and DC–AC converters have been presented in the literature [

18,

19,

20,

21,

22]. All of these approaches present interesting advantages inherent to the application of the 3SSC, i.e., reduction of weight and volume of the filter elements, current stress division between the semiconductors, and distribution of the losses, providing the reduction of the heat-sinks size [

23,

24,

25]. Although the 3SSC uses a high-frequency autotransformer, its dimensions are compact because that element operates in two quadrants of the B-H curve [

26]. Furthermore, the operation of the autotransformer naturally doubles the frequency of the inductor current ripple and still ensures that the interleaved currents may be equalized without the need of an active balancer, which does not occur in the classic interleaved converter [

22].

It is noteworthy that most of the applications with 3SSC mainly use the type-B cell (3SSC-B) topology [

27]. It could be associated with the fact that the 3SSC-B-based buck, boost, and buck-boost converters have a static gain identical to the classic non-isolated converters in the whole range of duty cycle when they operate in continuous conduction mode (CCM).

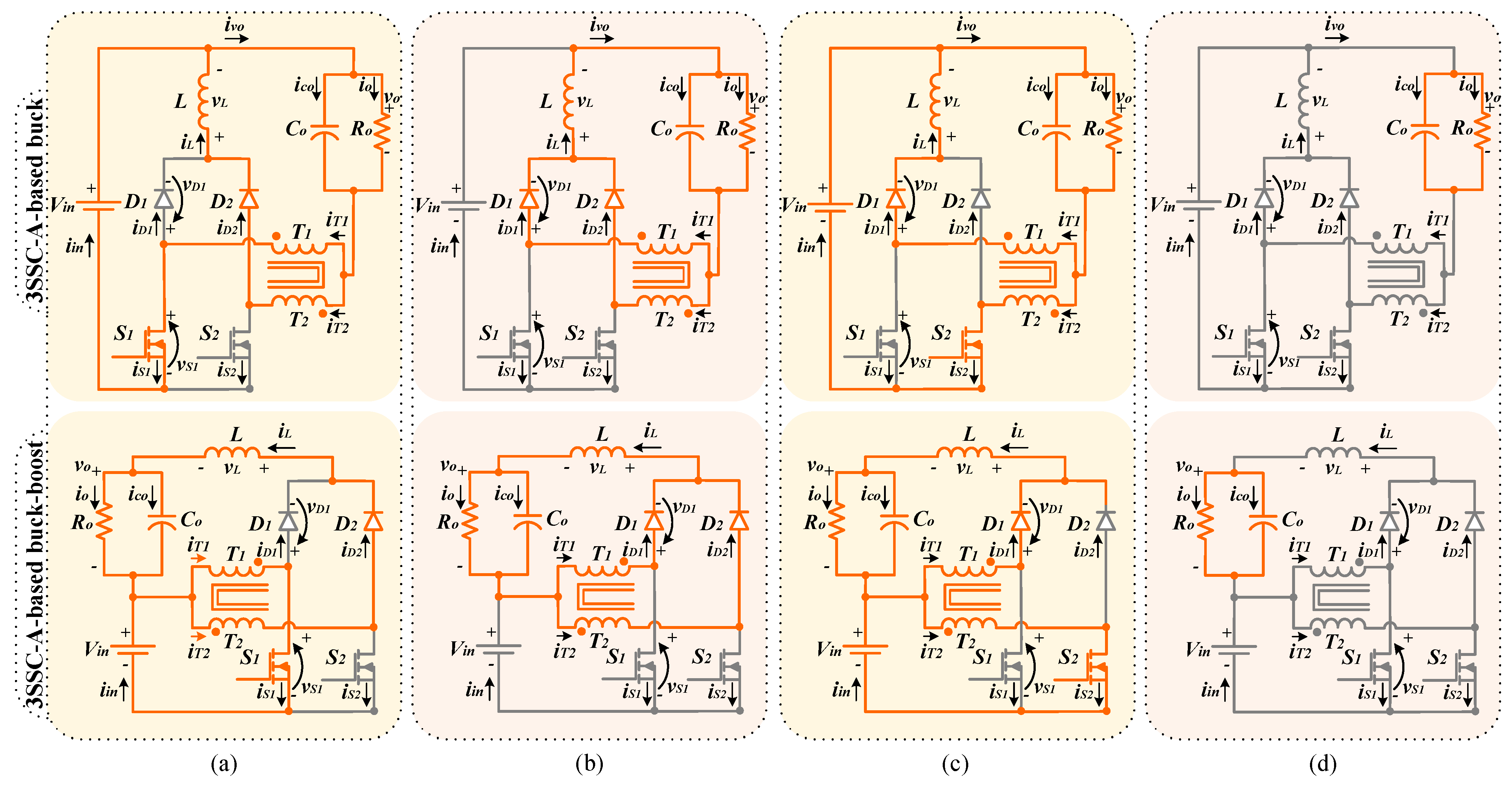

Therefore, taking into account the reduced amount of research that employs the 3SSC-A and the advantages inherent to the 3SCC applications, this paper contributes to the detailed development and the experimental validation of the 3SSC-A-based buck and buck-boost converters, both operating as step-down DC–DC converters.

In this way, completing the initial study presented by the authors in [

28], the proposed research fills a gap related to the exploration and implementation of the 3SSC-A-based DC–DC converters with the following contributions:

A generalized and detailed static analysis of 3SSC-A-based buck and buck-boost DC–DC converters, including highlights of discontinuous conduction mode (DCM) and critical conduction mode (CRM).

A complete theoretical and experimental validation of the loss model for both proposed structures, including a study of voltage and current stresses in semiconductors.

Development and validation of small-signal equivalent models and verification of the dynamic response of the closed-loop control scheme by simulation results.

A detailed experimental validation by implementing prototypes for each proposed converter, operating under several power rangers at the load side.

This paper is organized as follows:

Section 2 describes the analysis of the converters, including loss models, dynamic models, and control systems design.

Section 3 presents the experimental validations, which is followed by the final considerations.

3. Experimental Results

The two proposed converters were designed according to the specifications presented in

Table 5, following the design methodology developed in CCM. The experimental set-up implemented for carrying out the laboratory tests is shown in

Figure 9, with details for the power circuit of the converters.

The main experimental waveforms of the 3SSC-A-based buck converter are shown in

Figure 10.

Figure 10a shows the waveforms of the control signals from switches

and

, current

and voltage

. These results indicate that the converter operates with

D = 0.18 without overlapping the switches’ command signals. Furthermore, it can be verified that the maximum voltage

on the switches is approximately 264 V, which can allow the implementation of components with voltage

in the range of 300 V. The current

grows linearly up to 5 A. Complementarily,

Figure 10b presents the waveforms of voltage and current stress in switches

and

. It is observed that the switches do not conduct simultaneously, evidencing a delay of 180

between the control signals. As with the 3SSCA-based boost topology, the resonance between the leakage inductance of the autotransformer and the collector-emitter capacitance of the IGBT causes the current peaks observed in the currents

and

during the switching turn-on. However, these peaks were minimized with snubber RLD circuits, mitigating the voltage peaks in the switches.

In

Figure 10c, voltage

, currents

, current id1 and current

are shown. The diodes’ voltage stress is around −264 V, which confirms the theoretical analysis. Analyzing the currents

and

, it is verified that the switch

and the diode

operate in a complementary way, evidencing that they do not conduct simultaneously. In addition, observing the waveform of the current

, it is verified that the converter operates in CCM, with a current ripple at 100 kHz, that is, twice the switching frequency of the switches with an average value of 4.6 A. Additionally, it can be seen that diodes

and

conduct simultaneously when the current

decreases linearly, that is, the current through each diode is equivalent to half the inductor current at this instant, with an average value of 2.3 A. Therefore, due to the characteristic of 3SSC, the division of current efforts between these semiconductors naturally occurs.

Figure 10d shows the waveforms of input current

, current

and voltages

and

. These results demonstrate the characteristic of the converter operating as a voltage step-down, with an average output voltage

at 48 V, according to the desired voltage gain. Similar to the classic buck converter, the 3SSC-A-based buck structure generates a pulsating ripple current

with high

/

. In addition, the voltage

, and the currents

and

present a ripple corresponding to twice the switching frequency of the switches, an intrinsic characteristic of the three-state switching cell, which allows the reduction of weight and volume of the energy storage elements of this structure.

In the same way as the one presented for the 3SSC-A-based buck converter,

Figure 11 illustrates the main results obtained during the experimental validation of the 3SSC-A-based buck-boost structure. The waveforms of control signals from switches

and

, voltage

and current

are shown in

Figure 11a. Observing the gate pulses, it is verified that the converter operates without overlapping the command signals, with

D = 0.27. The

voltage stress on switch

is 360V, which is higher than that presented by the 3SSC-A-based buck converter. In a complementary way,

Figure 11b illustrates the current and voltage stress in switches

and

, demonstrating that these semiconductors do not remain in conduction simultaneously, with the 180

delay between the command signals being evident. As in the 3SSC-A-based boost and 3SSC-A-based buck topologies, the interaction between the leakage inductance of the autotransformer and the collector–emitter capacitance of the IGBT results in current peaks observed in currents

and

during the activation of switches, which is a characteristic of the 3SSC-A in these configurations. However, these peaks were also reduced in the 3SSC-A-based buck-boost structure by introducing RLD snubber circuits.

The waveforms of voltage

, current

and currents

and

are illustrated in

Figure 11c. The diodes are subjected to voltage stress equivalent to twice the voltage

, that is, −360 V. Analyzing the currents

and

, it is verified that switch

and diode

do not operate simultaneously, evidencing the complementary operation between these semiconductors. In addition, the current

has a ripple frequency equivalent to 100 kHz, that is, twice the switching frequency, with an average value of 6.25 A, and its format indicates that the converter operates in CCM. Additionally, as in other 3SSC-A-based converters, it is verified that diodes

and

conduct simultaneously when the switches are off, with the current through each of these semiconductors corresponding to half the current

, with a value average of 3.1 A; therefore, there is a division of the current stresses.

The waveforms of voltage

, voltage

, current

and input current

are shown in

Figure 11d. These results confirm the step-down characteristic of the converter, with

at 96 V. Analogously to the classical buck-boost and 3SSC-A-based buck structures, the current

of the 3SSC-A-based buck-boost converter also shows a pulsating ripple with high

/

. However, in contrast to the classic buck-boost converter, the 3SSC-A-based buck-boost structure has an inductor connected to the output, presenting reduced current ripple, as can be seen in

, which considerably decreases the RMS current in the output capacitor. Additionally, still, through

Figure 11d, it can be seen that both currents

and

, as well as voltage

present ripple equivalent to twice the switching frequency, which allows weight reduction and volume of energy storage elements.

Figure 12 presents the closed-loop operation of the converters. As can be seen in the experimental results of the 3SSC-A-based buck converter in

Figure 12a, the output voltage remains at 48 V for the load steps from 100% power to 50% and from 50% to 100%. Similarly, the same load percentage variation was applied to the 3SSC-A-based buck-boost structure, its dynamic response being shown in

Figure 12b, and it can be verified that the output bus is maintained at 96 V.

According to the theoretical model described in

Section 2.4 and the parameters in

Table 5 and

Table 7,

Figure 13 presents the distribution of power losses in converters operating at full load. The total power losses for the 3SSC-A-based buck and 3SSC-A-based buck-boost topologies are approximately 29.3 W and 50.3 W, with a theoretical efficiency of about 91.1% and 92.3%, respectively. It can be observed that in both converters, even with different operating points, the losses in the switches are dominant, contributing to a higher percentage of the total losses. In addition, the converter capacitors’ power loss is highly reduced compared to the other elements.

The efficiency of the experimental prototypes was evaluated in a load range from 16.67% to 100% of the rated load.

Figure 14 presents the normalized practical efficiency of the proposed converters. Both prototypes present performance superior to 85% in the entire defined power range, highlighting, at rated load, the efficiency of approximately 91% for the 3SSC-A-based buck converter and 92% for the 3SSC-A-based buck-boost structure. In contrast to

Figure 13, the measured losses at nominal power are practically identical to the calculated losses. Therefore, there is an experimental validation of the theoretical losses model.

A thermal image of the converters operating at full load is shown in

Figure 15. This result also validates the characterization of losses shown in

Figure 13, proving the distribution of thermal losses between the components caused by the division of current efforts between the semiconductors and, consequently, validating the potential benefits of the application of 3SSC-A in terms of improving the thermal performance in power processing.

4. Conclusions

In this paper, two unexplored topologies based on 3SSC-A for step-down applications were thoroughly analyzed, implemented and experimentally verified. According to the experimental validations, the proposed converters present several advantages compared with the classical topologies, such as reducing current stress between the semiconductors, distribution of power losses between these components, and reducing heat sinks. In addition, the energy storage elements of these topologies operate at twice the switching frequency, allowing weight and volume reduction and, consequently, increased power density. The 3SSC-A-based buck-boost structure presents less current ripple at the load side since the inductor is directly coupled to the output, reducing the RMS current over the capacitor. However, the 3SSC-A-based buck converter presents less voltage stress over the semiconductors. Furthermore, the 3SSC-A-based buck converter has a maximum static gain of half the input voltage, while the theoretical maximum static gain of the 3SSC-A-based buck-boost topology equals the input voltage.

Detailing the loss distribution effects, one can note that the losses in the inductors and autotransformers are very close for the two converters.

Table 2 indicates that the current stresses on these magnetic elements are higher for the 3SCC-A-based buck-boost converter, which would result in a relative increase in copper losses. However, the design specifications presented in

Table 5 indicate that the inductor and autotransformer winding resistances are lower for the 3SCC-A-based buck-boost converter, which justifies the balance of this losses portion between the two topologies. The losses proportion in the switches is slightly higher for the 3SCC-A-based buck-boost converter due to the higher relative current stresses indicated in

Table 4.

Therefore, the power loss characterization of the proposed converters allowed us to conclude that the switches contribute significantly to the power losses of the 3SSC-A converters. Moreover, although the converters were projected at different operating points, both presented a similar power loss distribution with high efficiency, which was around 91% for the 3SSC-A-based buck converter and 92% for the 3SSC-A-based buck-boost converter. Thus, it is up to the designer to analyze the figures of merit of each converter as a starting point for selecting the most suitable topology for a specific application.