Analysis and Design of the Split-Capacitor-Based Sub-Modules Equipped for Hybrid Modular Multilevel Converter

Abstract

:1. Introduction

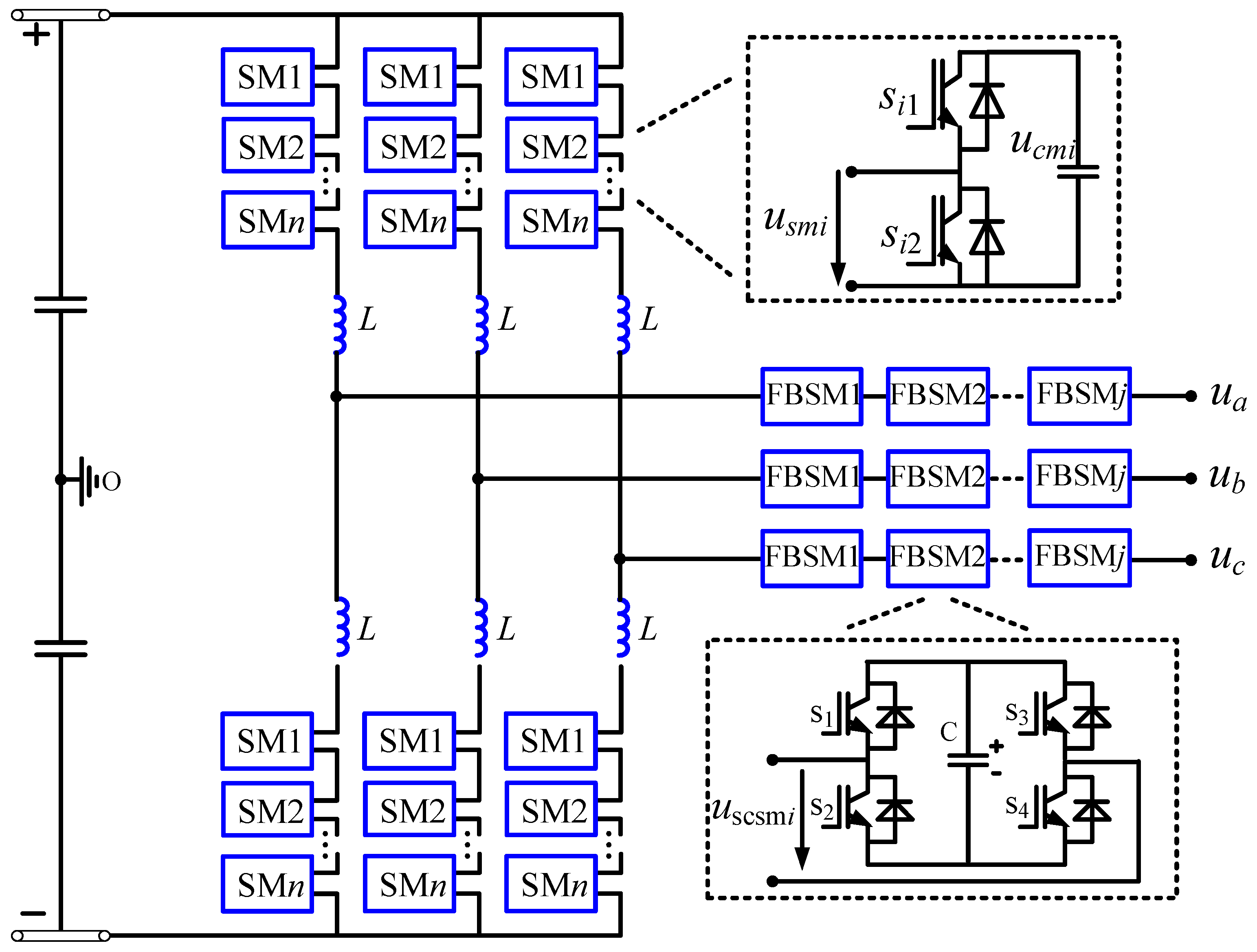

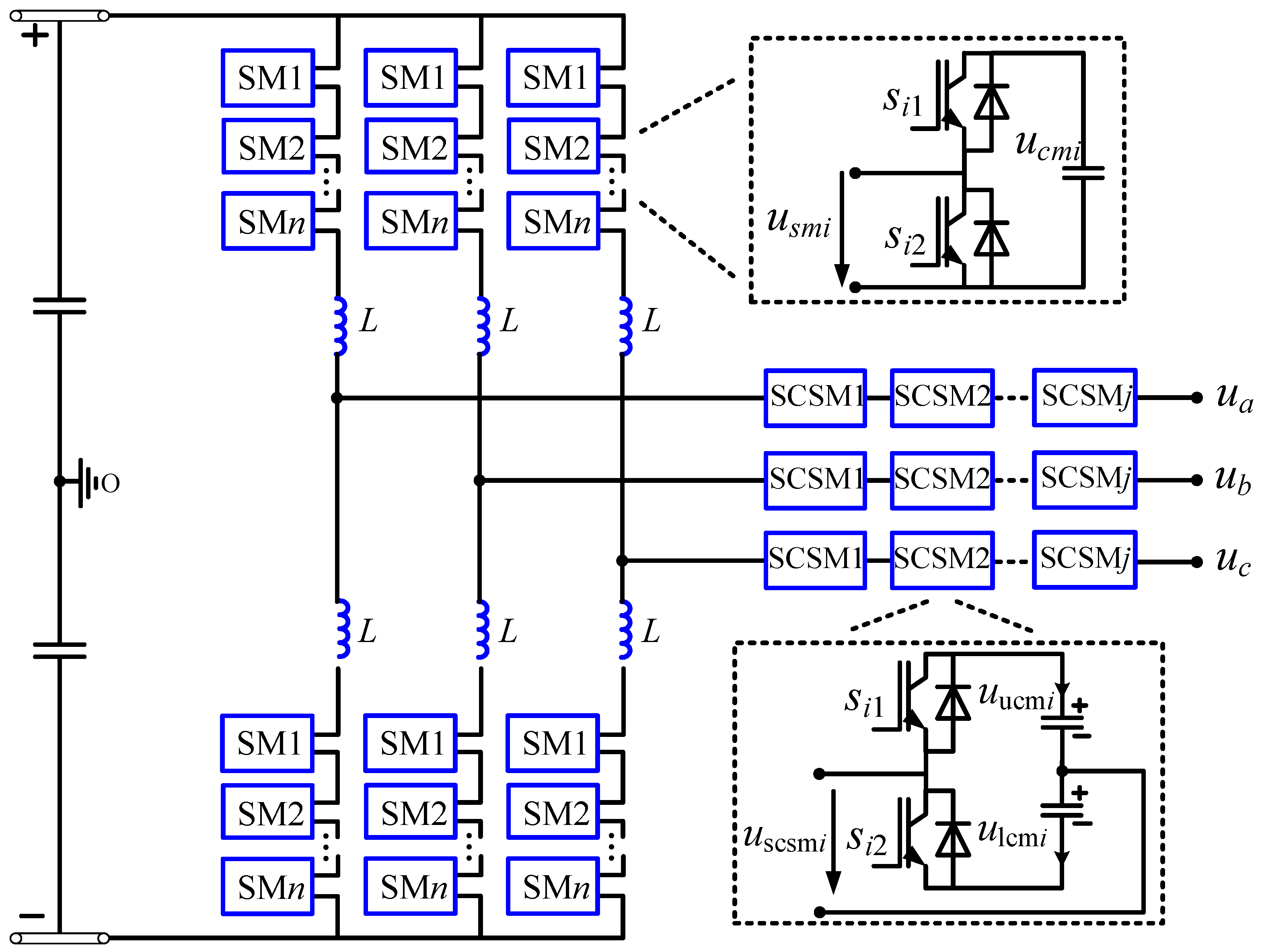

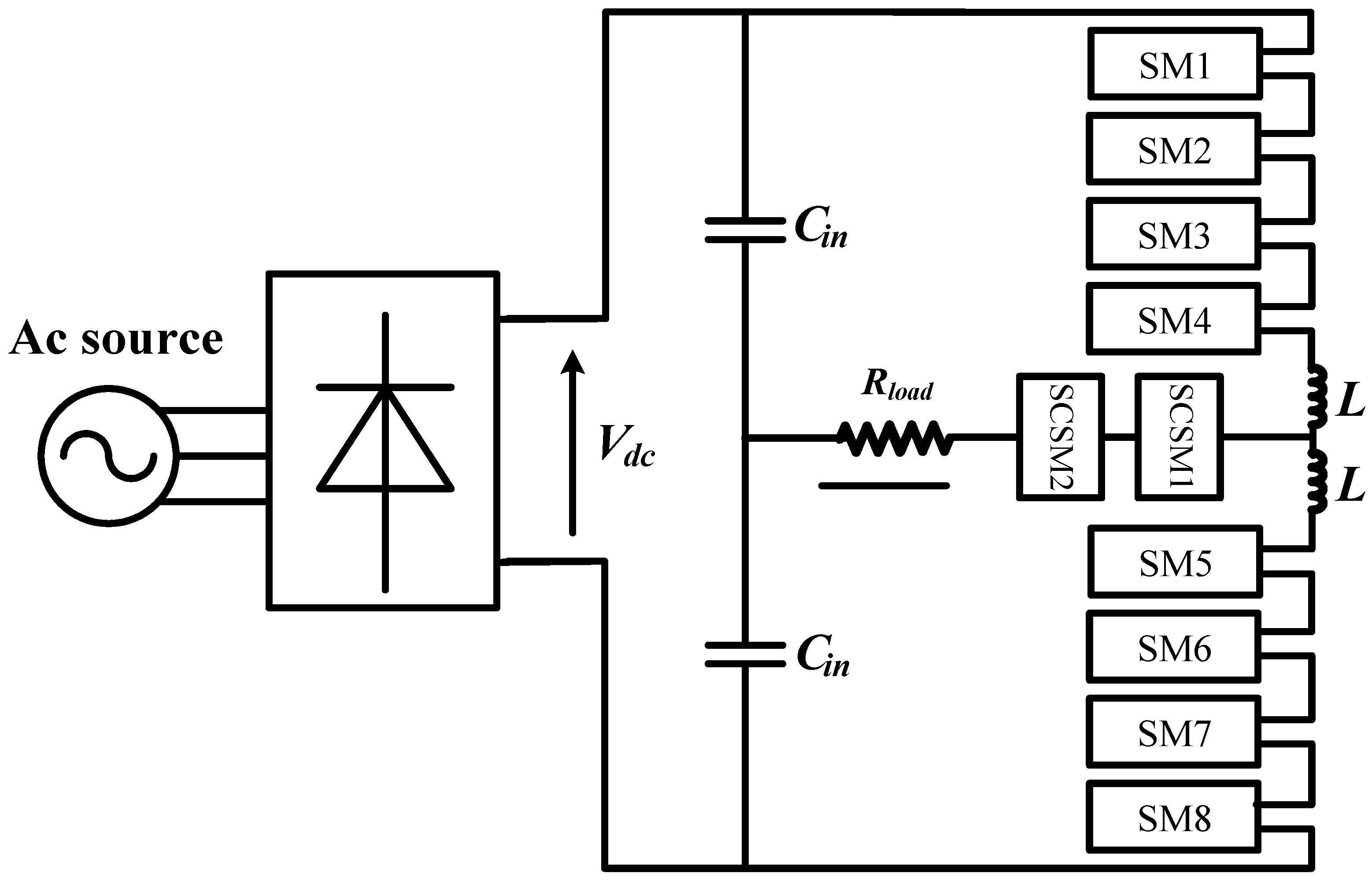

2. Analysis of the Proposed Hybrid MMC Topology

2.1. Basic Structure of the Proposed Hybrid MMC

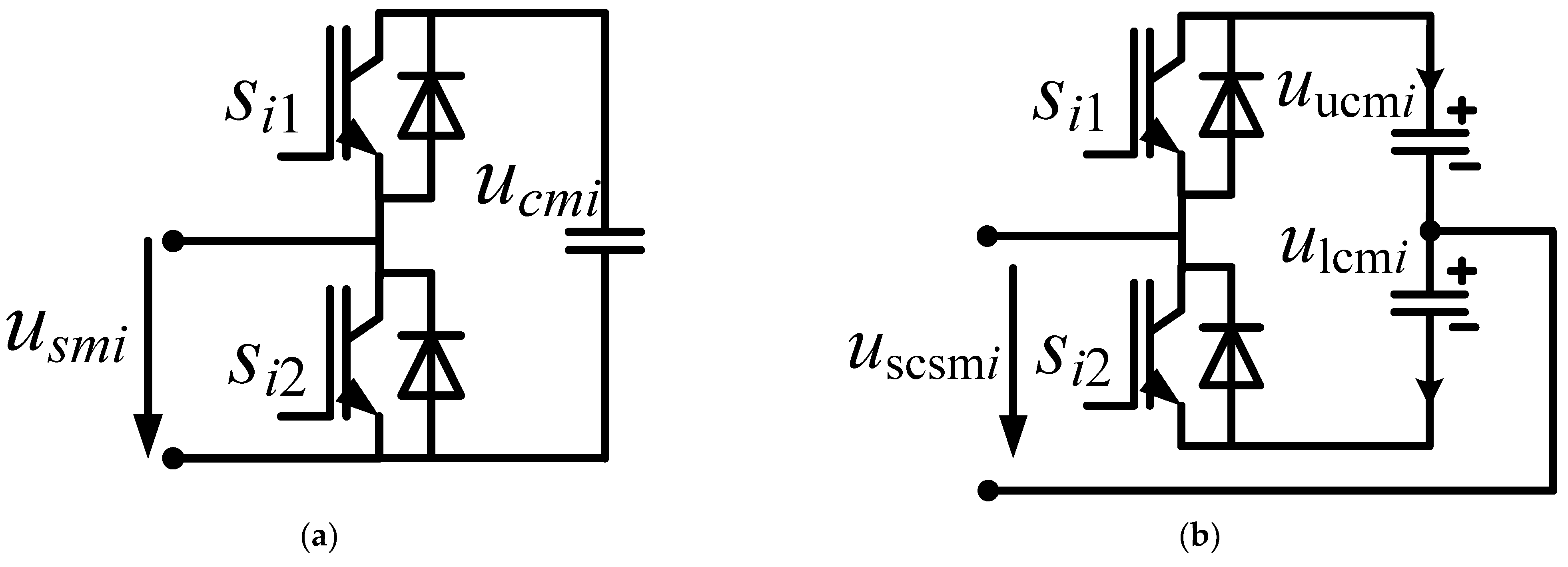

2.2. Model and Analysis of the Proposed SCSM

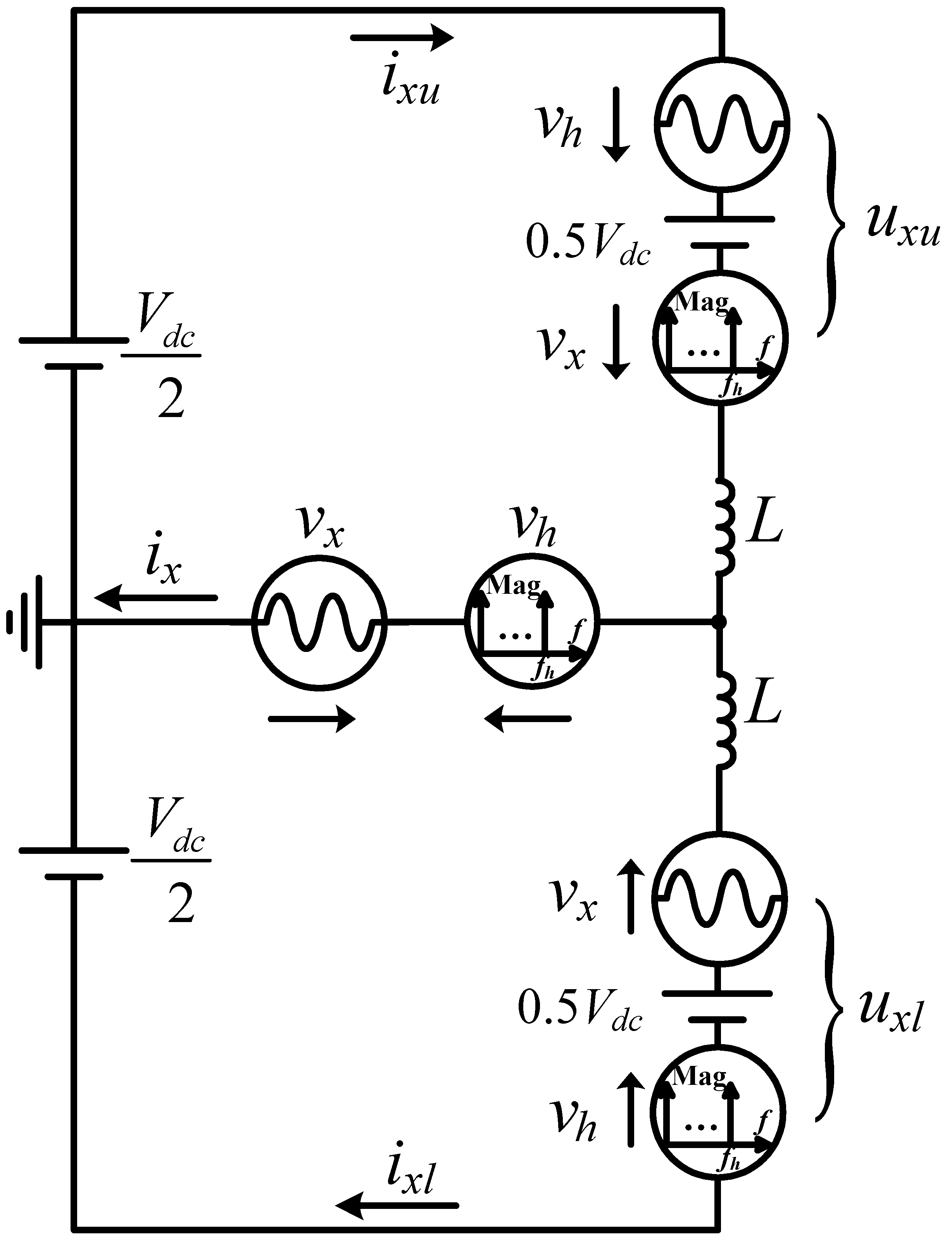

2.3. Model and Analysis of the Proposed Hybrid MMC

3. Control and Analysis of the Proposed Hybrid MMC

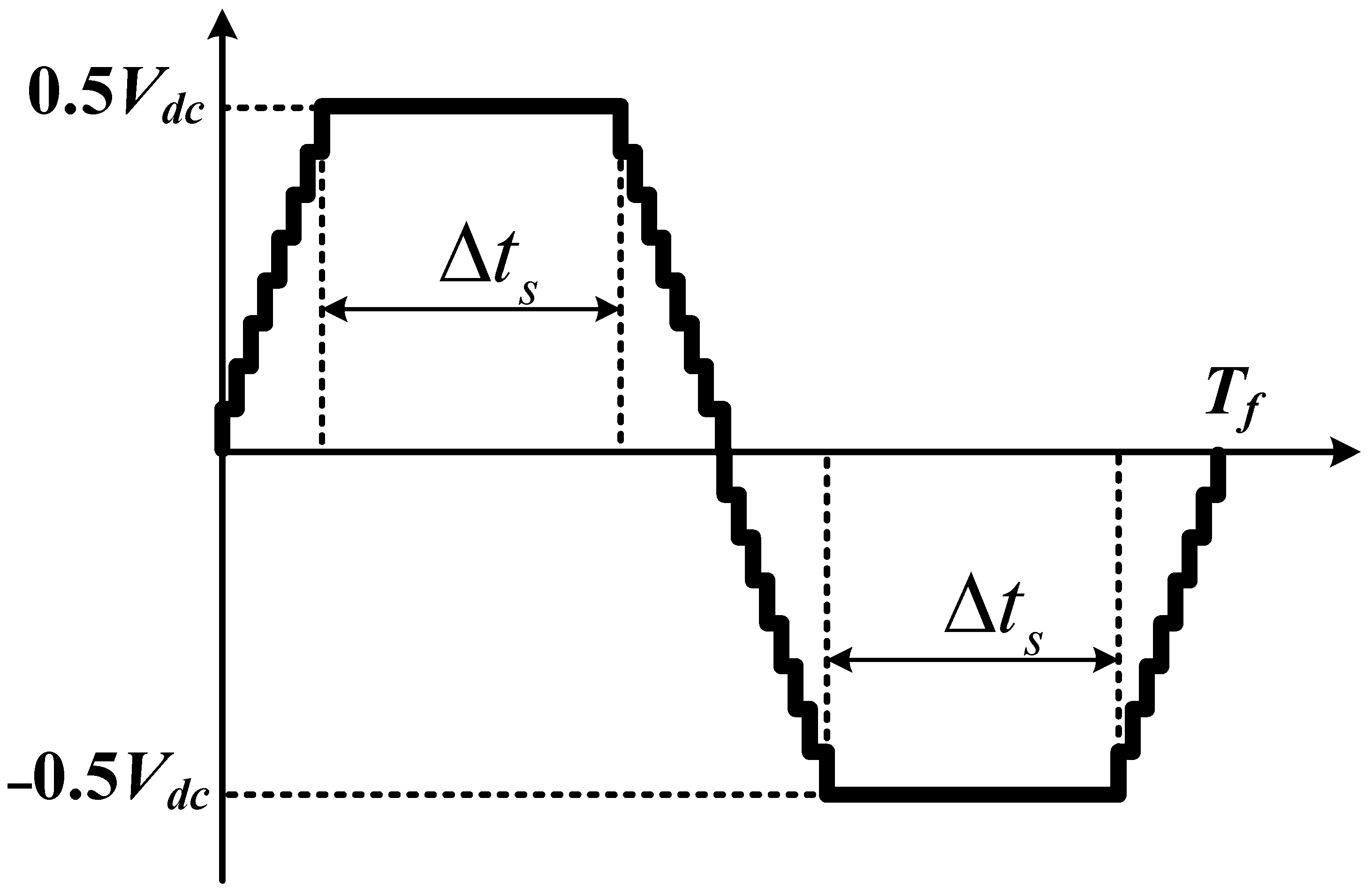

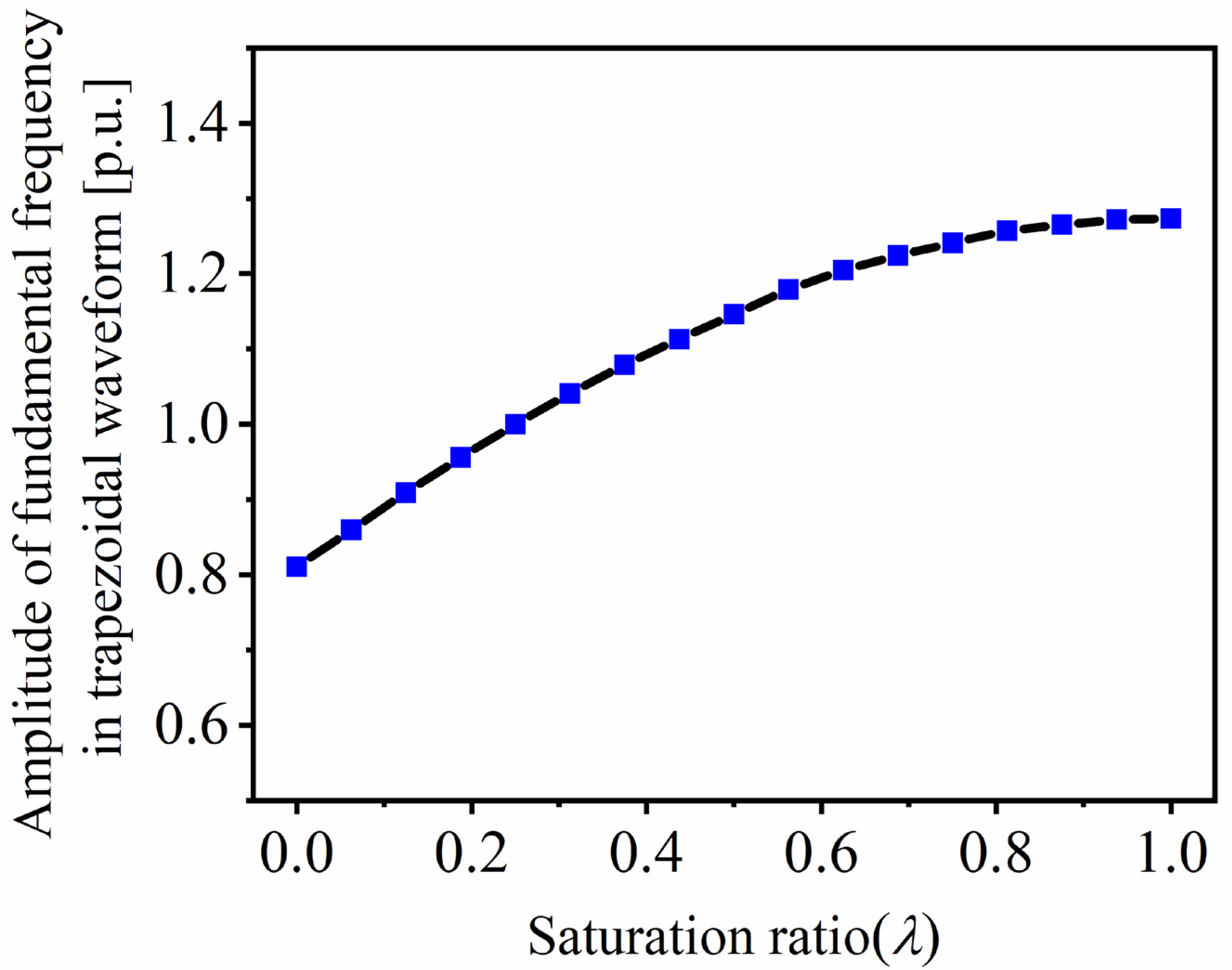

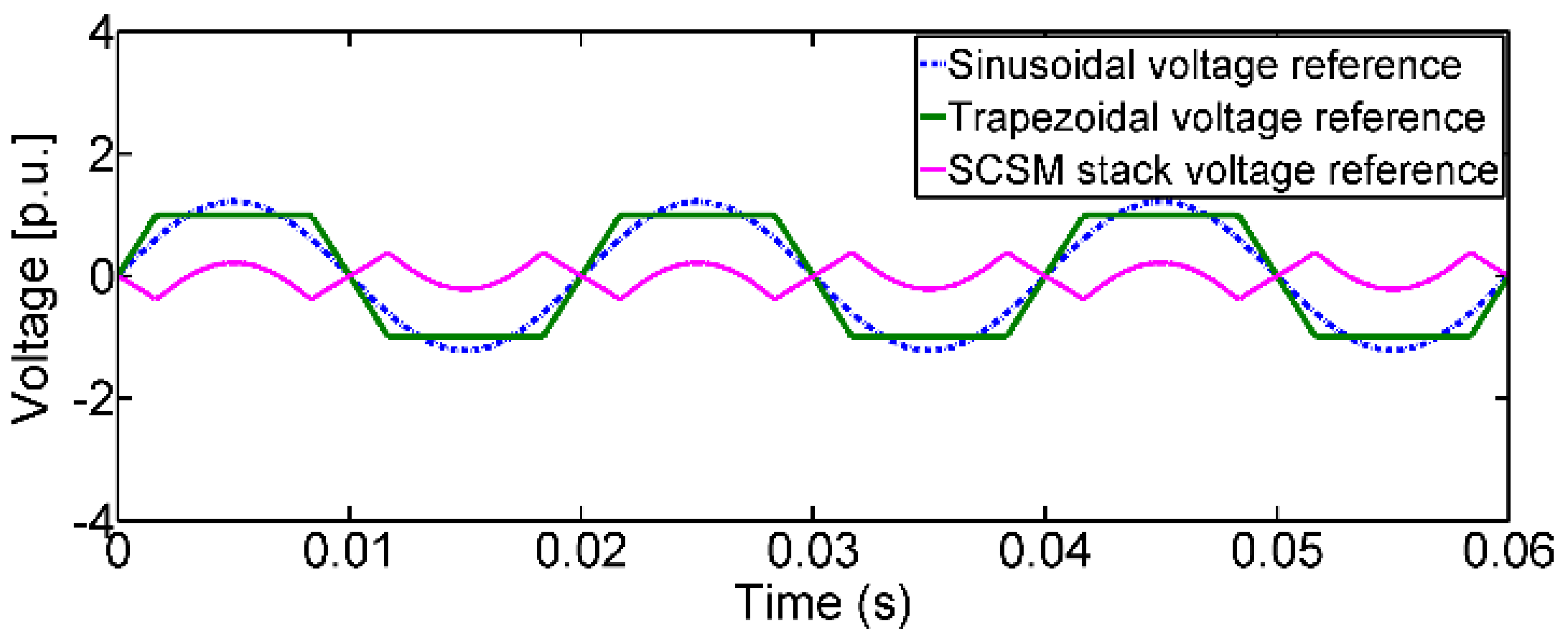

3.1. Modulation Scheme of the Proposed Hybrid MMC

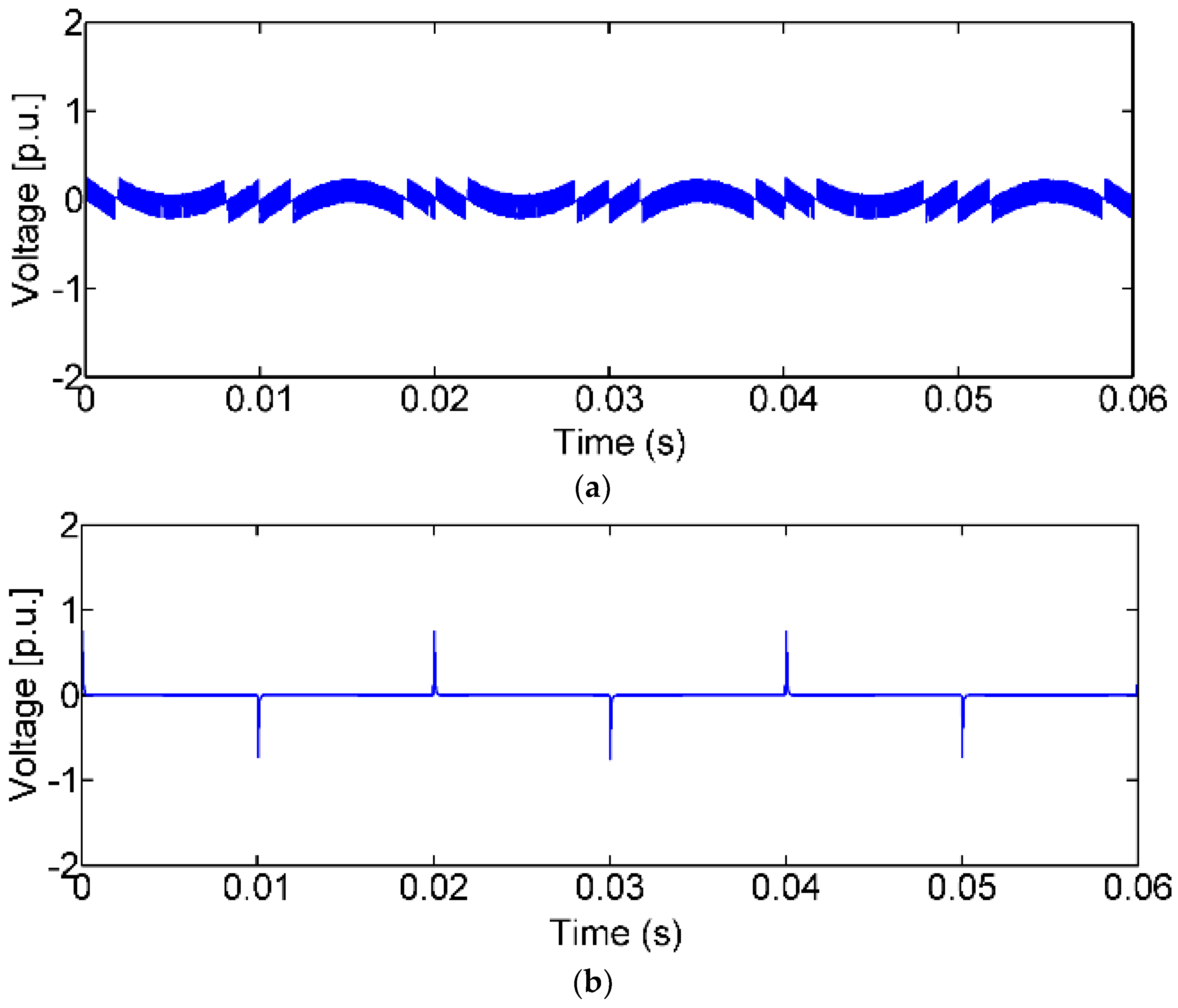

3.2. Analysis and Control of the SCSM Stack

3.3. Fault Blocking Capability of the Proposed Hybrid MMC

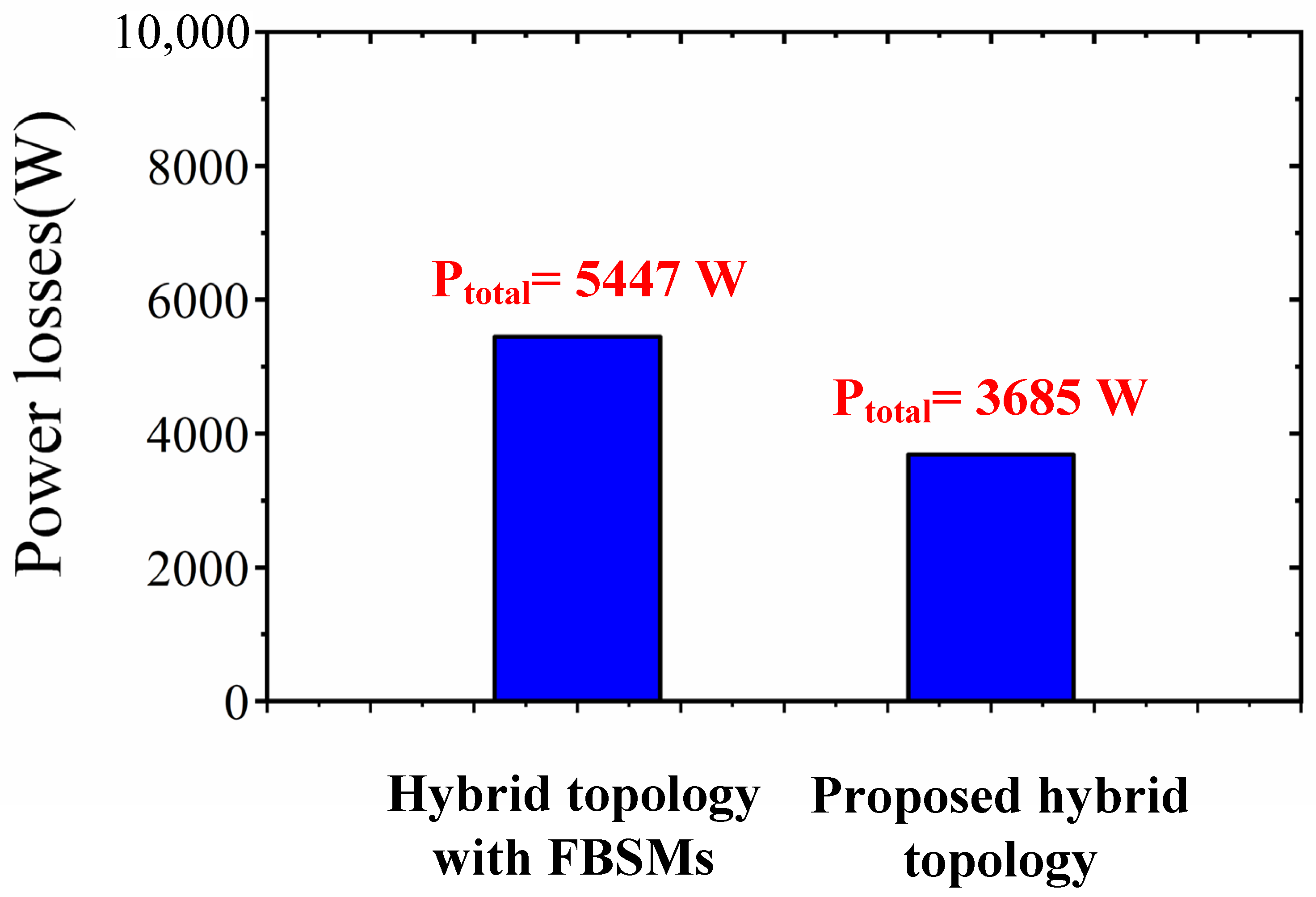

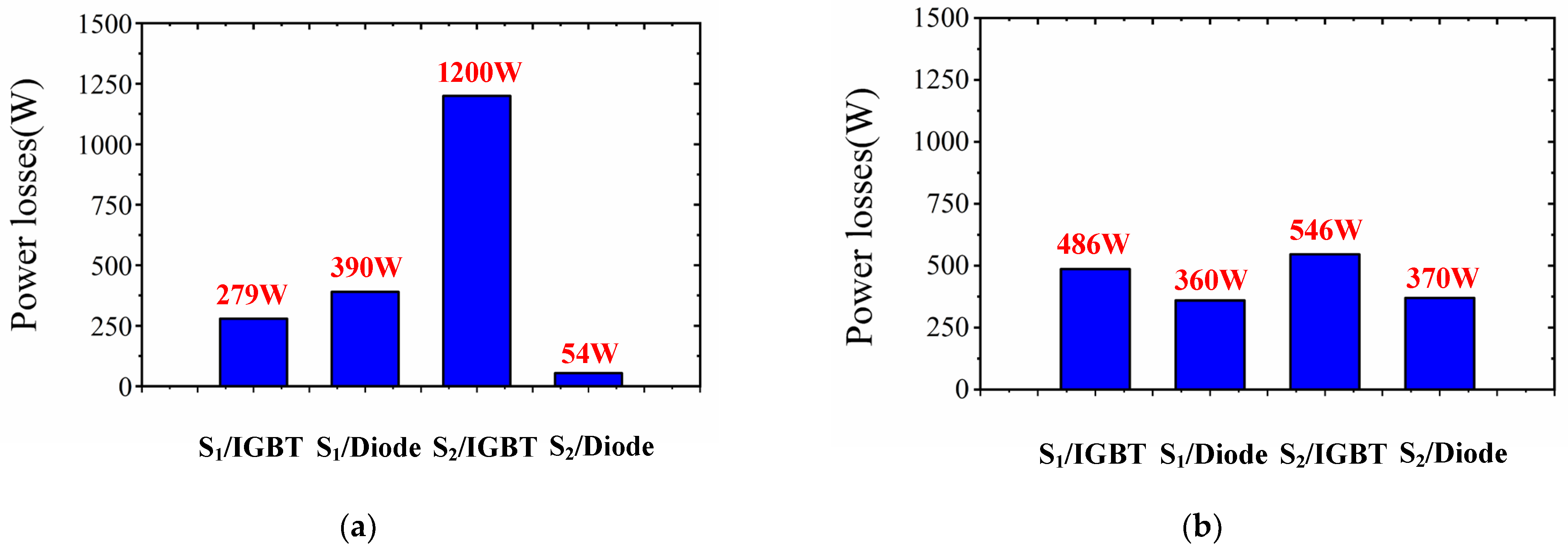

3.4. Power Losses Analysis of the Proposed Hybrid MMC

4. Simulation Results

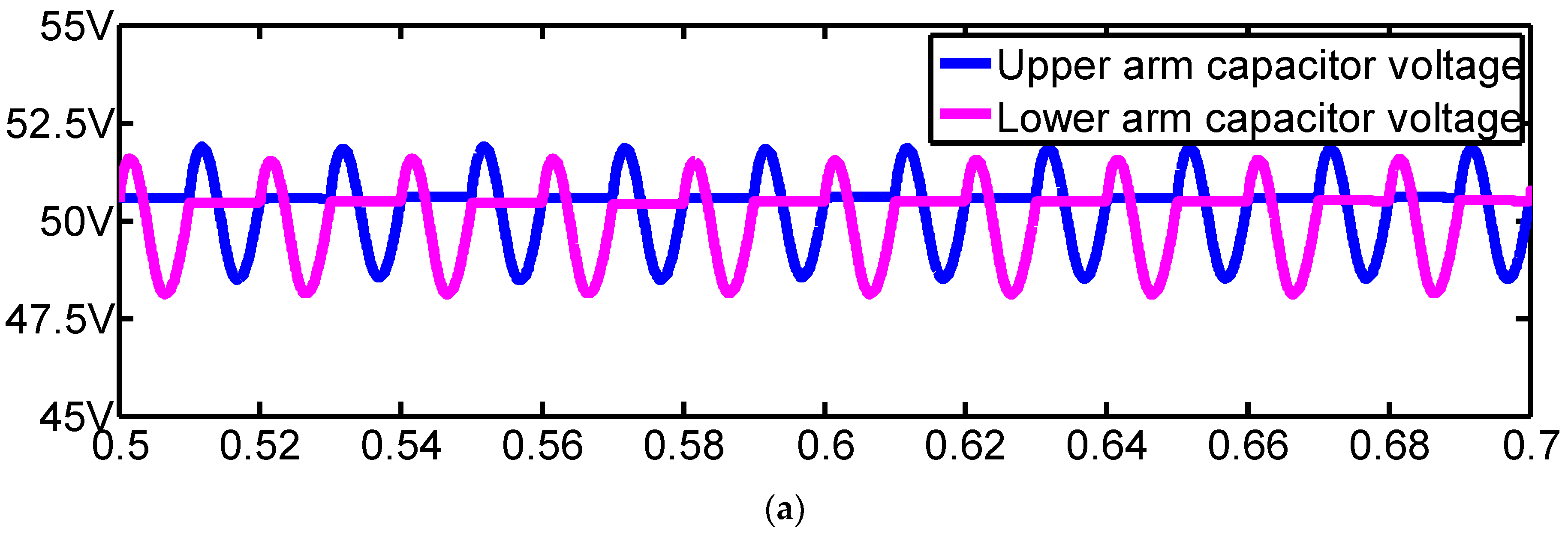

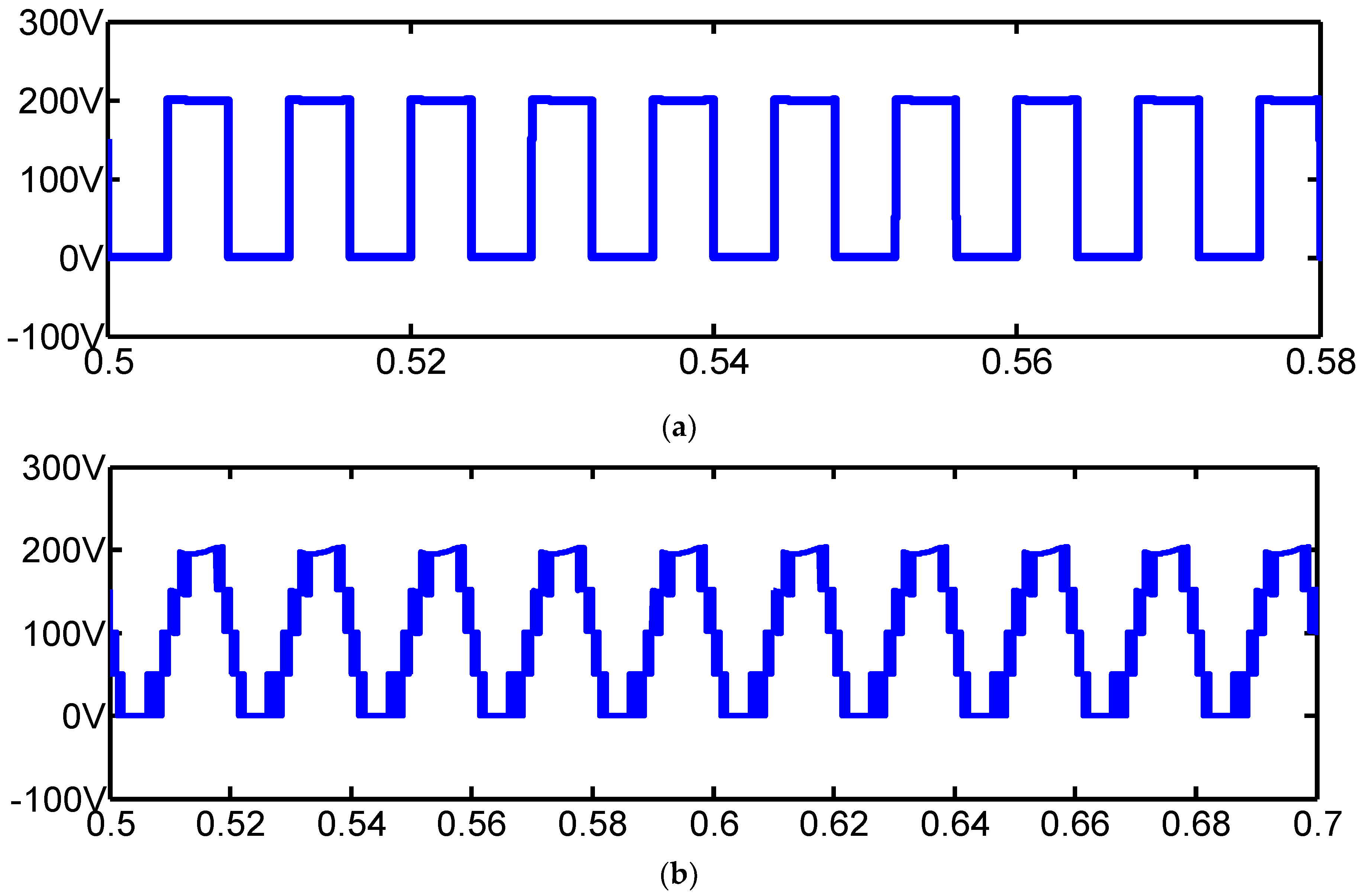

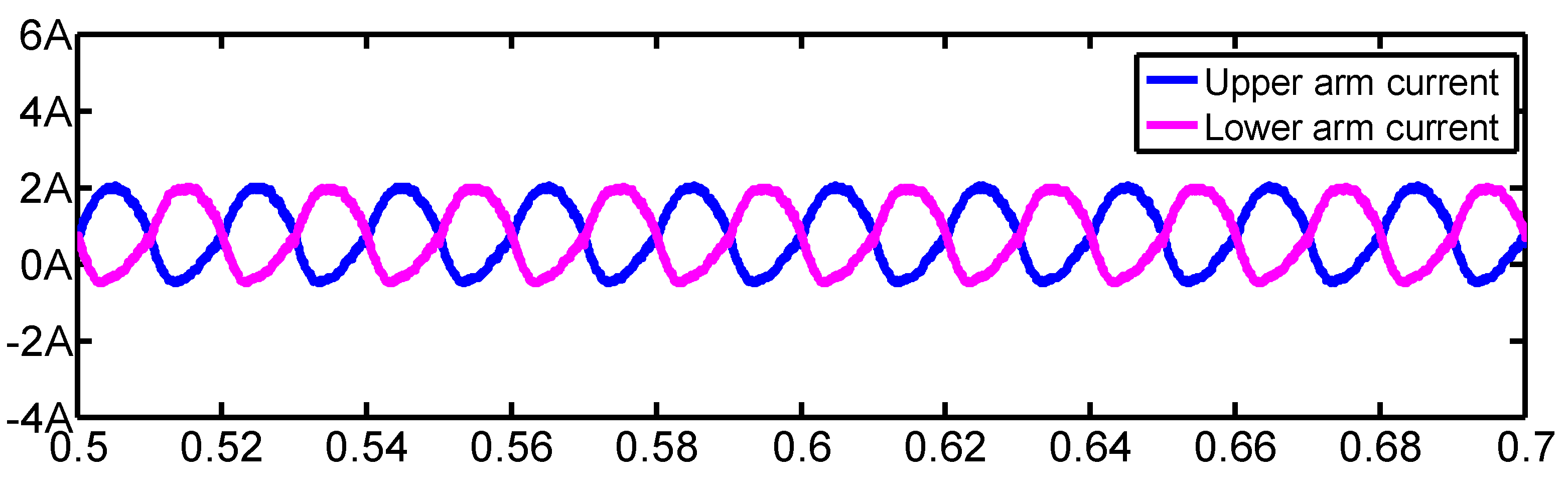

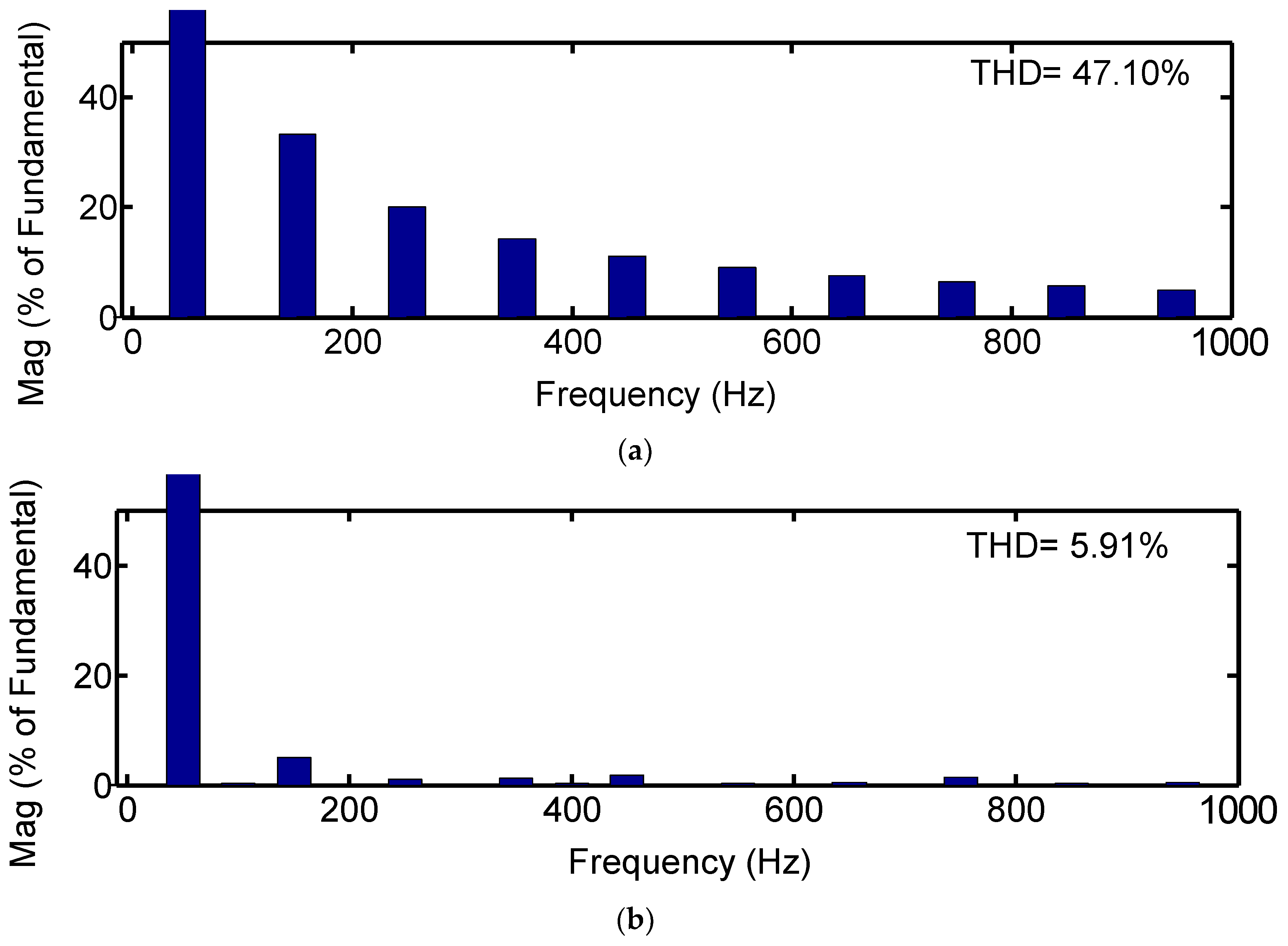

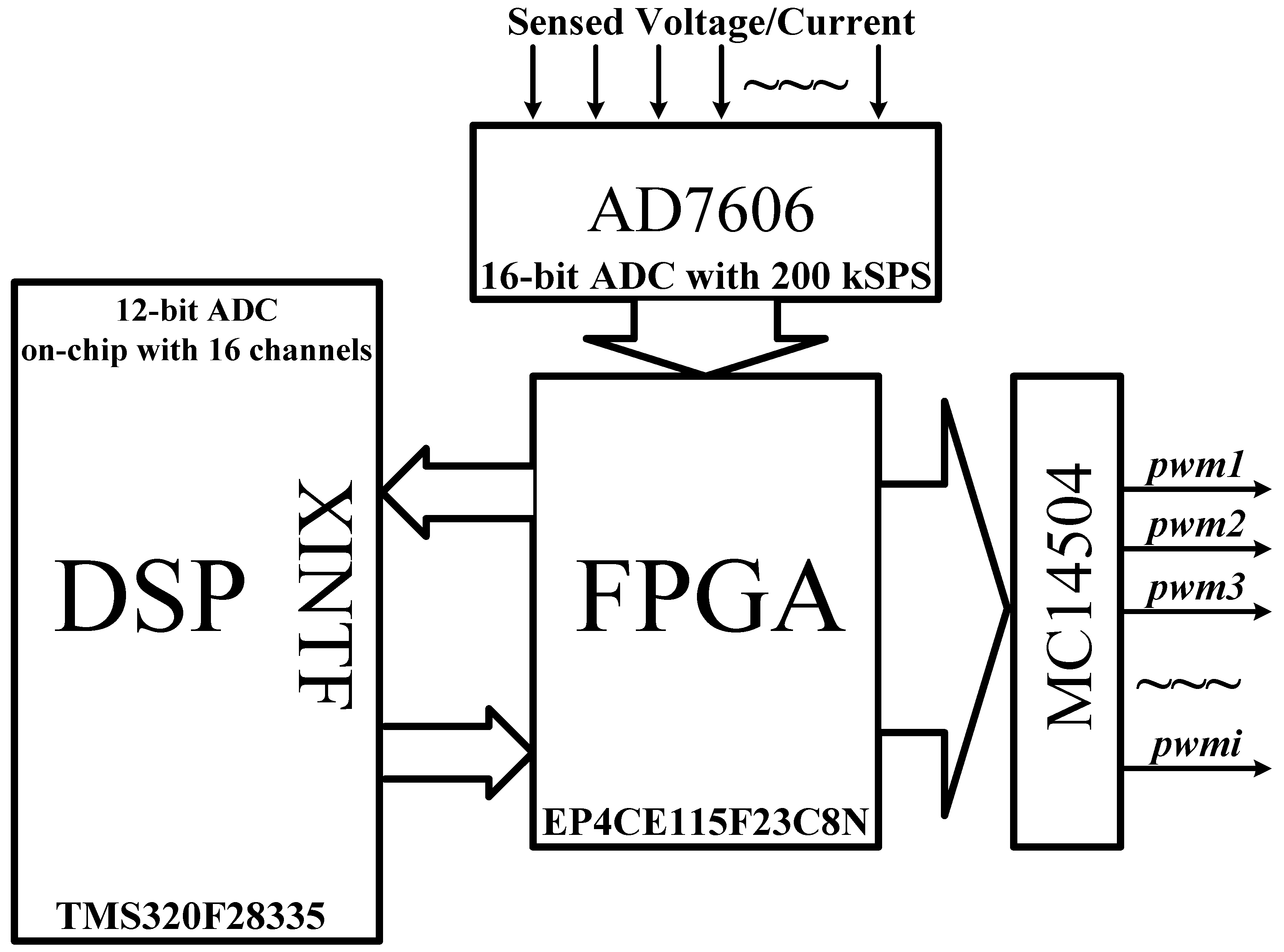

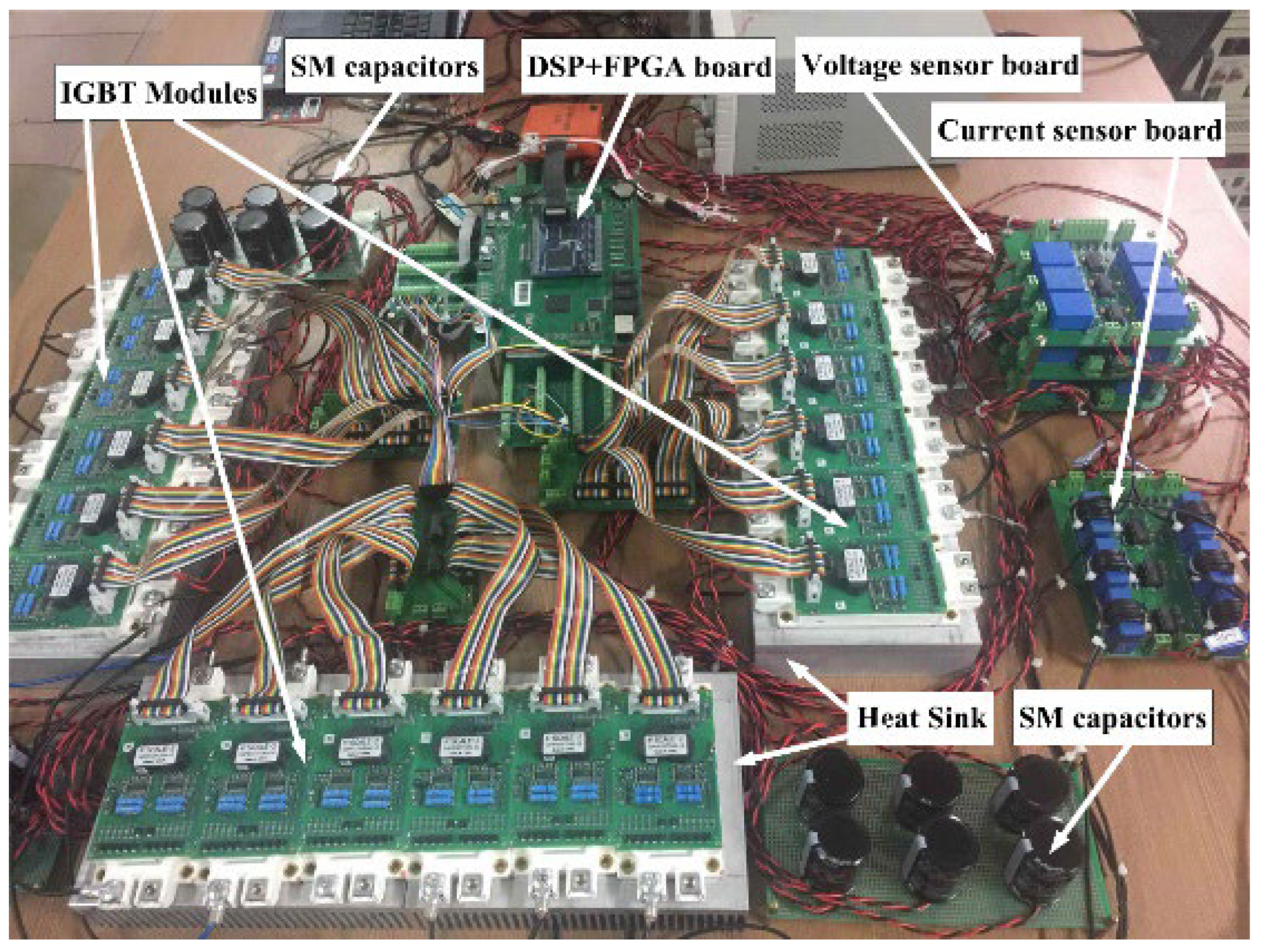

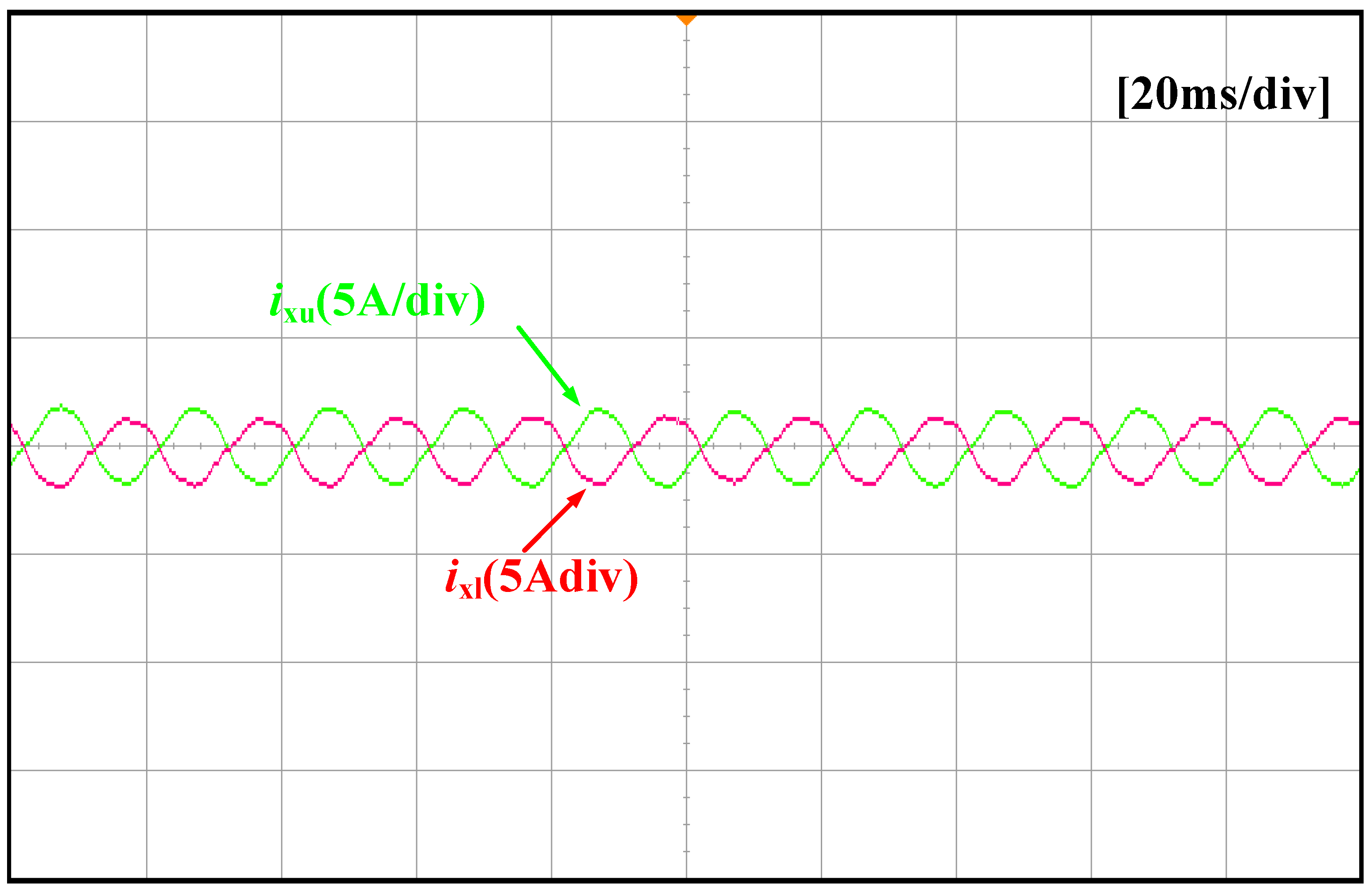

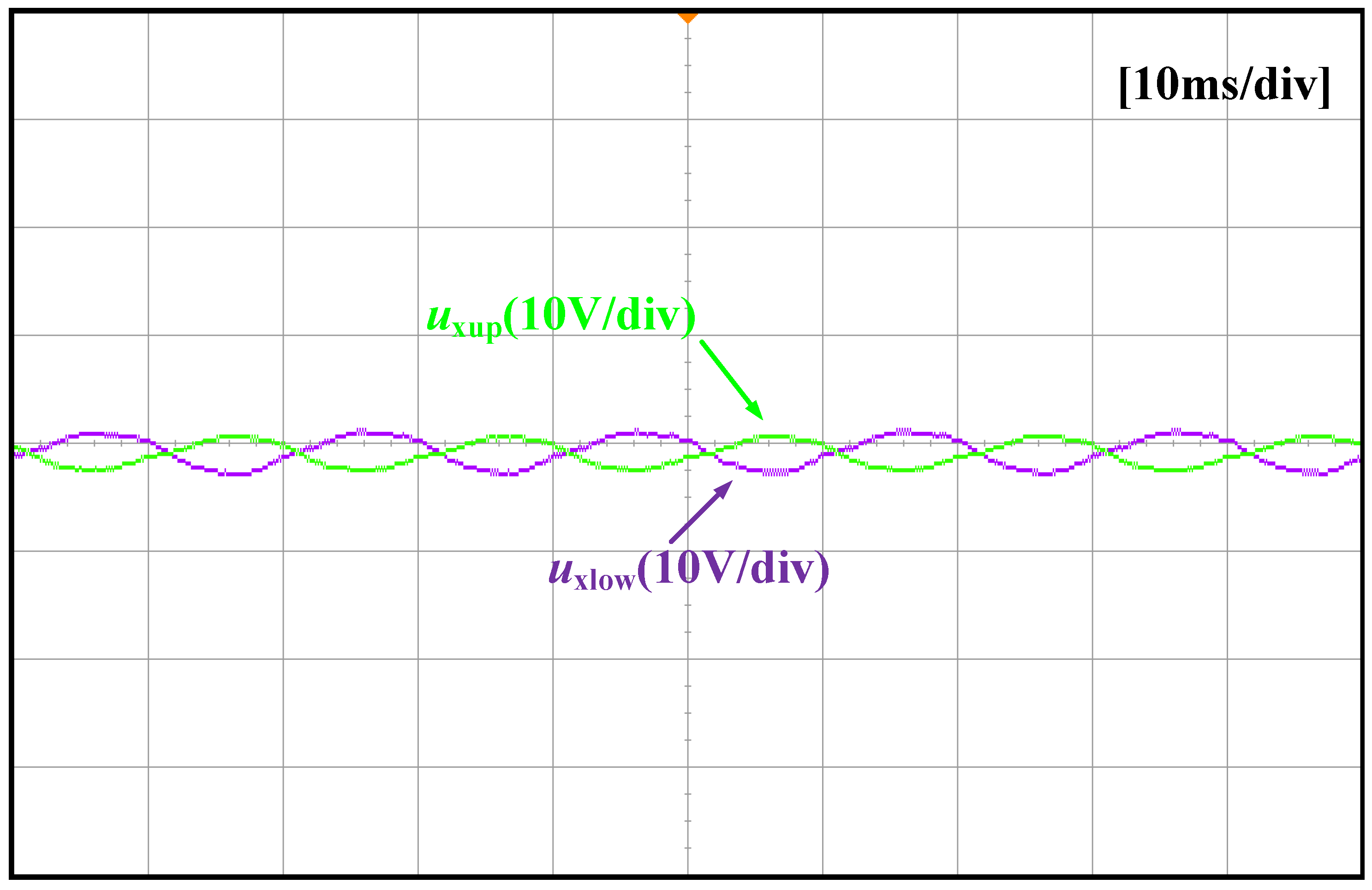

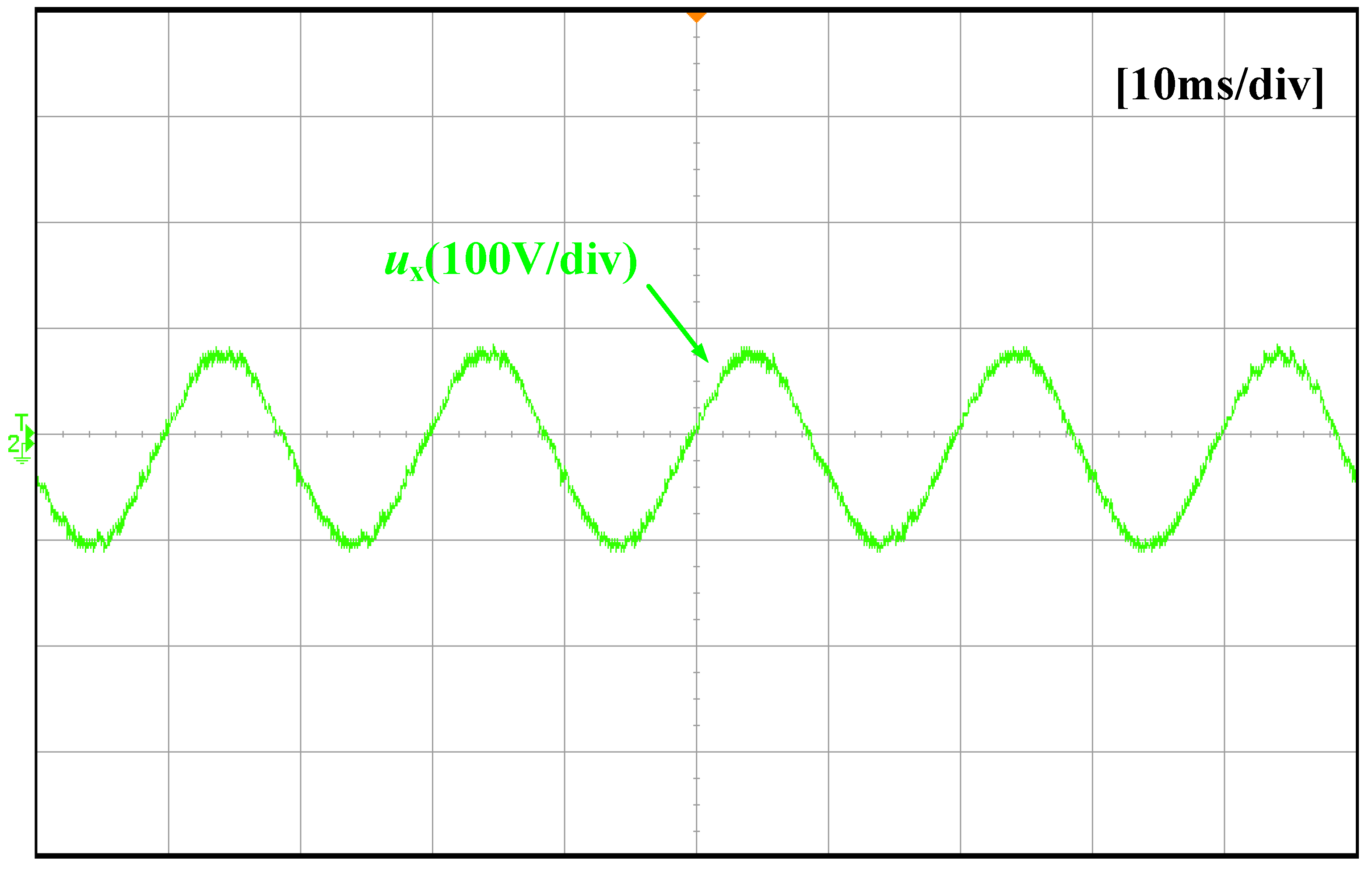

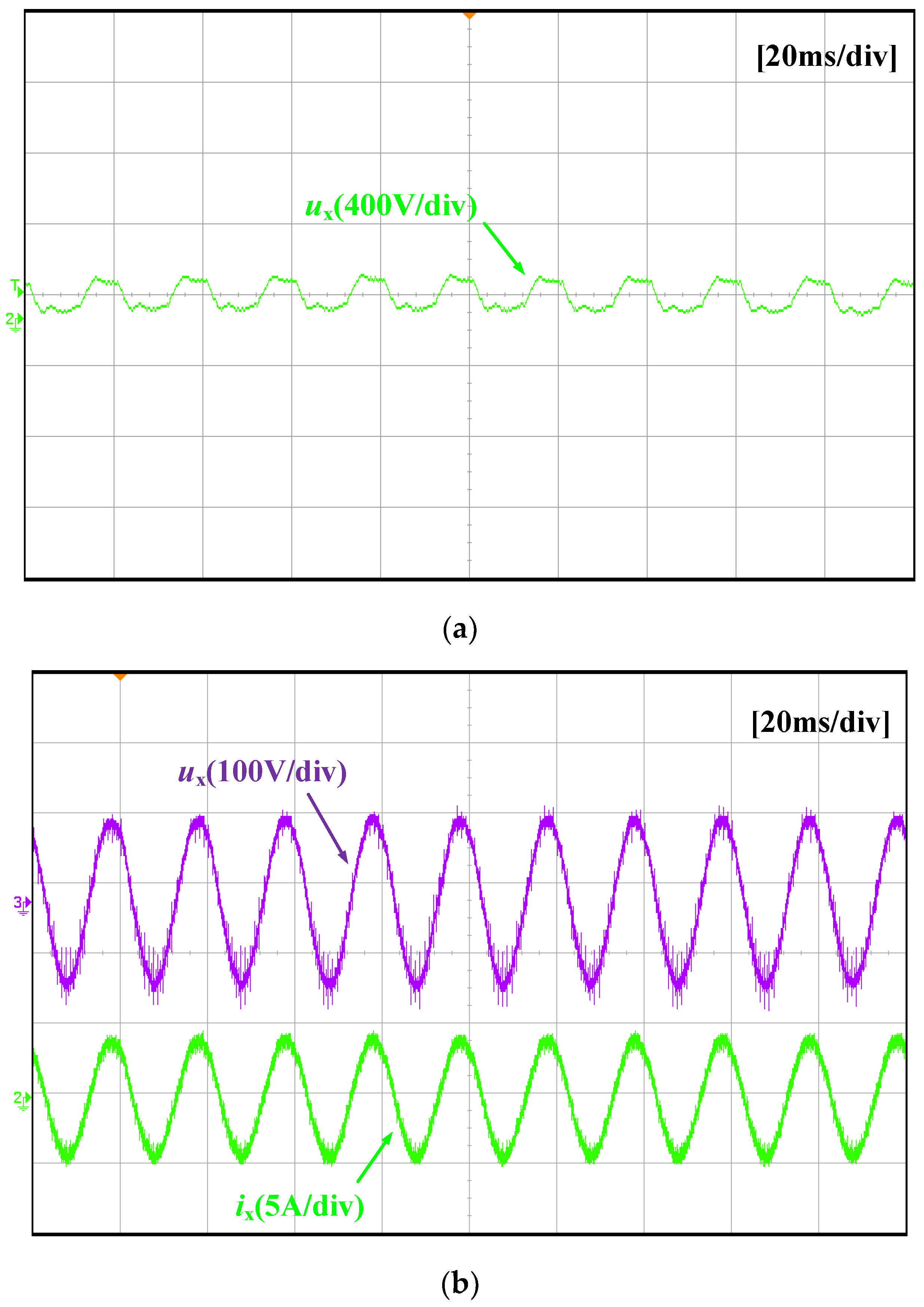

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Conflicts of Interest

References

- Lesnicar, A.; Marquardt, R. An innovative modular multilevel converter topology suitable for a wide power range. In Proceedings of the IEEE Bologna Power Tech Conference Proceedings, Bologna, Italy, 23–26 June 2003; Volume 3, p. 6. [Google Scholar] [CrossRef]

- Glinka, M.; Marquardt, R. A New AC/AC Multilevel Converter Family. IEEE Trans. Ind. Electron. 2005, 52, 662–669. [Google Scholar] [CrossRef]

- Glinka, M. Prototype of multiphase modular-multilevel-converter with 2 MW power rating and 17-level-output-voltage. In Proceedings of the 2004 IEEE 35th Annual Power Electronics Specialists Conference (IEEE Cat. No. 04CH37551), Aachen, Germany, 20–25 June 2004. [Google Scholar] [CrossRef]

- Akagi, H. Classification, Terminology, and Application of the Modular Multilevel Cascade Converter (MMCC). IEEE Trans. Power Electron. 2011, 26, 3119–3130. [Google Scholar] [CrossRef]

- Huang, M.; Zou, J.; Ma, X. Hybrid Modular Multilevel Converter with Redistributed Power to Reduce Submodule Capacitor Voltage Fluctuation. IEEE Trans. Power Electron. 2018, 33, 6595–6607. [Google Scholar] [CrossRef]

- Korn, A.J.; Winkelnkemper, M.; Steimer, P. Low output frequency operation of the Modular Multi-Level Converter. In Proceedings of the 2010 IEEE Energy Conversion Congress and Exposition, Atlanta, GA, USA, 12–16 September 2010; pp. 3993–3997. [Google Scholar]

- Hagiwara, M.; Nishimura, K.; Akagi, H. A Medium-Voltage Motor Drive with a Modular Multilevel PWM Inverter. IEEE Trans. Power Electron. 2010, 25, 1786–1799. [Google Scholar] [CrossRef]

- Zhang, M.; Huang, L.; Yao, W.; Liu, Z. Circulating Harmonic Current Elimination of a CPS-PWM-Based Modular Multi-level Converter with a Plug-in Repetitive Controller. IEEE Trans. Power Electron. 2014, 29, 2083–2097. [Google Scholar] [CrossRef]

- Yang, L.; Li, Y.; Li, Z.; Wang, P.; Xu, S.; Gou, R. Loss Optimization of MMC by Second-Order Harmonic Circulating Current Injection. IEEE Trans. Power Electron. 2018, 33, 5739–5753. [Google Scholar] [CrossRef]

- Wang, J.; Han, X.; Ma, H.; Bai, Z. Analysis and Injection Control of Circulating Current for Modular Multilevel Converters. IEEE Trans. Ind. Electron. 2019, 66, 2280–2290. [Google Scholar] [CrossRef]

- Li, S.; Wang, X.; Yao, Z.; Li, T.; Peng, Z. Circulating Current Suppressing Strategy for MMC-HVDC Based on Nonideal Proportional Resonant Controllers Under Unbalanced Grid Conditions. IEEE Trans. Power Electron. 2015, 30, 387–397. [Google Scholar] [CrossRef]

- Sun, Y.; Teixeira, C.; Holmes, D.G.; McGrath, B.; Zhao, J. Low-Order Circulating Current Suppression of PWM-Based Modular Multilevel Converters Using DC-Link Voltage Compensation. IEEE Trans. Power Electron. 2017, 33, 210–225. [Google Scholar] [CrossRef]

- Deng, F.; Chen, Z. Voltage-Balancing Method for Modular Multilevel Converters under Phase-Shifted Carrier-Based Pulse Width Modulation. IEEE Trans. Power Electron. 2015, 62, 4158–4169. [Google Scholar]

- Wang, K.; Li, Y.; Zheng, Z.; Xu, L. Voltage Balancing and Fluctuation-Suppression Methods of Floating Capacitors in a New Modular Multilevel Converter. IEEE Trans. Ind. Electron. 2013, 60, 1943–1954. [Google Scholar] [CrossRef]

- Siemaszko, D. Fast Sorting Method for Balancing Capacitor Voltages in Modular Multilevel Converters. IEEE Trans. Power Electron. 2014, 30, 463–470. [Google Scholar] [CrossRef]

- Barros, L.A.M.; Martins, A.P.; Pinto, J.G. A Comprehensive Review on Modular Multilevel Converters, Submodule Topologies, and Modulation Techniques. Energies 2022, 15, 1078. [Google Scholar] [CrossRef]

- Tang, G.; Xu, Z.; Zhou, Y. Impacts of Three MMC-HVDC Configurations on AC System Stability under DC Line Faults. IEEE Trans. Power Syst. 2014, 29, 3030–3040. [Google Scholar] [CrossRef]

- Xiang, W.; Yang, S.; Adam, G.P.; Zhang, H.; Zuo, W.; Wen, J. DC Fault Protection Algorithms of MMC-HVDC Grids: Fault Analysis, Methodologies, Experimental Validations, and Future Trends. IEEE Trans. Power Electron. 2021, 36, 11245–11264. [Google Scholar] [CrossRef]

- Hu, J.; Xiang, M.; Lin, L.; Lu, M.; Zhu, J.; He, Z. Improved Design and Control of FBSM MMC with Boosted AC Voltage and Reduced DC Capacitance. IEEE Trans. Ind. Electron. 2018, 65, 1919–1930. [Google Scholar] [CrossRef]

- Adam, G.P.; Finney, S.J.; Williams, B.W.; Trainer, D.R.; Oates, C.D.M.; Critchley, D.R. Network fault tolerant voltage-source-converters for high-voltage applications. In Proceedings of the 9th IET International Conference on AC and DC Power Transmission (ACDC 2010), London, UK, 19–21 October 2010. [Google Scholar]

- Zeng, R.; Xu, L.; Yao, L.; Williams, B.W. Design and Operation of a Hybrid Modular Multilevel Converter. IEEE Trans. Power Electron. 2015, 30, 1137–1146. [Google Scholar] [CrossRef] [Green Version]

- Li, R.; Adam, G.P.; Holliday, D.; Fletcher, J.E.; Williams, B.W. Hybrid Cascaded Modular Multilevel Converter with DC Fault Ride-Through Capability for the HVDC Transmission System. IEEE Trans. Power Deliv. 2015, 30, 1853–1862. [Google Scholar] [CrossRef] [Green Version]

| Mode | Switching States | uscsmi |

|---|---|---|

| Normal mode | sx1i is on, sx2i is off | uxucmi |

| Normal mode | sx1i is off, sx2i is on | –ulcmi |

| Fault blocking mode | sx1i is off, sx2i is off | N/A |

| Symbol | Quantity | Hybrid MMC in Figure 1 | Proposed Topology in Figure 2 |

|---|---|---|---|

| Vdc | DC-link voltage | 12 kV | 12 kV |

| n1 | Number of HBSMs per arm | 20 | 20 |

| n2 | Number of SCSMs (FBSMs) per phase | 20 | 20 |

| C | HBSM capacitance | 1 mF | 1 mF |

| Cref | AC side SM capacitance | 1 mF | 1 mF |

| L | Arm inductor | 10 mH | 10 mH |

| m | Modulation index | 1.2 | 1.2 |

| fc | SM switching frequency | 500 Hz | 500 Hz |

| f | Fundamental frequency | 50 Hz | 50 Hz |

| ucm | SM capacitor voltage reference | 600 V | 600 V |

| Uref | AC side SM capacitor reference | 600 V | 300 V |

| Rload | Load resistance | 50 Ω | 50 Ω |

| Symbol | Quantity | Value |

|---|---|---|

| Vdc | DC-link voltage | 200 V |

| n1 | Number of HBSMs per arm | 4 |

| n2 | Number of SCSMs per phase | 2 |

| C | SM capacitor | 0.5 mF |

| Cref | SCSM capacitor | 1 mF |

| L | Arm inductor | 10 mH |

| fc | SM switching frequency | 1 kHz |

| f | Fundamental frequency | 50 Hz |

| ucm | SM capacitor voltage reference | 50 V |

| Uref | SCSM capacitor voltage reference | 50 V |

| Rload | Load resistance | 50 Ω |

| Symbol | Quantity | Value |

|---|---|---|

| Cin | Input electrolytic capacitor | 10 mF |

| Vdc | DC-link voltage | 200 V |

| n1 | Number of HBSMs per arm | 4 |

| n2 | Number of SCSMs per arm | 2 |

| C | SM capacitor | 0.68 mF |

| Cmid | SCSM capacitor | 1 mF |

| L | Arm inductor | 6 mH |

| fc | SM switching frequency | 1 kHz |

| f | Fundamental frequency | 50 Hz |

| ucm | SM capacitor voltage reference | 50 V |

| Uref | SCSM capacitor voltage reference | 50 V |

| Rload | Load resistance | 30 Ω |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, M.; Li, J. Analysis and Design of the Split-Capacitor-Based Sub-Modules Equipped for Hybrid Modular Multilevel Converter. Energies 2022, 15, 2370. https://doi.org/10.3390/en15072370

Huang M, Li J. Analysis and Design of the Split-Capacitor-Based Sub-Modules Equipped for Hybrid Modular Multilevel Converter. Energies. 2022; 15(7):2370. https://doi.org/10.3390/en15072370

Chicago/Turabian StyleHuang, Ming, and Jianhua Li. 2022. "Analysis and Design of the Split-Capacitor-Based Sub-Modules Equipped for Hybrid Modular Multilevel Converter" Energies 15, no. 7: 2370. https://doi.org/10.3390/en15072370