A Single-Phase Transformerless Nine-Level Inverter and Its Control Strategy

Abstract

:1. Introduction

2. The Proposed Nine-Level Inverter Topology and Its Working Principle

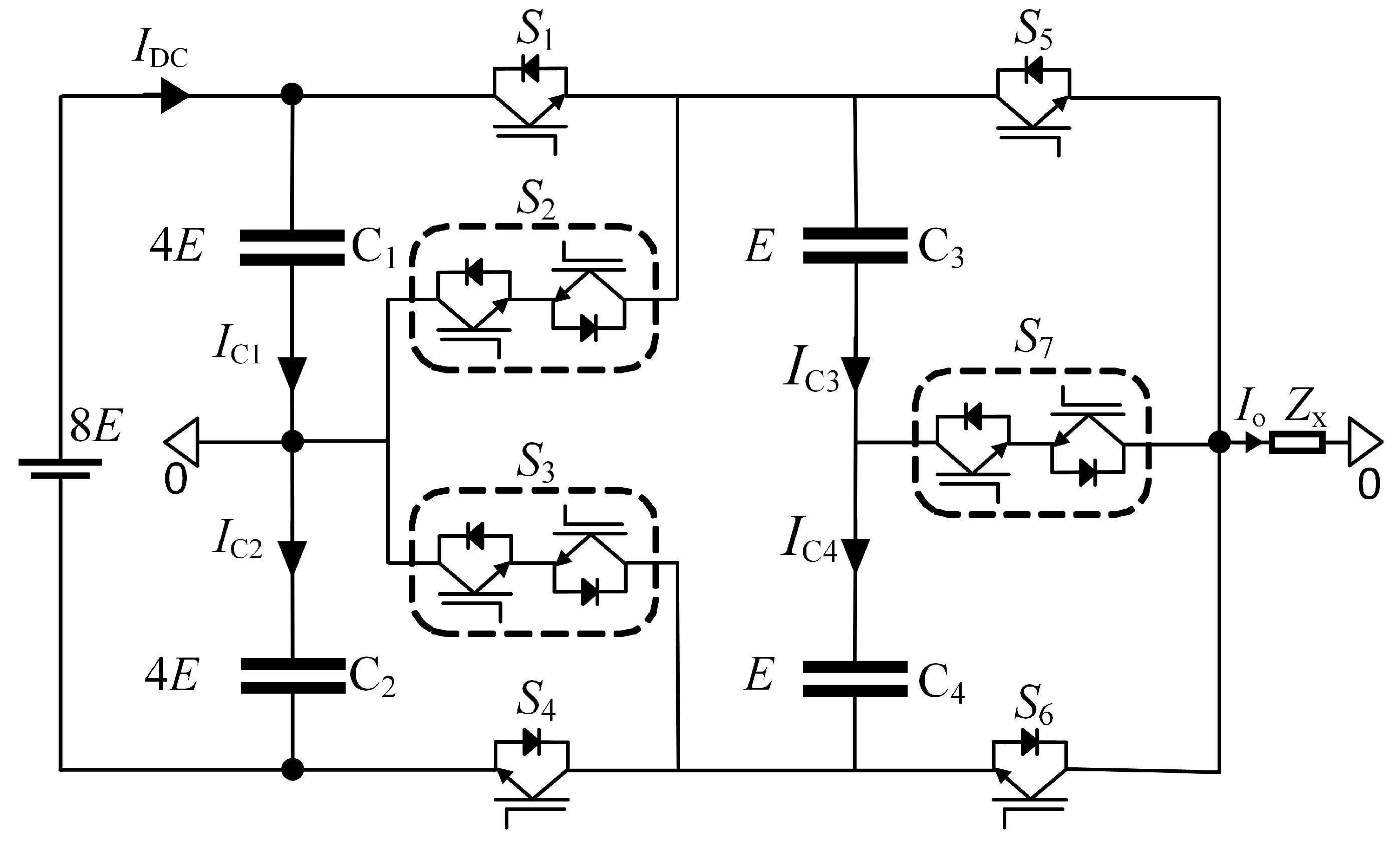

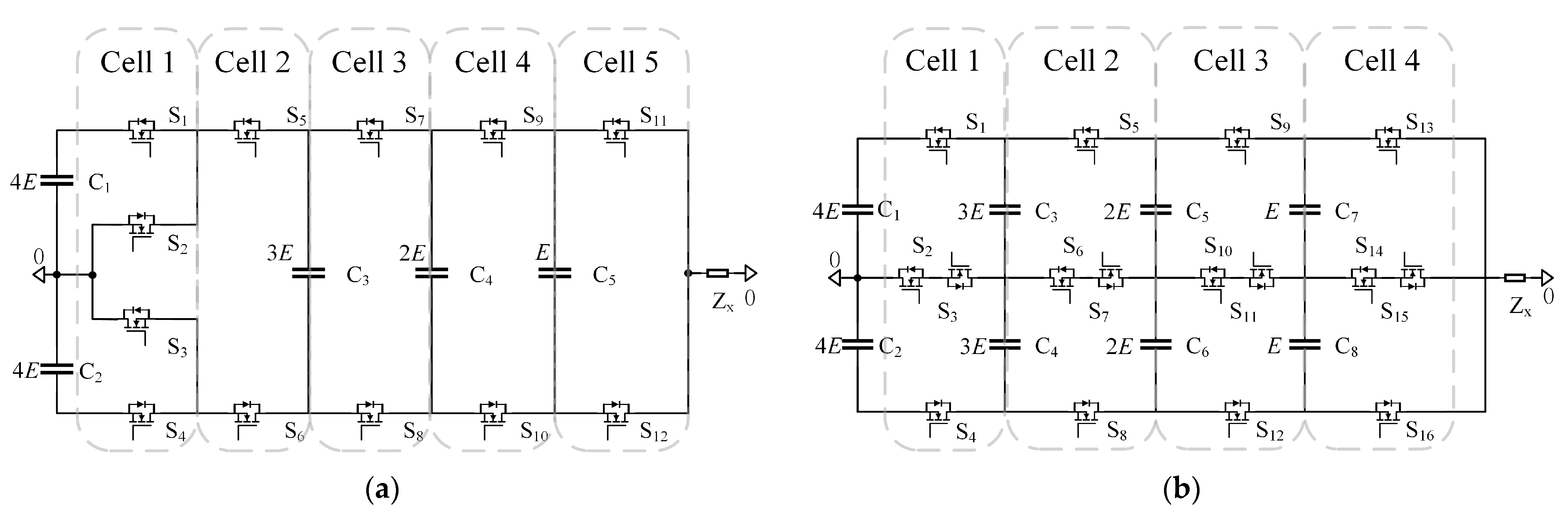

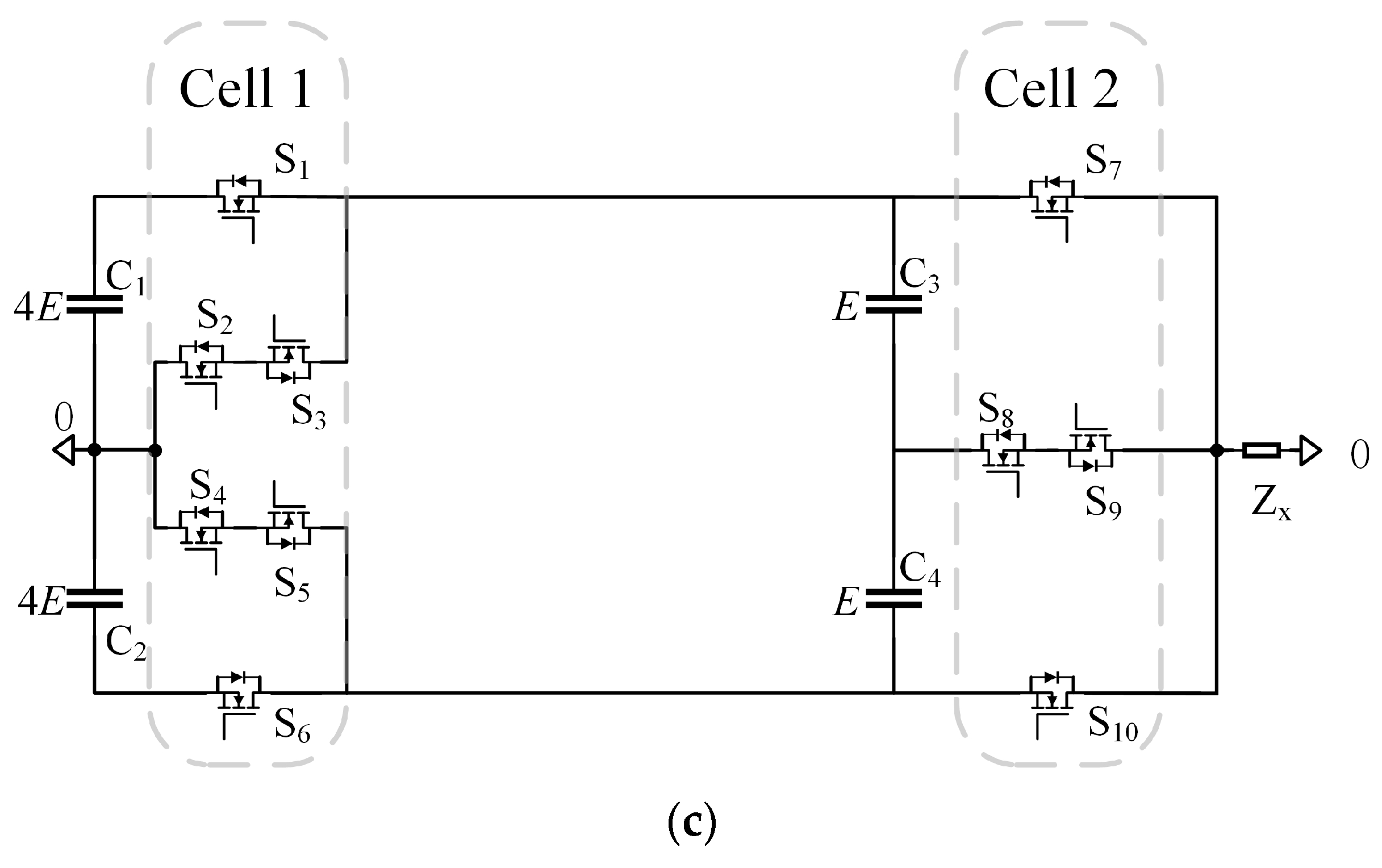

2.1. Topology

2.2. Working Modal Analysis

- (1)

- State P4 (Figure 2a): The switches S1 and S5 are turned on, the current flows from the positive terminal of the dc-link through the switches S1, S5 and the load, and then returns to the neutral point, the inverter output voltage VO = VDC/2. The current flowing through capacitors C3 and C4 is IC3 = IC4 = 0.

- (2)

- State P3 (Figure 2b): The switches S1 and S7 are turned on, the current starts from the positive end of the dc-link and returns to the neutral point after passing through S1, C3, S7 and the load, and the output voltage VO = 3VDC/8. The current through C3 is IO and the current through C4 is 0.

- (3)

- State P2P (Figure 2c): the switches S1 and S6 are turned on, the current starts from the positive terminal of the dc-link and returns to the neutral point through S1, C3, C4, S6 and the load. The output voltage VO = VDC/4, and the currents IC3 = IC4 = IO.

- (4)

- State P2N (Figure 2d): the switch S3 and S5 are turned on, the current starts from the neutral point and returns to the neutral point after passing through S3, C4, C3, S5 and the load. The output voltage VO = VDC/4, and the currents IC3 = IC4= −IO.

- (5)

- State P1 (Figure 2e): the switches S3 and S7 are turned on, the current starts from the neutral point and returns to the neutral point after passing through S3, C4, S7 and the load. The output voltage VO = VDC/8, while the currents IC3 = 0 and IC4 = −IO.

- (6)

- State OP (Figure 2f): The switches S2 and S5 are turned on, and the current starts from the neutral point and returns to the neutral point after passing through S2, S5 and the load. At this time, VO = 0, IC3 = IC4 = 0.

- (7)

- The state is ON (Figure 2g): the switches S3 and S6 are turned on, the current starts from the neutral point and then returns to the neutral point after passing through S3, S6 and the load, and the voltage VO = 0, and the currents IC3 = IC4 = 0.

- (8)

- State N1 (Figure 2h): The switches S2 and S7 are turned on, the current starts from the neutral point and returns to the neutral point after passing through S2, C3, S7 and the load. The output voltage VO = −VDC/8, and the currents IC3 = IO, IC4 = 0.

- (9)

- State N2P (Figure 2i): The switch tubes S2 and S6 are turned on, the current starts from the neutral point and returns to the neutral point after passing through S2, C3, C4, S6 and the load. The voltage VO = −VDC/4, and the currents IC3 = IC4 = IO.

- (10)

- State N2N (Figure 2j): The switches S4 and S5 are turned on, and the current starts from the negative end of the dc-link and returns to the neutral point through S4, C4, C3, S5 and the load. The output voltage VO = −VDC/4, and the currents IC3 = IC4 = −IO.

- (11)

- State N3 (Figure 2k): the switches S4 and S7 are turned on, the current starts from the negative end of the dc-link and then returns to the negative end of the dc-link through S4, C4, S7 and the load. The voltage VO = −3VDC/8, and the current IC4 = −IO.

- (12)

- State N4 (Figure 2l): The switches S4 and S6 are turned on, the current starts from the negative end of the dc-link and returns to the neutral point after passing through S4, S6 and the load. The voltage VO = −VDC/2, and the currents IC3 = IC4 = 0.

2.3. Comparison with Existing Nine-Level Inverter Topologies

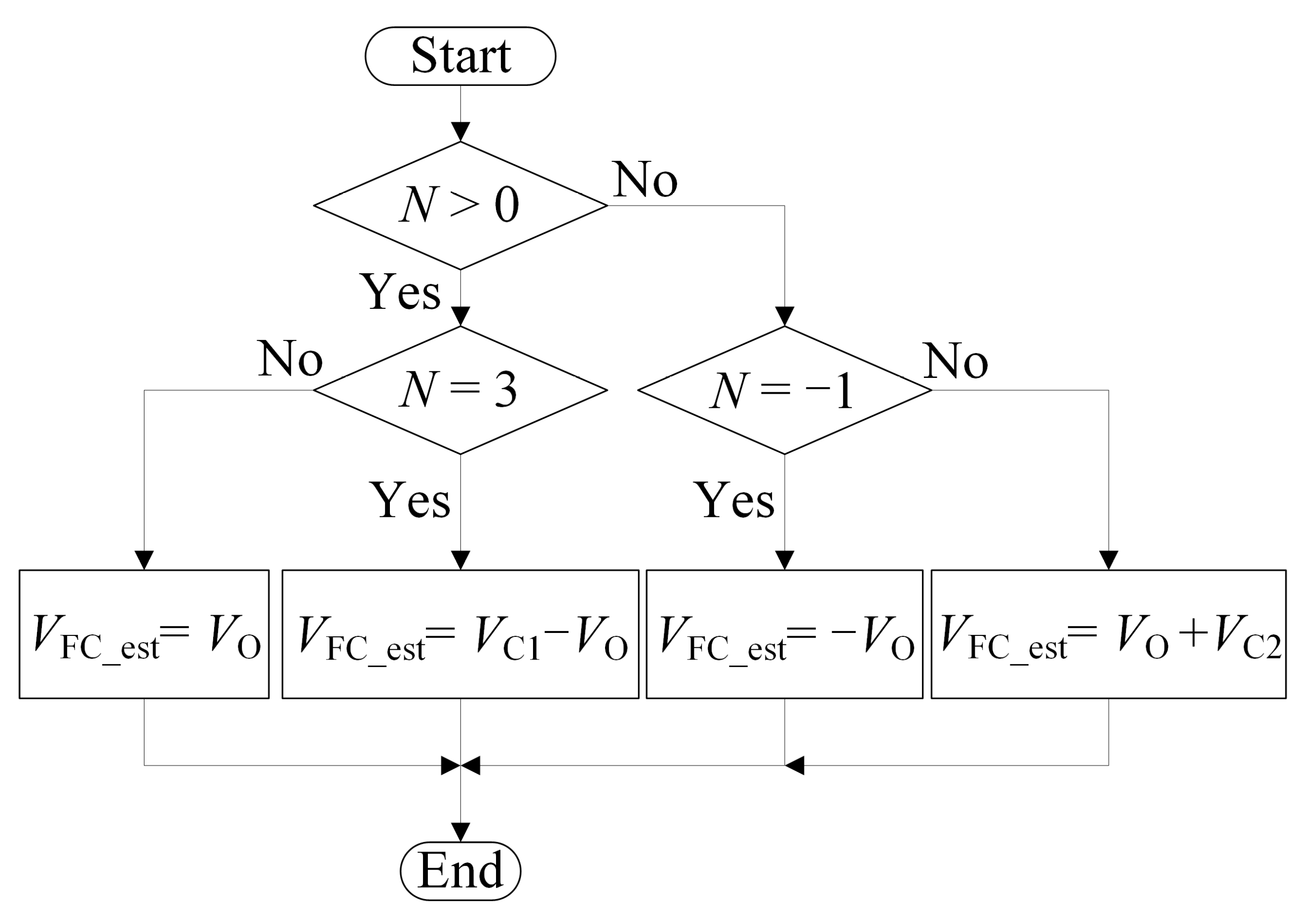

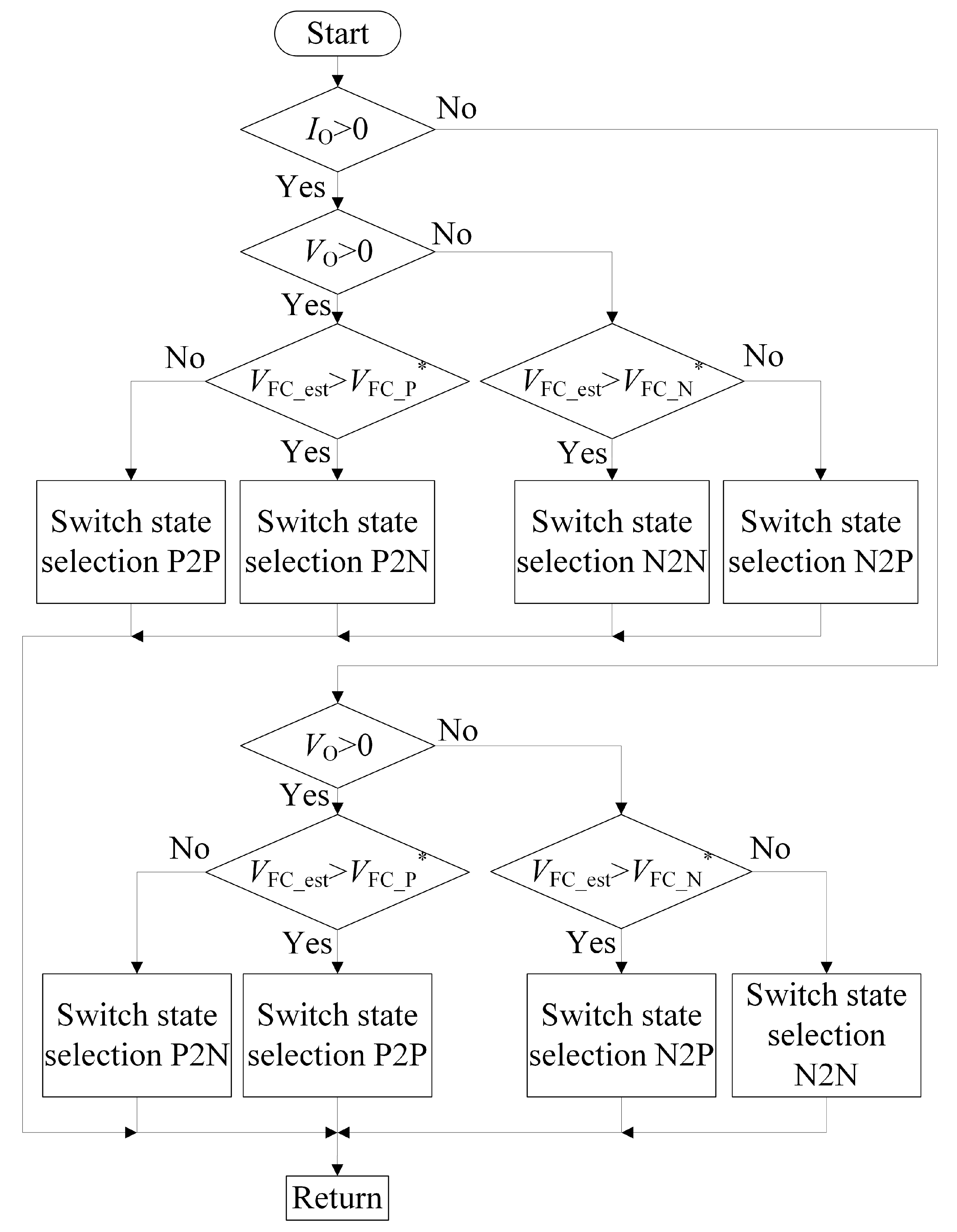

3. Control Strategy of Voltage Sensor without Floating Capacitance

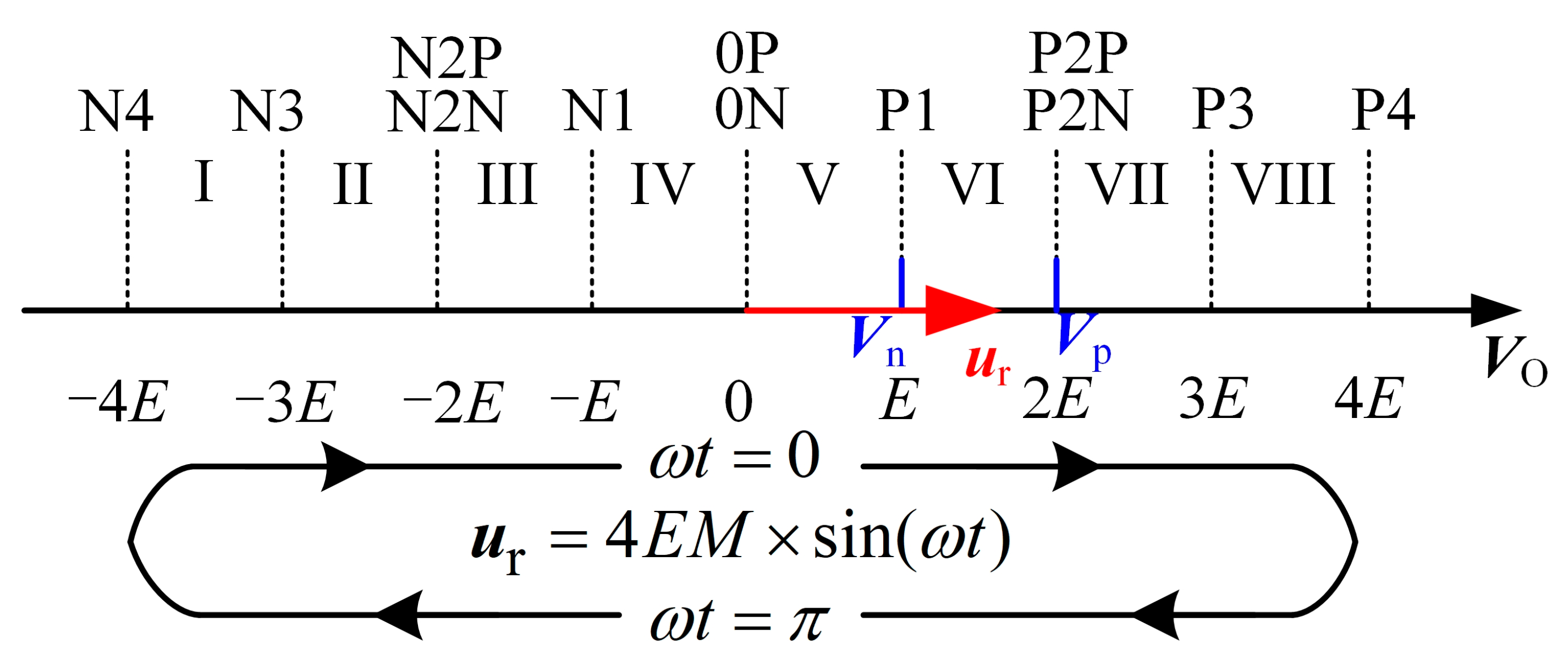

3.1. One-Dimensional Space Vector Modulation Algorithm

3.2. Control Strategy of Voltage Sensor without Floating Capacitance

3.3. Implementation of the Proposed Algorithm

4. Simulation and Experimental Analysis

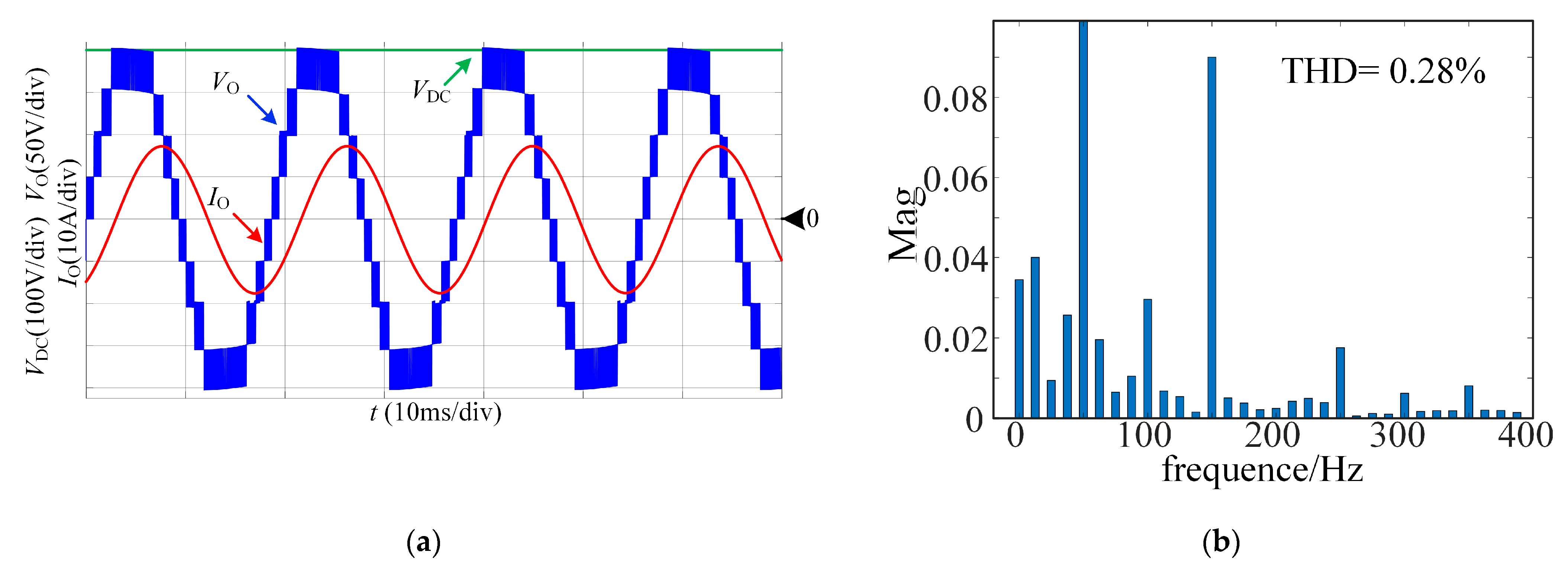

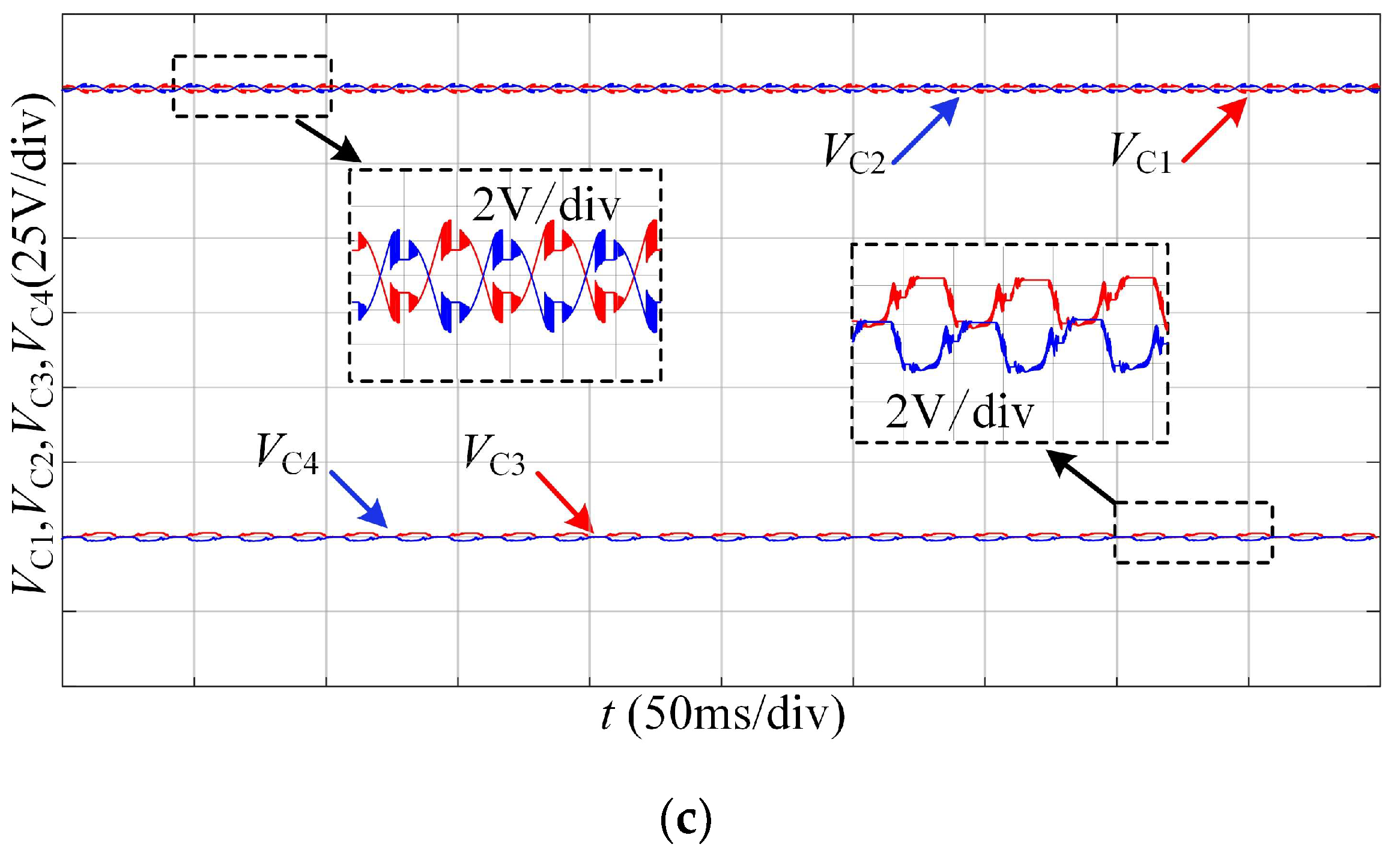

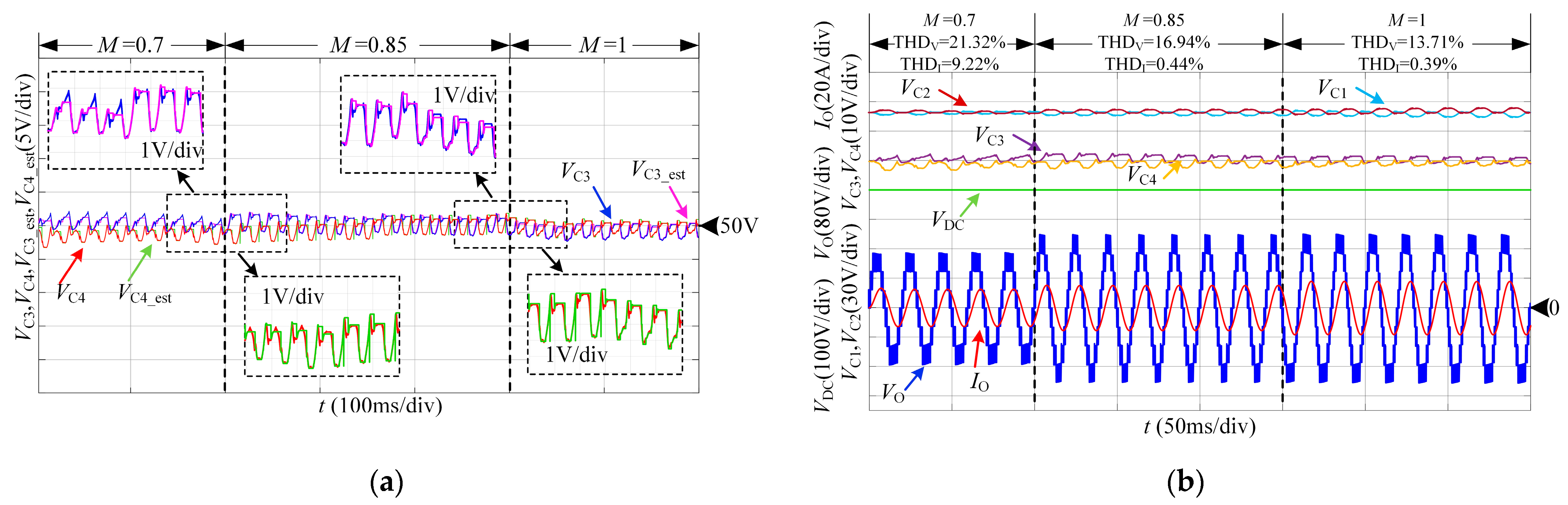

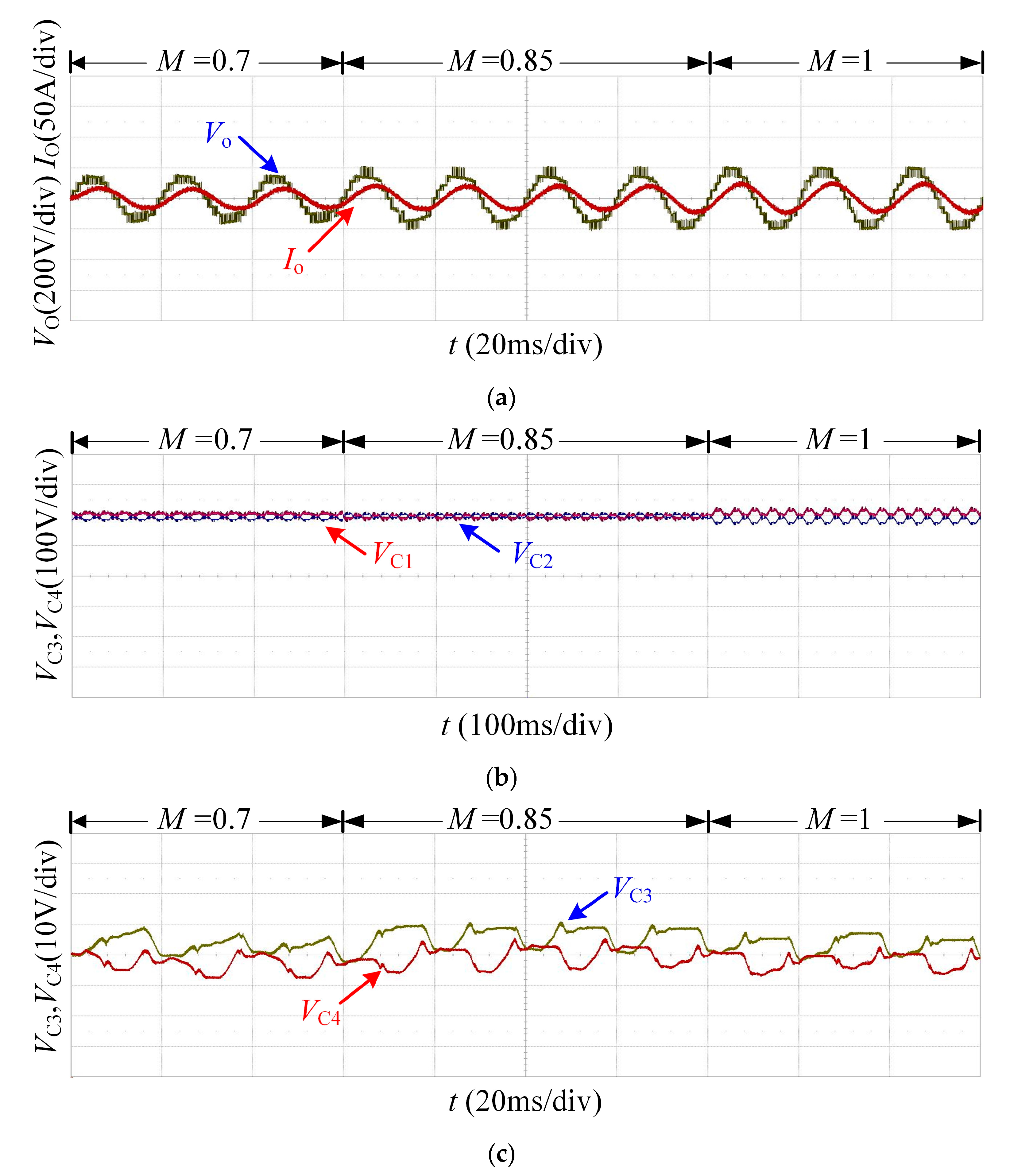

4.1. Simulation Analysis

4.2. Experimental Analysis

5. Conclusions

- (1)

- Compared with the traditional nine level inverter topology, the proposed nine level inverter has obvious advantages in the number of switching devices and the number of flying capacitors. The most prominent is that the number of switching devices through which the current flows is the least, which reduces the device switching loss in the inverter.

- (2)

- The proposed method reduces 50% capacitor voltage sampling circuit, which can greatly reduce the cost of the system, and it can realize the accurate estimation of the floating capacitor voltage and its balance control at a specific moment.

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Wang, Y.Q.; Ku, R.H.; Zhou, C.L.; Wang, Z.; Wang, M.D. Hybrid T-type multilevel inverter and its modulation strategy. High Volt. Eng. 2020, 46, 3220–3228. [Google Scholar]

- Yu, H.Y.; Chen, B.; Yao, W.X.; Liu, Z.Y. Hybrid seven-level converter based on t-type converter and h-bridge cascaded under SPWM and SVM. IEEE Trans. Power Electron. 2018, 33, 689–702. [Google Scholar] [CrossRef]

- Zhang, Y.L.; Wang, Q.J.; Hu, C.G.; Zhou, Y.F. A novel low voltage seventeen-level converter and control strategy. Proc. CSEE 2020, 40, 1095–1105. [Google Scholar]

- Yousofi-Darmian, S.; Barakati, S.M. A new asymmetric multilevel inverter with reduced number of co-mponents. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 4333–4342. [Google Scholar] [CrossRef]

- Hu, C.G.; Rui, T.; Ma, D.J.; Wang, Q.J.; Luo, F.L. SVM control strategy for neutral point voltage balance and switching loss reduction of three-level ANPC inverter. Proc. CSEE 2016, 36, 3598–3608. [Google Scholar]

- Cao, Y.; Yang, J.T.; Li, R.; Cai, X.; Yu, W.; Xu, J.; Du, C.R.; Huang, L.; Zhang, T.; Ma, Z.Y.; et al. Circulating current suppression strategy of ANPC nine-level inverter. Proc. CSEE 2020, 40, 232–242. [Google Scholar]

- Viju, N.R.; Arun, R.S.; Kaarthik, R.S. Generation of higher number of voltage levels by stacking inverters of lower multilevel structures with low voltage devices for drives. IEEE Trans. Power Electron. 2017, 32, 52–59. [Google Scholar]

- Liu, J.F.; Wu, J.L.; Zeng, J.; Guo, H.F. A novel nine-level inverter employing one voltage source and reduced components as high-frequency AC power source. IEEE Trans. Power Electron. 2017, 32, 2939–2947. [Google Scholar] [CrossRef]

- Ghias, A.M.Y.M.; Pou, J.; Agelidis, V.G. An active voltage-balancing method based on phase-shifted PWM for stacked multicell converters. IEEE Trans. Power Electron. 2016, 31, 1921–1929. [Google Scholar] [CrossRef]

- Ghias, A.M.Y.M.; Pou, J.; Acuna, P.; Ceballos, S.; Heidari, A.; Agelidis, V.G.; Merabet, A. Elimination of low-frequency ripples and regulation of neutral-point voltage in stacked multicell converters. IEEE Trans. Power Electron. 2017, 32, 164–175. [Google Scholar] [CrossRef]

- Lee, S.S.; Sidorov, M.; Lim, C.S. Hybrid cascaded multilevel inverter (HCMLI) with improved symmetrical 4-Level submodule. IEEE Trans. Power Electron. 2018, 33, 932–935. [Google Scholar] [CrossRef]

- Sandeep, N.; Yaragatti, U.R. Design and implementation of a sensorless multilevel inverter with reduced part count. IEEE Trans. Power Electron. 2017, 33, 6677–6683. [Google Scholar] [CrossRef]

- Sandeep, N.; Yaragatti, U.R. Operation and control of a nine-level modified ANPC inverter topology with reduced part count for grid-connected applications. IEEE Trans. Ind. Electron. 2018, 65, 4810–4818. [Google Scholar] [CrossRef]

- Liu, C.K.; Deng, F.J.; Wang, Q.J.; Wang, Y.B.; Blaabjerg, F.; Wang, Z. Double half-bridge submodule-based modular multilevel converters with reduced voltage sensors. IEEE Trans. Power Electron. 2021, 36, 3643–3648. [Google Scholar] [CrossRef]

- Li, J.J.; Jiang, J.G. A novel space vector pulse width modulation for five-level nested neutral point piloted converter. Proc. CSEE 2018, 38, 3306–3315. [Google Scholar]

- Hu, C.G.; Dong, H.; Zhang, Y.L.; Li, J. Hybrid active neutral clamped seven level inverter and its control strategy. Electr. Mach. Control 2020, 24, 40–49. [Google Scholar]

- Sandeep, N.; Yaragatti, U.R. A switched-capacitor-based multilevel inverter topology with reduced components. IEEE Trans. Power Electron. 2018, 33, 5538–5542. [Google Scholar] [CrossRef]

- Cheng, Q.; Wang, C.; Chen, Z.; Li, Z. A capacitor-voltage-balancing method based on optimal zero-sequence voltage injection in stacked multicell converter. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 4700–4714. [Google Scholar] [CrossRef]

- Davis, T.T.; Joseph, T.; Dey, A. A capacitor voltage balancing scheme for single-source fed switch optimized three-phase nine-level inverter. IEEE Trans. Ind. Electron. 2021, 68, 3652–3661. [Google Scholar] [CrossRef]

- Tian, K.; Wu, B.; Narimani, M.; Xu, D.; Cheng, Z.Y.; Zargari, N.R. A capacitor voltage-balancing method for nested neutral point clamped (NNPC) inverter. IEEE Trans. Power Electron. 2016, 31, 2575–2583. [Google Scholar] [CrossRef]

- Wang, K.; Xu, L.; Zheng, Z.D.; Li, Y.D. Voltage balancing control of a four-level hybrid-clamped converter based on zero-sequence voltage injection using phase-shifted PWM. IEEE Trans. Power Electron. 2016, 31, 5389–5399. [Google Scholar] [CrossRef]

- Li, W.C.; Ma, W.M.; Wang, G.G.; Lin, C.M.; Lie, S.X.; Guo, D.H. Novel space vector pulse width modulation method for neutral point clamped H-bridge cascaded single-phase inverter. Proc. CSEE 2014, 34, 5313–5319. [Google Scholar]

- Liu, B.; Feng, X.Y.; Deng, R.; Xia, W.J.; Song, W.S. Grid voltage sensorless control strategy of single-phase PWM rectifiers with model reference adaptive system. Proc. CSEE 2019, 39, 6065–6074. [Google Scholar]

- Zhang, L.H.; Born, R.; Gu, B.; Chen, B.F.; Zheng, C.; Zhao, X.N.; Lai, J.S. A sensorless implementation of the parabolic current control for single-phase stand-alone inverters. IEEE Trans. Power Electron. 2016, 31, 3913–3921. [Google Scholar] [CrossRef]

- Viswadev, R.; Mudlapur, A.; Ramana, V.V.; Venkatesaperumal, B.; Mishra, S. A novel AC current sensorless hysteresis control for grid tie inverters. IEEE Trans. Circuits Syst. II 2020, 67, 2577–2581. [Google Scholar] [CrossRef]

- Leon, J.I.; Portillo, R.; Vazquez, S.; Padilla, J.J.; Franquelo, L.G.; Carrasco, J.M. Simple unified approach to develop a time-domain modulation strategy for single-phase multilevel converters. IEEE Trans. Ind. Electron. 2008, 55, 3239–3248. [Google Scholar] [CrossRef]

- Liu, F.; Wu, X.Z.; Zhao, Y.M.; Liu, J.D.; Zhang, P.; Zhao, Y.X.; Wang, J. Research on common mode voltage suppression technology of multilevel inverter based on one-dimensional space vector modulation. Power Syst. Technol. 2020, 44, 3972–3982. [Google Scholar]

- Teymour, H.R.; Sutanto, D.; Muttaqi, K.M.; Cinfo, P. A novel modulation technique and a new balancing control strategy for a single-phase five-level ANPC converter. IEEE Trans. Ind. Appl. 2015, 51, 1215–1227. [Google Scholar] [CrossRef]

| S1–S7 | States | VC3 | VC4 | VO | ||

|---|---|---|---|---|---|---|

| IO > 0 | IO < 0 | IO > 0 | IO < 0 | |||

| 1000100 | P4 | - | - | - | - | 4E |

| 1000001 | P3 | ↑ | ↓ | - | - | 3E |

| 1000010 | P2P | ↑ | ↓ | ↑ | ↓ | 2E |

| 0010100 | P2N | ↓ | ↑ | ↓ | ↑ | 2E |

| 0010001 | P1 | - | - | ↓ | ↑ | E |

| 0100100 | OP | - | - | - | - | 0 |

| 0010010 | ON | - | - | - | - | 0 |

| 0100001 | N1 | ↑ | ↓ | - | - | E |

| 0100010 | N2P | ↑ | ↓ | ↑ | ↓ | −2E |

| 0001100 | N2N | ↓ | ↑ | ↓ | ↑ | −2E |

| 0001001 | N3 | - | - | ↑ | −3E | |

| 0001010 | N4 | - | - | - | - | −4E |

| Parameters | ANPC-9L | SMC-9L | Proposed Topology |

|---|---|---|---|

| number of switching devices | 12 | 16 | 10 |

| switching devices withstand voltage | 4E × 4 + E × 8 | E × 16 | 4E × 6 + E × 4 |

| capacitive voltage sensing number of devices | 5 | 8 | 4 |

| number of floating capacitors | 3 | 6 | 2 |

| suspension capacitance withstand voltage | 3E × 1 + 2E × 1 + E × 1 | 3E × 2 + 2E × 2 + E × 2 | E × 2 |

| VO | Total Number of Devices in the Current Path | ||

|---|---|---|---|

| ANPC-9L | SMC-9L | Proposed Topology | |

| 4E | 5 | 4 | 2 |

| 3E | 5 | 5 | 3 |

| 2E | 5 | 6 | 2 |

| E | 5 | 7 | 4 |

| 0 | 5 | 8 | 3 |

| −E | 5 | 7 | 4 |

| −2E | 5 | 6 | 2 |

| −3E | 5 | 5 | 3 |

| −4E | 5 | 4 | 2 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, Y.; Huang, W.; Li, Z.; Sun, Y.; Liu, B. A Single-Phase Transformerless Nine-Level Inverter and Its Control Strategy. Energies 2022, 15, 3418. https://doi.org/10.3390/en15093418

Li Y, Huang W, Li Z, Sun Y, Liu B. A Single-Phase Transformerless Nine-Level Inverter and Its Control Strategy. Energies. 2022; 15(9):3418. https://doi.org/10.3390/en15093418

Chicago/Turabian StyleLi, Yuan, Wenwen Huang, Zhen Li, Yue Sun, and Bi Liu. 2022. "A Single-Phase Transformerless Nine-Level Inverter and Its Control Strategy" Energies 15, no. 9: 3418. https://doi.org/10.3390/en15093418