Passivating Silicon Tunnel Diode for Perovskite on Silicon Nip Tandem Solar Cells

Abstract

:1. Introduction

2. Results and Discussion

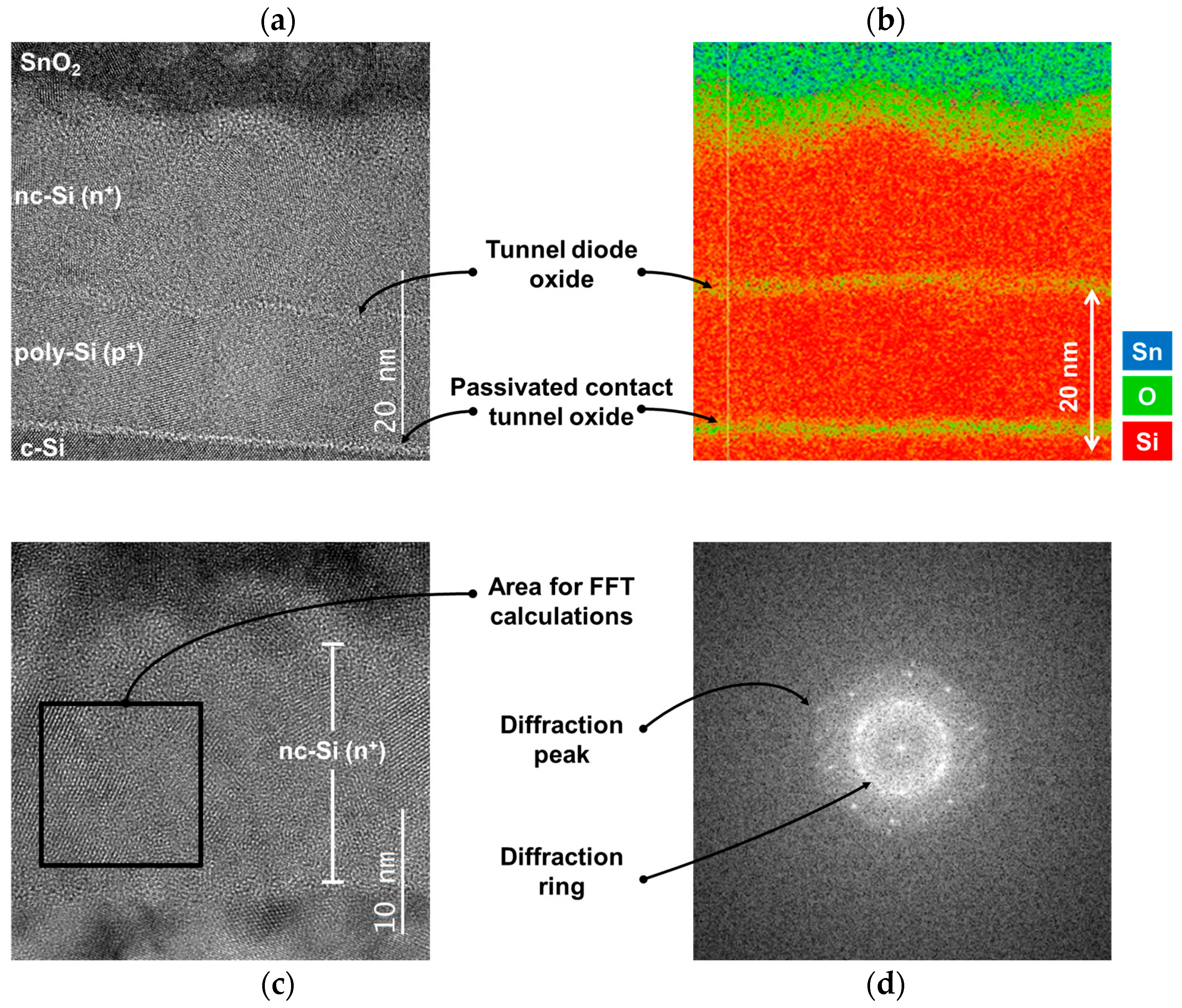

2.1. n+/p+ Tunnel Diode Fabrication

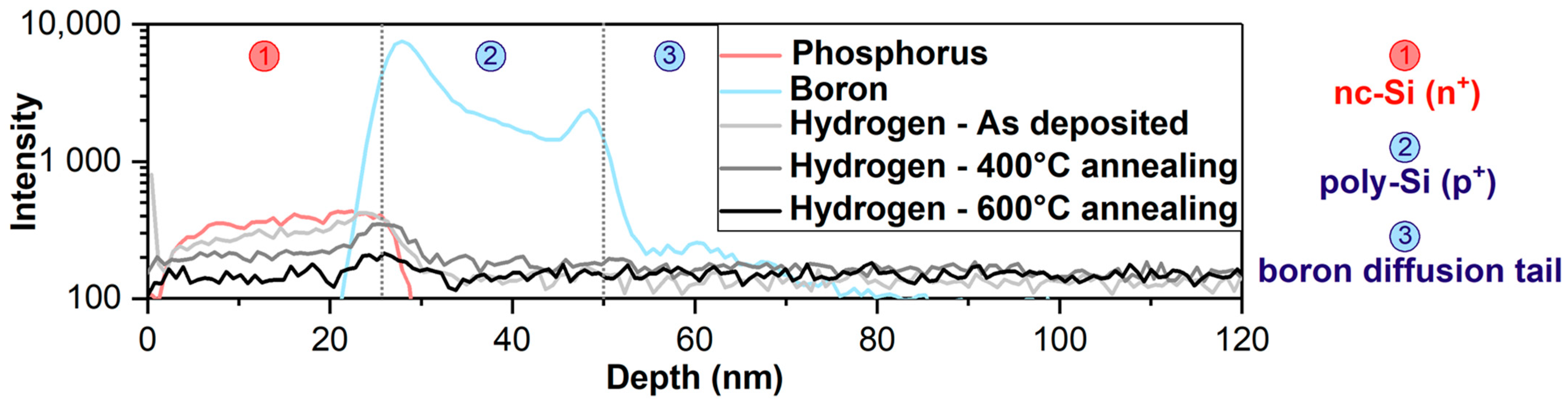

2.2. Passivation Quality Assessment

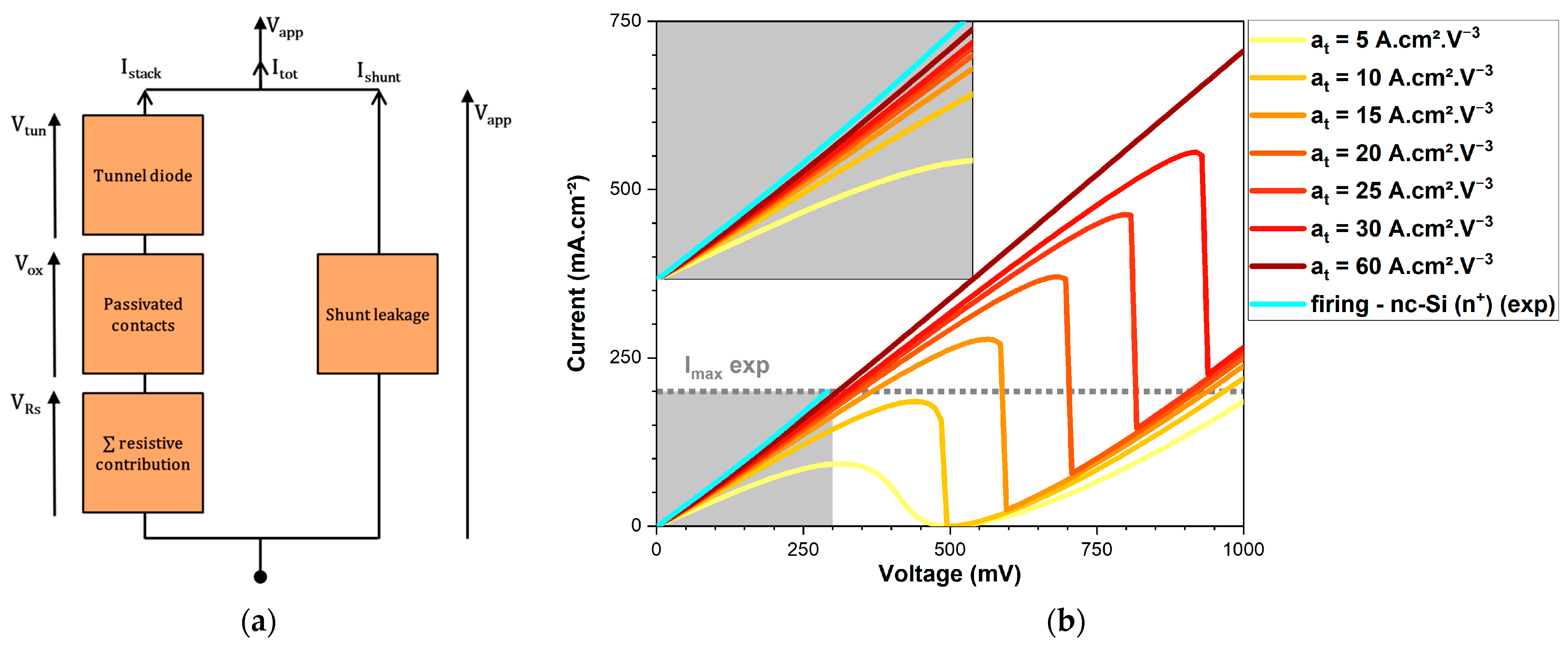

2.3. Conduction Assessment

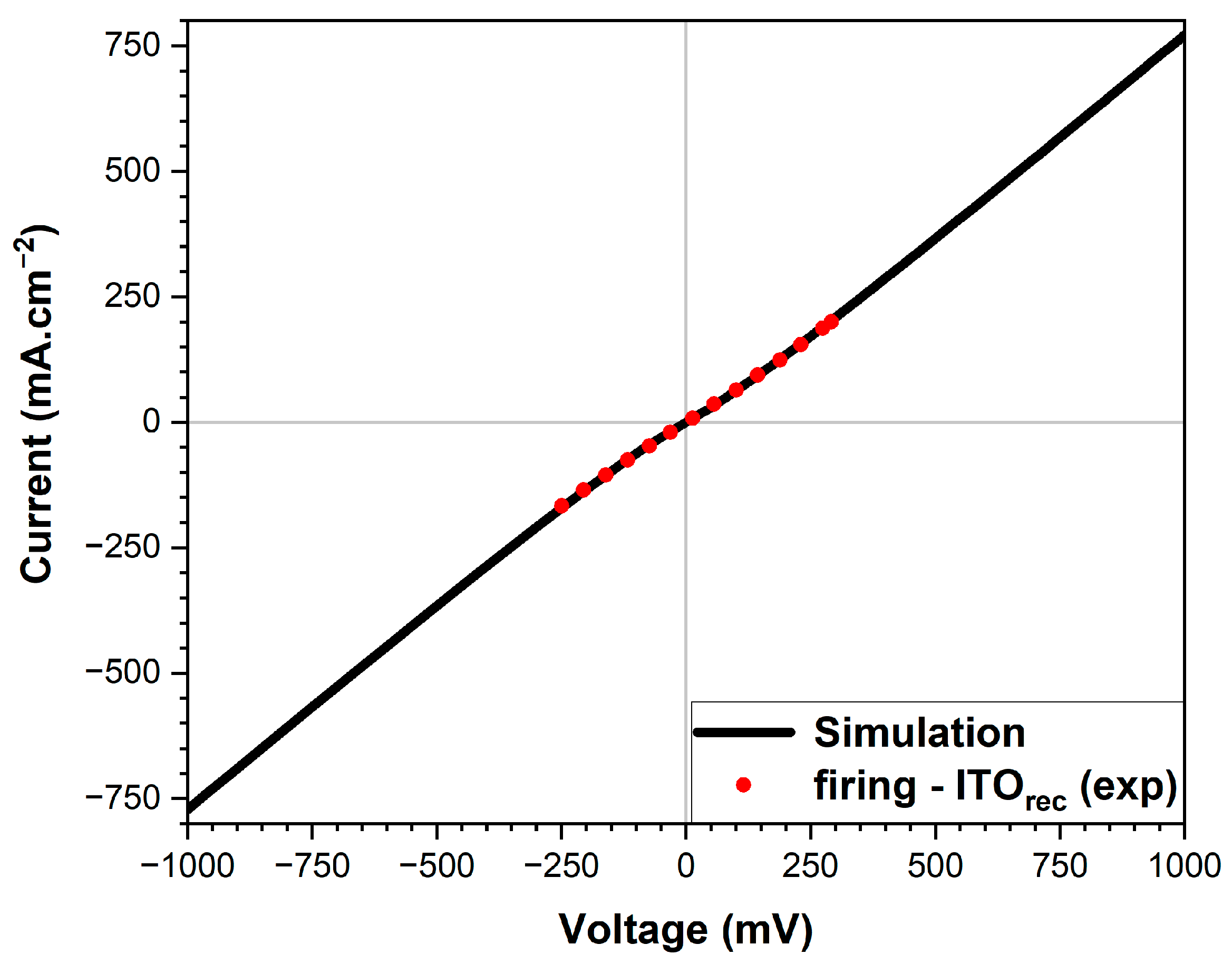

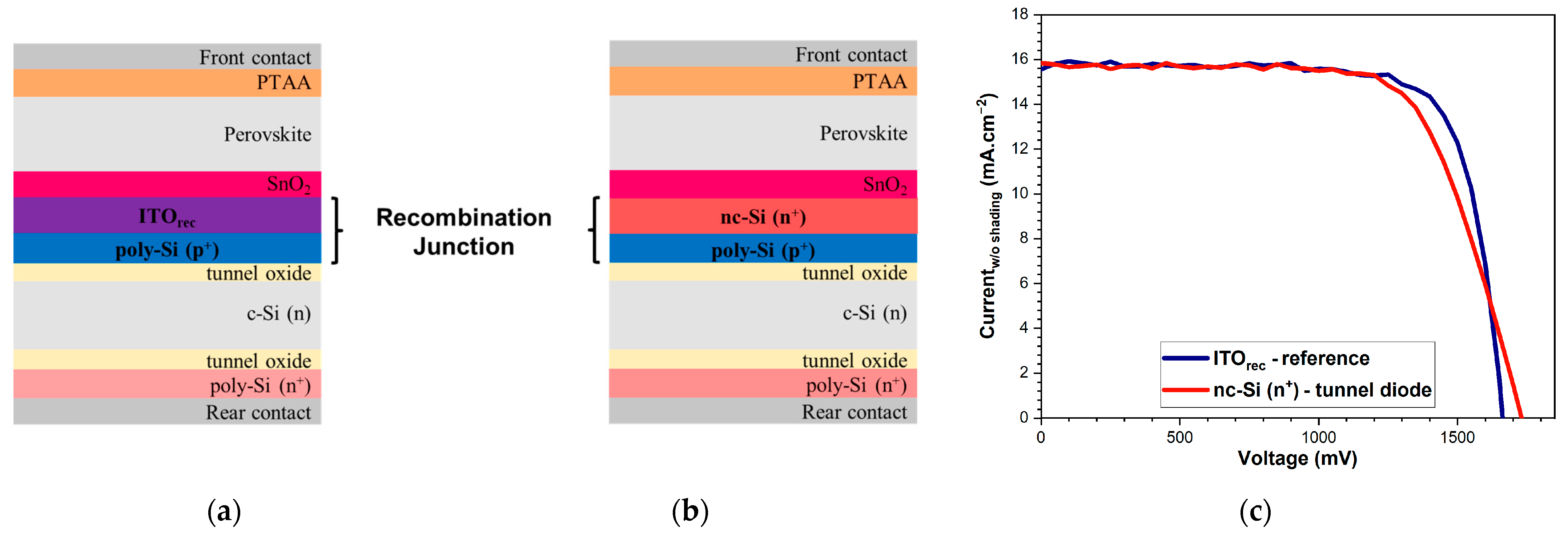

2.4. Tandem Integration

3. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Appendix A. Dark IV Simulation of Resistivity Samples

References

- International Technology Roadmap for Photovoltaic (ITRPV)—vdma.org—VDMA. Available online: https://www.vdma.org/international-technology-roadmap-photovoltaic (accessed on 23 February 2023).

- At 26.81%, LONGi Sets a New World Record Efficiency for Silicon Solar Cells, Longi. Available online: https://www.longi.com/en/news/propelling-the-transformation// (accessed on 23 February 2023).

- JinkoSolar’s High-Efficiency N-Type Monocrystalline Silicon Solar Cell Sets New World Record with Maximum Conversion Efficiency of 25.7%|JinkoSolar. Available online: https://ir.jinkosolar.com/news-releases/news-release-details/jinkosolars-high-efficiency-n-type-monocrystalline-silicon-0 (accessed on 23 February 2023).

- Hollemann, C.; Haase, F.; Schäfer, S.; Krügener, J.; Brendel, R.; Peibst, R. 26.1%-efficient POLO-IBC cells: Quantification of electrical and optical loss mechanisms. Prog. Photovolt. Res. Appl. 2019, 27, 950–958. [Google Scholar] [CrossRef]

- Richter, A.; Hermle, M.; Glunz, S.W. Reassessment of the Limiting Efficiency for Crystalline Silicon Solar Cells. IEEE J. Photovolt. 2013, 3, 1184–1191. [Google Scholar] [CrossRef]

- NREL. Best Research-Cell Efficiency Chart. Available online: https://www.nrel.gov/pv/cell-efficiency.html (accessed on 23 February 2023).

- Li, X. High-Efficiency Si Solar Cell Including Tunnel Junction for Tandem Photovoltaic Cells. Ph.D. Thesis, Université de Lyon, Lyon, France, 2021; p. 155. [Google Scholar]

- Helmholtz-Zentrum Berlin. World Record Back at HZB: Tandem Solar Cell Achieves 32.5 Percent Efficiency, HZB Website. Available online: https://www.helmholtz-berlin.de/pubbin/news_seite?nid=24348;sprache=en (accessed on 23 February 2023).

- Leijtens, T.; Bush, K.A.; Prasanna, R.; McGehee, M.D. Opportunities and challenges for tandem solar cells using metal halide perovskite semiconductors. Nat. Energy 2018, 3, 10. [Google Scholar] [CrossRef]

- Communication from the Commission to The European Parliament; The Council; The European Economic and Social Committee; The Committee of The Regions. Critical Raw Materials Resilience: Charting a Path towards greater Security and Sustainability. 2020. Available online: https://eur-lex.europa.eu/legal-content/EN/TXT/?uri=CELEX:52020DC0474 (accessed on 28 April 2023).

- Kim, M.; Zhang, Y.; Verlinden, P.; Hallam, B. Towards sustainable silicon PV manufacturing at the terawatt level. AIP Conf. Proc. 2022, 2487, 090001. [Google Scholar] [CrossRef]

- De Bastiani, M.; Subbiah, A.S.; Aydin, E.; Isikgor, F.H.; Allen, T.G.; De Wolf, S. Recombination junctions for efficient monolithic perovskite-based tandem solar cells: Physical principles, properties, processing and prospects. Mater. Horiz. 2020, 7, 2791–2809. [Google Scholar] [CrossRef]

- Chi, W.; Banerjee, S.K.; Jayawardena, K.G.D.I.; Silva, S.R.P.; Seok, S.I. Perovskite/Silicon Tandem Solar Cells: Choice of Bottom Devices and Recombination Layers. ACS Energy Lett. 2023, 8, 1535–1550. [Google Scholar] [CrossRef]

- Shen, H.; Walter, D.; Wu, Y.; Fong, K.C.; Jacobs, D.A.; Duong, T.; Peng, J.; Weber, K.; White, T.P.; Catchpole, K.R. Monolithic Perovskite/Si Tandem Solar Cells: Pathways to Over 30% Efficiency. Adv. Energy Mater. 2019, 10, 1902840. [Google Scholar] [CrossRef]

- Nogay, G.; Sahli, F.; Werner, J.; Monnard, R.; Boccard, M.; Despeisse, M.; Haug, F.-J.; Jeangros, Q.; Ingenito, A.; Ballif, C. 25.1%-Efficient Monolithic Perovskite/Silicon Tandem Solar Cell Based on a p-type Monocrystalline Textured Silicon Wafer and High-Temperature Passivating Contacts. ACS Energy Lett. 2019, 4, 844–845. [Google Scholar] [CrossRef]

- Sahli, F.; Kamino, B.A.; Werner, J.; Bräuninger, M.; Paviet-Salomon, B.; Barraud, L.; Monnard, R.; Seif, J.P.; Tomasi, A.; Jeangros, Q.; et al. Improved Optics in Monolithic Perovskite/Silicon Tandem Solar Cells with a Nanocrystalline Silicon Recombination Junction. Adv. Energy Mater. 2018, 8, 1701609. [Google Scholar] [CrossRef]

- Sahli, F.; Werner, J.; Kamino, B.A.; Bräuninger, M.; Monnard, R.; Paviet-Salomon, B.; Barraud, L.; Ding, L.; Leon, J.J.D.; Sacchetto, D.; et al. Fully textured monolithic perovskite/silicon tandem solar cells with 25.2% power conversion efficiency. Nat. Mater. 2018, 17, 9. [Google Scholar] [CrossRef] [PubMed]

- Seron, C.; Desrues, T.; Jay, F.; Lanterne, A.; Torregrosa, F.; Borvon, G.; Rafhay, Q.; Kaminski, A.; Dubois, S. Hydrogenation of sputtered ZnO:Al layers for double side poly-Si/SiOx solar cells. EPJ Photovolt. 2022, 13, 8. [Google Scholar] [CrossRef]

- Luderer, C.; Penn, M.; Reichel, C.; Feldmann, F.; Goldschmidt, J.C.; Richter, S.; Hahnel, A.; Naumann, V.; Bivour, M.; Hermle, M. Controlling Diffusion in Poly-Si Tunneling Junctions for Monolithic Perovskite/Silicon Tandem Solar Cells. IEEE J. Photovolt. 2021, 11, 1395–1402. [Google Scholar] [CrossRef]

- Penn, M.; Luderer, C.; Reichel, C.; Goldschmidt, J.C.; Feldmann, F.; Bivour, M.; Hermle, M. Passivating Poly-Si Tunnel Junctions with Oxide-based Diffusion Barriers for Interconnection in Perovskite/Si Tandem Solar Cells. AIP Conf. Proc. 2022, 2487, 4. [Google Scholar]

- Esaki, L. New Phenomenon in Narrow Germaniump−nJunctions. Phys. Rev. 1958, 109, 603–604. [Google Scholar] [CrossRef]

- Burgelman, M.; Nollet, P.; Degrave, S. Modelling polycrystalline semiconductor solar cells. Thin Solid Film. 2000, 361–362, 527–532. [Google Scholar] [CrossRef]

- Song, L.; Hu, Z.; Lin, D.; Yang, D.; Yu, X. Progress of hydrogenation engineering in crystalline silicon solar cells: A review. J. Phys. D Appl. Phys. 2022, 55, 453002. [Google Scholar] [CrossRef]

- Sze, S.M.; Lee, M.K. Semiconductor Devices, Physics and Technology, 3rd ed.; Wiley: Hoboken, NJ, USA, 2012. [Google Scholar]

- Arunachalam, B.; Rafhay, Q.; Roy, D.; Kaminski-Cachopo, A. Simulation Study of High-Speed Ge Photodetector Dark and Light Current Degradation. IEEE Trans. Device Mater. Reliab. 2022, 22, 410–416. [Google Scholar] [CrossRef]

- Jeon, H.; Choi, H.; Cho, Y.S.; Ryoo, K.K.; Jung, S.D. Effects of UV/O3 and SC1 Steps for the HF Last Silicon Wafer Cleaning. MRS Online Proc. Libr. 1995, 386, 297–302. [Google Scholar] [CrossRef]

- Moldovan, A.; Feldmann, F.; Krugel, G.; Zimmer, M.; Rentsch, J.; Hermle, M.; Roth-Fölsch, A.; Kaufmann, K.; Hagendorf, C. Simple Cleaning and Conditioning of Silicon Surfaces with UV/Ozone Sources. Energy Procedia 2014, 55, 834–844. [Google Scholar] [CrossRef]

- Press, W.H. (Ed.) FORTRAN Numerical Recipes, 2nd ed.; Cambridge University Press: Cambridge, NY, USA, 1996. [Google Scholar]

| Steps | Poly-Si (p+) Formation (Both Sides) | nc-Si (n+) Deposition (Front Side) | 400 °C (N2) | 600 °C (N2) | 400 °C (N2 + O2) |

|---|---|---|---|---|---|

| iVOC (mV) | 691.3 (±3.7) | 680.1 (±10.4) | 681.7 (±1.0) ΔiVOC = +7.3 | 671.7 (±3.6) ΔiVOC = −8.4 | 688.7 (±3.4) ΔiVOC = +8.0 |

| RS | Rshunt | J0 | n |

|---|---|---|---|

| 1.20 Ω·cm2 | 60 Ω·cm2 | 0.1 A·cm−2 | 1.3 |

| Interlayer | VOC (mV) | ISC (mA.cm−2) | FF (%) | PCE (%) |

|---|---|---|---|---|

| ITOrec | 1676 ± 19 | 15.7 ± 0.2 | 75.6 ± 0.8 | 19.9 ± 0.2 |

| nc-Si (n+) | 1688 ± 40 | 16.1 ± 0.8 | 69.3 ± 0.8 | 18.8 ± 0.4 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Marteau, B.; Desrues, T.; Rafhay, Q.; Kaminski, A.; Dubois, S. Passivating Silicon Tunnel Diode for Perovskite on Silicon Nip Tandem Solar Cells. Energies 2023, 16, 4346. https://doi.org/10.3390/en16114346

Marteau B, Desrues T, Rafhay Q, Kaminski A, Dubois S. Passivating Silicon Tunnel Diode for Perovskite on Silicon Nip Tandem Solar Cells. Energies. 2023; 16(11):4346. https://doi.org/10.3390/en16114346

Chicago/Turabian StyleMarteau, Baptiste, Thibaut Desrues, Quentin Rafhay, Anne Kaminski, and Sébastien Dubois. 2023. "Passivating Silicon Tunnel Diode for Perovskite on Silicon Nip Tandem Solar Cells" Energies 16, no. 11: 4346. https://doi.org/10.3390/en16114346