Simple Discrete Control of a Single-Phase Voltage Source Inverter in a UPS System for Low Switching Frequency

Abstract

:1. Introduction

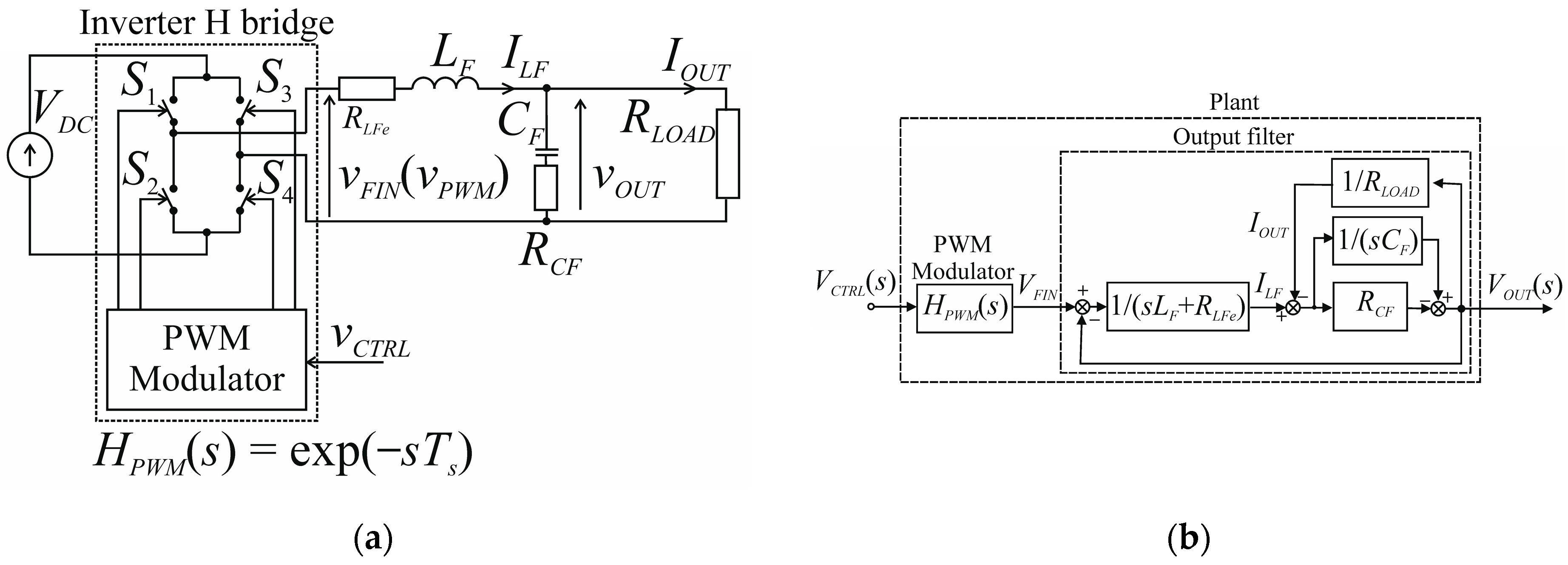

2. Continuous Model of the Voltage Source Inverter

3. Modulation Scheme

4. Design of the Output Filter

5. Discretizing the Continuous Model of the VSI

6. The Discrete Model of the VSI

7. Measuring Bode Plots of the Inverter and Measuring Traces

8. The Prediction of the State Variables

9. Simulation of the Inverter with the Delay in the Measurement Traces

10. The Experimental Verification of Output Voltage Distortions

11. Results

12. Discussion

13. Conclusions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| VSI | Voltage Source Inverter; |

| THD | Total Harmonic Distortion; |

| CDM | Coefficient Diagram Method; |

| PBC | Passivity-Based Control; |

| ESR | Equivalent Series Resistance of the capacitor. |

| The inverter parameters symbols: | |

| CF | The output filter capacitor or capacitance (Figure 1 and Figure 2); |

| LF | The output filter coil or inductance (Figure 1 and Figure 2); |

| RCF | The series resistance of the output capacitor (ESR), assigned equal to 0; |

| RLFe | The equivalent serial resistance of the whole inverter, the sum of the serial resistance of the filter coil LF, the resistances of two (on the diagonal of the inverter bridge) switched-on transistors in the bridge and the resistance of the PCB traces, connections, etc., strongly depends on the power losses in the output filter coil core; |

| fs | The switching frequency; |

| fm | The fundamental frequency (50 Hz); |

| ωF0 | The angular resonant frequency of the output filter; |

| ωmax | The angular frequency, for which the magnitude Bode plot has the maximum; |

| Ts | The switching period; |

| TON | The switching-on time. |

| The load parameters symbols: | |

| RLOAD | The load resistance (Figure 1) for the pure resistive load; |

| R, C | the resistance and the capacitance of the nonlinear rectifier RC load (according to EN-62040-3 for PF = 0.7). |

| The currents and voltages symbols: | |

| ILF, iLF | The filter coil (inductor) current (Figure 1 and Figure 2); |

| ILFh1RMS | The RMS value of the fundamental harmonic of the inductor current; |

| IOUT, iOUT | The inverter output current (Figure 1 and Figure 2); |

| VDC | The DC voltage supplying the inverter (Figure 1 and Figure 2); |

| VCTRL, vCTRL | The input voltage of the PWM modulator—the control voltage (Figure 1 and Figure 2); |

| VOUT, vOUT | The output voltage of the inverter (Figure 1 and Figure 2); |

| VOUTh1 | The amplitude of the fundamental harmonic (the first harmonic) of the inverter output voltage; |

| VOUTh1RMS | The RMS value of the fundamental harmonic of the inverter output voltage; |

| VOUTripplepp | The peak-to-peak value of the output ripple voltage; |

| VPWM, vPWM | The square output voltage waveform of the inverter bridge, the input voltage of the filter; |

| VFIN, vFIN | The envelope of the inverter bridge input voltage VPWM used in calculations—delayed to vCTRL with Ts. |

| The transfer functions symbols: | |

| The transfer function of the control signal of the inverter with the PWM modulator; | |

| The discretized transfer function of the inverter with the PWM modulator; | |

| The transfer function of the bridge with the output filter without the PWM modulator; | |

| KAMP | The transfer function of the measuring trace; |

| FLC(s) | Transfer function of the output filter, equal to KINV(s); |

| ZOUT(s) | output impedance of the inverter. |

| The state variables and matrixes symbols: | |

| A, B and C | The state matrix, input matrix and output matrix of the inverter, respectively; |

| The inverter state variables vector; | |

| The predicted state variables vector; | |

| The inverter input vector (in the presented case one variable); | |

| The inverter output vector (in the presented case one variable); | |

| The predicted inverter output vector; | |

| The discrete state matrix of the inverter; | |

| The discrete control matrix of the inverter; | |

| Coefficients of the discrete state matrix; | |

| gij | Coefficients of the discrete control matrix; |

| Luenberger observer symbols: | |

| The discretized Luenberger observer gain matrix; | |

| li | Gains in the Luenberger observer gain matrix; |

| The CDM symbols: | |

| The discretized characteristic equation of the closed-loop system (Manabe Standard Form); | |

| τ/Ts | The relative time constant of the closed-loop system. |

| The PBC symbols: | |

| H(x) | The Hamiltonian function (Lyapunov function). |

| The other symbols: | |

| Fcost | The cost function equal to the sum of the absolute values of the reactive powers in the output filter inductor and capacitor; |

| S1, S2, S3, S4 | The control signals of the bridge transistors; |

| THDVOUT | Total harmonic distortion of the output voltage. |

References

- IEC 62040-3:2021; Uninterruptible Power Systems (UPS)—Part 3: Method of Specifying the Performance and Test Requirements. IEC: Geneva, Switzerland, 2021.

- Steinmetz, C.P. On the law of hysteresis. Trans. Am. Inst. Electr. Eng. 1892, 9, 3–64. [Google Scholar] [CrossRef]

- Bertotti, G. General properties of power losses in soft ferromagnetic materials. IEEE Trans. Magn. 1988, 24, 621–630. [Google Scholar] [CrossRef]

- Kazimierczuk, M.A. High Frequency Magnetic Components, 2nd ed.; Wiley & Sons: Hoboken, NJ, USA, 2014. [Google Scholar]

- Yuan, W.; Wang, Y.; Liu, D.; Deng, F.; Chen, Z. Robust droop control of ac microgrid against nonlinear characteristic of inductor. In Proceedings of the IEEE 10th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Xi’an, China, 3–6 June 2019; pp. 642–647. [Google Scholar] [CrossRef]

- Cheng, X.; Chen, Y.; Chen, X.; Zhang, B.; Qiu, D. An extended analytical approach for obtaining the steady-state periodic solutions of SPWM single-phase inverters. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 24 August 2017; pp. 1311–1316. [Google Scholar] [CrossRef]

- Cheng, Y.; Zha, X.; Liu, Y. Nonlinear modeling of inverter using the Hammerstein’s approach. In Proceedings of the INTELEC 2009—31st International Telecommunications Energy Conference, Incheon, Republic of Korea, 18–22 October 2009; pp. 1–4. [Google Scholar] [CrossRef]

- Rymarski, Z. The discrete model of the power stage of the voltage source inverter for UPS. Int. J. Electron. 2011, 98, 1291–1304. [Google Scholar] [CrossRef]

- 2021 Alloy Powder Products Catalog, Micrometals Powder Core Solutions. Available online: https://www.micrometals.com/design-and-applications/literature/ (accessed on 25 July 2023).

- Micrometals 2022 Iron Powder Cores Catalog. Available online: https://www.micrometals.com/design-and-applications/literature/ (accessed on 25 July 2023).

- Rymarski, Z. Measuring the real parameters of single-phase voltage source inverters for UPS systems. Int. J. Electron. 2017, 104, 1020–1033. [Google Scholar] [CrossRef]

- Bernacki, K.; Rymarski, Z.; Dyga, Ł. Selecting the coil core powder material for the output filter of a voltage source inverter. Electron. Lett. 2017, 53, 1068–1069. [Google Scholar] [CrossRef]

- Rymarski, Z.; Bernacki, K.; Dyga, Ł. Measuring the power conversion losses in voltage source inverters. AEU-Int. J. Electron. Commun. 2020, 124, 153359. [Google Scholar] [CrossRef]

- Rymarski, Z.; Bernacki, K. Different Features of Control Systems for Single-Phase Voltage Source Inverters. Energies 2020, 13, 4100. [Google Scholar] [CrossRef]

- Bernacki, K.; Rymarski, Z. The Effect of Replacing Si-MOSFETs with WBG Transistors on the Control Loop of Voltage Source Inverters. Energies 2022, 15, 5316. [Google Scholar] [CrossRef]

- Astrom, K.A.; Wittenmark, B. Computer-Controlled Systems: Theory and Design, 3rd ed.; Dover Publications, Dover Books on Electrical Engineering: Garden City, NY, USA, 2011; ISBN 13 978-0486486130. [Google Scholar]

- Kumar, V.E.; Jerome, E.J.; Ayyappan, S. Comparison of four state observer design algorithms for MIMO system. Arch. Control Sci. 2013, 23, 243–256. [Google Scholar] [CrossRef] [Green Version]

- Luenberger, D.G. Observing the state of a linear system. IEEE Trans. Mil. Electron. 1964, 8, 74–80. [Google Scholar] [CrossRef]

- Luenberger, D.G. An introduction to observers. IEEE Trans. Autom. Control 1971, 16, 596–602. [Google Scholar] [CrossRef]

- Blachuta, M.; Rymarski, Z.; Bieda, R.; Bernacki, K.; Grygiel, R. Design, Modeling and Simulation of PID Control for DC/AC Inverters. In Proceedings of the 24th International Conference on Methods and Models in Automation and Robotics, Międzyzdroje, Poland, 26–29 August 2019; pp. 428–433. [Google Scholar] [CrossRef]

- Blachuta, M.; Rymarski, Z.; Bieda, R.; Bernacki, K.; Grygiel, R. Continuous-time approach to discrete-time PID Control for UPS inverters—A case study. In Proceedings of the Asian Conference on Intelligent Information and Database Systems, ACIIDS, Phuket, Thailand, 23–26 March 2020; pp. 1–12. [Google Scholar]

- Ben-Brahim, L.; Yokoyama, T.; Kawamura, A. Digital control for UPS inverters. In Proceedings of the Fifth International Conference on Power Electronics and Drive Systems (PEDS 2003), Singapore, 17–20 November 2003; Volume 2, pp. 1252–1257. [Google Scholar]

- Deng, H.; Srinivasan, D.; Oruganti, R. Modeling and control of single-phase UPS inverters: A survey. In Proceedings of the 2005 International Conference on Power Electronics and Drives Systems (PEDS 2005), Kuala Lumpur, Malaysia, 28 November–1 December 2005; Volume 2, pp. 848–853. [Google Scholar]

- Rymarski, Z. The influence of the output filter parameters tolerance and the load on the PID/CDM control of the single phase VSI. Przegląd Elektrotechniczny 2011, 87, 114–117. [Google Scholar]

- Borsalani, J.; Dastfan, A. Decoupled phase voltages control of three phase four-leg voltage source inverter via state feedback. In Proceedings of the 2012 2nd International eConference on Computer and Knowledge Engineering (ICCKE), Mashhad, Iran, 18–19 October 2012; pp. 71–76. [Google Scholar] [CrossRef]

- Serra, F.M.; De Angelo, C.H.; Forchetti, D.G. IDA-PBC control of a DC–AC converter for sinusoidal three-phase voltage generation. Int. J. Electron. 2016, 104, 93–110. [Google Scholar] [CrossRef]

- Moon, S.; Choe, J.M.; Lai, J.S. Design of a state-space controller employing a deadbeat state observer for ups inverters. In Proceedings of the 2017 Asian Conference on Energy, Power and Transportation Electrification (ACEPT), Singapore, 24 October 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Hu, C.; Wang, Y.; Luo, S.; Zhang, F. State-space model of an inverter-based micro-grid. In Proceedings of the 2018 3rd International Conference on Intelligent Green Building and Smart Grid (IGBSG), Yilan, Taiwan, 22 April 2018; pp. 1–7. [Google Scholar] [CrossRef]

- Manabe, S. Coefficient diagram method. IFAC Proc. 1998, 31, 211–222. [Google Scholar] [CrossRef]

- Manabe, S. Importance of coefficient diagram in polynomial method. In Proceedings of the 42nd IEEE Conference on Decision and Control, Maui, HI, USA, 9–12 December 2003; pp. 3489–3494. [Google Scholar] [CrossRef]

- Coelho, J.P.; Pinho, T.M.; Boaventura-Cunha, J. Controller system design using the coefficient diagram method. Arab. J. Sci. Eng. 2016, 41, 3663–3681. [Google Scholar] [CrossRef]

- Rymarski, Z. Single-Phase and Three-Phase Voltage Source Inverters for UPS Systems; Wydawnictwo Politechniki Śląskiej: Gliwice, Poland, 2010; p. 238. ISBN 978-83-7335-642-9. [Google Scholar]

- Bernacki, K.; Rymarski, Z. Electromagnetic compatibility of voltage source inverters for uninterruptible power supply system depending on the pulse-width modulation scheme. IET Power Electron. 2015, 8, 1026–1034. [Google Scholar] [CrossRef]

- Van der Broeck, H.W.; Miller, M. Harmonics in DC to AC converters of single-phase uninterruptible power supplies. In Proceedings of the 17th International Telecommunications Energy Conference 1995 (INTELEC’ 95), The Hague, The Netherlands, 29 October–1 November 1995; pp. 653–658. [Google Scholar]

- Dahono, P.A.; Purwadi, A.; Qamaruzzaman. An LC filter design method for single-phase PWM inverters. In Proceedings of the International Conference on Power Electronics and Drive System, Singapore, 21–24 February 1995; Volume 2, pp. 571–576. [Google Scholar]

- Kim, J.; Choi, J.; Hong, H. Output LC filter design of voltage source inverter considering the performance of controller. In Proceedings of the International Conference on Power System Technology (PowerCon 2000), Perth, WA, Australia, 4–7 November 2000; Volume 3, pp. 1659–1664. [Google Scholar]

- Ryu, B.; Kim, J.; Choi, J.; Choi, C. Design and analysis of output filter for 3-phase UPS inverter. In Proceedings of the Power Conversion Conference, Osaka, Japan, 2–5 April 2002; Volume 3, pp. 941–946. [Google Scholar]

- Rymarski, Z. Design Method of Single-Phase Inverters for UPS Systems. Int. J. Electron. 2009, 96, 521–535. [Google Scholar] [CrossRef]

- Hyosung, K.; Seung-Ki, S. A Novel Filter Design for Output LC Filters of PWM Inverters. J. Power Electron. 2011, 11, 74–81. [Google Scholar] [CrossRef] [Green Version]

- Kawamura, A.; Chuarayapratip, R.; Haneyoshi, T. Deadbeat control of PWM inverter with modified pulse patterns for uninterruptible power supply. IEEE Trans. Ind. Electron. 1988, 35, 295–300. [Google Scholar] [CrossRef]

- Rymarski, Z. The choice of microcontroller for the voltage source inverter control in UPS system. Elektron.-Konstr. Technol. Zastos. 2012, 53, 111–114. [Google Scholar]

- Rymarski, Z.; Bernacki, K. Technical Limits of Passivity-Based Control Gains for a Single-Phase Voltage Source Inverter. Energies 2021, 14, 4560. [Google Scholar] [CrossRef]

- Kawamura, A.; Yokoyama, T. Comparison of five different approaches for real time digital feedback control of PWM inverters. In Proceedings of the 1990 IEEE Industry Applications Society Annual Meeting, Seattle, WA, USA, 7–12 October 1990; Volume 2, pp. 1005–1011. [Google Scholar]

- Kawamura, A.; Ishihara, K. Real time digital feedback control of three phase PWM inverter with quick transient response suitable for uninterruptible power supply. In Proceedings of the IEEE Industry Applications Society Annual Meeting, Pittsburgh, PA, USA, 2–7 October 1988; Volume 1, pp. 728–734. [Google Scholar]

- Montagner, V.F.; Carati, E.G.; Grundling, H.A. An adaptive linear quadratic regulator with repetitive controller applied to uninterruptible power supplies. In Proceedings of the Industry Applications Conference 2000, Rome, Italy, 8–12 October 2000; Volume 4, pp. 2231–2236. [Google Scholar]

- Bernacki, K.; Rymarski, Z. A Contemporary Design Process for Single-Phase Voltage Source Inverter Control Systems. Sensors 2022, 22, 7211. [Google Scholar] [CrossRef] [PubMed]

- Komurcugil, H. Improved passivity-based control method and its robustness analysis for single-phase uninterruptible power supply inverters. IET Power Electron. 2015, 8, 1558–1570. [Google Scholar] [CrossRef]

- Franklin, G.F.; Powel, J.D.; Workman, M.L. Digital Control of Dynamic Systems, 3rd ed.; Addison-Wesley: Hoboken, NJ, USA, 1998. [Google Scholar]

| τ/Ts, fs | pz0 | pz1 | pz2 | pz3 | l1 | l2 | l3 | Abs (Root1) | Abs (Root2) | Abs (Root3) |

|---|---|---|---|---|---|---|---|---|---|---|

| 1, 12.8 k | 1 | 0.043 | 0.015 | −0.007 | 2.852 | −7.780 | −9.215 | 0.211 | 0.211 | 0.152 |

| 2, 12.8 k | 1 | −0.866 | 0.396 | −0.082 | 1.943 | −3.194 | −3.930 | 0.459 | 0.459 | 0.389 |

| 3, 12.8 k | 1 | −1.456 | 0.846 | −0.189 | 1.353 | −1.392 | −1.764 | 0.595 | 0.595 | 0.5332 |

| 4, 12.8 k | 1 | −1.805 | 1.196 | −0.287 | 1.004 | −0.719 | −0.917 | 0.678 | 0.678 | 0.624 |

| 5, 12.8 k | 1 | −2.029 | 1.458 | −0.368 | 0.780 | −0.427 | −0.531 | 0.732 | 0.732 | 0.686 |

| 6, 12.8 k | 1 | −2.184 | 1.657 | −0.435 | 0.626 | −0.284 | −0.335 | 0.772 | 0.772 | 0.730 |

| 7, 12.8 k | 1 | −2.297 | 1.812 | −0.490 | 0.513 | −0.207 | −0.223 | 0.801 | 0.801 | 0.764 |

| Kv | Ri | l1 | l2 | l3 | THD | |

|---|---|---|---|---|---|---|

| Open loop, fs = 12,800 Hz | - | - | - | - | - | 4.63% |

| No additional delay, PBC without prediction, fs = 12,800 Hz | 0.5 | 25 | - | - | - | 1.04% |

| Additional delay 2Ts, PBC without prediction, fs = 12,800 Hz | 0.1 | 4 | - | - | - | 5.19% |

| Additional delay 2Ts, PBC with prediction, fs = 12,800 Hz | 0.1 | 4 | 0.285 | −0.778 | −0.092 | 2.80% |

| Additional delay 2Ts, PBC without prediction, fs = 51,200 Hz | 0.6 | 25 | - | - | - | 0.87% |

| Kv | Ri | l1 | l2 | l3 | THD | |

|---|---|---|---|---|---|---|

| Open loop, fs = 12,800 Hz | - | - | - | - | - | 6.35% |

| PBC without prediction, fs = 12,800 Hz | 0.1 | 4 | - | - | - | 7.63% |

| PBC with prediction, fs = 12,800 Hz | 0.2 | 9 | 0.285 | −0.778 | −0.138 | 4.09% |

| Additional delay 2Ts, PBC without prediction, fs = 51,200 Hz | 0.3 | 30 | - | - | - | 1.73% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rymarski, Z. Simple Discrete Control of a Single-Phase Voltage Source Inverter in a UPS System for Low Switching Frequency. Energies 2023, 16, 5717. https://doi.org/10.3390/en16155717

Rymarski Z. Simple Discrete Control of a Single-Phase Voltage Source Inverter in a UPS System for Low Switching Frequency. Energies. 2023; 16(15):5717. https://doi.org/10.3390/en16155717

Chicago/Turabian StyleRymarski, Zbigniew. 2023. "Simple Discrete Control of a Single-Phase Voltage Source Inverter in a UPS System for Low Switching Frequency" Energies 16, no. 15: 5717. https://doi.org/10.3390/en16155717