AC Grid–DC Microgrid Coupling with High-Performance Three-Phase Single-Stage Bidirectional Converters †

Abstract

:1. Introduction

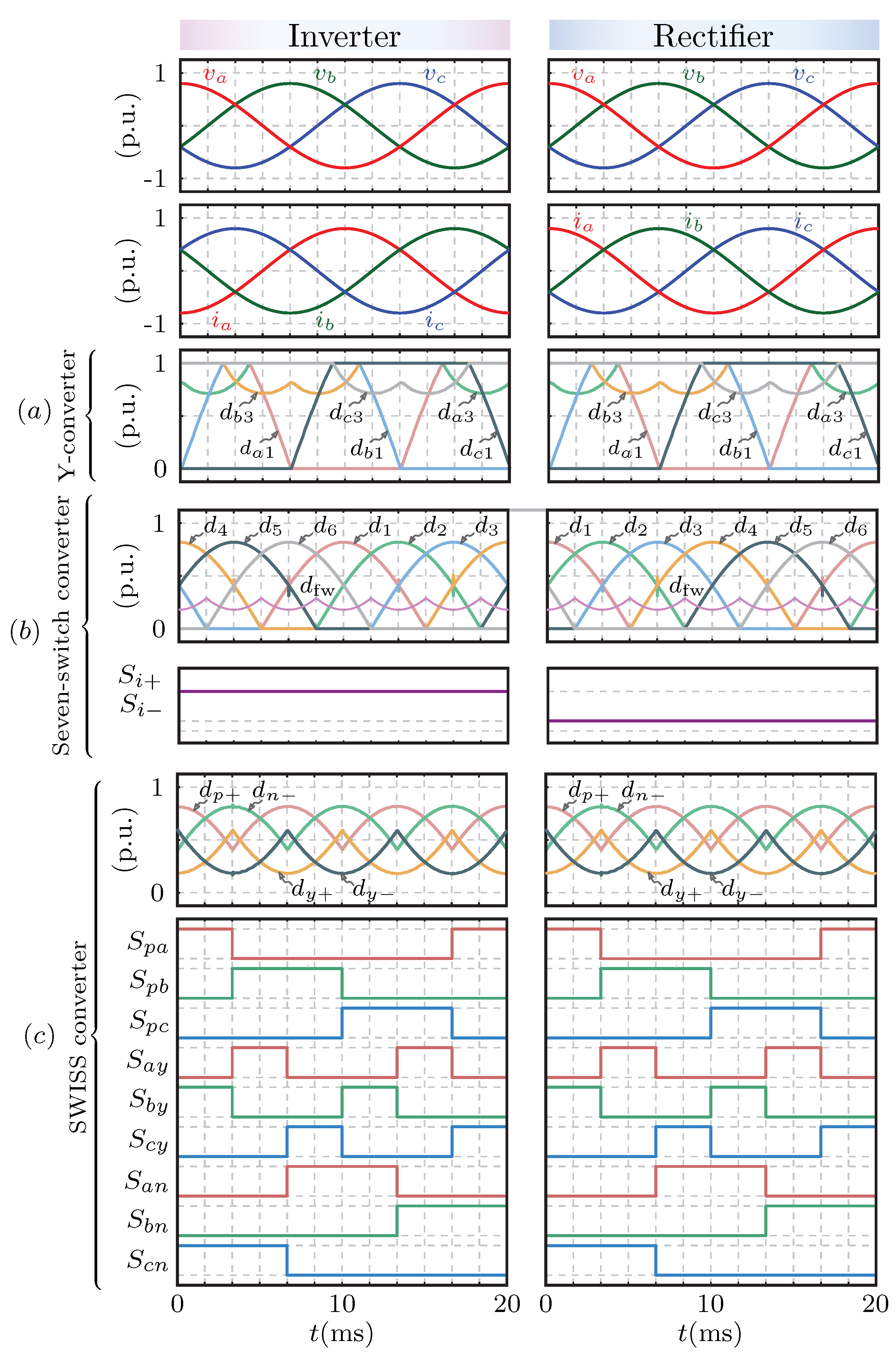

2. Topology Overview

2.1. Y-Converter

2.2. Seven-Switch Buck Converter

2.3. Swiss Converter

3. Analytical Power Loss Model

- The inductances in all converters are assumed to be constant for the whole operating power range;

- The comparison is held at a fixed junction temperature for all devices ( = 25 °C);

- The reverse recovery losses of the SiC Schottky diode are neglected as a zero-reverse recovery current diode is utilized;

- The input filter () is fixed for all topologies; the EMI filter is not considered.

3.1. Semiconductor Conduction Losses

3.2. Semiconductors Switching Losses

3.3. Inductor Losses

4. Comparative Analysis

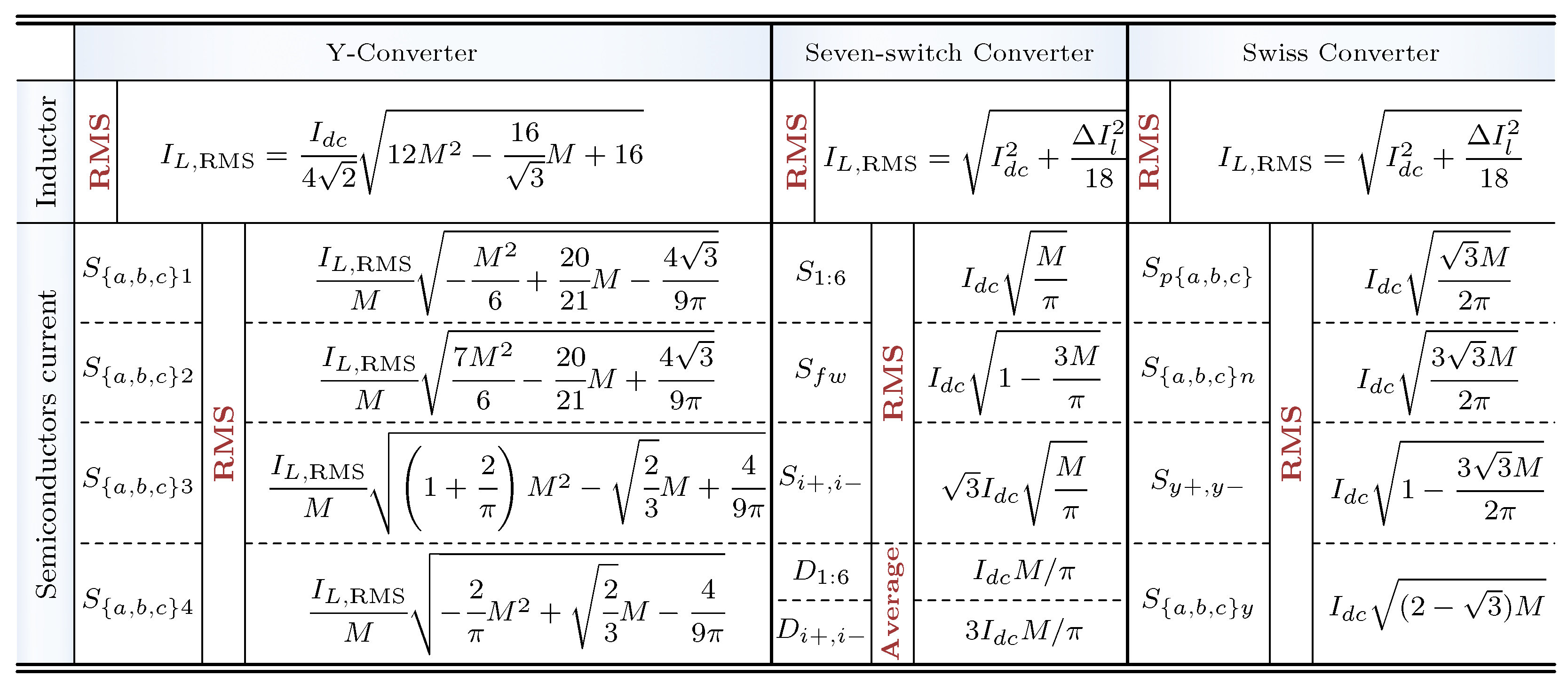

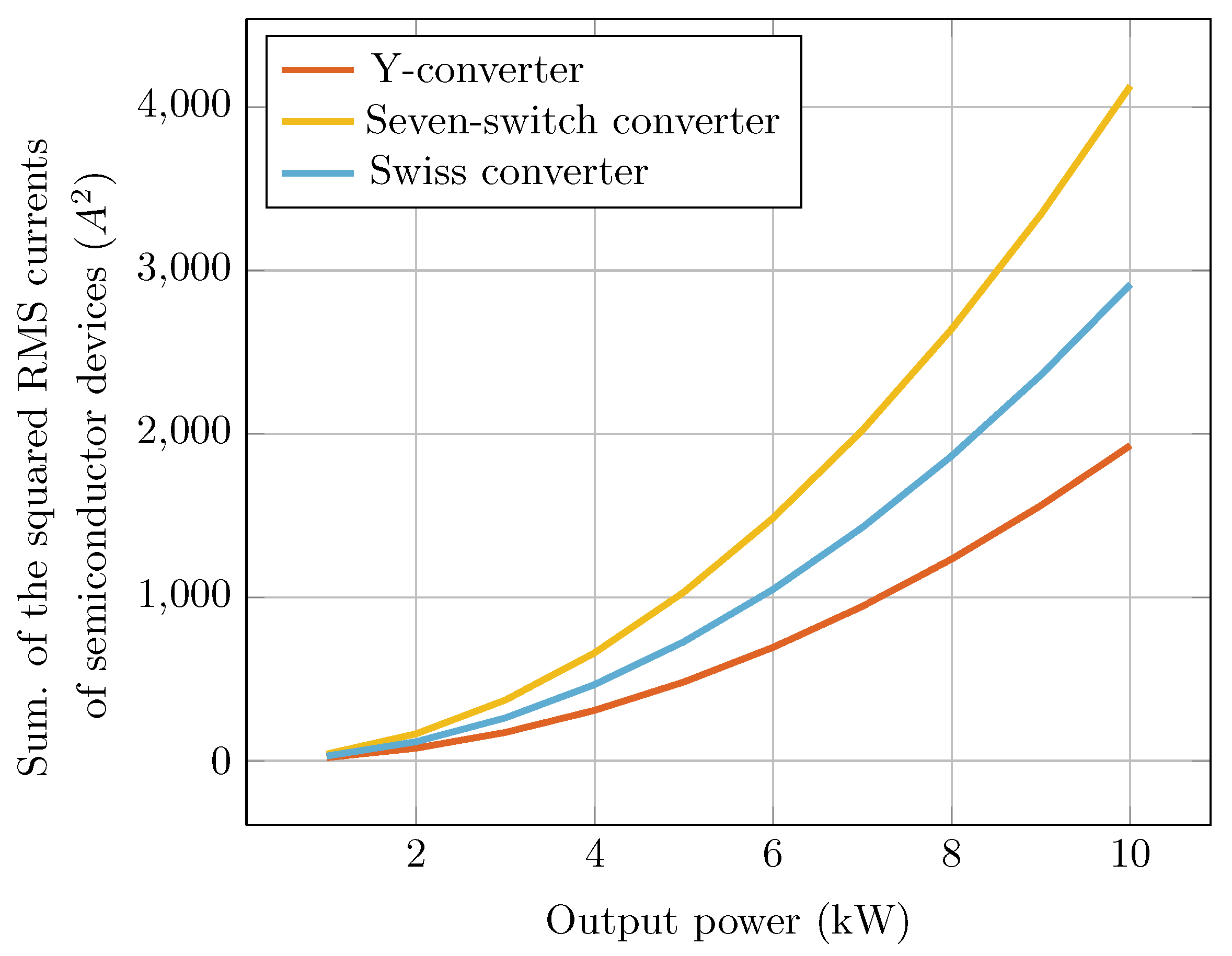

4.1. Semiconductors Stresses

4.1.1. Voltage Stresses

4.1.2. Current Stresses

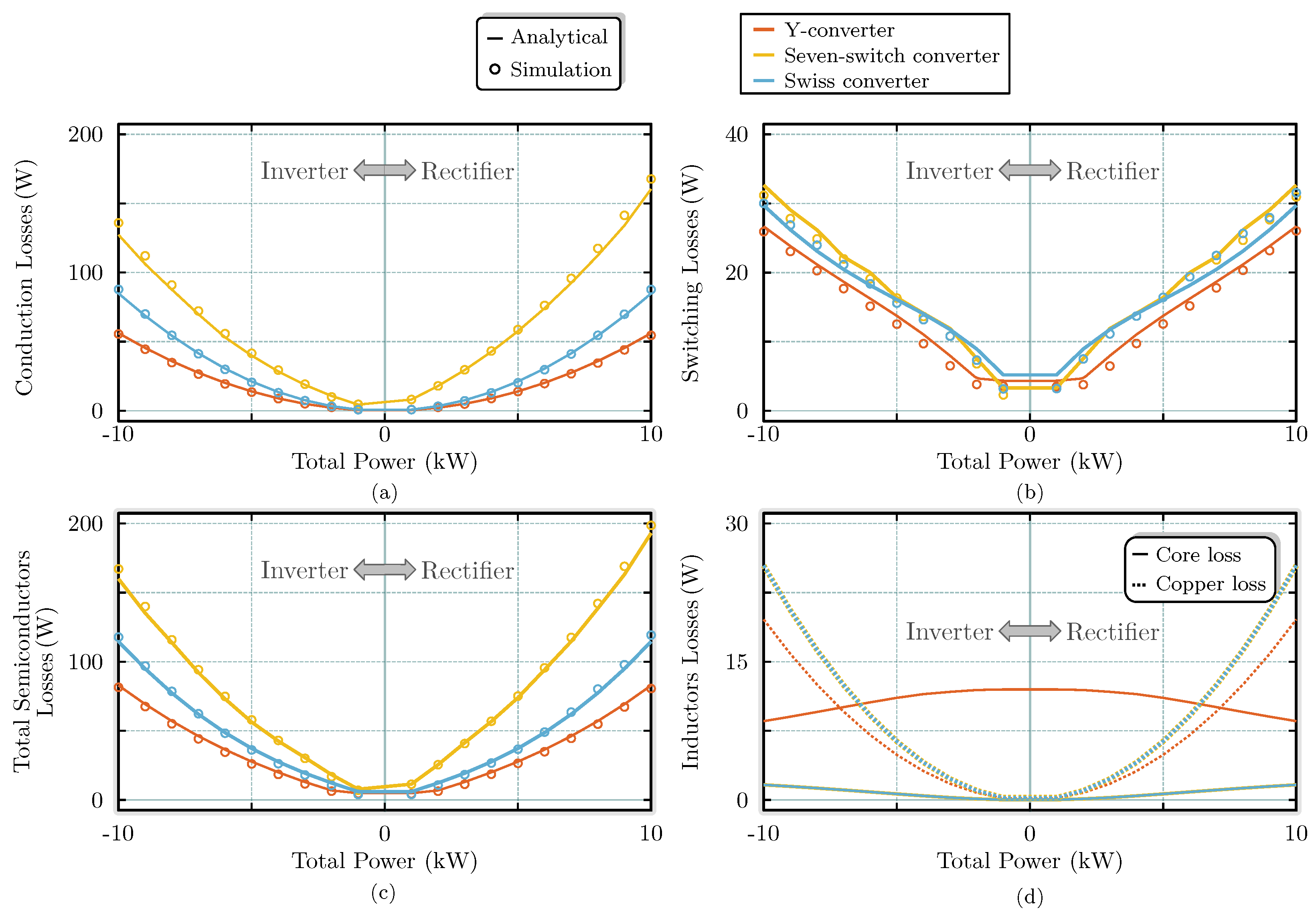

4.2. Semiconductors Losses

4.2.1. Conduction Losses

4.2.2. Switching Losses

4.3. Inductor Losses

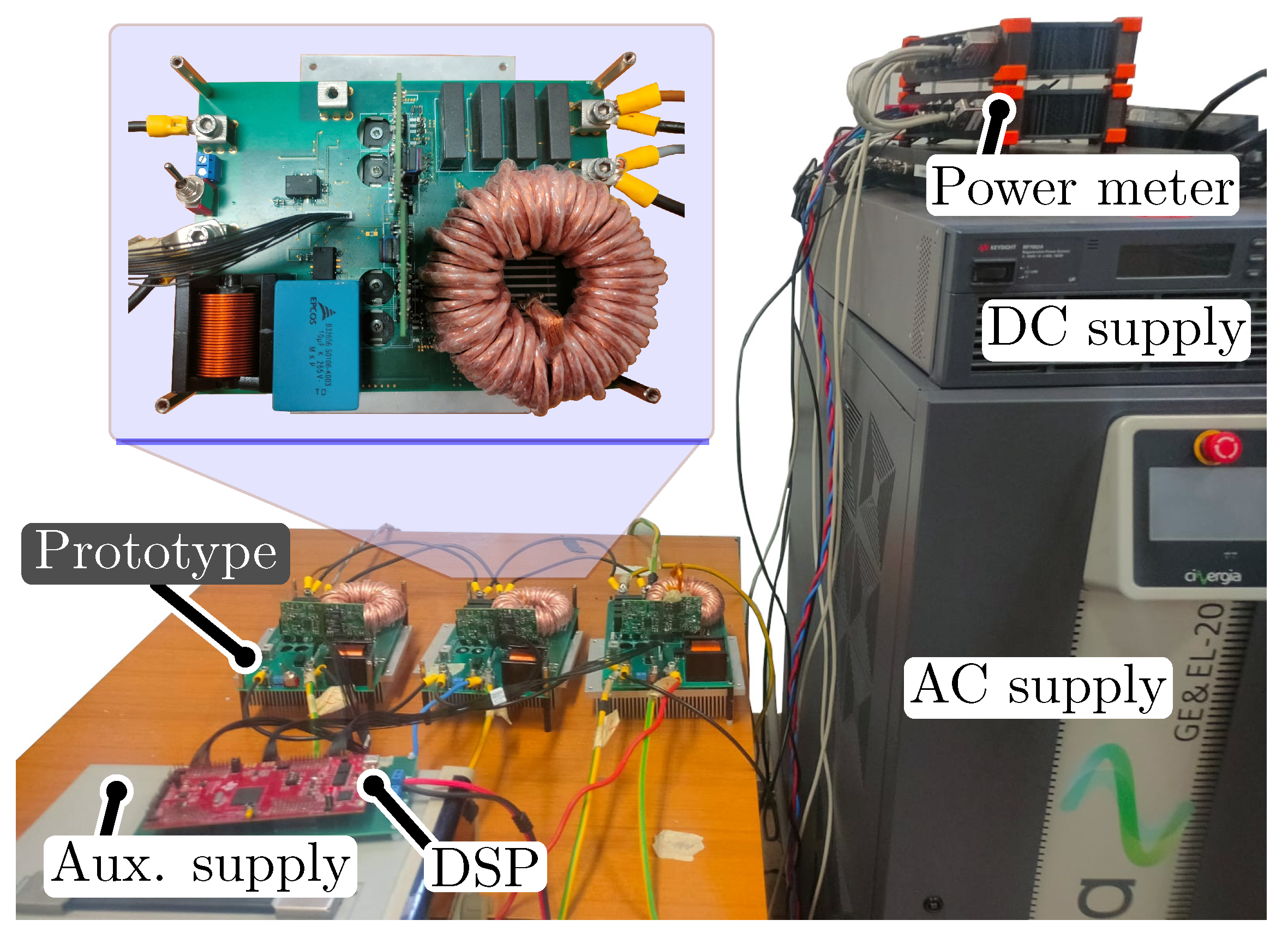

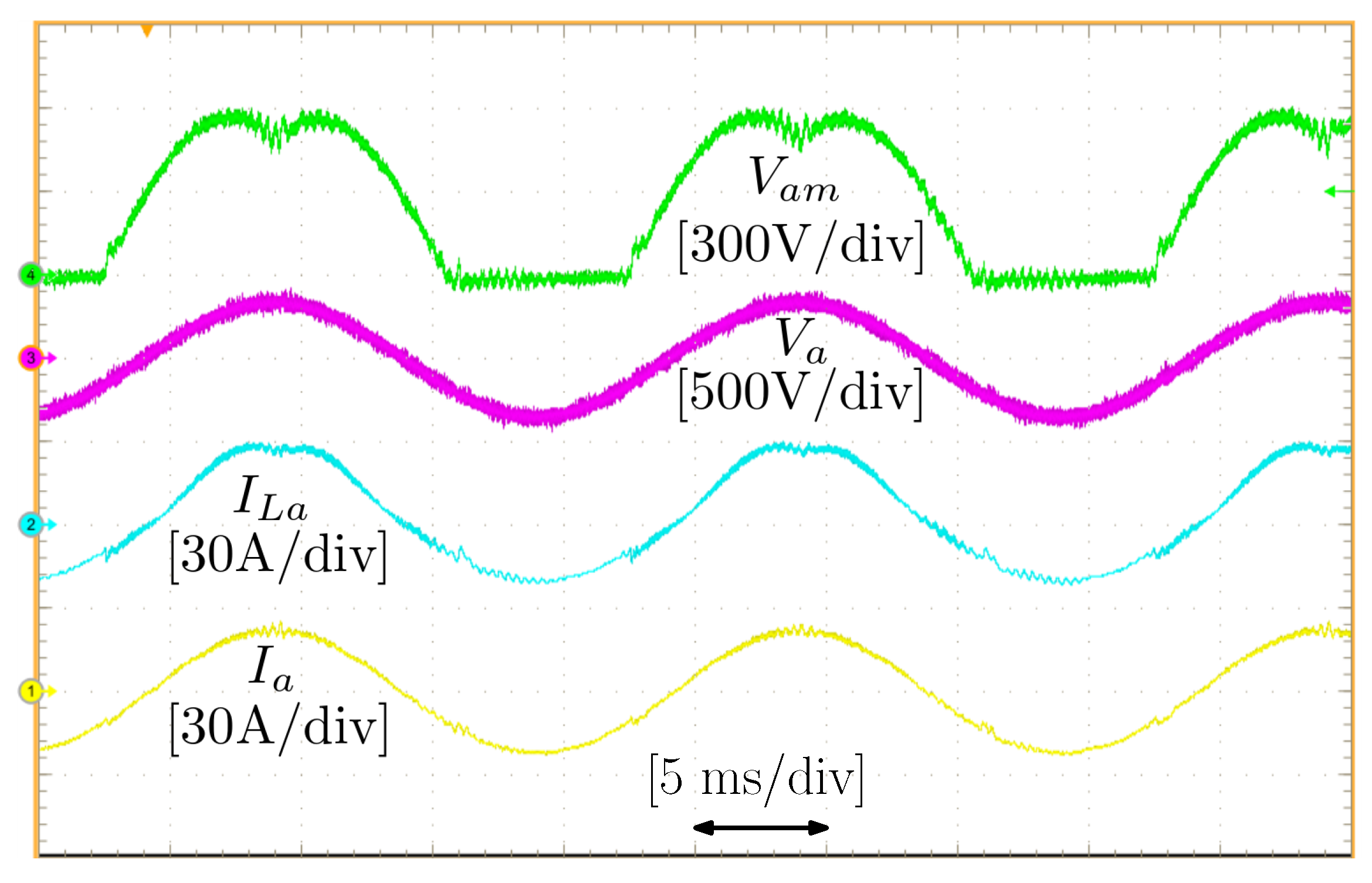

5. Experimental Results

5.1. Key Waveforms and AC Current THDs

5.2. Measured Efficiency and Power Loss Breakdown

6. Discussion and Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| PFC | power factor correction |

| SiC | silicon carbide |

| PWM | pulse width modulation |

| DPWM | discontinuous pulse width modulation |

| SVPWM | space vector pulse width modulation |

References

- Kulasekaran, P.S.; Dasarathan, S. Design and Analysis of Interleaved High-Gain Bi-Directional DC-DC Converter for Microgrid Application Integrated with Photovoltaic Systems. Energies 2023, 16, 5135. [Google Scholar] [CrossRef]

- Murshed, M.; Chamana, M.; Schmitt, K.E.K.; Bhatta, R.; Adeyanju, O.; Bayne, S. Design and Performance Analysis of a Grid-Connected Distributed Wind Turbine. Energies 2023, 16, 5778. [Google Scholar] [CrossRef]

- Yan, S.; Gu, Z.; Park, J.H.; Xie, X. Adaptive Memory-Event-Triggered Static Output Control of T–S Fuzzy Wind Turbine Systems. IEEE Trans. Fuzzy Syst. 2022, 30, 3894–3904. [Google Scholar] [CrossRef]

- Yan, S.; Gu, Z.; Park, J.H.; Xie, X. Sampled Memory-Event-Triggered Fuzzy Load Frequency Control for Wind Power Systems Subject to Outliers and Transmission Delays. IEEE Trans. Cybern. 2023, 53, 4043–4053. [Google Scholar] [CrossRef] [PubMed]

- Pires, V.F.; Pires, A.; Cordeiro, A. DC Microgrids: Benefits, Architectures, Perspectives and Challenges. Energies 2023, 16, 1217. [Google Scholar] [CrossRef]

- Ali, S.; Zheng, Z.; Aillerie, M.; Sawicki, J.P.; Péra, M.C.; Hissel, D. A Review of DC Microgrid Energy Management Systems Dedicated to Residential Applications. Energies 2021, 14, 4308. [Google Scholar] [CrossRef]

- Kumar, D.; Zare, F.; Ghosh, A. DC Microgrid Technology: System Architectures, AC Grid Interfaces, Grounding Schemes, Power Quality, Communication Networks, Applications, and Standardizations Aspects. IEEE Access 2017, 5, 12230–12256. [Google Scholar] [CrossRef]

- Prabhala, V.A.; Baddipadiga, B.P.; Fajri, P.; Ferdowsi, M. An Overview of Direct Current Distribution System Architectures and Benefits. Energies 2018, 11, 2463. [Google Scholar] [CrossRef]

- Dragičević, T.; Lu, X.; Vasquez, J.C.; Guerrero, J.M. DC Microgrids—Part II: A Review of Power Architectures, Applications, and Standardization Issues. IEEE Trans. Power Electron. 2016, 31, 3528–3549. [Google Scholar] [CrossRef]

- Elsayed, A.T.; Mohamed, A.A.; Mohammed, O.A. DC microgrids and distribution systems: An overview. Electr. Power Syst. Res. 2015, 119, 407–417. [Google Scholar] [CrossRef]

- Justo, J.J.; Mwasilu, F.; Lee, J.; Jung, J.W. AC-microgrids versus DC-microgrids with distributed energy resources: A review. Renew. Sustain. Energy Rev. 2013, 24, 387–405. [Google Scholar] [CrossRef]

- Kolar, J.W.; Friedli, T. The Essence of Three-Phase PFC Rectifier Systems—Part I. IEEE Trans. Power Electron. 2013, 28, 176–198. [Google Scholar] [CrossRef]

- Stupar, A.; Friedli, T.; Minibock, J.; Kolar, J.W. Towards a 99% Efficient Three-Phase Buck-Type PFC Rectifier for 400-V DC Distribution Systems. IEEE Trans. Power Electron. 2012, 27, 1732–1744. [Google Scholar] [CrossRef]

- Baumann, M.; Kolar, J. Comparative evaluation of modulation methods for a three-phase/switch buck power factor corrector concerning the input capacitor voltage ripple. In Proceedings of the 2001 IEEE 32nd Annual Power Electronics Specialists Conference (IEEE Cat. No.01CH37230), Vancouver, BC, Canada, 17–21 June 2001; Volume 3, pp. 1327–1332. [Google Scholar] [CrossRef]

- Lorenzani, E.; Immovilli, F.; Migliazza, G.; Frigieri, M.; Bianchini, C.; Davoli, M. CSI7: A Modified Three-Phase Current-Source Inverter for Modular Photovoltaic Applications. IEEE Trans. Ind. Electron. 2017, 64, 5449–5459. [Google Scholar] [CrossRef]

- Wang, W.; Gao, F.; Yang, Y.; Blaabjerg, F. Operation and Modulation of H7 Current-Source Inverter with Hybrid SiC and Si Semiconductor Switches. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 387–399. [Google Scholar] [CrossRef]

- Vancu, M.F.; Soeiro, T.; Mühlethaler, J.; Kolar, J.W.; Aggeler, D. Comparative evaluation of bidirectional buck-type PFC converter systems for interfacing residential DC distribution systems to the smart grid. In Proceedings of the IECON 2012—38th Annual Conference on IEEE Industrial Electronics Society, Montreal, QC, Canada, 25–28 October 2012; pp. 5153–5160. [Google Scholar] [CrossRef]

- Soeiro, T.B.; Heldwein, M.L. Bidirectional three-phase PFC concept based on an integrated inverting-link current source converter. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 15–19 September 2013; pp. 5137–5144. [Google Scholar] [CrossRef]

- Guo, B.; Wang, F.; Aeloiza, E. A novel three-phase current source rectifier with delta-type input connection to reduce the device conduction loss. IEEE Trans. Power Electron. 2016, 31, 1074–1084. [Google Scholar] [CrossRef]

- Soeiro, T.B.; Friedli, T.; Kolar, J.W. Design and Implementation of a Three-Phase Buck-Type Third Harmonic Current Injection PFC Rectifier SR. IEEE Trans. Power Electron. 2013, 28, 1608–1621. [Google Scholar] [CrossRef]

- Schrittwieser, L.; Leibl, M.; Haider, M.; Thöny, F.; Kolar, J.W.; Soeiro, T.B. 99.3% Efficient Three-Phase Buck-Type All-SiC SWISS Rectifier for DC Distribution Systems. IEEE Trans. Power Electron. 2019, 34, 126–140. [Google Scholar] [CrossRef]

- Schrittwieser, L.; Kolar, J.W.; Soeiro, T.B. Novel SWISS Rectifier Modulation Scheme Preventing Input Current Distortions at Sector Boundaries. IEEE Trans. Power Electron. 2017, 32, 5771–5785. [Google Scholar] [CrossRef]

- Chen, R.; Yao, Y.; Zhao, L.; Xu, M. Inhibiting mains current distortion for SWISS Rectifier—A three-phase buck-type harmonic current injection PFC converter. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 1850–1854. [Google Scholar] [CrossRef]

- Zhang, B.; Xie, S.; Li, Z.; Zhao, P.; Xu, J. An Optimized Single-Stage Isolated Swiss-Type AC/DC Converter Based on Single Full-Bridge with Midpoint-Clamper. IEEE Trans. Power Electron. 2021, 36, 11288–11297. [Google Scholar] [CrossRef]

- Soeiro, T.B.; Vancu, F.; Kolar, J.W. Hybrid Active Third-Harmonic Current Injection Mains Interface Concept for DC Distribution Systems. IEEE Trans. Power Electron. 2013, 28, 7–13. [Google Scholar] [CrossRef]

- Antivachis, M.; Bortis, D.; Schrittwieser, L.; Kolar, J.W. Three-phase buck-boost Y-inverter with wide DC input voltage range. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 1492–1499. [Google Scholar] [CrossRef]

- Farag, A.Y.; Younis, T.; Mattavelli, P.; Biadene, D. AC Grid-interface Bidirectional Buck-Type Converters for DC microgrids: A Comparative Study. In Proceedings of the IECON 2022—48th Annual Conference of the IEEE Industrial Electronics Society, Brussels, Belgium, 17–20 October 2022; pp. 1–6. [Google Scholar] [CrossRef]

- Antivachis, M.; Kleynhans, N.; Kolar, J.W. Three-Phase Sinusoidal Output Buck-Boost GaN Y-Inverter for Advanced Variable Speed AC Drives. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 10, 3459–3476. [Google Scholar] [CrossRef]

- Rothmund, D.; Bortis, D.; Kolar, J.W. Accurate Transient Calorimetric Measurement of Soft-Switching Losses of 10-kV SiC mosfets and Diodes. IEEE Trans. Power Electron. 2018, 33, 5240–5250. [Google Scholar] [CrossRef]

- Sochor, P.; Huerner, A.; Hell, M.; Elpelt, R. Understanding the Turn-off Behavior of SiC MOSFET Body Diodes in Fast Switching Applications. In PCIM Europe Digital Days 2021; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management; Mesago Messe Frankfurt GmbH: Stuttgart, Germany, 2021; pp. 1–8. [Google Scholar]

- Magnetics Inc. Magnetics Powder Cores Catalog. 2020. Available online: https://www.mag-inc.com/Media/Magnetics/File-Library/Product%20Literature/Powder%20Core%20Literature/Magnetics-Powder-Core-Catalog-2020.pdf?ext=.pdf (accessed on 12 August 2023).

| Parameter | Symbol | Value | ||

|---|---|---|---|---|

| Converter parameters 1 | Nominal power | P | 10 | |

| AC line voltage | Vac | 400 | ||

| Line frequency | f | 50 | ||

| Switching frequency | 62.5 | |||

| Output voltage | Vdc | 400 | ||

| SiC MOSFET | Part number | IMZ120R030M1H | ||

| Voltage | VDS | 1200 | ||

| Current | 56 | |||

| SiC Diode | Part number | C4D20120D | ||

| Voltage | VRRM | 1200 | ||

| Current | 66 | |||

| Input Filter | Inductor | 50 | ||

| Capacitor | 11.3 | |||

| Parameter | Symbol | Value | ||

|---|---|---|---|---|

| Inductor Parameters | Part number | KoolMu 0079908A7 | ||

| Magnetic path length | MPL | 19.6 | ||

| Core volume | 43.4 | |||

| Number of turns | N | 80 | Turns | |

| Inductor DC resistance | 20.3 | |||

| Fitting Parameters | Flux density B Equation (20) | a | 3.763 | |

| b | 1.712 /Oe | |||

| c | 5.155 /Oe2 | |||

| d | 9.190 Oe−1 | |||

| e | 4.909 Oe−2 | |||

| x | 1.812 | |||

| Core losses Equation (21) | 52.36 /(.3) | |||

| 1.988 | ||||

| 1.541 | ||||

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Farag, A.Y.; Younis, T.; Biadene, D.; Mattavelli, P. AC Grid–DC Microgrid Coupling with High-Performance Three-Phase Single-Stage Bidirectional Converters. Energies 2023, 16, 6106. https://doi.org/10.3390/en16176106

Farag AY, Younis T, Biadene D, Mattavelli P. AC Grid–DC Microgrid Coupling with High-Performance Three-Phase Single-Stage Bidirectional Converters. Energies. 2023; 16(17):6106. https://doi.org/10.3390/en16176106

Chicago/Turabian StyleFarag, Ahmed Y., Tarek Younis, Davide Biadene, and Paolo Mattavelli. 2023. "AC Grid–DC Microgrid Coupling with High-Performance Three-Phase Single-Stage Bidirectional Converters" Energies 16, no. 17: 6106. https://doi.org/10.3390/en16176106