Gate Driver Circuit with All-Magnetic Isolation for Cascode-Connected SiC JFETs in a Three-Level T-Type Bridge-Leg

Abstract

:1. Introduction

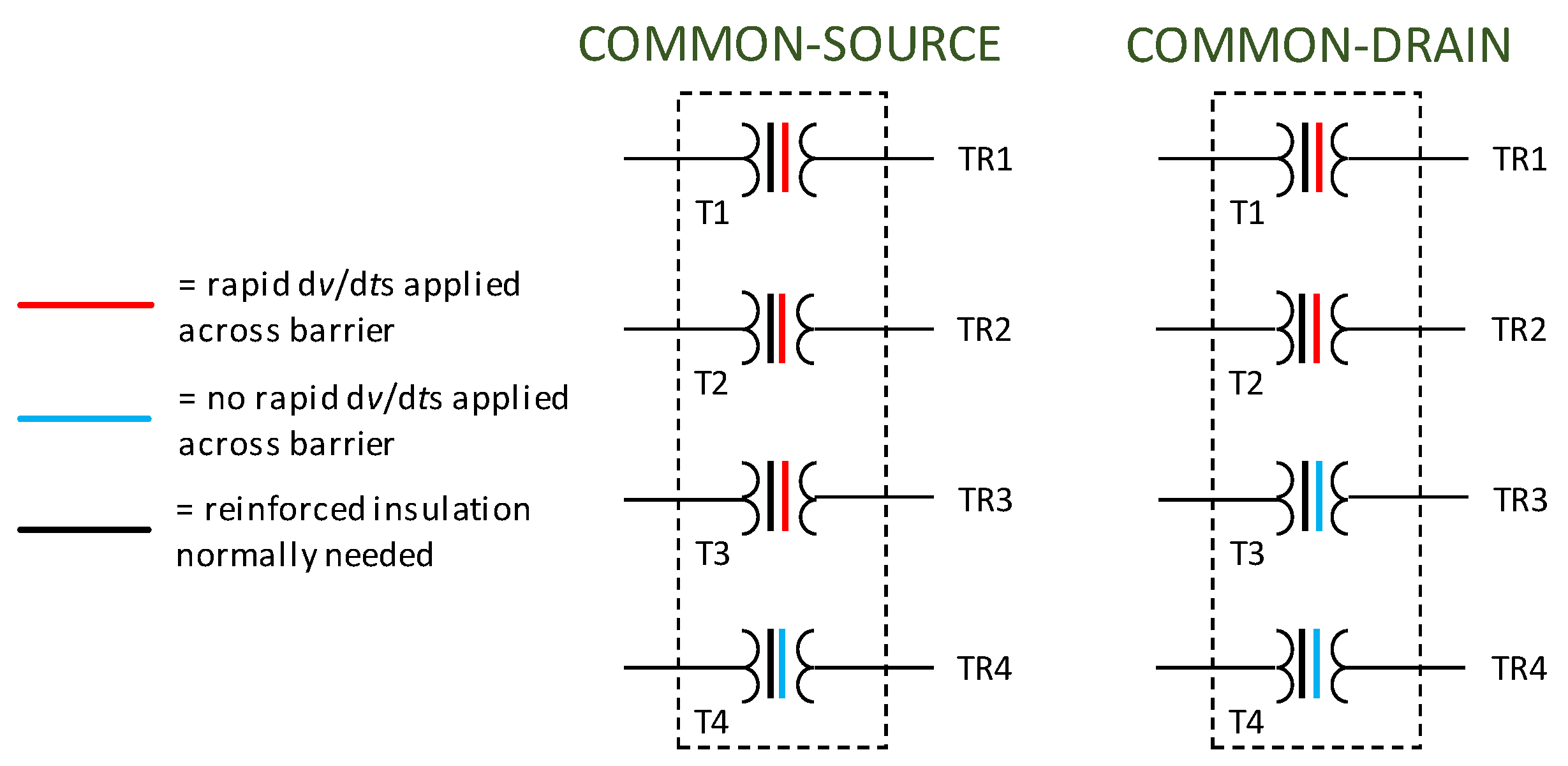

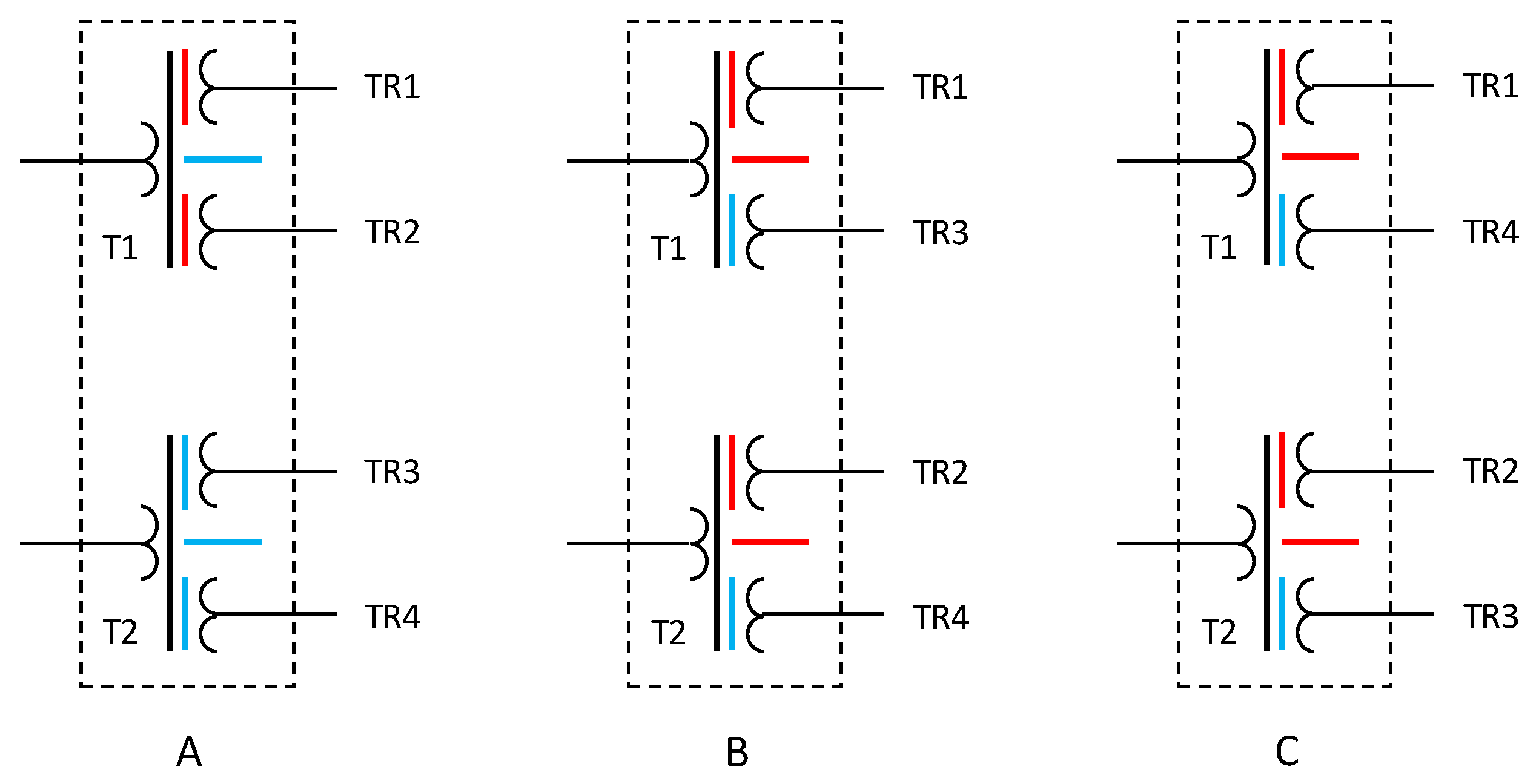

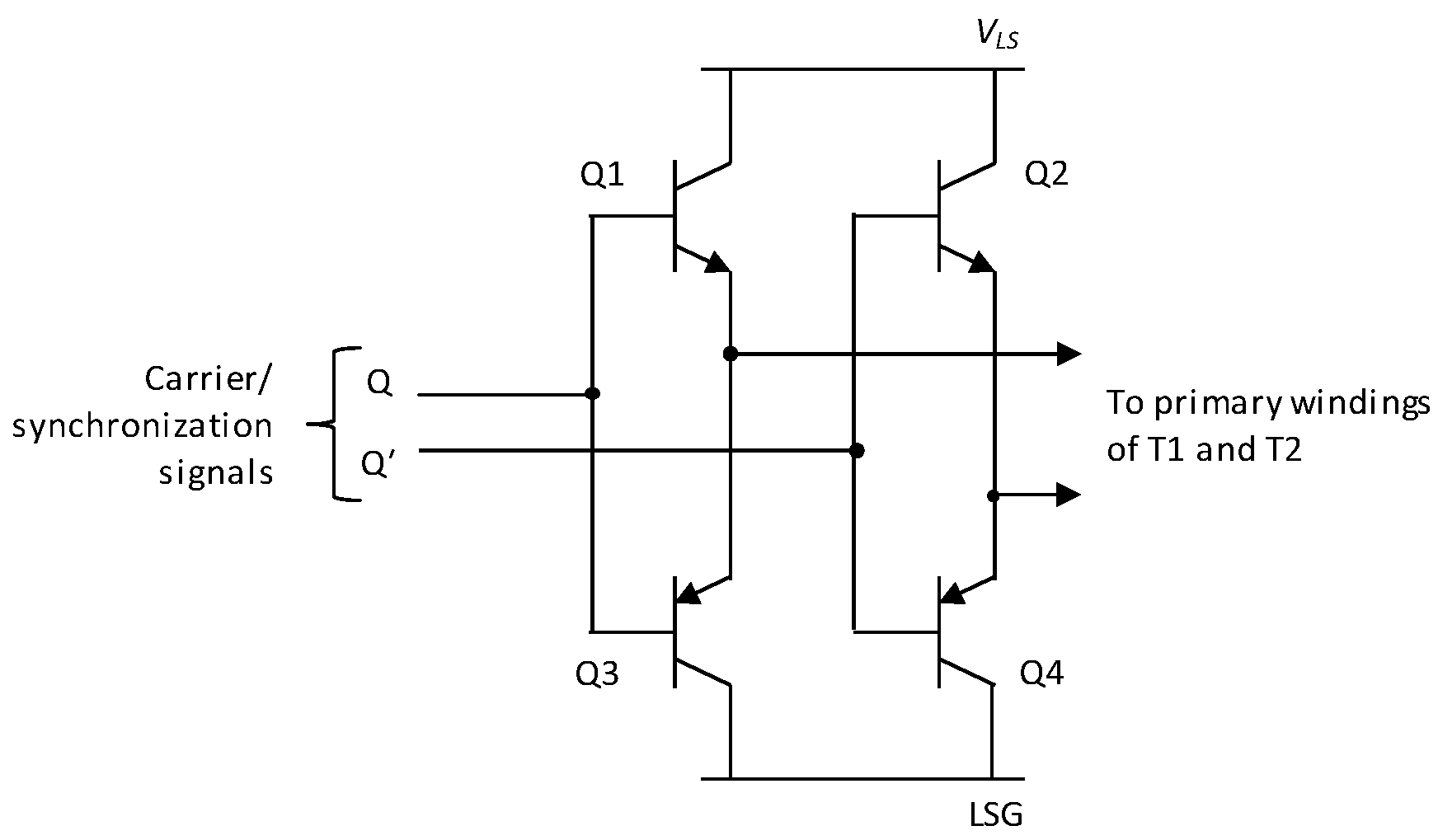

2. Power Transmission Options with Transformers

3. Signal Transmission Options with Transformers

3.1. Transformer Arrangements

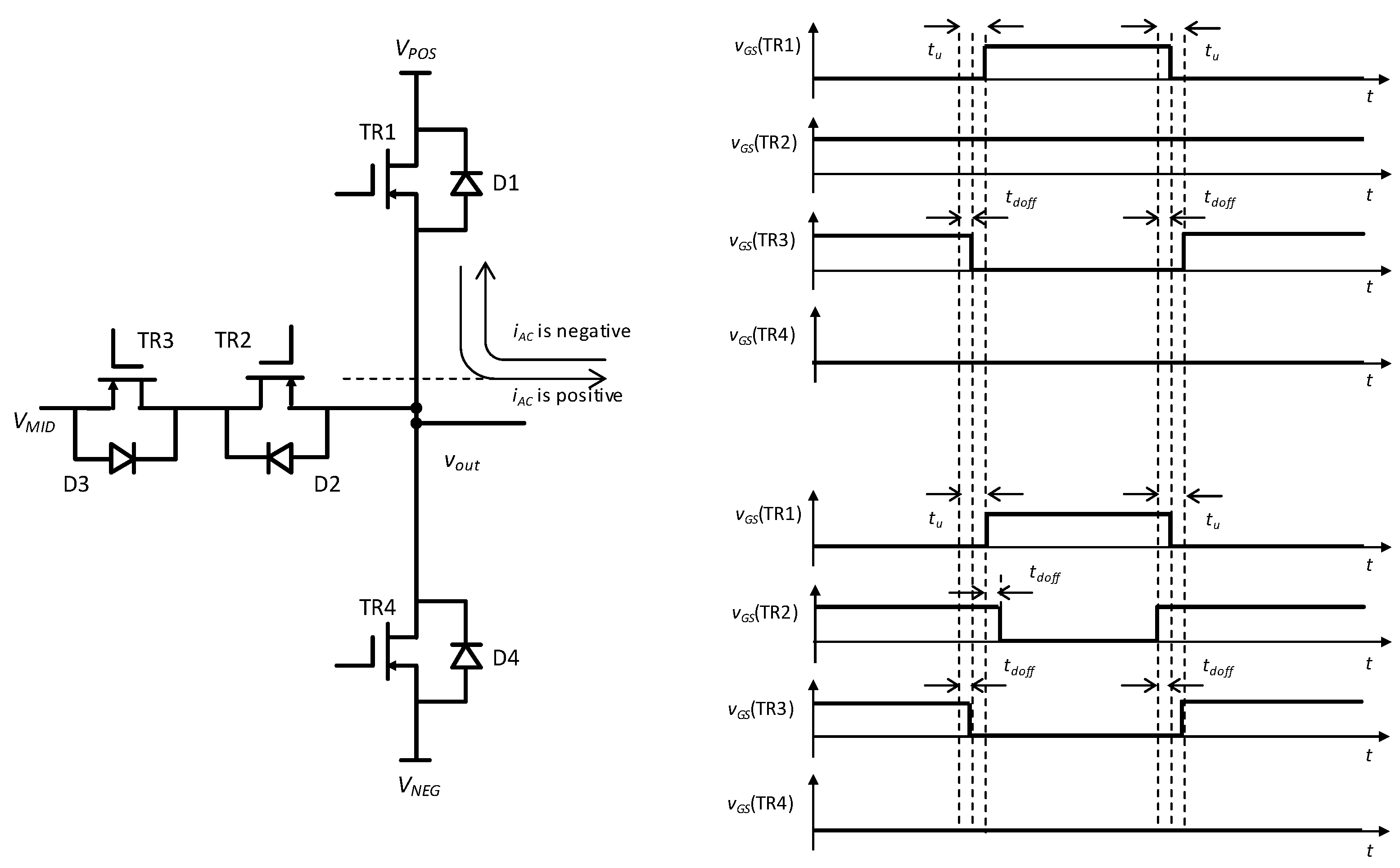

3.2. Signal Timing Issues

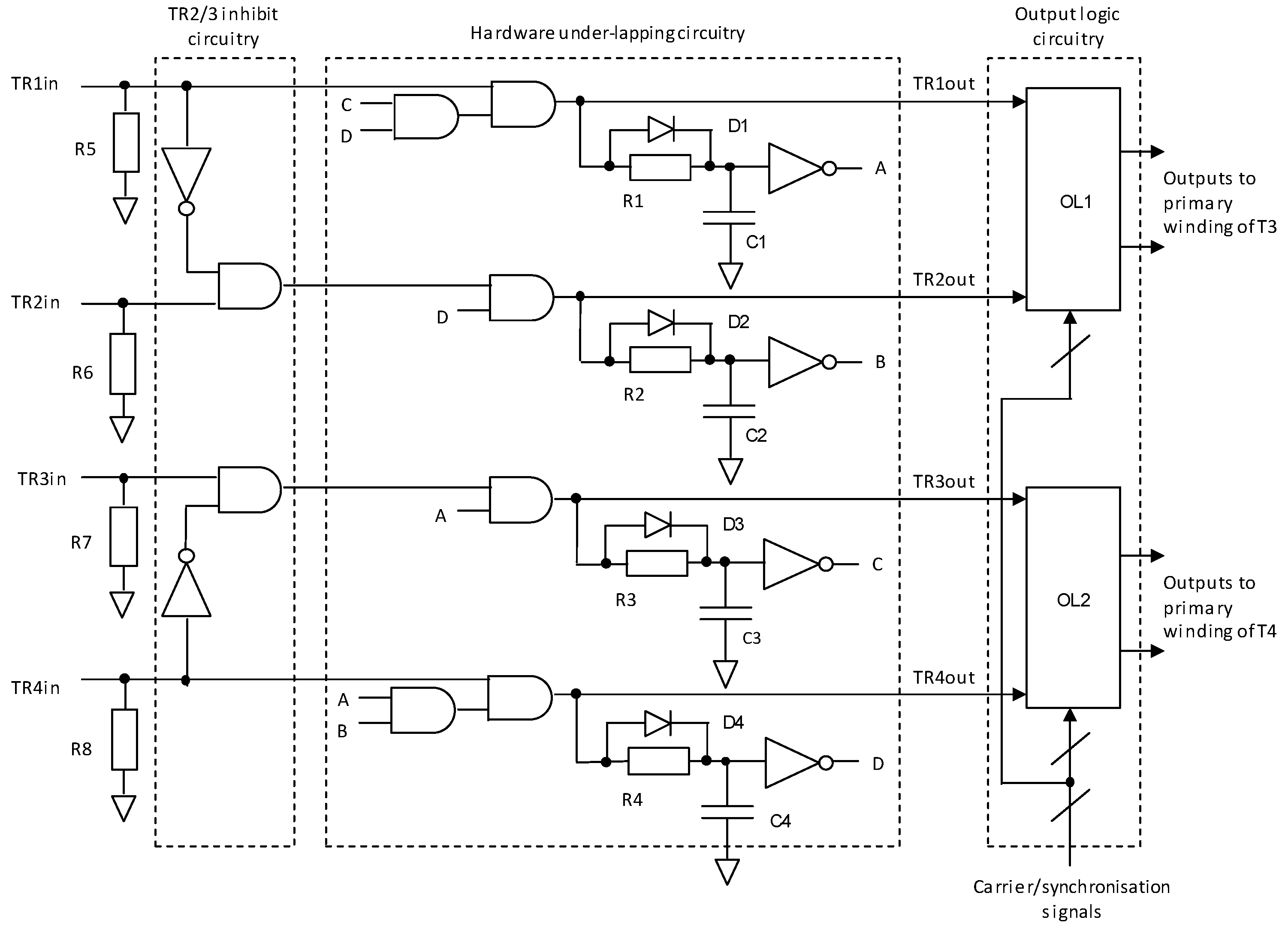

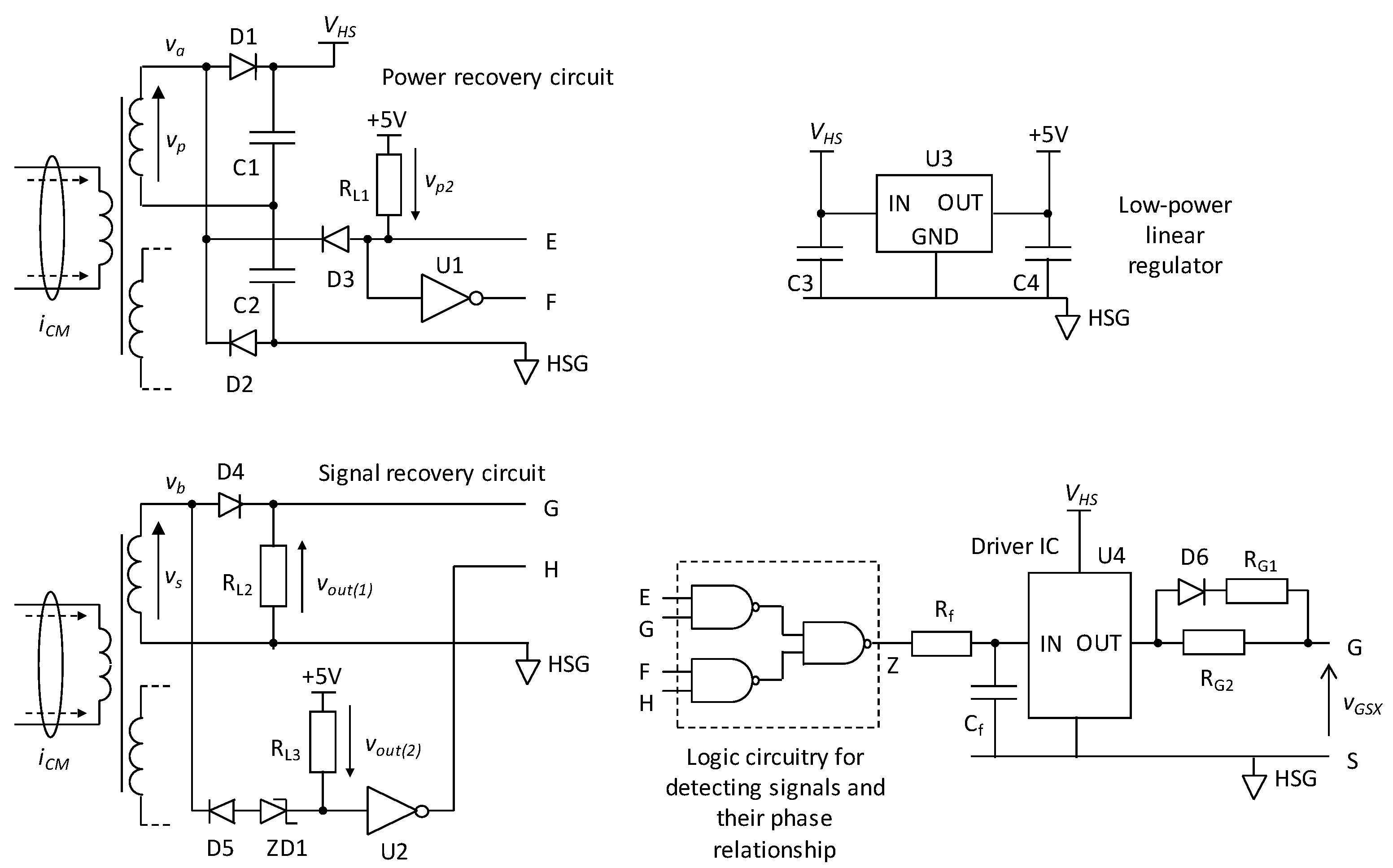

3.3. Proposed Low-Side Circuitry

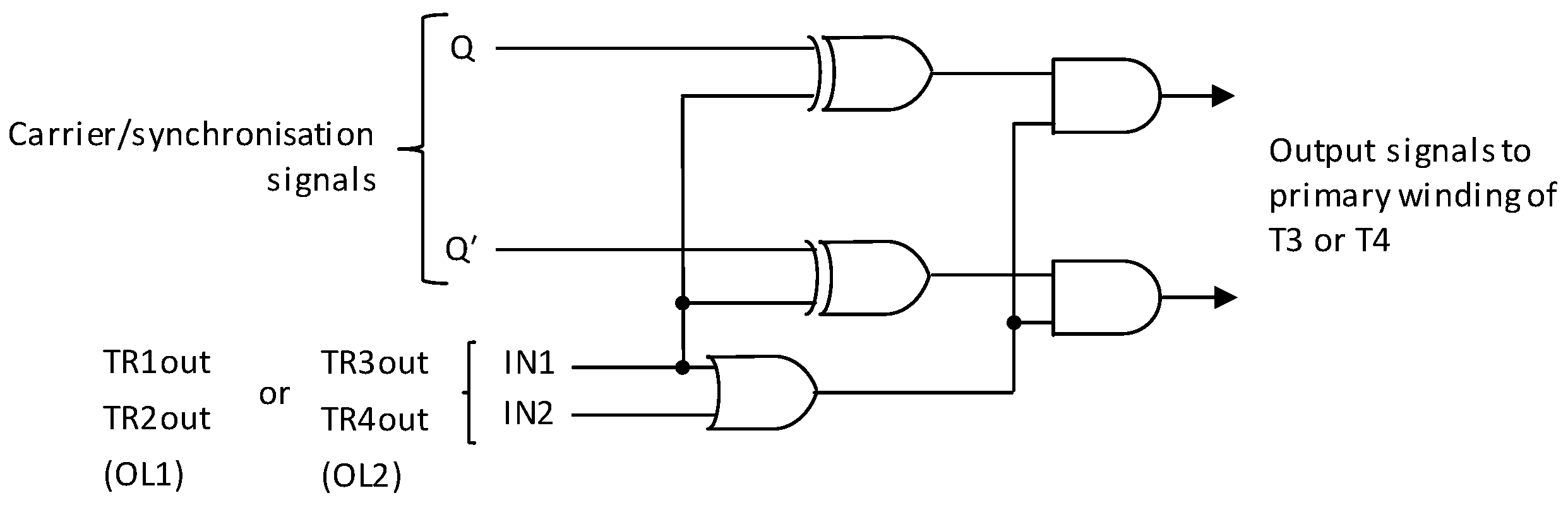

4. Overview of Proposed Circuit, and Details of High-Side Circuitry

5. Experimental Circuitry and Results

5.1. Hardware Configuration

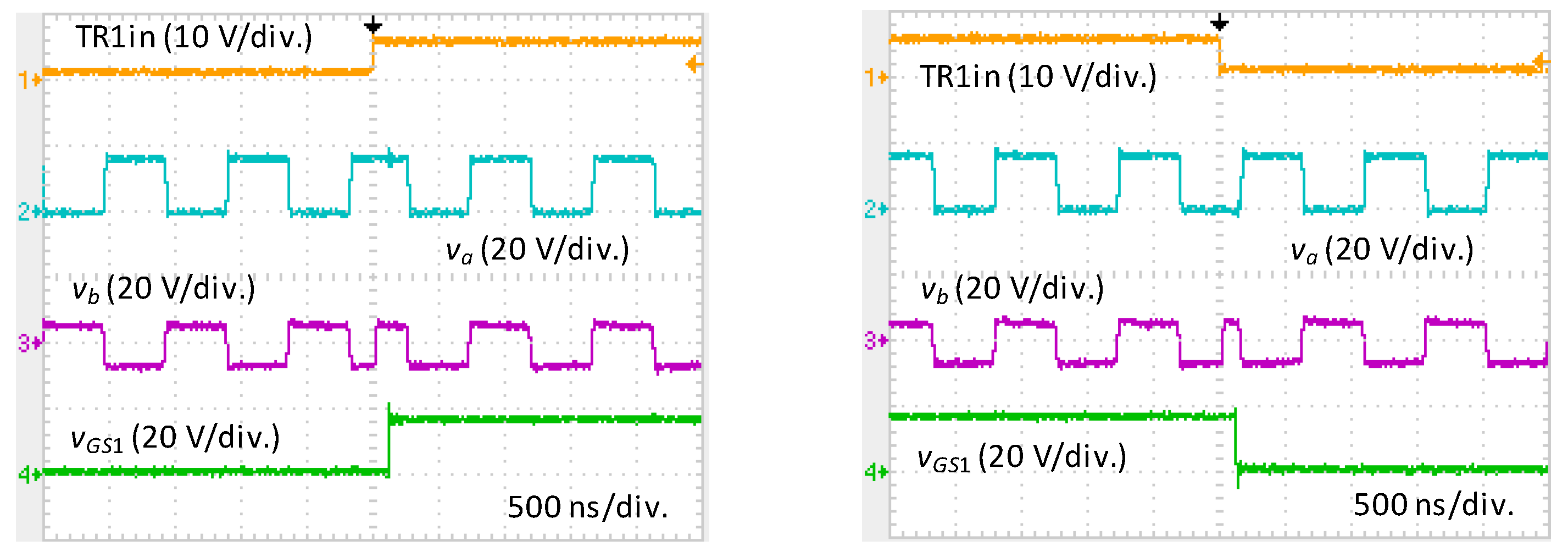

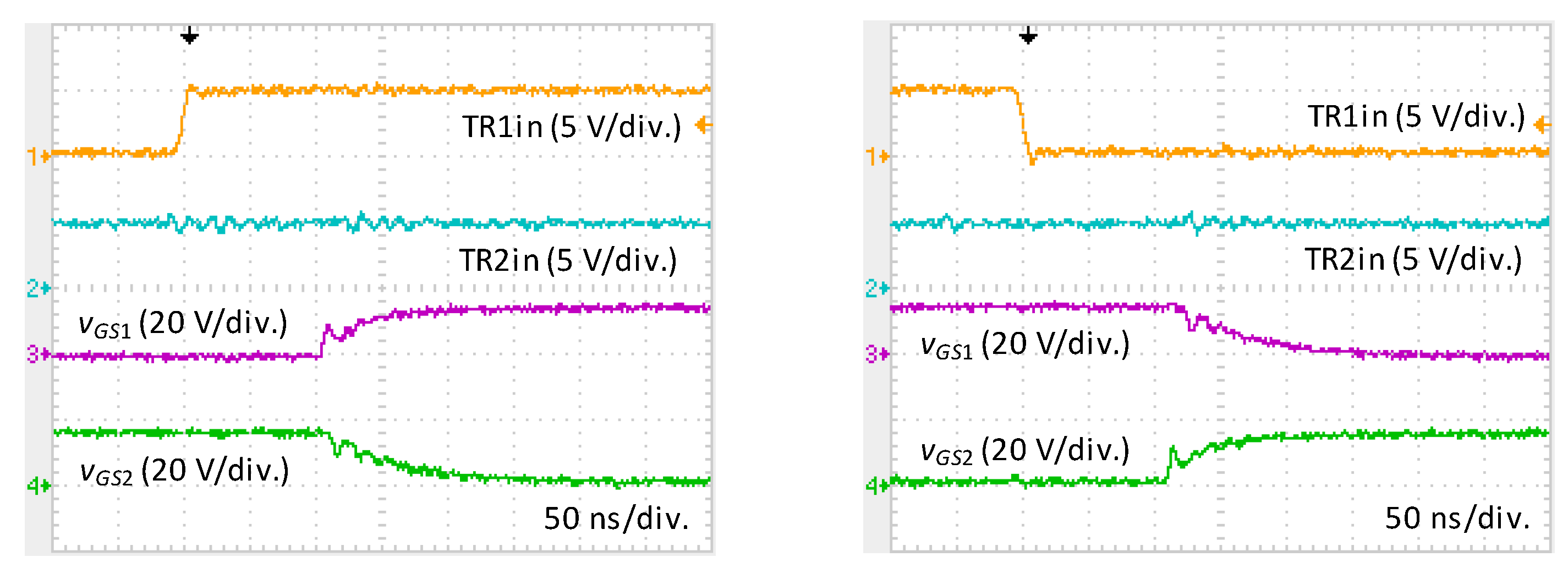

5.2. Propagation Delays and Power Consumption

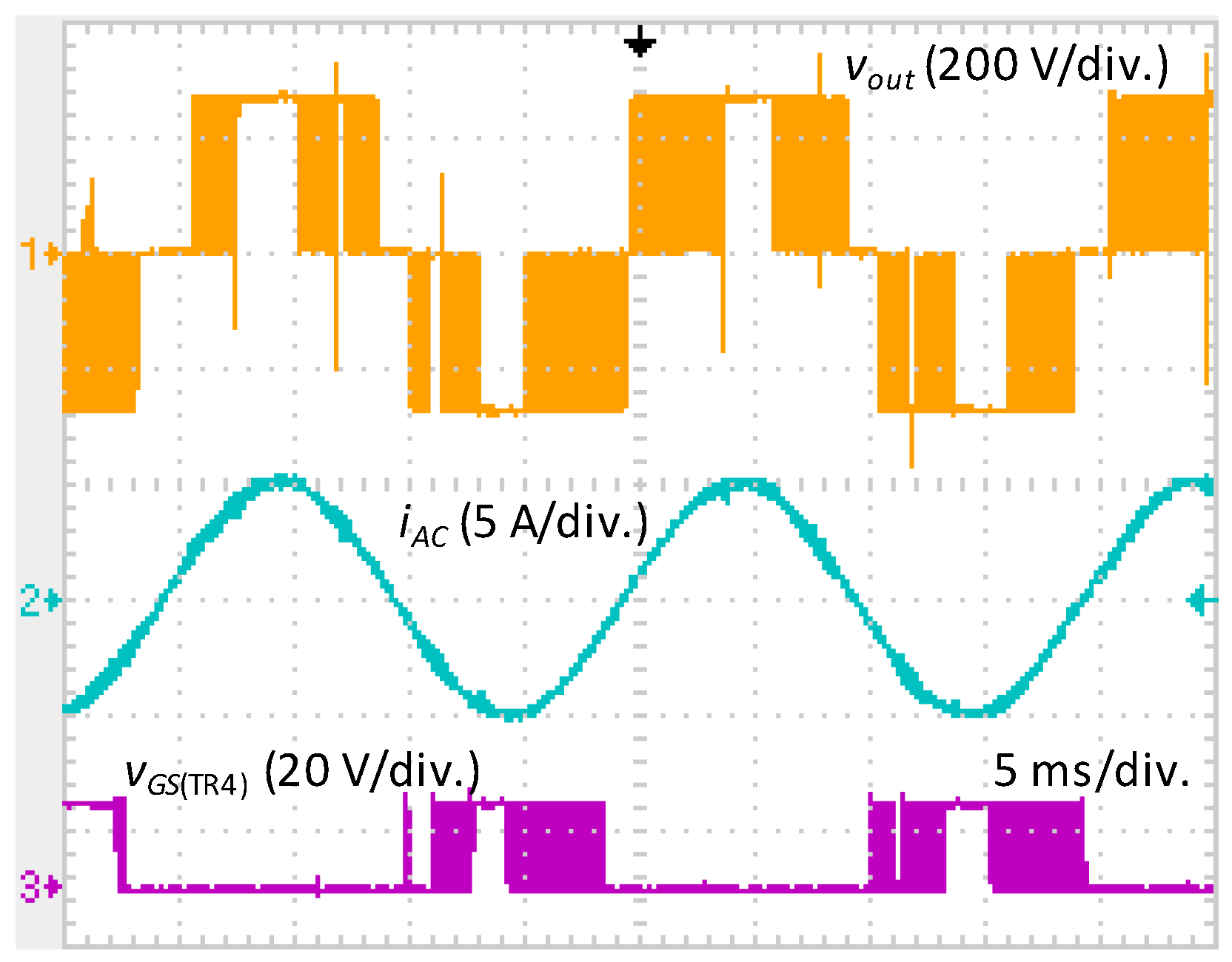

5.3. Operation with a T-Type Bridge-Leg

6. Discussion

6.1. Power Transmission Stage

6.2. Timing Issues

6.3. Signal Recovery Stages

6.4. Use of Magnetic Coupling for Signal Transmission

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Pérez, M.A.; Leon, J.I. Recent advances and industrial applications of multilevel converters. IEEE Trans. Ind. Electron. 2010, 8, 2553–2579. [Google Scholar] [CrossRef]

- 3L NPC & TNPC Topology, Application Note AN11001. Available online: www.semikron.com (accessed on 1 October 2022).

- Zhang, Z.; Anthon, A.; Andersen, M.A.E. Comprehensive loss evaluation of neutral-point-clamped (NPC) and T-type three-level inverters based on a circuit level decoupling modulation. In Proceedings of the 2014 International Power Electronics Applications Conference and Exposition, Shanghai, China, 5–8 November 2014; pp. 82–87. [Google Scholar]

- Anthon, A.; Zhang, Z.; Andersen, M.A.E.; Franke, T. Efficiency investigations of a 3 kW T-type inverter for switching frequencies up to 100 kHz. In Proceedings of the International Power Electronics Conference, Hiroshima, Japan, 18–21 May 2014; pp. 78–83. [Google Scholar]

- Schweizer, M.; Kolar, J.W. Design and implementation of a highly efficient three-level T-type converter. IEEE Trans. Power Electron. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Sun, B.; Burgos, R.; Boroyevich, D. Ultralow input–output capacitance PCB-embedded dual-output gate-drive power supply for 650 V GaN-based half-bridges. IEEE Trans. Power Electron. 2019, 34, 1382–1393. [Google Scholar] [CrossRef]

- Anurag, A.; Acharya, S.; Prabowo, Y.; Gohil, G.; Bhattacharya, S. Design considerations and development of an innovative gate driver for medium voltage power devices with high dv/dt. IEEE Trans. Power Electron. 2019, 34, 5256–5267. [Google Scholar] [CrossRef]

- Rothmund, D.; Bortis, D.; Kolar, J.W. Highly compact isolated gate driver with ultrafast overcurrent protection for 10 kV SiC MOSFETs. CPSS Trans. Power Electron. Appl. 2018, 3, 278–291. [Google Scholar] [CrossRef]

- She, X.; Datta, R.; Harfman Todorovic, M.; Mandrusiak, G.; Dai, J.; Frangieh, T.; Cioffi, P.; Rowden, B.; Mueller, F. High performance silicon carbide power block for industry applications. IEEE Trans. Ind. Appl. 2017, 53, 3738–3747. [Google Scholar] [CrossRef]

- Mao, S.; Popovic, J.; Ferreira, J.A. Switching characterization and low inter-winding capacitance gate driver power supply of 1200 V SiC MOSFET for the 300 kHz 10 kW inverter. In Proceedings of the 1st Workshop on Wide Bandgap Power Devices and Applications in Asia, Xi’an, China, 16–18 May 2018; pp. 270–275. [Google Scholar]

- Hui, S.Y.; Tang, S.C.; Chung, H.S.-H. Optimal operation of coreless PCB transformer-isolated gate drive circuits with wide switching frequency range. IEEE Trans. Power Electron. 1999, 14, 506–514. [Google Scholar] [CrossRef]

- Gui, Z.; Li, H.; Cheetham, P. A very-high-frequency isolated gate driver power supply using solid dielectrics for medium voltage MOSFETs. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition, Houston, TX, USA, 20 March 2022; pp. 1394–1399. [Google Scholar]

- Gottschlich, J.; Schäfer, M.; Neubert, M.; De Doncker, R.W. A galvanically isolated gate driver with low coupling capacitance for medium voltage SiC MOSFETs. In Proceedings of the 18th European Conference on Power Electronics Applications, Karlsruhe, Germany, 5–9 September 2016. [Google Scholar]

- Hu, J.; Wang, J.; Burgos, R.; Wen, B.; Boroyevich, D. High-density current-transformer based gate-drive power supply with reinforced isolation for 10 kV SiC MOSFET modules. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 2217–2226. [Google Scholar] [CrossRef]

- Gill, L.; Ikari, T. CM filter analysis and mitigation of common mode current in SiC MOSFET gate driver power supply. In Proceedings of the 2018 IEEE International Conference on Electrical Systems for Aircraft, Railway, Ship Propulsion and Road Vehicles & International Transportation Electrification Conference, Nottingham, UK, 7–9 November 2018. [Google Scholar]

- Hazra, S.; Madhusoodhanan, S.; Moghaddam, G.K.; Hatua, K.; Bhattacharya, S. Design considerations and performance evaluation of 1200-V 100-A SiC MOSFET-based two-level voltage source converter. IEEE Trans. Ind. Appl. 2016, 52, 4257–4268. [Google Scholar] [CrossRef]

- Nguyen, V.-S.; Kerachev, L.; Lefranc, P.; Crebier, J.-C. Architecture characterization and analysis of an innovative gate driver and power supplies architecture for HF power devices with high dv/dt. IEEE Trans. Power Electron. 2017, 32, 6079–6090. [Google Scholar] [CrossRef]

- Alves, L.F.S.; Lefranc, P.; Jeannin, P.-O.; Sarrazin, B. A new gate drive power supply configuration for common mode conducted EMI reduction in phase-shifted full-bridge converter. IEEE Trans. Power Electron. 2021, 36, 4081–4090. [Google Scholar] [CrossRef]

- Zhang, X.; Li, H.; Brothers, J.A.; Fu, L.; Perales, M.; Wu, J.; Wang, J. A gate drive with power over fiber-based isolated power supply and comprehensive protection functions for 15-kV SiC MOSFET. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 946–955. [Google Scholar] [CrossRef]

- Pan, J.; Qi, F.; Cai, H.; Xu, L. Efficiency and electromagnetic interference analysis of wireless power transfer for high voltage gate driver application. In Proceedings of the IEEE 9th Energy Conversion Congress and Exposition, Milwaukee, WI, USA, 18–22 September 2016. [Google Scholar]

- Falck, J.S.; Felgemacher, C.; Rojko, A.; Liserre, M.; Zacharias, P. Reliability of power electronics systems: An industry perspective. IEEE Ind. Electron. Mag. 2018, 12, 24–35. [Google Scholar] [CrossRef] [Green Version]

- Waffler, S.; Round, S.D.; Kolar, J.W. High temperature (>200°C) isolated gate drive topologies for silicon carbide (SiC) JFET. In Proceedings of the IEEE 34th Annual Industrial Electronics Conference, Orlando, FL, USA, 10–13 November 2008; pp. 2867–2872. [Google Scholar]

- Turnbull, F.G. A carrier frequency gating circuit for static inverters, converters, and cycloconverters. IEEE Trans. Magn. 1966, 2, 14–17. [Google Scholar] [CrossRef]

- McNeill, N.; Holliday, D.; Mellor, P.H. Alleviating common-mode interference effects in phase-switched power device gate driver circuit. IET Electron. Lett. 2008, 44, 880–881. [Google Scholar] [CrossRef]

- Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J. Active gate driver for crosstalk suppression of SiC devices in a phase-leg configuration. IEEE Trans. Power Electron. 2014, 29, 1986–1997. [Google Scholar] [CrossRef]

- Khanna, R.; Amrhein, A.; Stanchina, W.; Reed, G.; Mao, Z.-H. An analytical model for evaluating the influence of device parasitics on Cdv/dt induced false turn-on in SiC MOSFETs. In Proceedings of the IEEE 28th Annual Applied Power Electronics Conference and Exposition, Long Beach, CA, USA, 17–21 March 2013; pp. 518–525. [Google Scholar]

- McNeill, N.; Jin, B.; Yuan, X.; Laird, I. Evaluation of the off-state base-emitter voltage requirement of the SiC BJT with a regenerative proportional base driver circuit and their application in an inverter. IEEE Trans. Ind. Electron. 2020, 67, 7179–7189. [Google Scholar] [CrossRef] [Green Version]

- Ortiz-Gonzalez, J.; Wu, R.; Jahdi, S.; Alatise, O. Performance and reliability review of 650 V and 900 V silicon and SiC devices: MOSFETs, cascode JFETs and IGBTs. IEEE Trans. Ind. Electron. 2020, 67, 7385–7395. [Google Scholar]

- Wu, R.; Ortiz-Gonzalez, J.; Davletzhanova, Z.; Mawby, P.A.; Alatise, O. The potential of SiC cascode JFETs in electric vehicle traction inverters. IEEE Trans. Transp. Electrif. 2019, 5, 1349–1359. [Google Scholar] [CrossRef] [Green Version]

- Josifović, I.; Popović-Gerber, J.; Ferreira, J.A. Improving SiC JFET switching behavior under influence of circuit parasitics. IEEE Trans. Power Electron. 2012, 27, 3843–3854. [Google Scholar] [CrossRef]

- Pou, J.; Zaragoza, J.; Rodriguez, P.; Ceballos, S.; Sala, V.M.; Burgos, R.P.; Boroyevich, D. Fast-processing modulation strategy for the neutral-point-clamped converter with total elimination of low-frequency voltage oscillations in the neutral point. IEEE Trans. Ind. Electron. 2007, 54, 2288–2294. [Google Scholar] [CrossRef]

| Symbol or Abbreviation | Description |

|---|---|

| Ae | Effective area of magnetic core (m2) |

| AL | Inductance factor of magnetic core (H/turn2) |

| Bpk | Peak magnetic flux density (T) |

| CD | Common-drain |

| CM | Common-mode |

| CS | Common-source |

| fc | Carrier frequency (Hz) |

| Im(pk) | Peak magnetising current drawn by transformer (A) |

| N1pwr | Number of turns on primary winding of power transformer |

| N1sig | Number of turns on primary winding of signal transformer |

| N2pwr | Number of turns on each secondary winding of power transformer |

| N2sig | Number of turns on each secondary winding of signal transformer |

| VBE | Base-emitter voltage drop of BJT when conducting (V) |

| Vf | Forward voltage drop of diode when conducting (V) |

| vGS | Gate-source voltage applied to MOS-gated device (V) |

| VGS(th) | Threshold gate-source voltage of MOS-gated device (V) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

McNeill, N.; Vozikis, D.; Peña-Alzola, R.; Wang, S.; Pollock, R.; Holliday, D.; Williams, B.W. Gate Driver Circuit with All-Magnetic Isolation for Cascode-Connected SiC JFETs in a Three-Level T-Type Bridge-Leg. Energies 2023, 16, 1226. https://doi.org/10.3390/en16031226

McNeill N, Vozikis D, Peña-Alzola R, Wang S, Pollock R, Holliday D, Williams BW. Gate Driver Circuit with All-Magnetic Isolation for Cascode-Connected SiC JFETs in a Three-Level T-Type Bridge-Leg. Energies. 2023; 16(3):1226. https://doi.org/10.3390/en16031226

Chicago/Turabian StyleMcNeill, Neville, Dimitrios Vozikis, Rafael Peña-Alzola, Shuren Wang, Richard Pollock, Derrick Holliday, and Barry W. Williams. 2023. "Gate Driver Circuit with All-Magnetic Isolation for Cascode-Connected SiC JFETs in a Three-Level T-Type Bridge-Leg" Energies 16, no. 3: 1226. https://doi.org/10.3390/en16031226