Designing Reconfigurable Cyber-Physical Systems Using Unified Modeling Language

Abstract

:1. Introduction

- a novel UML-based design method for the reconfigurable CPSs is proposed;

- the presented approach is oriented toward hardware implementation of the CPS control part in reconfigurable FPGA devices;

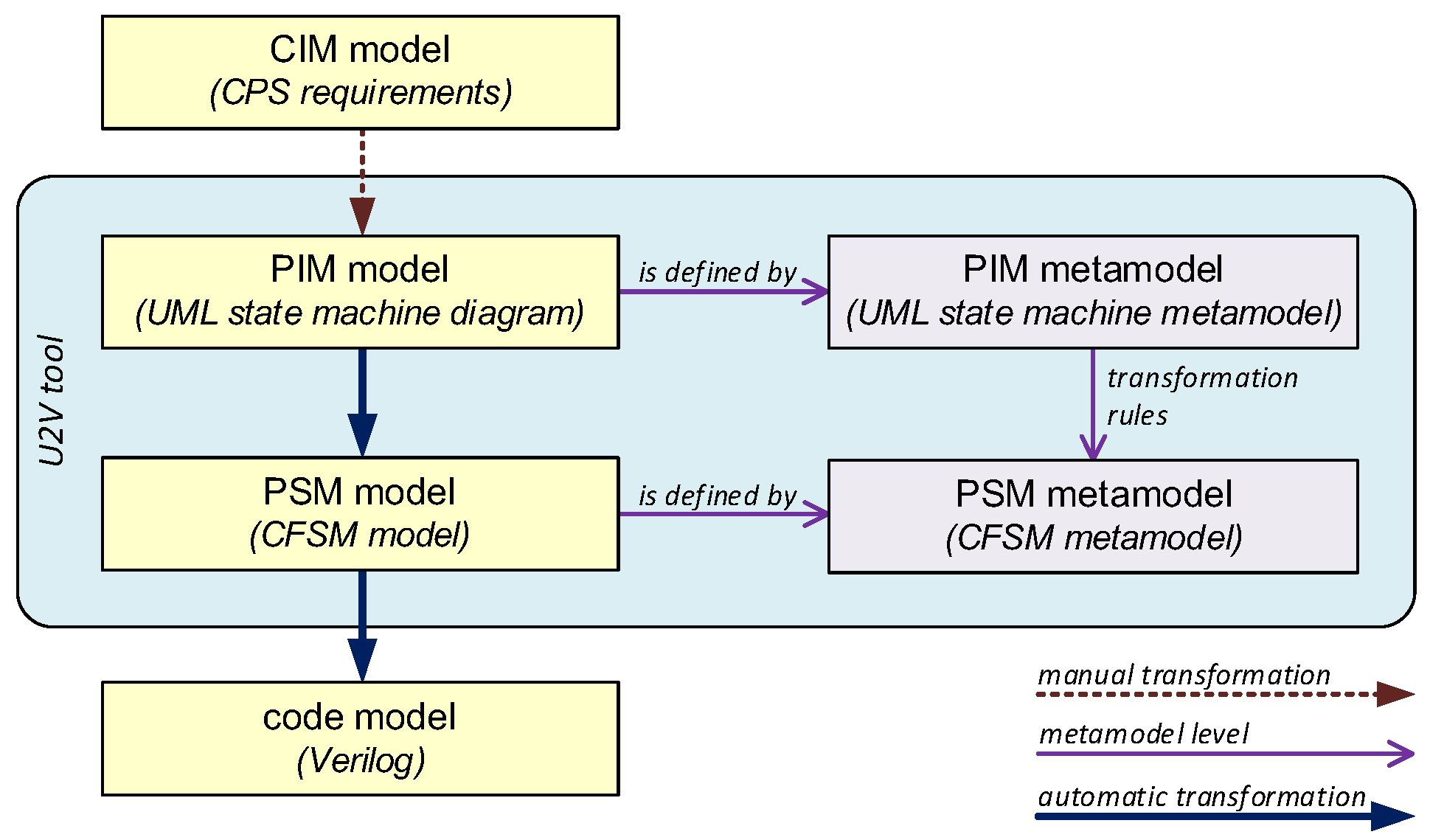

- the proposed CPS design framework utilizes MDD techniques (used to models transformation from a high-level graphical model into a code model) combined with the use of CFSM as a temporary model;

- MDD approach with the use of MDA enables automatic model generation from UML state machine diagram through CFSM model into modular and synthesizable Verilog specification;

- CFSM model applied idle states which are perfect to obtain a safe model, that is ready for dynamic partial reconfiguration (exchanging part of the control algorithm implemented in FPGA without switching the device off);

- a practical case-study example (reconfigurable smart home system) illustrating the successive stages of the proposed method is presented.

2. Related Works

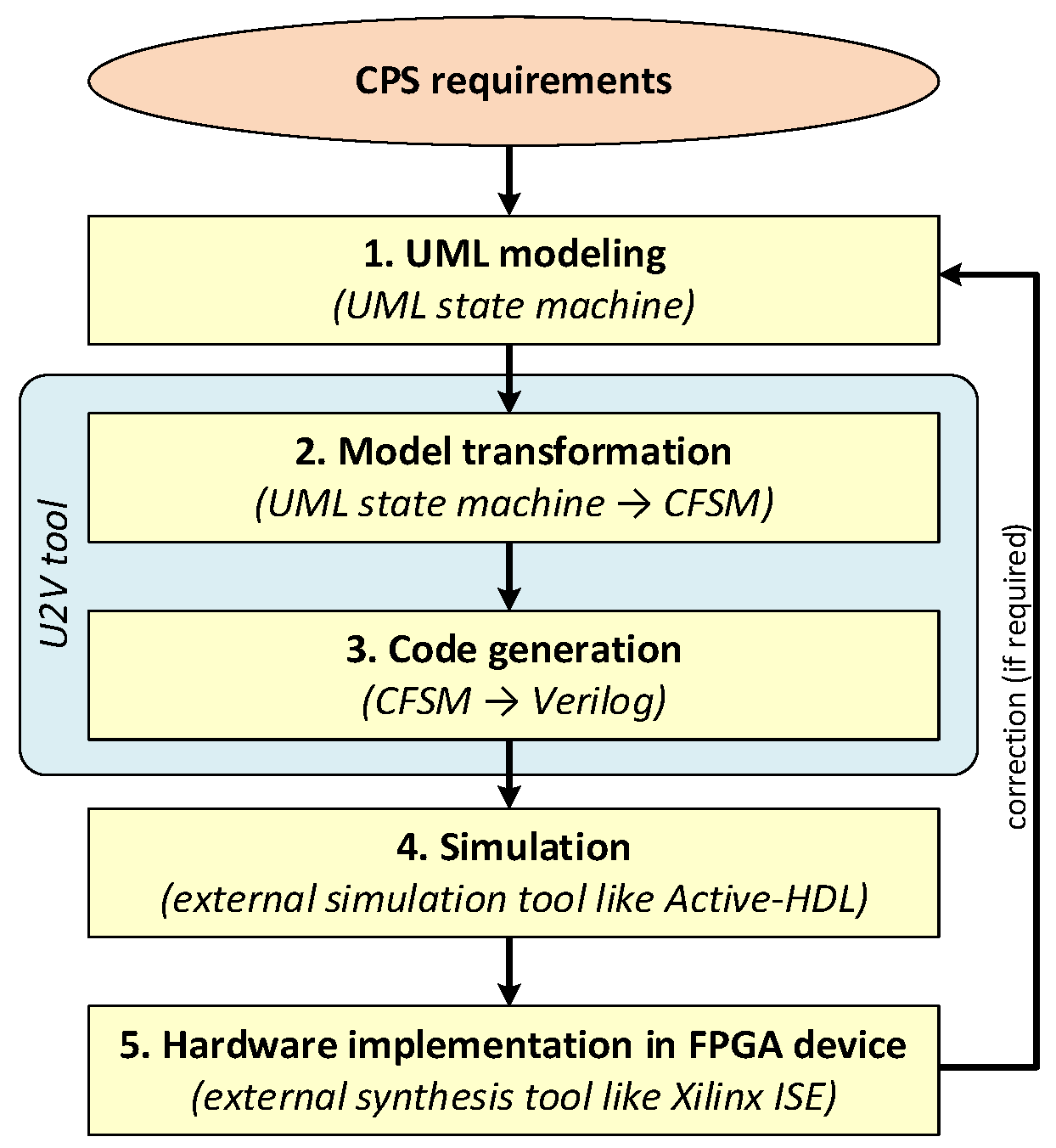

3. The Proposed Method

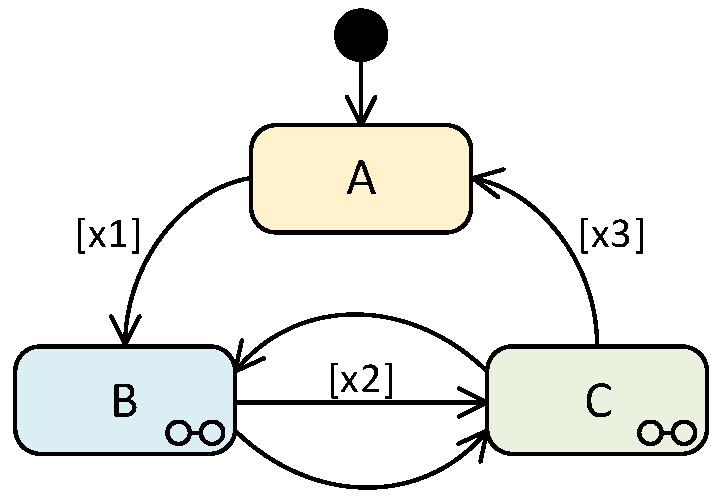

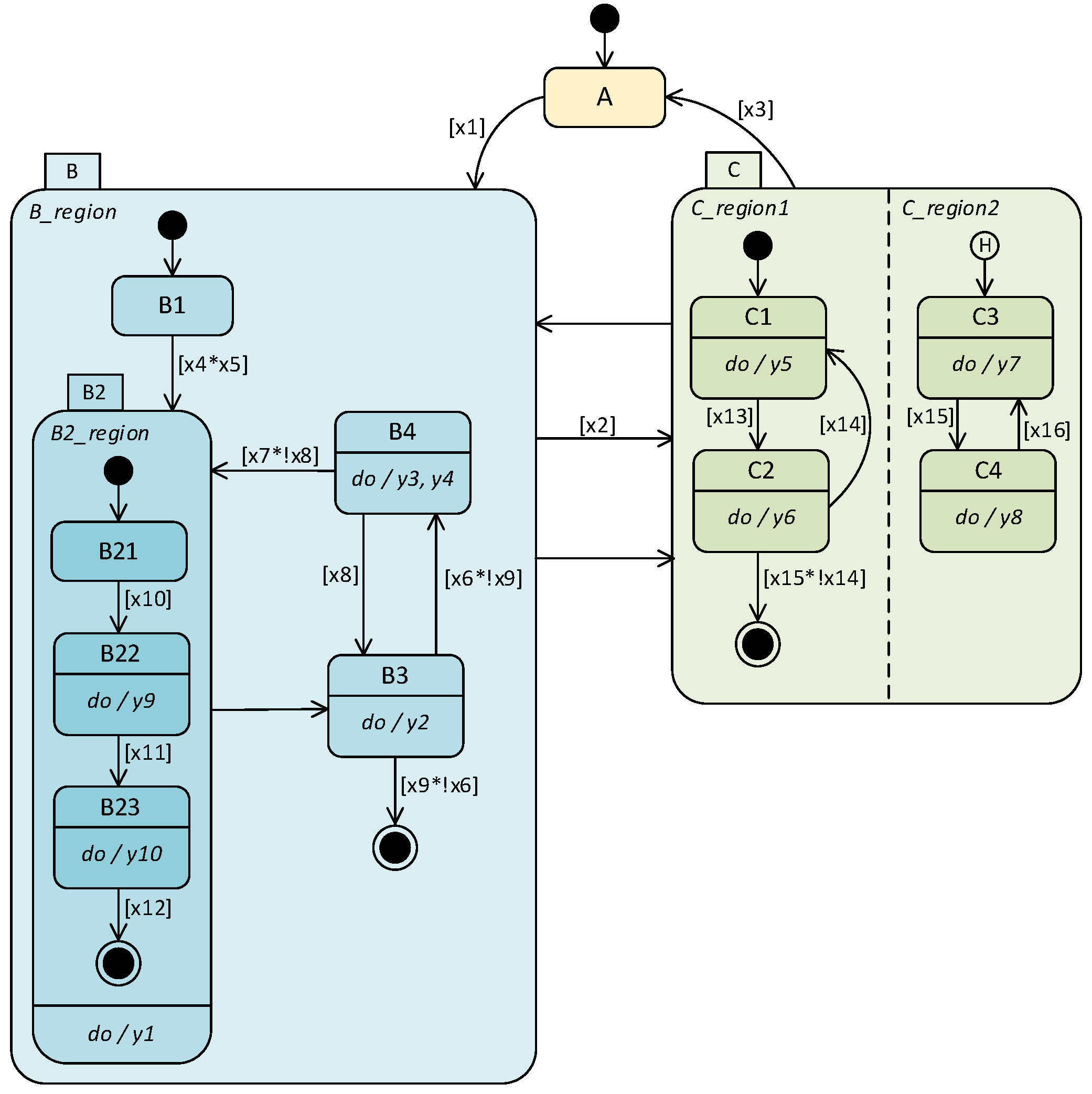

3.1. UML Modeling

3.2. Model Transformation

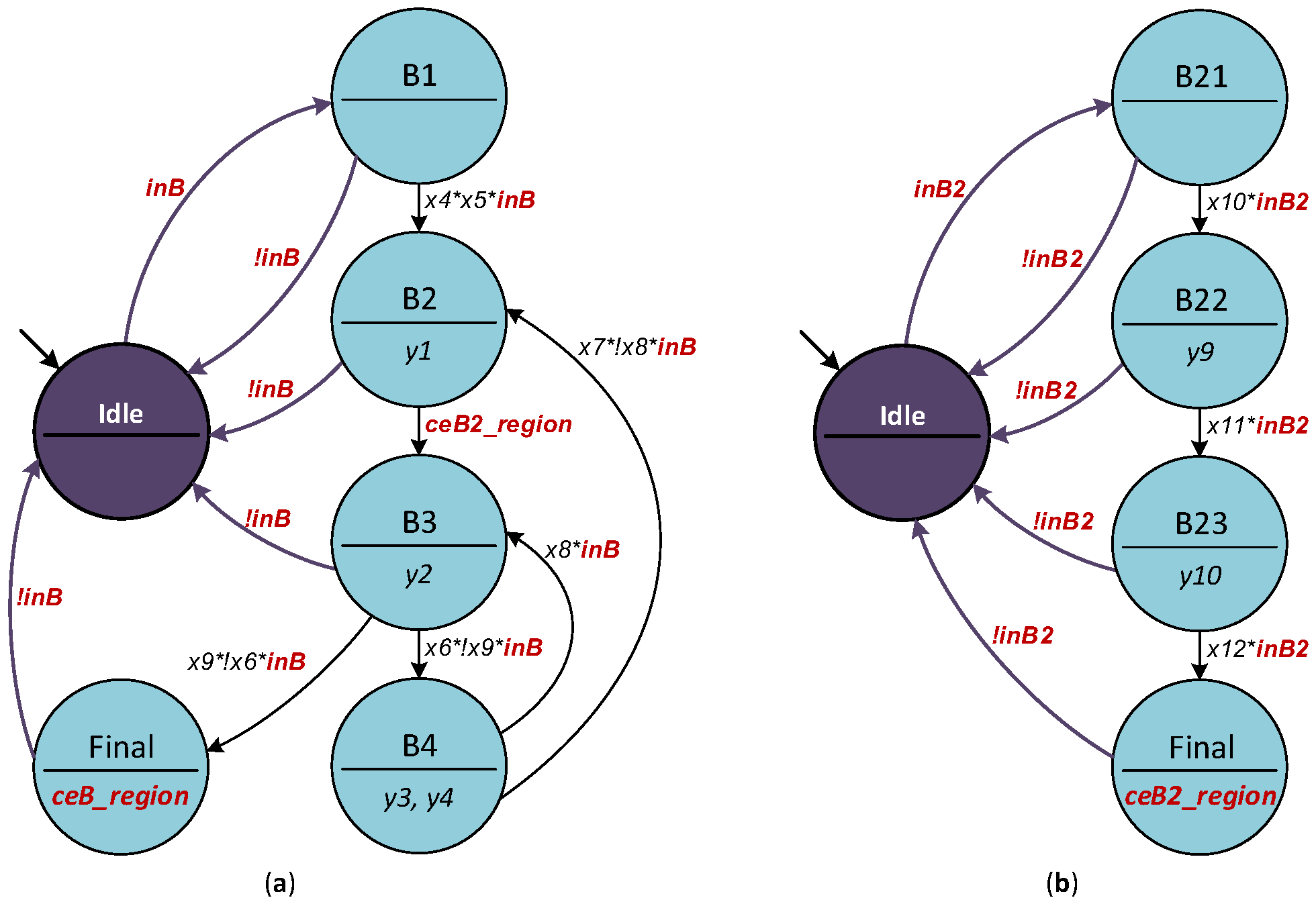

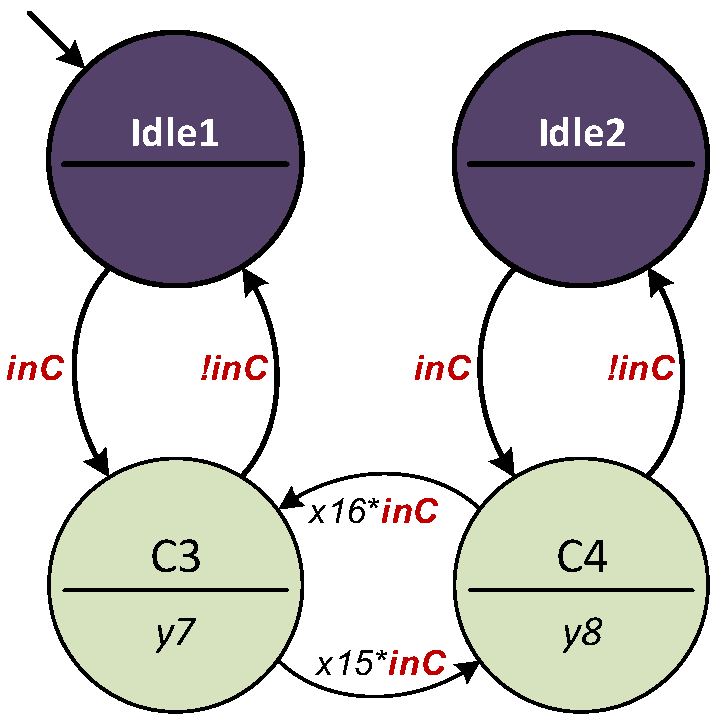

- State machine decomposition.

- Augmenting the obtained FSMs.

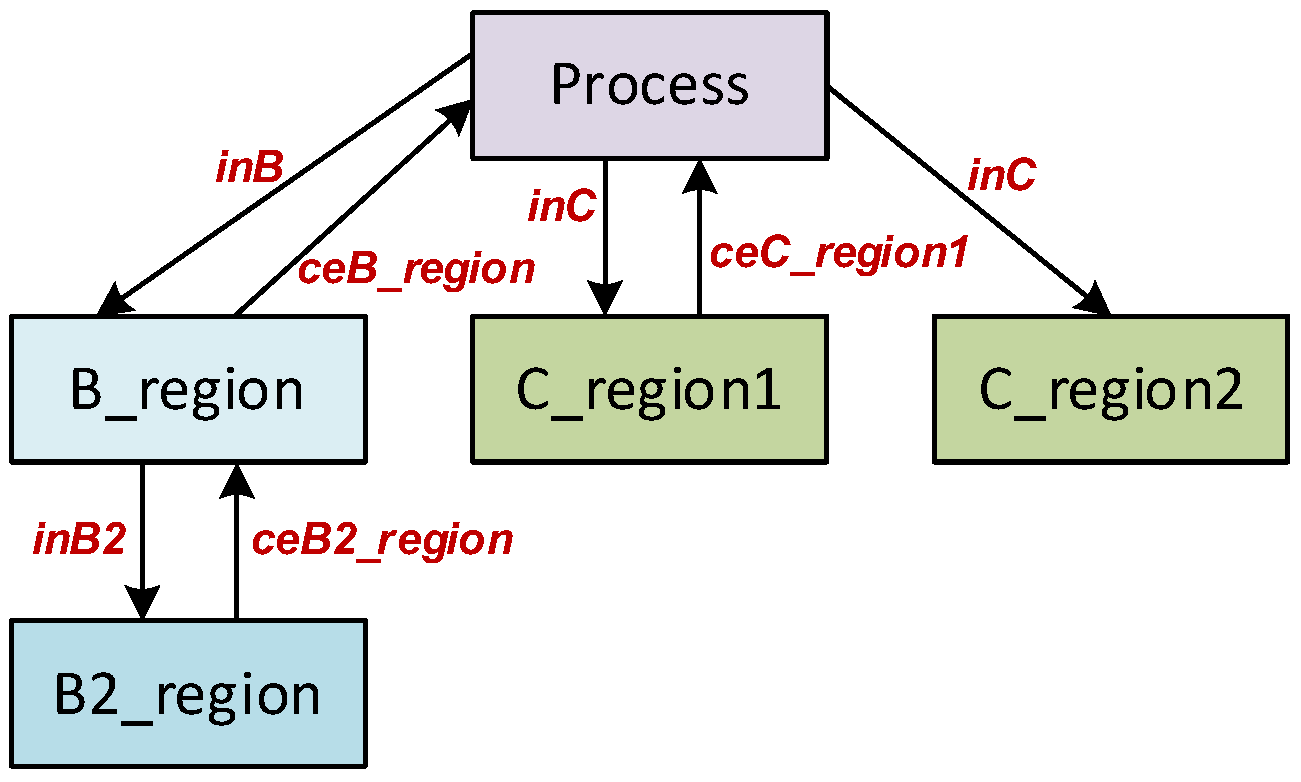

- Building the CFSM model.

3.2.1. State Machine Decomposition

3.2.2. Augmenting the Obtained FSMs

3.2.3. Building a CFSM Model

3.3. Transformation of the CFSM Model into Verilog

3.4. Simulation

3.5. Hardware Implementation

4. Case-Study Example

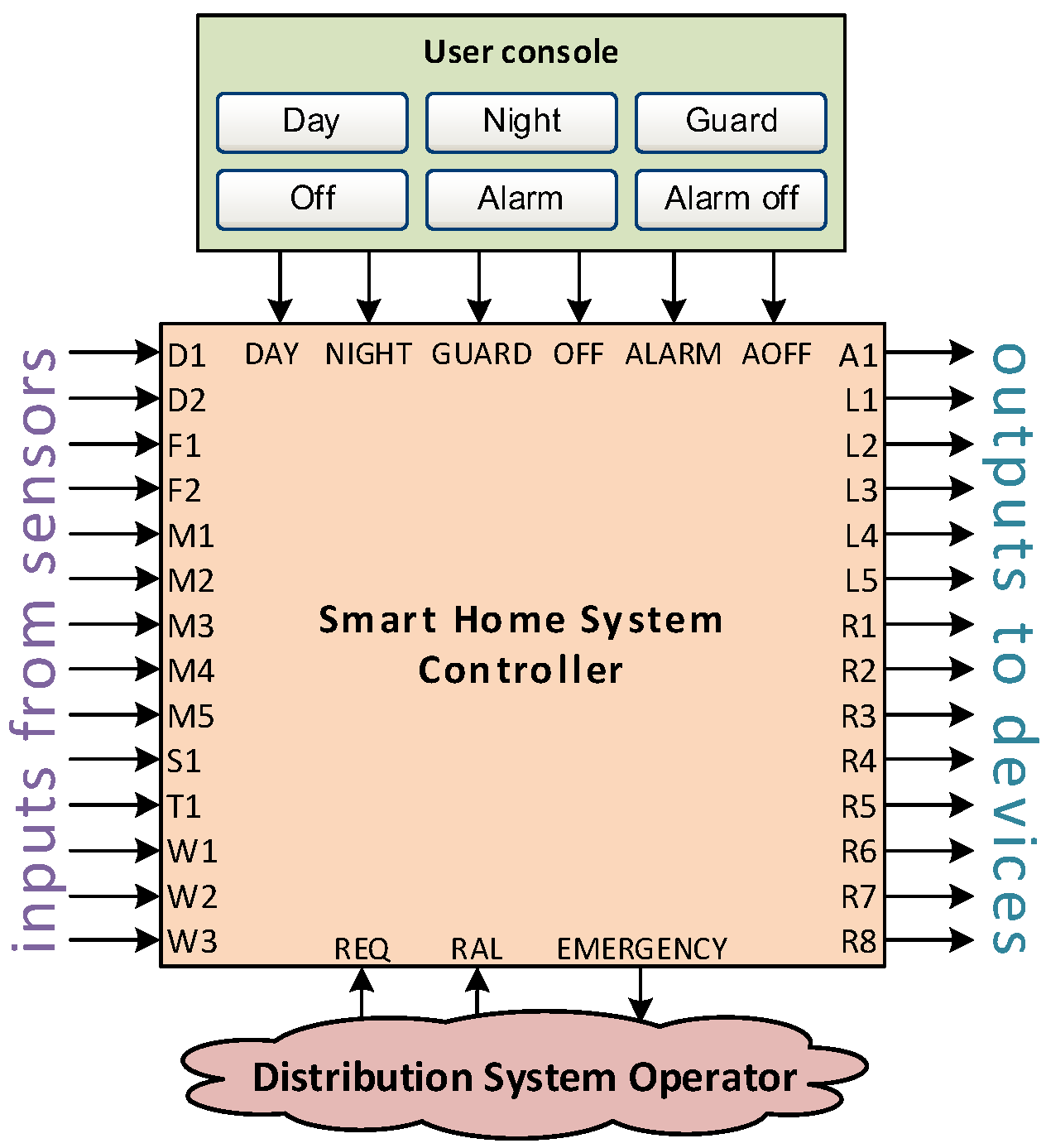

4.1. SHS Description

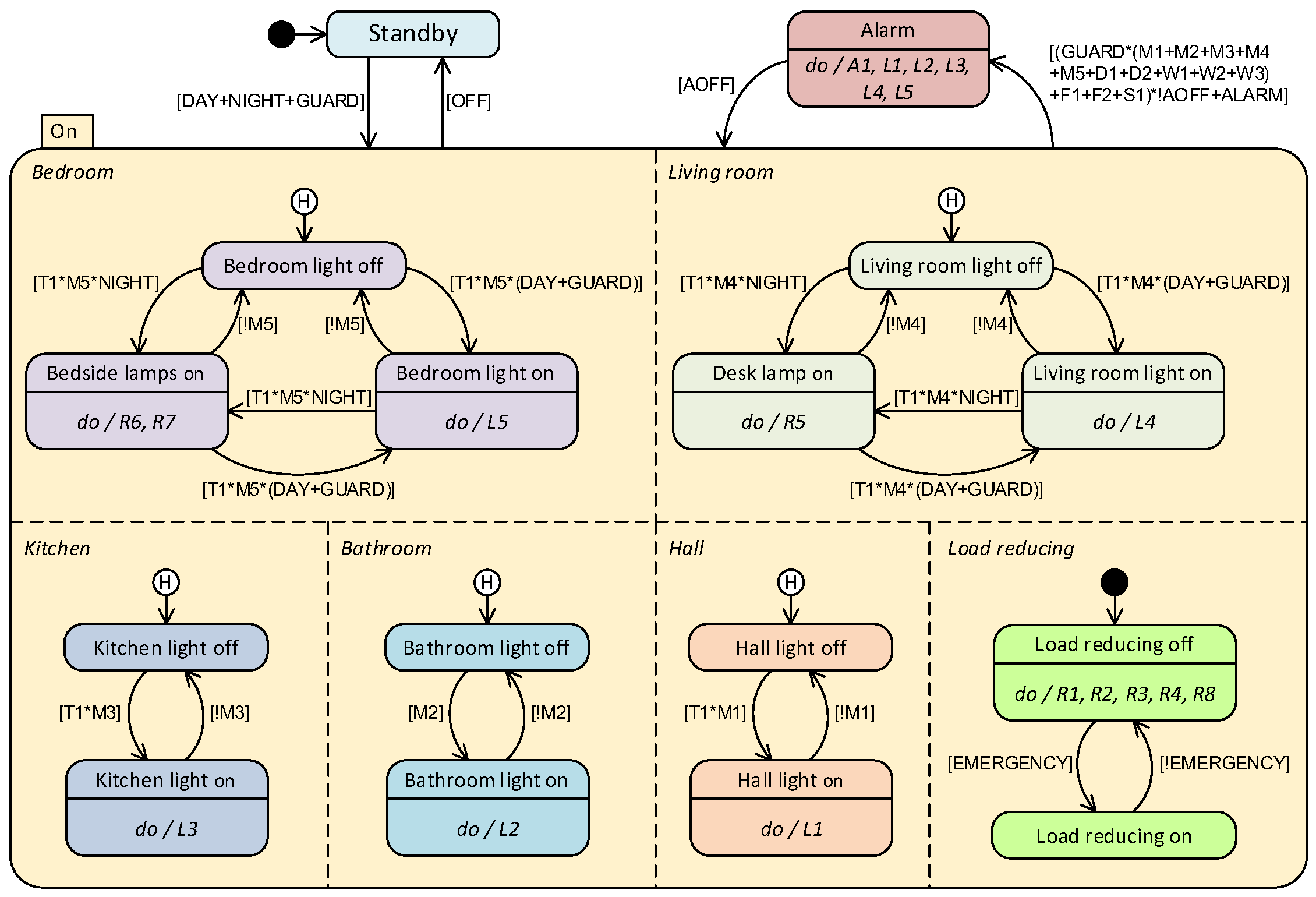

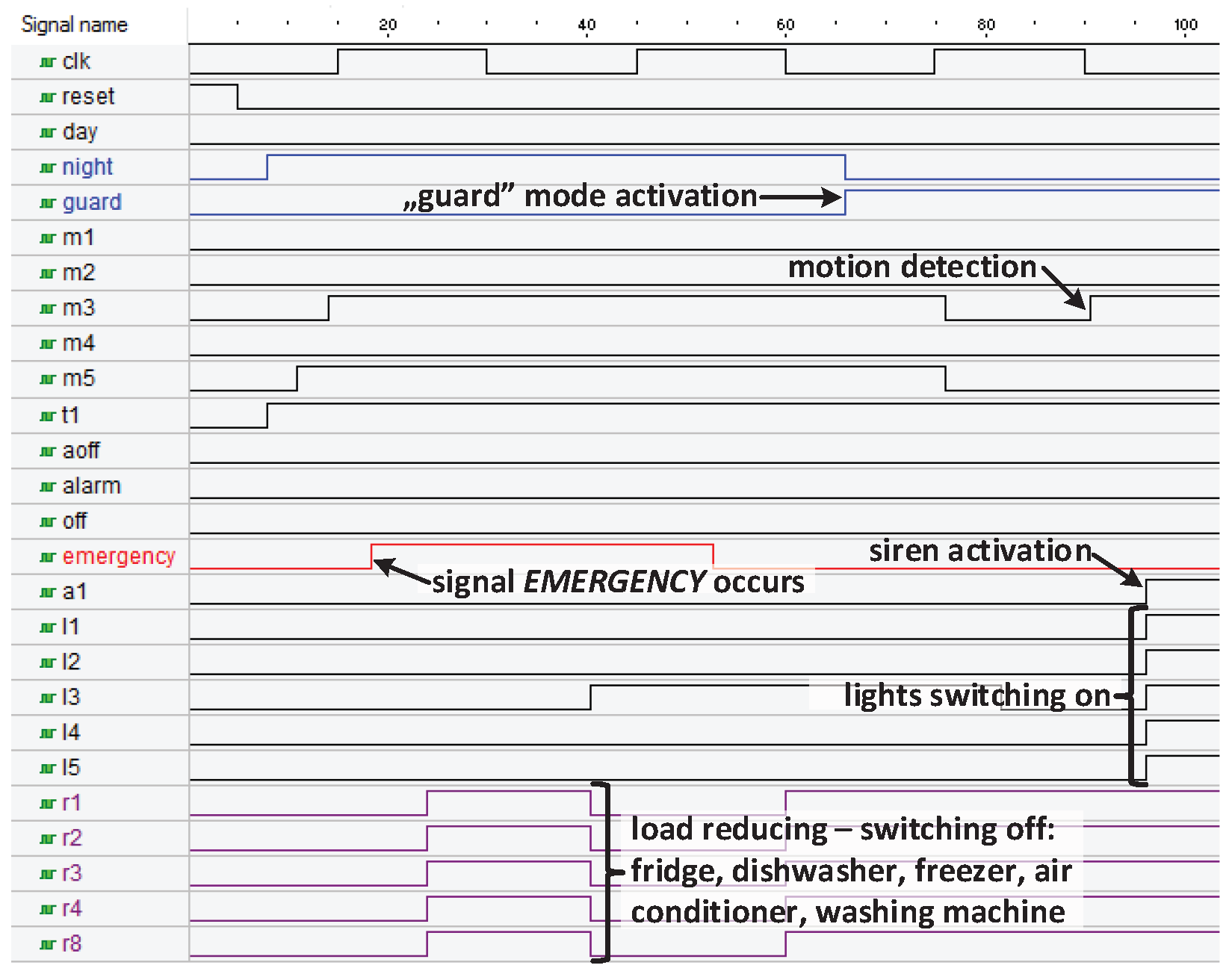

- 14 binary sensors—two door sensors: D1 (on the front door) and D2 (balcony door), three window sensors: W1, W2, W3, two flood sensors: F1 (in the bathroom) and F2 (in the kitchen), smoke detector S1 (in the kitchen), dusk sensor T1 (on the balcony), five motion sensors: M1, M2, M3, M4, M5 (in each room),

- 14 controlled actuators—five light switches: L1, L2, L3, L4, L5 (in each room), alarm siren A1 (in the hall), and eight relay switches, which are connected to a fridge R1, dishwasher R2, and freezer R3 (in the kitchen), air conditioner R4 and desk lamp R5 (in the living room), two bedside lamps: R6 and R7 (in the bedroom) and washing machine R8 (in the bathroom),

- 1 SHS controller (all sensors and actuators are connected to the SHS controller).

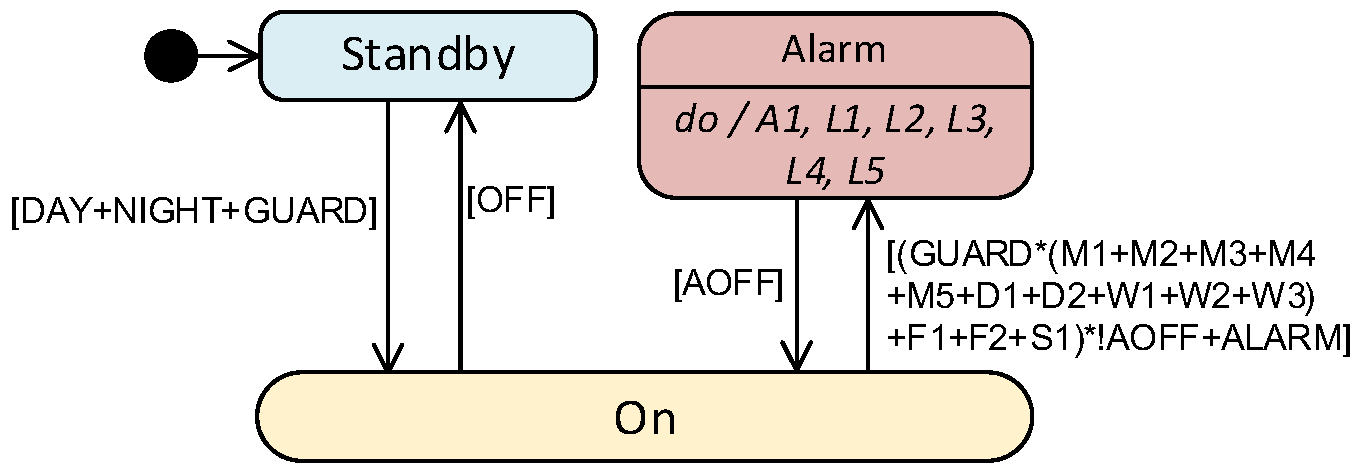

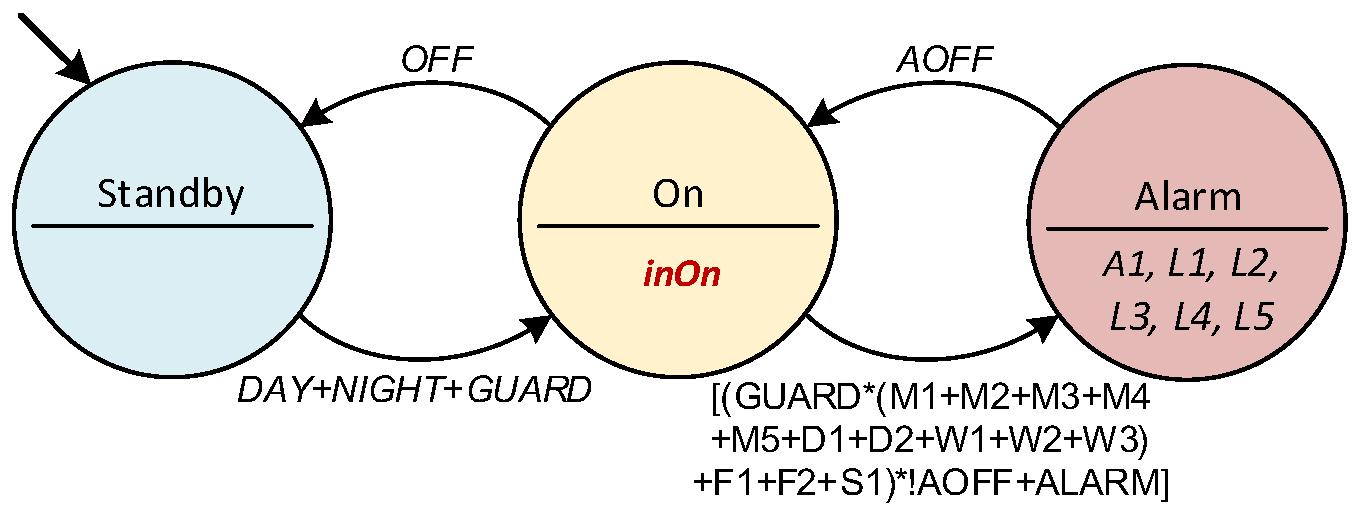

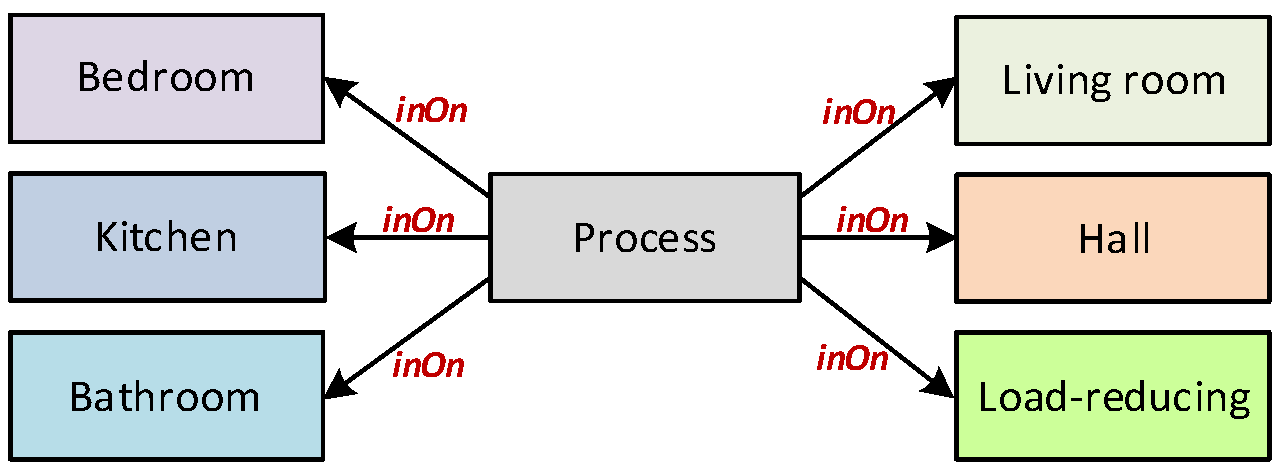

4.2. Design of the SHS Controller

4.3. Dynamic Partial Reconfiguration

5. Discussion

5.1. Verification of the Proposed Method

- First, based on the user requirements, a system was modeled with the use of a UML state machine diagram.

- Then the state machine model using a temporary CFSM model was transformed into a synthesizable and modular Verilog specification.

- In the next step, using the Active-HDL tool, the correctness of Verilog files was verified.

- Then the simulation (with the use of Active-HDL) was done, and the obtained results were compared with the initial CPS requirements.

- Finally, using the Xilinx ISE environment, a synthesis process was carried out to check if the output specification can be truly synthesized.

5.2. Limitation and Scope of the Method

5.3. Comparison with Other Methods and Approaches

6. Conclusions

Funding

Data Availability Statement

Conflicts of Interest

Appendix A. Smart Home System (SHS) Requirements

- when the SHS controller is in the “Day” mode (signal DAY = 1) it should automatically:

- −

- if it is dark outside, switch on the light in the living room and bedroom, but only if the residents are there (if T1 = 1 and Mi = 1 then Li = 1, where i = {4,5}),

- −

- switch off the light in the living room and bedroom, where there is no one (if Mi = 0 then Li = 0, where i = {4,5}),

- when the SHS controller is in the “Night” mode (all residents are sleeping, signal NIGHT = 1) it should automatically:

- −

- if it is dark outside, switch on the bedside lamps in the bedroom, when somebody moves (if T1 = 1 and M5 = 1 then R6 = 1 and R7 = 1),

- −

- if it is dark outside, switch on the desk lamp in the living room, when somebody moves (if T1 = 1 and M4 = 1 then R5 = 1),

- −

- switch off the bedside lamps in the bedroom, if there is no movement (if M5 = 0 then R6 = 0 and R7 = 0),

- −

- switch off the desk lamp in the living room, if there is no movement (if M4 = 0 then R5 = 0),

- when the SHS controller is in the “Guard” mode (there is no one inside, signal GUARD = 1) it should automatically:

- −

- if somebody moves, switch on the alarm siren (if Mi = 1 then A1 = 1, where i = {1,2,3,4,5}),

- −

- if somebody opens the door, switch on the alarm siren (if Di = 1 then A1 = 1, where i = {1,2}),

- −

- if somebody opens the window, switch on the alarm siren (if Wi = 1 then A1 = 1, where i = {1,2,3}),

- when the SHS controller is in the “Alarm” mode (signal ALARM = 1) it should automatically:

- −

- switch on the alarm siren and switch on the lights in the hall, bedroom, bathroom, living room, and kitchen to facilitate eventual fire evacuation (if ALARM = 1 then A1 = 1 and Li = 1, where i = {1,2,3,4,5}),

- −

- switch off the alarm siren, if the user pushes the button “Alarm off” (if AOFF = 1 then A1 = 0) on the user console, and “restore” the previous system state (e.g., if the light in the bedroom was switched on before the alarm was activated, after alarm deactivation the light should be also switched on),

- when the SHS controller is in any mode it should automatically:

- −

- switch on the light in the bathroom whenever someone enters this room (if M2 = 1 then L2 = 1),

- −

- if it is dark outside, switch on the light in the hall and kitchen, if somebody is in these rooms (if T1 = 1 and Mi = 1 then Li = 1, where i = {1,3}),

- −

- switch off the light in the hall, kitchen, and bathroom, where there is no one (if Mi = 0 then Li = 0, where i = {1,2,3}),

- −

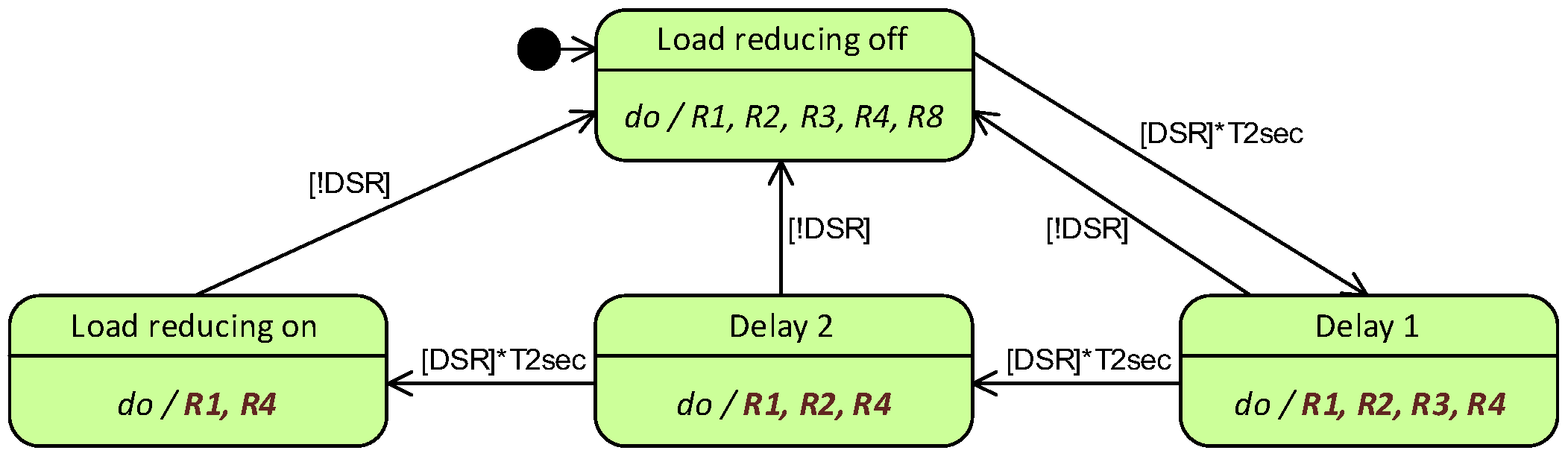

- when the EMERGENCY signal occurs (EMERGENCY = 1), switch off the devices like a fridge (R1 = 0), dishwasher (R2 = 0), freezer (R3 = 0), air conditioner (R4 = 0) and washing machine (R8 = 0), which means, that these devices are disconnected from the power grid and cannot be used by the user,

- −

- when the EMERGENCY signal is not active (EMERGENCY = 0), switch on the fridge (R1 = 1), dishwasher (R2 = 1), freezer (R3 = 1), air conditioner (R4 = 1) and washing machine (R8 = 1), which means, that these devices are connected to the power grid and can be switched on/off and used by the user,

- −

- when the user pushes the “Off” button (OFF = 1), switch the system to the standby state,

- −

- when the user pushes the “Day”/“Night”/“Guard”/“Alarm” button (DAY = 1, NIGHT = 1, GUARD = 1, ALARM = 1), activate the appropriate “Day”/“Night”/“Guard”/“Alarm” mode,

- −

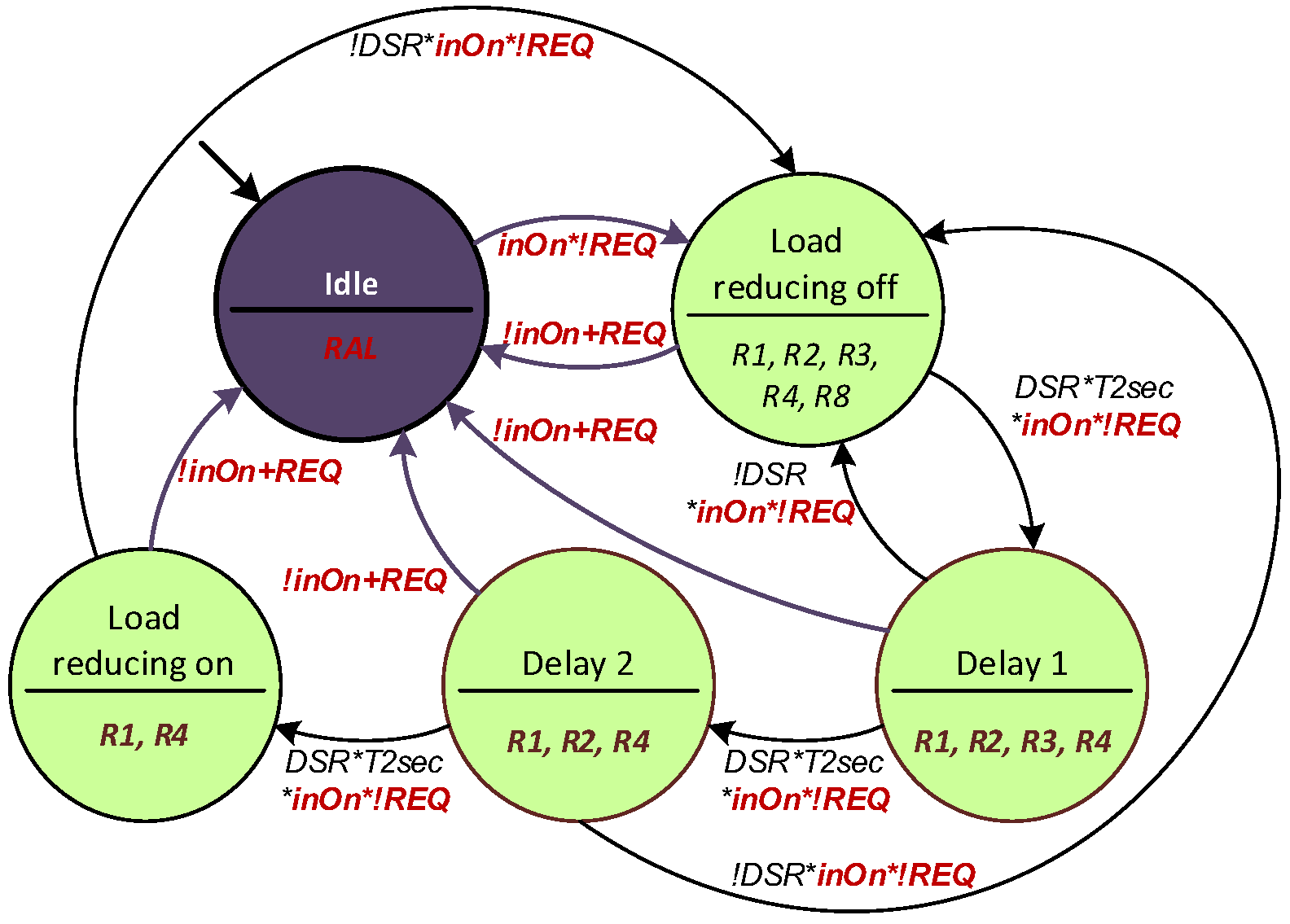

- when the REQ signal is active (REQ = 1) the system should wait for the safe state of the system when the reconfiguration can be done, and indicate this state by activation of the RAL signal,

- when the SHS controller is switched on, the system should stand by and wait for the user’s choice of mode (by pressing the appropriate mode button).

| Signal | Meaning of Active Signal |

|---|---|

| DAY | The system is in the “Day” mode |

| NIGHT | The system is in the “Night” mode |

| GUARD | The system is in the “Guard” mode |

| OFF | The system is in the standby mode |

| ALARM | The system is in the “Alarm” mode |

| AOFF | The alarm is off |

| EMERGENCY | There is an urgent need for load reduction (signal sent by DSO) |

| D1 | The front door is open |

| D2 | The balcony door is open |

| W1 | The window in the bedroom is open |

| W2 | The window in the kitchen is open |

| W3 | The balcony window is open |

| F1 | There is water on the floor in the bathroom |

| F2 | There is water on the floor in the kitchen |

| S1 | There is smoke in the kitchen |

| T1 | It is dark outside |

| M1 | Motion in the hall has been detected |

| M2 | Motion in the bathroom has been detected |

| M3 | Motion in the kitchen has been detected |

| M4 | Motion in the living room has been detected |

| M5 | Motion in the bedroom has been detected |

| REQ | DSO wants to reconfigure the SHS controller (signal sent by DSO) |

| RAL | The SHS controller is ready for dynamic partial reconfiguration |

References

- Lee, E.A.; Seshia, S.A. Introduction to Embedded Systems, a Cyber-Physical Systems Approach, 2nd ed.; MIT Press: Cambridge, MA, USA, 2017. [Google Scholar]

- Lee, E.A. Cyber Physical Systems: Design Challenges. In Proceedings of the 11th IEEE International Symposium on Object Oriented Real-Time Distributed Computing (ISORC), Orlando, FL, USA, 5–7 May 2008. [Google Scholar]

- Zhang, Y.; Qiu, M.; Tsai, C.-W.; Hassan, M.M.; Alamri, A. Health-CPS: Healthcare Cyber-Physical System Assisted by Cloud and Big Data. IEEE Syst. J. 2017, 11, 88–95. [Google Scholar] [CrossRef]

- Shih, C.-S.; Chou, J.-J.; Reijers, N.; Kuo, T.-W. Designing CPS/IoT applications for smart buildings and cities. IET Cyber-Phys. Syst. Theory Appl. 2016, 1, 3–12. [Google Scholar] [CrossRef]

- Guo, Y.; Hu, X.; Hu, B.; Cheng, J.; Zhou, M.; Kwok, R.Y.K. Mobile Cyber Physical Systems: Current Challenges and Future Networking Applications. IEEE Access 2018, 6, 12360–12368. [Google Scholar] [CrossRef]

- Patalas-Maliszewska, J.; Posdzich, M.; Skrzypek, K. Modelling information for the burnishing process in a cyber-physical production system. Int. J. Appl. Math. Comput. Sci. 2022, 32, 345–354. [Google Scholar] [CrossRef]

- Zurawski, R. Embedded Systems Handbook; CRC Press: Boca Raton, FL, USA, 2005. [Google Scholar]

- Paulsson, K.; Hubner, M.; Becker, J. Strategies to On-Line Failure Recovery in Self-Adaptive Systems based on Dynamic and Partial Reconfiguration. In Proceedings of the First NASA/ESA Conference on Adaptive Hardware and Systems (AHS’06), Istanbul, Turkey, 15–18 June 2006; pp. 288–291. [Google Scholar]

- Vargas, J.S.; Moreno, J.M.; Madrenas, J.; Cabestany, J. Self-adaptive Hardware Architecture with Parallel Processing Capabilities and Dynamic Reconfiguration. In Proceedings of the 16th Workshop on Adaptive and Reflective Middleware (ARM ’17), Las Vegas, NV, USA, 11–15 December 2017; ACM: New York, NY, USA, 2017. [Google Scholar]

- An, X.; Rutten, J.; Diguet, E.; Gamatié, A. Model-Based Design of Correct Controllers for Dynamically Reconfigurable Architectures. ACM Trans. Embed. Comput. Syst. 2016, 15, 51. [Google Scholar] [CrossRef] [Green Version]

- Linehan, E.; Clarke, S. An aspect-oriented, model-driven approach to functional hardware verification. J. Syst. Archit. 2012, 58, 195–208. [Google Scholar] [CrossRef]

- Mohamed, M.A.; Challenger, M.; Kardas, G. Applications of model-driven engineering in cyber-physical systems: A systematic mapping study. J. Comput. Lang. 2020, 59, 100972. [Google Scholar] [CrossRef]

- Guglielmo, G.; Guglielmo, L.; Foltinek, A.; Fujita, M.; Fummi, F.; Marconcini, C.; Pravadelli, G. On the integration of model-driven design and dynamic assertion-based verification for embedded software. J. Syst. Softw. 2013, 86, 2013–2033. [Google Scholar] [CrossRef]

- Object Management Group: Unified Modeling Language (UML), OMG UML Specification v.2.5.1. Available online: https://www.omg.org/spec/UML/2.5.1/PDF (accessed on 23 December 2022).

- Moreira, T.G.; Wehrmeister, M.A.; Pereira, C.E.; Pétin, J.F.; Levrat, E. Automatic code generation for embedded systems: From UML specifications to VHDL code. In Proceedings of the 8th IEEE International Conference on Industrial Informatics, Osaka, Japan, 13–16 July 2010; pp. 1085–1090. [Google Scholar]

- Ordinez, L.; Eggly, G.; Micheletto, M.; Santos, R. Using UML for Learning How to Design and Model Cyber-Physical Systems. IEEE Rev. Iberoam. Tecnol. Aprendiz. 2020, 15, 50–60. [Google Scholar] [CrossRef]

- Zhao, H. Multi-View Design for Cyber-Physical Systems. Ph.D. Thesis, Université Côte d’Azur, Nice, France, 2022. (In English). [Google Scholar]

- Patnaik, K.S.; Snigdh, I. Architectural Modelling of Cyber Physical Systems Using UML. Int. J. Cyber-Phys. Syst. 2019, 1, 19–37. [Google Scholar] [CrossRef]

- Graja, I.; Kallel, S.; Guermouche, N.; Cheikhrouhou, S.; Hadj Kacem, A. A comprehensive survey on modeling of cyber-physical systems. Concurr. Comput. Pr. Exper. 2020, 32, e4850. [Google Scholar] [CrossRef]

- Object Management Group: Model Driven Architecture (MDA), MDA Guide Rev. 2.0. Available online: https://www.omg.org/cgi-bin/doc?ormsc/14-06-01.pdf (accessed on 23 December 2022).

- Fitz, T.; Theiler, M.; Smarsly, K. A metamodel for cyber-physical systems. Adv. Eng. Inform. 2019, 41, 100930. [Google Scholar] [CrossRef]

- Mohamed, M.A.; Kardas, G.; Challenger, M. A Systematic Literature Review on Model-driven Engineering for Cyber-Physical Systems. arXiv 2021, arXiv:2103.08644. [Google Scholar] [CrossRef]

- Csuvarszki, J.C.; Graics, B.; Vörös, A. Model-Driven Development of Heterogeneous Cyber-Physical Systems. In Proceedings of the 28th PhD Minisymposium of the Department of Measurement and Information Systems, Budapest, Hungary, 1–2 February 2021; Budapest University of Technology and Economics: Budapest, Hungary, 2021; pp. 24–27. [Google Scholar]

- Wood, S.K.; Akehurst, D.H.; Uzenkov, O.; Howells, W.G.J.; McDonald-Maier, K.D. A Model-Driven Development Approach to Mapping UML State Diagrams to Synthesizable VHDL. IEEE Trans. Comput. 2008, 57, 1357–1371. [Google Scholar] [CrossRef]

- Larsen, P.G.; Fitzgerald, J.; Woodcock, J.; Fritzson, P.; Brauer, J.; Kleijn, C.; Sadovykh, A. Integrated tool chain for model-based design of Cyber-Physical Systems: The INTO-CPS project. In Proceedings of the 2nd International Workshop on Modelling, Analysis, and Control of Complex CPS (CPS Data), Vienna, Austria, 11 April 2016; pp. 1–6. [Google Scholar]

- Hartsell, C.; Mahadevan, N.; Ramakrishna, S.; Dubey, A.; Bapty, T.; Johnson, T.; Koutsoukos, X.; Sztipanovits, J.; Karsai, G. Model-based design for CPS with learning-enabled components. In Proceedings of the of the Workshop on Design Automation for CPS and IoT (DESTION ‘19), Montreal, QC, Canada, 15 April 2019; Association for Computing Machinery: New York, NY, USA, 2019; pp. 1–9. [Google Scholar]

- Combemale, B.; Wimmer, M. Towards a Model-Based DevOps for Cyber-Physical Systems. In Software Engineering Aspects of Continuous Development and New Paradigms of Software Production and Deployment. DEVOPS 2019; Bruel, J.M., Mazzara, M., Meyer, B., Eds.; Lecture Notes in Computer Science; Springer: Cham, Switzerland, 2020; p. 12055. [Google Scholar]

- Object Management Group: Systems Modeling Language (SysML), OMG SysML Specification v.1.5. Available online: https://www.sysml.org/.res/docs/specs/OMGSysML-v1.5-17-05-01.pdf (accessed on 23 December 2022).

- Object Management Group: UML Profile for MARTE, Ver. 1.2. 2019. Available online: https://www.omg.org/spec/MARTE/1.2/PDF (accessed on 23 December 2022).

- Kapos, G.D.; Dalakas, V.; Tsadimas, A.; Nikolaidou, M.; Anagnostopoulos, D. Model-based system engineering using SysML: Deriving executable simulation models with QVT. In Proceedings of the 2014 IEEE International Systems Conference Proceedings, Ottawa, ON, Canada, 31 March–3 April 2014; pp. 531–538. [Google Scholar]

- Berrani, S.; Hammad, A.; Mountassir, H. Mapping SysML to Modelica to validate wireless sensor networks non-functional requirements. In Proceedings of the 11th International Symposium on Programming and Systems (ISPS), Algiers, Algeria, 22–24 April 2013; pp. 177–186. [Google Scholar]

- Schranz, M.; Sende, M. Modeling Swarm Intelligence Algorithms for CPS Swarms. Ada Lett. 2020, 40, 64–73. [Google Scholar] [CrossRef]

- IBM: IBM Engineering Systems Design Rhapsody. Available online: https://www.ibm.com/pl-pl/products/systems-design-rhapsody (accessed on 23 December 2022).

- Xilinx: StateCAD. Available online: https://www.xilinx.com/products/design-tools/ise-design-suite.html (accessed on 23 December 2022).

- Mathworks: HDL Coder. Available online: http://www.mathworks.com/products/slhdlcoder (accessed on 23 December 2022).

- Coyle, F.P.; Thornton, M.A. From UML to HDL: A model driven architectural approach to hardware-software co-design. In Proceedings of the Information Systems: New Generations Conference (ISNG), Las Vegas, NV, USA, 11–13 April 2005; Volume 1, pp. 88–93. [Google Scholar]

- Wehrmeister, M.A. Generating ROS-based Software for Industrial Cyber-Physical Systems from UML/MARTE. In Proceedings of the 25th IEEE International Conference on Emerging Technologies and Factory Automation (ETFA), Vienna, Austria, 8–11 September 2020; pp. 313–320. [Google Scholar] [CrossRef]

- Anwar, M.W.; Rashid, M.; Azam, F.; Kashif, M.; Butt, W.H. A model-driven framework for design and verification of embedded systems through SystemVerilog. Des. Autom. Embed. Syst. 2019, 23, 179–223. [Google Scholar] [CrossRef]

- Khan, A.M.; Mallet, F.; Rashid, M. A framework to specify system requirements using natural interpretation of UML/MARTE diagrams. Softw. Syst. Model. 2019, 18, 11–37. [Google Scholar] [CrossRef] [Green Version]

- Bazydło, G.; Adamski, M.; Stefanowicz, Ł. Translation UML diagrams into Verilog. In Proceedings of the 7th International Conference on Human System Interactions (HSI), Costa da Caparica, Portugal, 16–18 June 2014; pp. 267–271. [Google Scholar]

- Object Management Group: XML Metadata Interchange (XMI), OMG XMI Specification v.2.5.1. Available online: https://www.omg.org/spec/XMI/2.5.1/PDF (accessed on 23 December 2022).

- Bazydło, G. Graphic Specification of Programs for Reconfigurable Logic Controllers Using Unified Modeling Language; Lecture Notes in Control and Computer Science; University of Zielona Góra Press: Zielona Góra, Poland, 2012; Volume 19. [Google Scholar]

- Gomes, L.; Costa, A.; Barros, J.; Lima, P. From Petri net models to VHDL implementation of digital controllers. In Proceedings of the 33rd Annual Conference of the IEEE Industrial Electronics Society IECON07, Taipei, Taiwan, 5–8 November 2007; pp. 94–99. [Google Scholar]

- Gajski, D.D.; Abdi, S.; Gerstlauer, A.; Schirner, G. Embedded System Design: Modeling, Synthesis and Verification; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2009. [Google Scholar]

- Wiśniewski, R.; Bazydło, G.; Gomes, L.; Costa, A. Dynamic Partial Reconfiguration of Concurrent Control Systems Implemented in FPGA Devices. IEEE Trans. Ind. Inform. 2017, 13, 1734–1741. [Google Scholar] [CrossRef]

- Nunna, K.; Doolla, S. Responsive end-user-based demand side management in multimicrogrid environment. IEEE Trans. Ind. Inform. 2014, 10, 1262–1272. [Google Scholar] [CrossRef]

- Murata, T. Petri nets: Properties, analysis and applications. Proc. IEEE 1989, 77, 541–580. [Google Scholar] [CrossRef]

- Wiśniewski, R.; Wojnakowski, M.; Li, Z. Design and Verification of Petri-Net-Based Cyber-Physical Systems Oriented toward Implementation in Field-Programmable Gate Arrays—A Case Study Example. Energies 2023, 16, 67. [Google Scholar] [CrossRef]

- Wojnakowski, M.; Wiśniewski, R.; Bazydło, G.; Popławski, M. Analysis of safeness in a Petri net-based specification of the control part of Cyber-Physical Systems. Int. J. Appl. Math. Comput. Sci. 2021, 31, 647–657. [Google Scholar] [CrossRef]

- Wisniewski, R. Design of Petri Net-Based Cyber-Physical Systems Oriented on the Implementation in Field Programmable Gate Arrays. Energies 2021, 14, 7054. [Google Scholar] [CrossRef]

- Girault, C.; Valk, R. Petri Nets for Systems Engineering: A Guide to Modeling, Verification, and Applications; Springer: Berlin/Heidelberg, Germany, 2013. [Google Scholar]

- Wiśniewski, R.; Bazydło, G.; Gomes, L.; Costa, A.; Wojnakowski, M. Analysis and Design Automation of Cyber-Physical System with Hippo and IOPT-Tools. In Proceedings of the IECON 2019—45th Annual Conference of the IEEE Industrial Electronics Society, Lisbon, Portugal, 14–17 October 2019; pp. 5843–5848. [Google Scholar] [CrossRef]

- Łabiak, G.; Wȩgrzyn, M.; Rosado-Muñoz, A.; Bazydło, G. Dual-model approach for safety-critical embedded systems. Microprocess. Microsyst. 2020, 72, 102924. [Google Scholar] [CrossRef]

- Baresi, L.; Pezzè, M. On Formalizing UML with High-Level Petri Nets. In Concurrent Object-Oriented Programming and Petri Nets; Agha, G.A., De Cindio, F., Rozenberg, G., Eds.; Lecture Notes in Computer Science; Springer: Berlin/Heidelberg, Germany, 2001; Volume 2001. [Google Scholar] [CrossRef] [Green Version]

- Distefano, S.; Scarpa, M.; Puliafito, A. From UML to Petri Nets: The PCM-Based Methodology. IEEE Trans. Softw. Eng. 2011, 37, 65–79. [Google Scholar] [CrossRef]

- Shailesh, T.; Nayak, A.; Prasad, D. An UML Based Performance Evaluation of Real-Time Systems Using Timed Petri Net. Computers 2020, 9, 94. [Google Scholar] [CrossRef]

- Lyazidi, A.; Mouline, S. Formal Verification of UML State Machine Diagrams Using Petri Nets. In Networked Systems. NETYS 2019; Atig, M., Schwarzmann, A., Eds.; Lecture Notes in Computer Science; Springer: Cham, Switzerland, 2019; Volume 11704. [Google Scholar] [CrossRef]

- Vanderperren, Y.; Mueller, W.; Dehaene, W. UML for electronic systems design: A comprehensive overview. Des. Autom. Embed. Syst. 2008, 12, 261–292. [Google Scholar] [CrossRef]

- Barkalov, A.; Titarenko, L.; Krzywicki, K.; Saburova, S. Improving Characteristics of LUT-Based Mealy FSMs. Int. J. Appl. Math. Comput. Sci. 2021, 10, 901. [Google Scholar]

- Barkalov, A.; Titarenko, L.; Mazurkiewicz, M. Improving the LUT count for Mealy FSMs with transformation of output collections. Int. J. Appl. Math. Comput. Sci. 2022, 32, 479–494. [Google Scholar] [CrossRef]

- Lysaght, P.; Blodget, B.; Mason, J.; Young, J.; Bridgford, B. Invited Paper: Enhanced Architectures, Design Methodologies and CAD Tools for Dynamic Reconfiguration of Xilinx FPGAs. In Proceedings of the Field Programmable Logic and Applications, FPL ’06, Madrid, Spain, 28–30 August 2006; pp. 1–6; 28–30. [Google Scholar]

- Durand, S.H.M.; Bonato, V. A tool to support Bluespec System Verilog coding based on UML diagrams. In Proceedings of the IEEE 38th Annual Conference on Industrial Electronics IECON, Montreal, QC, Canada, 25–28 October 2012; pp. 4670–4675. [Google Scholar]

- McUmber, W.; Cheng, B. UML-based analysis of embedded systems using a mapping to VHDL. In Proceedings of the 4th IEEE International Symposium on High-Assurance Systems Engineering, Washington, DC, USA, 17–19 November 1999; IEEE: New York, NY, USA, 1999; pp. 56–63. [Google Scholar]

- Łabiak, G. Using a Hierarchical Model of Concurrent Automation in Design of Digital Controllers; Lecture Notes in Control and Computer Science; University of Zielona Góra Press: Zielona Góra, Poland, 2005; Volume 6. (In Polish) [Google Scholar]

- Ranaldi, L.; Fallucchi, F.; Zanzotto, F.M. Dis-Cover AI Minds to Preserve Human Knowledge. Future Internet 2022, 14, 10. [Google Scholar] [CrossRef]

- Lohstroh, M.; Menard, C.; Bateni, S.; Lee, E.A. Toward a Lingua Franca for Deterministic Concurrent Systems. ACM Trans. Embed. Comput. Syst. 2021, 20, 36. [Google Scholar] [CrossRef]

| Feature of the Method | [13] | [62] | [63] | [36] | [24] | [64] | U2V |

|---|---|---|---|---|---|---|---|

| Using models in UML 2.x | + | + | + | + | + | − | + |

| Using MDD approach | + | − | + | + | + | − | + |

| Support for hierarchical systems | + | + | + | − | + | + | + |

| Support for concurrent systems | + | + | + | − | + | + | + |

| Generating of system description in HDL | − | + | + | + | + | + | + |

| Output specification is synthesizable | − | + | − | + | + | + | + |

| Output specification is modular | − | − | − | − | − | − | + |

| Feature of the Method | MODEASY [24] | U2V |

|---|---|---|

| simple state | + | + |

| composite state | + | + |

| region | + | + |

| submachine state | − | − |

| external transitions | + | + |

| internal transitions | − | + |

| local transitions | − | − |

| initial pseudostate | + | + |

| shallow history pseudostate | + | + |

| deep history pseudostate | + | + |

| join pseudostate | + | − |

| fork pseudostate | + | − |

| junction pseudostate | + | − |

| choice pseudostate | + | − |

| terminate pseudostate | − | − |

| entry point | − | − |

| exit point | − | − |

| deferred events | − | − |

| entry behavior (in the state) | − | + |

| do-activity (in the state) | + | + |

| exit behavior (in the state) | − | + |

| triggers (in the transition) | + | + |

| guards (in the transition) | + | + |

| effects (in the transition) | + | + |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bazydło, G. Designing Reconfigurable Cyber-Physical Systems Using Unified Modeling Language. Energies 2023, 16, 1273. https://doi.org/10.3390/en16031273

Bazydło G. Designing Reconfigurable Cyber-Physical Systems Using Unified Modeling Language. Energies. 2023; 16(3):1273. https://doi.org/10.3390/en16031273

Chicago/Turabian StyleBazydło, Grzegorz. 2023. "Designing Reconfigurable Cyber-Physical Systems Using Unified Modeling Language" Energies 16, no. 3: 1273. https://doi.org/10.3390/en16031273