PLF Design for DC-DC Converters Based on Accurate IL Estimations

Abstract

:1. Introduction

2. Circuit Models of the SMPSs

2.1. Model of Buck Converter

- -

- Mode 1: The switch S conducts, and the diode D is blocked. The inductor L produces an opposing voltage across its terminals in response to the changing current. This voltage drop counteracts the voltage of the source and therefore reduces the net voltage across the load;

- -

- Mode 2: The switch S is blocked, and the diode D conducts. The inductor becomes a current source (the stored energy in the inductor’s magnetic field supports the current flow through the load).

2.2. Model of Boost Converter

- -

- Mode 1: The switch S conducts, and the diode D is blocked. The current is diverted through to the MOSFET through the inductor;

- -

- Mode 2: The switch S is blocked, and the diode D conducts. The output capacitor is charged to the sum of the input voltage and the inductor voltage, stepping up the input DC voltage to higher output.

2.3. Model of a SEPIC Converter

- -

- Mode 1: The switch S conducts, and the diode D is blocked. The energy in L1 is increased, and the capacitor C1 transfers energy to the inductor L2. Since the diode D is blocked, the load’s energy comes from the capacitor C2;

- -

- Mode 2: The switch S is blocked, and the diode D conducts. The inductors L1 and L2 are discharged and provide energy to the load and to the capacitors C1 and C2.

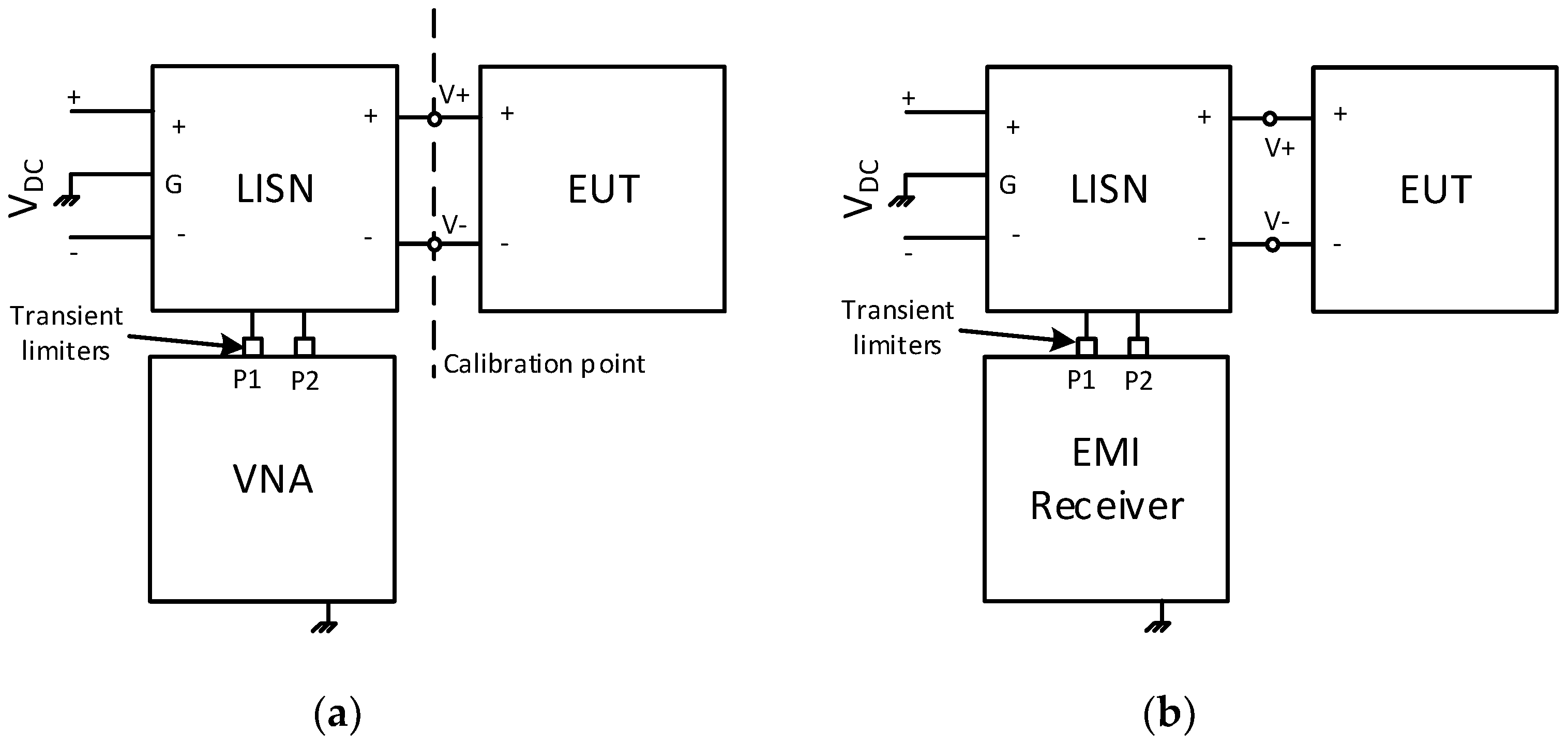

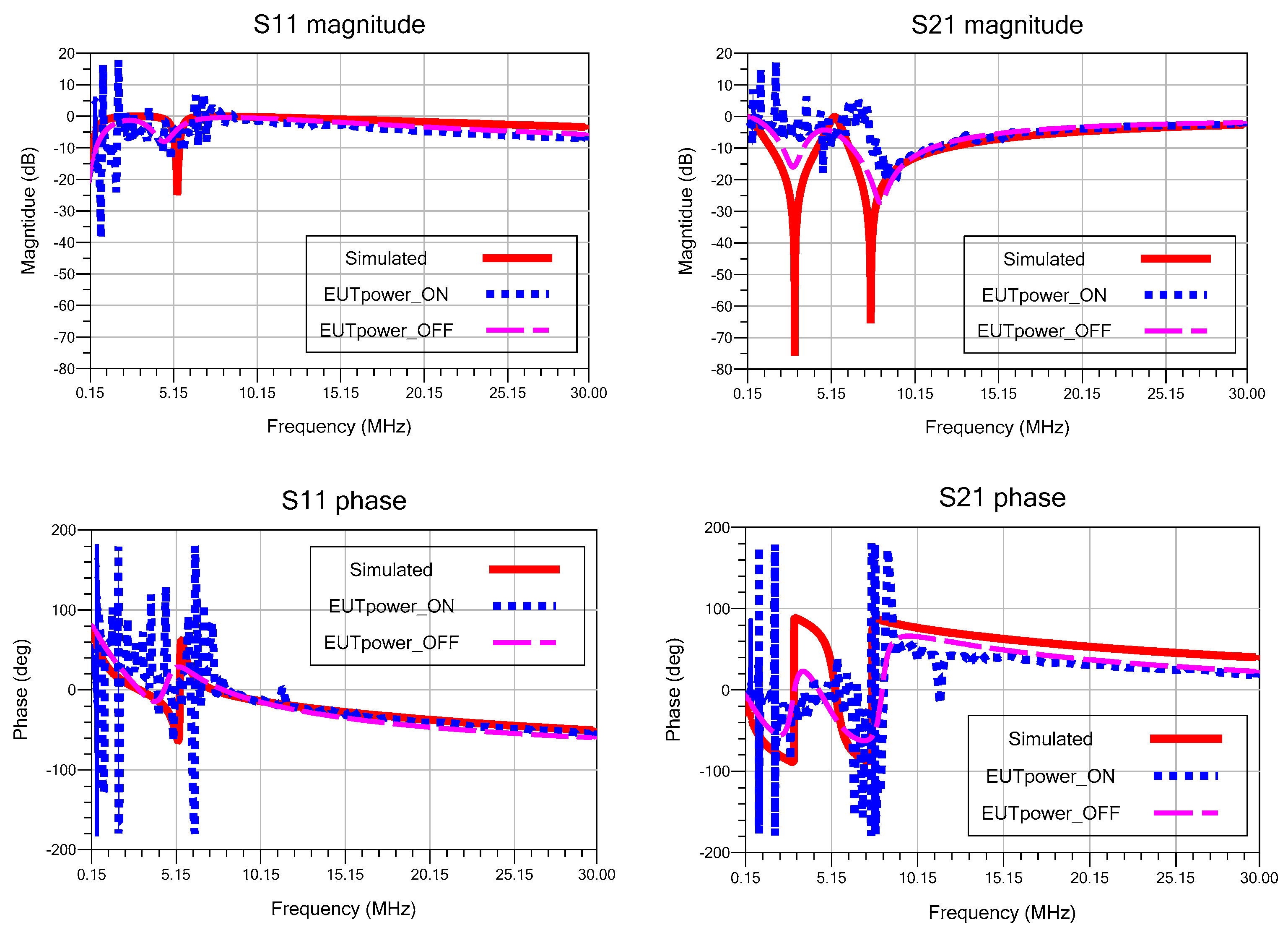

3. EUT Characterization

4. PLF Design

4.1. Accurate Estimation of the IL of a PLF

4.2. PLF Design Methodology

- Measurement of the S-parameters of the EUT;

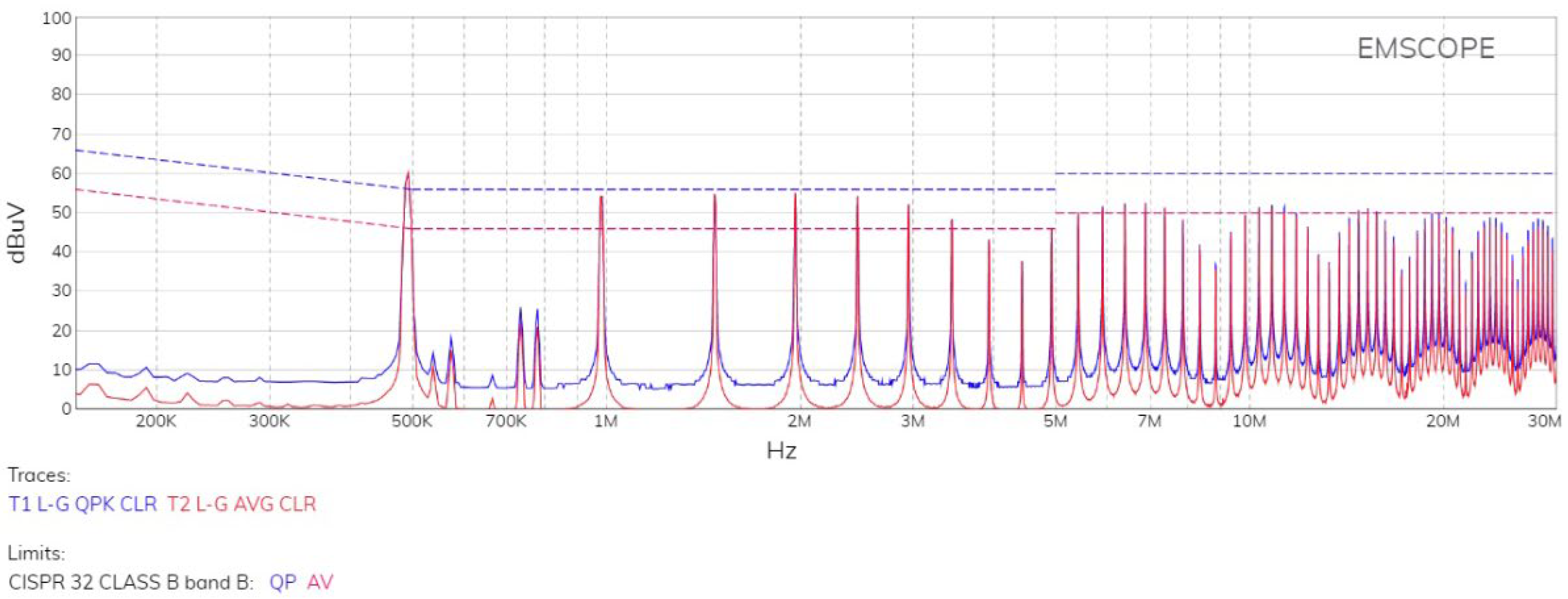

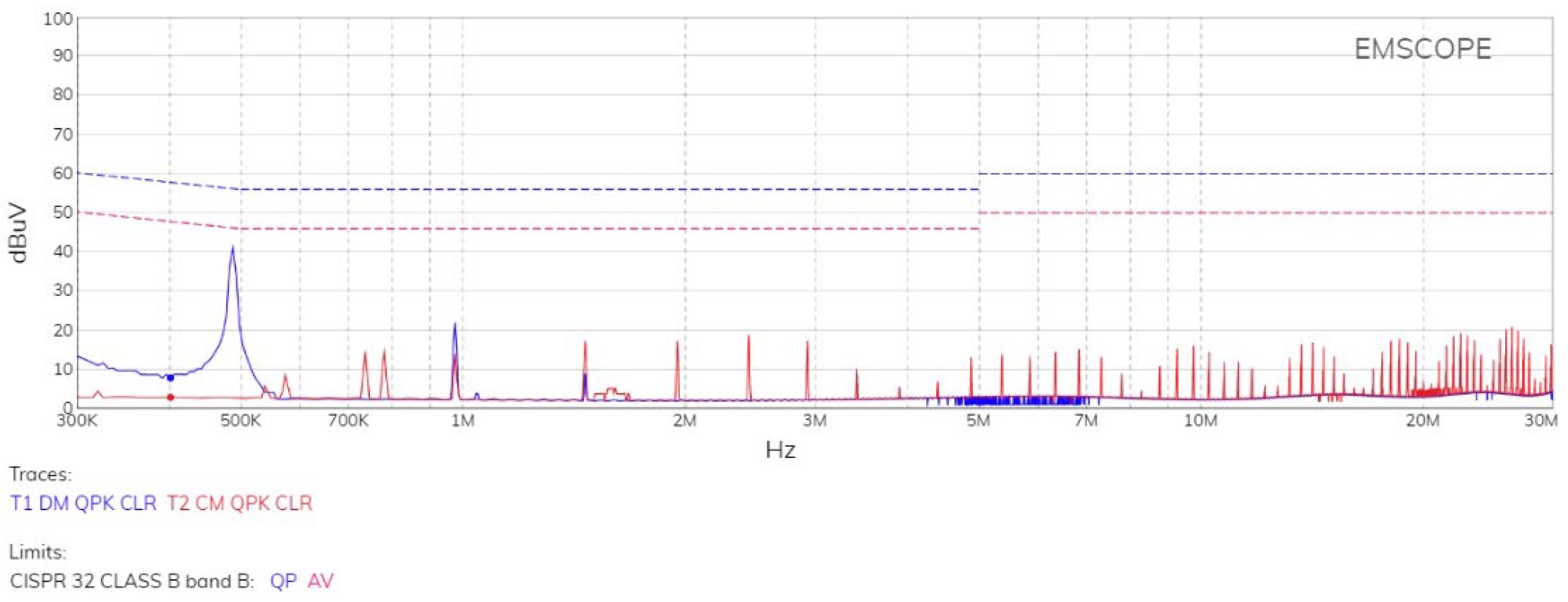

- Measurement of the modal CE and determination of the IL needed to mitigate each mode under a threshold level;

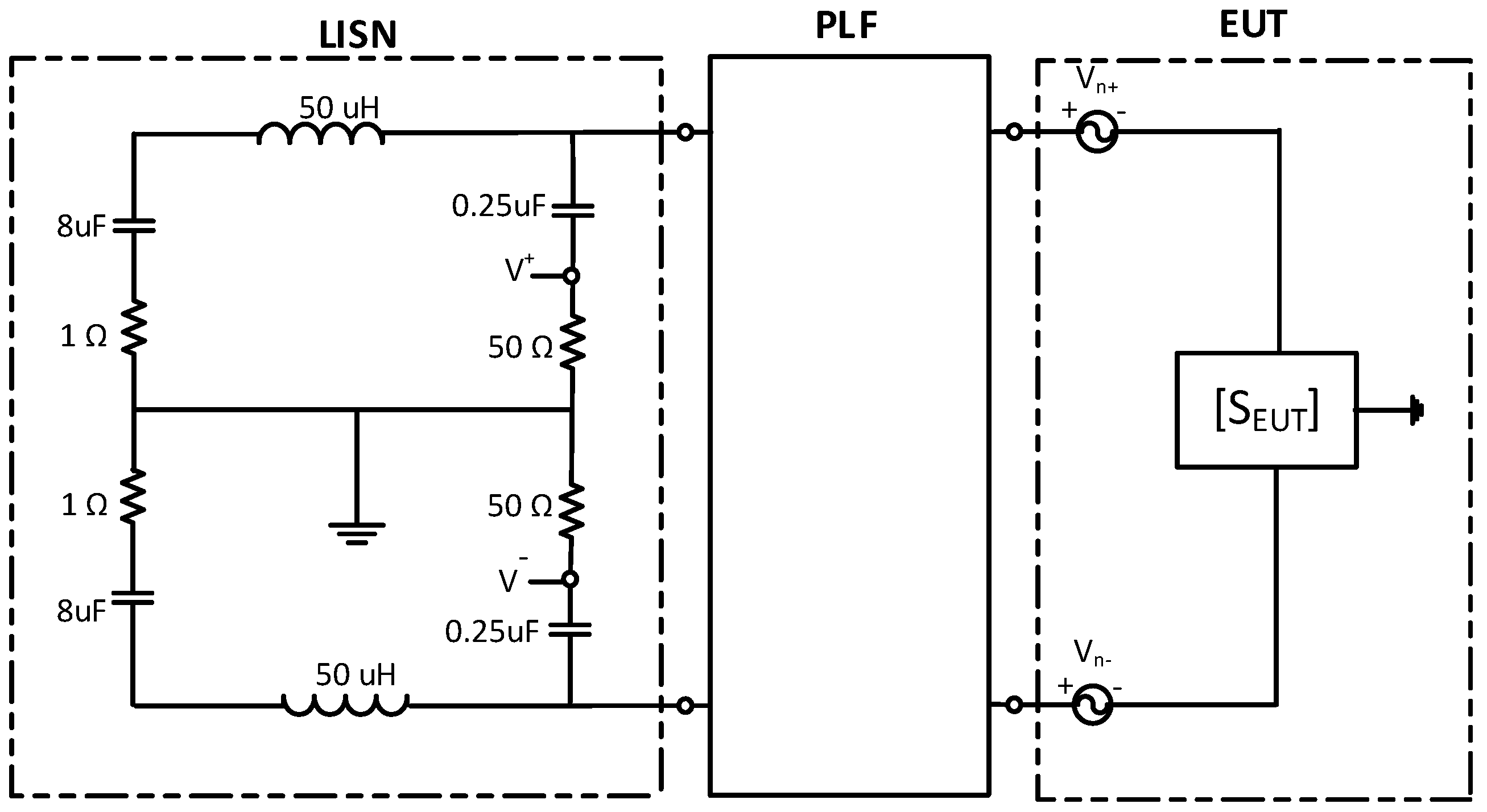

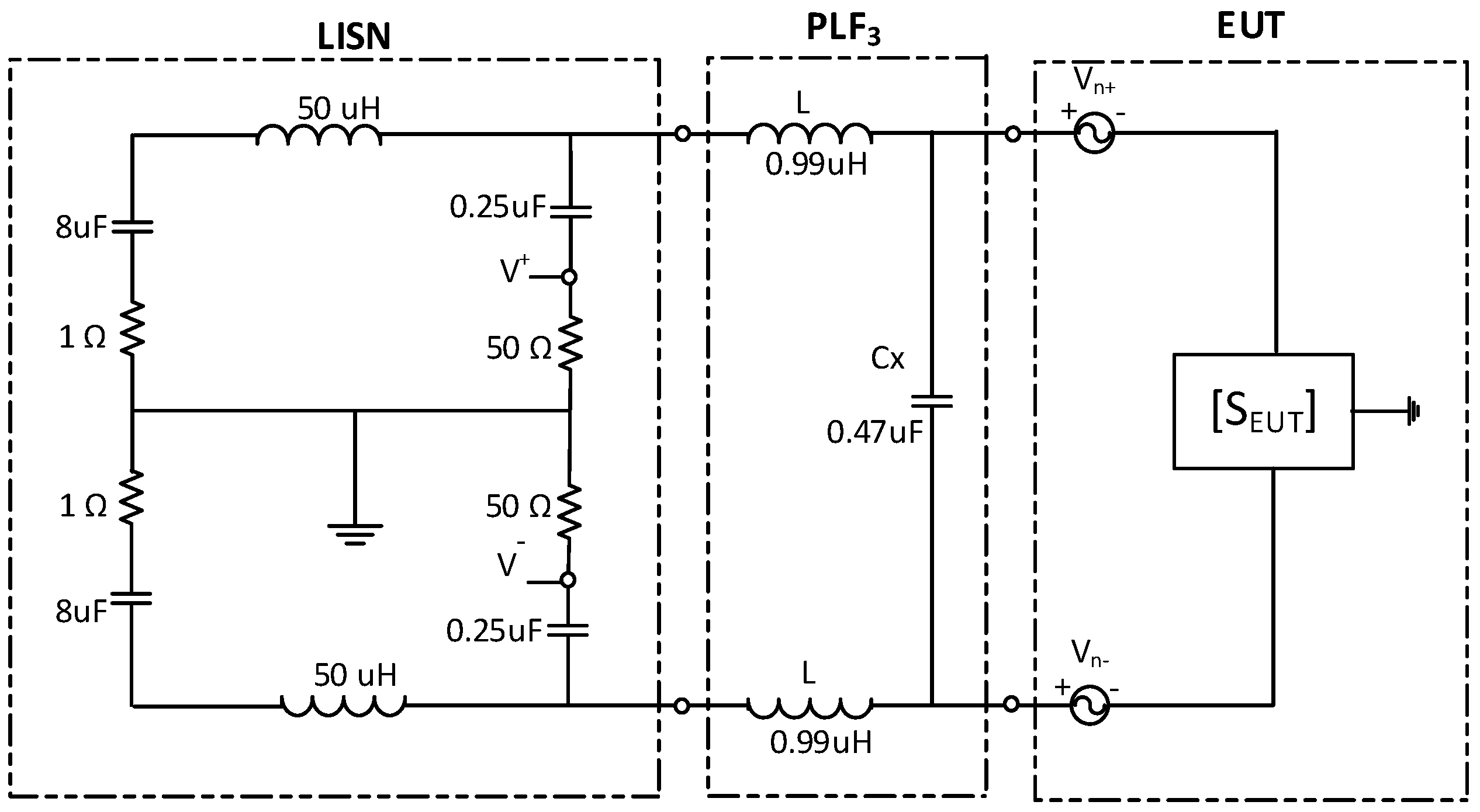

- Introduction of the S-parameters in a circuit simulator as a black box with two ports. The circuit is completed by adding two voltage sources and a LISN circuit, as seen in Figure 5. The two voltage sources emit the same amplitude at all frequencies, and their phase can be modified between 0° and 180° to have pure CM or DM CE, respectively;

- The same circuit is implemented again in the simulator adding the PLF, as seen in Figure 6;

- Both circuits are simulated in the frequency domain, obtaining the voltage amplitude at the measurement ports of the LISN in both cases (that is, ). The CM IL is computed using (5), and the DM IL using (6) (they are both introduced in the simulator, which provides the result);

- Since each simulation needs less than a second to be completed, the determination of the optimal values for each PLF component and its optimal position inside the PLF is done manually using iterative simulations. Optionally, optimization techniques can be implemented to improve this methodology.

5. Experimental Validation

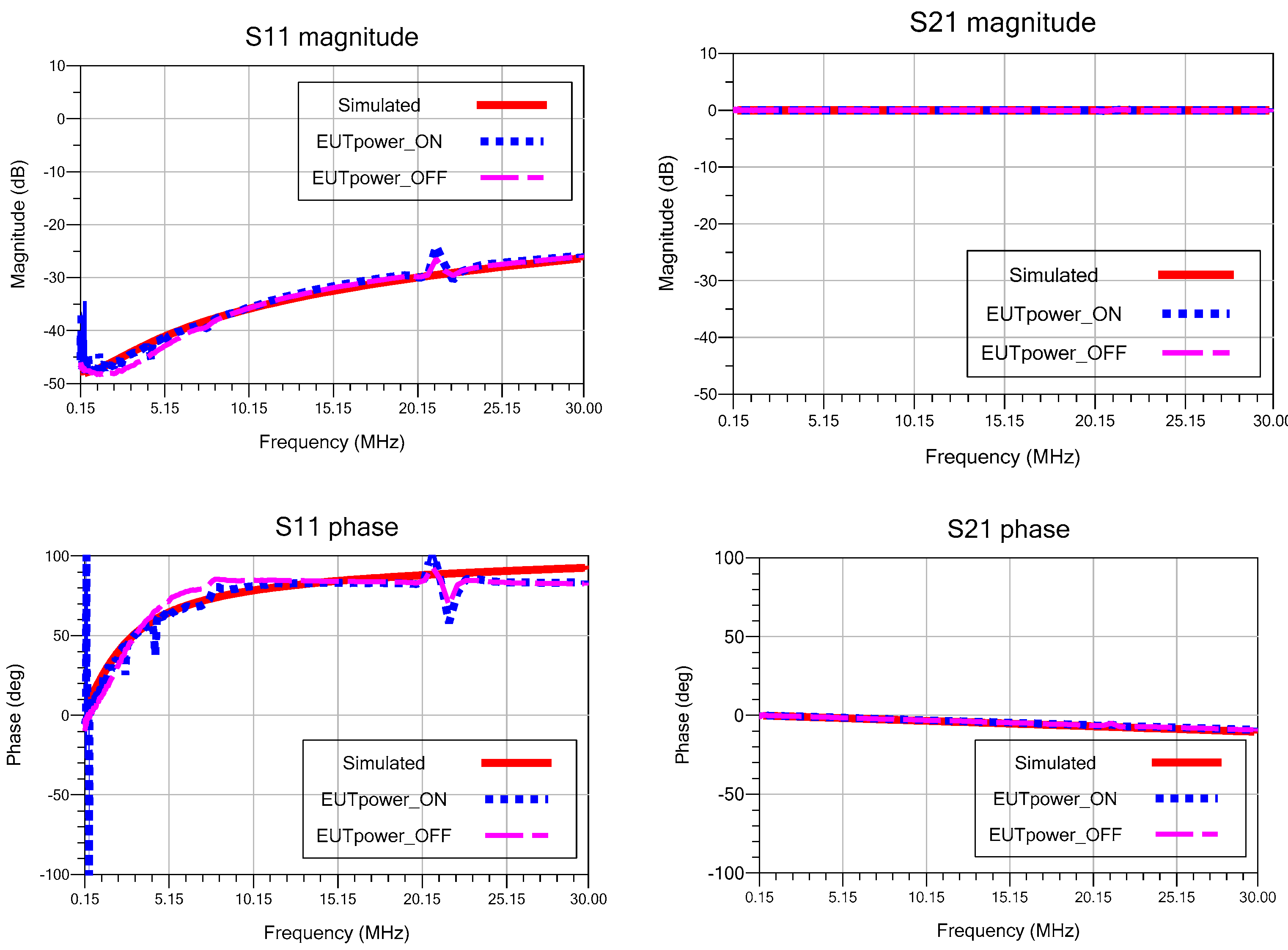

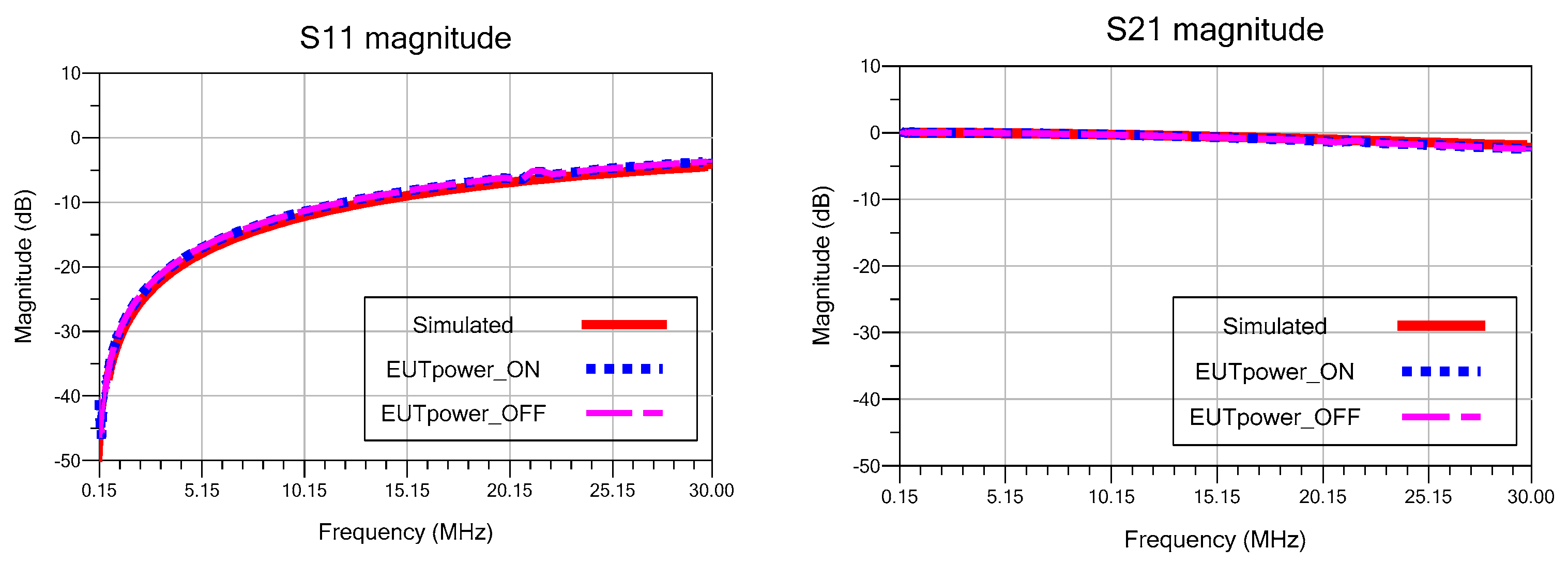

5.1. Validation of the Circuit Models

- The circuit model is implemented in a circuit simulator using the values provided in the datasheet for the normal components (CIN, D, C, …). Parasitic components (CPAR, Lpar1, Lpar2, rS, rD, rC, rL, …) are added with a ‘0’ value. For each parasitic component, a margin of possible values is considered in the simulator;

- The S-parameter measurements obtained from the actual EUT are also introduced in the circuit simulator;

- An optimization algorithm, based on the gradient search method, modifies the values of the parasitic components (within the specified margin) until the computed S-parameters of the circuit model are as equal as possible to the measured ones. When the results are satisfactory (that means that measured and computed S-parameters are very similar both in phase and amplitude), the values of the parasitic components are updated with the values found in the last iteration of the algorithm.

5.1.1. Circuit Validation of the DC-DC Buck Converter Power Supply Module Output 1.23 V–30 V, Model LM2596

5.1.2. Circuit Validation of the Boost Converter Model MCP1640EV-SBC

5.1.3. Circuit Validation of the DC-DC SEPIC Converter Model MCP1663

5.2. Conducted Emissions Measurements

5.3. PLF Design for the Boost Converter

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- CISPR 16-1-1; Specification for Radio Disturbance and Immunity Measuring Apparatus and Methods—Part 1-1: Radio Disturbance and Immunity Measuring Apparatus—Measuring apparatus. International Electrotechnical Commission: Geneva, Switzerland, 2019.

- CISPR 32:2015+AMD1:2019 CSV; Electromagnetic Compatibility of Multimedia Equipment—Emission Requirements. International Electrotechnical Commission: Geneva, Switzerland, 2015.

- Jayasree, P.; Priya, J.; Poojita, G.; Kameshwari, G. EMI Filter Design for Reducing Common-Mode and Differential-Mode Noise in Conducted Interference. Int. J. Electron. Commun. Eng. 2012, 5, 319–329. [Google Scholar]

- Tarateeraseth, V.; See, K.Y.; Wang, L.B.; Canavero, F.G. Systematic power line EMI filter design for SMPS. In Proceedings of the 10th International Symposium on Electromagnetic Compatibility, York, UK, 26–30 September 2011. [Google Scholar]

- Biela, J.; Wirthmueller, A.; Waespe, R.; Heldwein, M.L.; Raggl, K.; Kolar, J.W. Passive and Active Hybrid Integrated EMI Filters. IEEE Trans. Power Electron. 2009, 24, 1340–1349. [Google Scholar] [CrossRef]

- Zamazal, M.; Urbanec, T. Variable impedance in measuring EMI filter’s insertion loss. In Proceedings of the 2005 Asia-Pacific Conference on Communications, Perth, WA, Australia, 3–5 October 2005; pp. 24–27. [Google Scholar]

- Pérez, A.; Sánchez, A.-M.; Regué, J.; Ribó, M.; Rodríguez-Cepeda, P.; Pajares, F. Characterization of Power-Line Filters and Electronic Equipment for Prediction of Conducted Emissions. IEEE Trans. Electromagn. Compat. 2008, 50, 577–585. [Google Scholar] [CrossRef]

- Pérez, A.; Sanchez, A.M.; Regue, J.R.; Ribó, M.; Aquilué, R.; Rodriguez-Cepeda, P.; Pajares, F.J. Circuital and Modal Characterization of the Power-Line Network in the PLC Band. IEEE Trans. Power Deliv. 2009, 24, 1182–1189. [Google Scholar] [CrossRef]

- Sánchez, A.-M.; Pignari, S.A.; Regué, J.-R.; Ribó, M. Device Modeling for Nonstationary Conducted Emissions Based on Frequency- and Time-Domain Measurements. IEEE Trans. Electromagn. Compat. 2012, 54, 738–746. [Google Scholar] [CrossRef]

- Sánchez, A.; Regué, J.; Ribó, M.; Pérez, A.; Rodríguez-Cepeda, P.; Pajares, F. Automated Power-Line Filter Design under High 50-Hz Current Load Conditions. IEEE Trans. Electromagn. Compat. 2013, 55, 717–724. [Google Scholar] [CrossRef]

- Negri, S.; Spadacini, G.; Grassi, F.; Pignari, S.A. Prediction of EMI Filter Attenuation in Power-Electronic Converters via Circuit Simulation. IEEE Trans. Electromagn. Compat. 2022, 64, 1086–1096. [Google Scholar] [CrossRef]

- CISPR 17:2011; Methods of Measurement of the Suppression Characteristics of Passive EMC Filtering Devices. International Electrotechnical Commission: Geneva, Switzerland, 2011.

- Munir, H.A.; Jenu, M.Z.M.; Abdullah, M.F.L. Analysis and design of EMI filters to mitigate conducted emissions. In Proceedings of the Student Conference on Research and Development, Shah Alam, Malaysia, 17 July 2002; pp. 204–207. [Google Scholar] [CrossRef]

- Nussbaumer, T.; Heldwein, M.L.; Kolar, J.W. Common mode EMC input filter design for a three-phase buck-type PWM rectifier system. In Proceedings of the Twenty-First Annual IEEE Applied Power Electronics Conference and Exposition, Dallas, TX, USA, 19–23 March 2006; p. 7. [Google Scholar] [CrossRef]

- Luo, F.; Dong, D.; Boroyevich, D.; Mattavelli, P.; Wang, S. Improving high-frequency performance of an input common mode EMI filter using an impedance-mismatching filter. IEEE Trans. Power Electron. 2014, 29, 5111–5115. [Google Scholar] [CrossRef]

- Kotny, J.L.; Duquesne, T.; Idir, N. EMI Filter design using high frequency models of the passive components. In Proceedings of the IEEE Workshop on Signal Propagation on Interconnects (SPI 2011), Naples, Italy, 8–11 May 2011. [Google Scholar]

- Narayanasamy, B.; Jalanbo, H.; Luo, F. Development of Software to Design Passive Filters for EMI Suppression in SiC DC Fed Motor Drives. In Proceedings of the IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA 2015), Blacksburg, VA, USA, 2–4 November 2015; pp. 230–235. [Google Scholar]

- Zhang, D.; Fan, T.; Ning, P.; Wen, X. An automatic EMI filter design methodology for electric vehicle application. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017; pp. 4497–4503. [Google Scholar] [CrossRef]

- Wang, F.; Shen, W.; Boroyevich, D.; Ragon, S.; Stefanovic, V.; Arpilliere, M. Design Optimization of Industrial Motor Drive Power Stage Using Genetic Algorithms. In Proceedings of the IEEE Industry Applications Conference, Tampa, FL, USA, 8–12 October 2006; pp. 2581–2586. [Google Scholar]

- Giglia, G.; Ala, G.; Di Piazza, M.C.; Giaconia, G.C.; Luna, M.; Vitale, G.; Zanchetta, P. Automatic EMI Filter Design for Power Electronic Converters Oriented to High Power Density. Electronics 2018, 7, 9. [Google Scholar] [CrossRef] [Green Version]

- Danilovic, M.; Luo, F.; Xue, L.; Wang, R.; Mattavelli, P.; Boroyevich, D. Size and weight dependence of the single stage input EMI filter on switching frequency for low voltage bus aircraft applications. In Proceedings of the 15th International Power Electronics and Motion Control Conference (PEMC 2012), Novi Sad, Serbia, 4–6 September 2012; pp. LS4a.41–LS4a.47. [Google Scholar]

- Raggl, K.; Nussbaumer, T.; Kolar, J.W. Guideline for a Simplified Differential-Mode EMI Filter Design. IEEE Trans. Ind. Electron. 2010, 57, 1031–1040. [Google Scholar] [CrossRef]

- Ala, G.; Di Piazza, M.C.; Giaconia, G.C.; Giglia, G.; Luna, M.; Vitale, G.; Zanchetta, P. Computer Aided Optimal Design of High Power Density EMI Filters. In Proceedings of the IEEE 16th International Conference on Environment and Electrical Engineering (EEEIC 2016), Florence, Italy, 7–10 June 2016; pp. 1–6. [Google Scholar]

- Wang, S.; Lee, F.C.; Odendaal, W.G. Characterization and parasitic extraction of EMI filters using scattering parameters. IEEE Trans. Power Electron. 2005, 20, 502–510. [Google Scholar] [CrossRef]

- Wang, S.; Lee, F.C.; Chen, D.Y.; Odendaal, W.G. Effects of parasitic parameters on the performance of EMI filters. IEEE Trans. Power Electron. 2004, 19, 869–877. [Google Scholar] [CrossRef]

- Luo, F.; Boroyevich, D.; Mattavelli, P. Improving EMI filter design within circuit impedance mismatching. In Proceedings of the 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 5–9 February 2012; pp. 1652–1658. [Google Scholar] [CrossRef]

- Kovacic, M.; Hanic, Z.; Stipetic, S.; Krishnamurthy, S.; Zarko, D. Analytical Wideband Model of a Common-Mode Choke. IEEE Trans. Power Electron. 2012, 27, 3173–3185. [Google Scholar] [CrossRef]

- Nave, M.J. On Modeling the Common Mode Inductor. In Proceedings of the IEEE 1991 International Symposium on Electromagnetic Compatibility, Cherry Hill, NJ, USA, 12 July–16 August 1991. [Google Scholar]

- IHernandez, I.; de Leon, F.; Gomez, P. Design Formulas for the Leakage Inductance of Toroidal Distribution Transformers. IEEE Trans. Power Deliv. 2011, 26, 2197–2204. [Google Scholar] [CrossRef]

- Ren, R.; Dong, Z.; Liu, B.; Wang, F. Leakage Inductance Estimation of Toroidal Common-mode Choke from Perspective of Analogy between Reluctances and Capacitances. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition, New Orleans, LA, USA, 15–19 March 2020; pp. 2822–2828. [Google Scholar] [CrossRef]

- Shih, F.-Y.; Chen, D.; Wu, Y.-P.; Chen, Y.-T. A procedure for designing EMI filters for AC line applications. IEEE Trans. Power Electron. 1996, 11, 170–181. [Google Scholar] [CrossRef]

- Lai, Y.-S.; Chen, P.-S. New EMI Filter Design Method for Single Phase Power Converter Using Software-Based Noise Separation Method. In Proceedings of the 2007 IEEE Industry Applications Annual Meeting, New Orleans, LA, USA, 23–27 September 2007; pp. 2282–2288. [Google Scholar] [CrossRef]

- Xu, D.; Gao, Q.; Wang, W. Design of a Passive Filter to Reduce Common-Mode and Differential-Mode Voltage Generated by Voltage-Source PWM Inverter. In Proceedings of the IECON 2006—32nd Annual Conference on IEEE Industrial Electronics, Paris, France, 6–10 November 2006; pp. 2483–2487. [Google Scholar] [CrossRef]

- Caponet, M.C.; Profumo, F.; Tenconi, A. EMI filters design for power electronics. In Proceedings of the 2002 IEEE 33rd Annual IEEE Power Electronics Specialists Conference. Proceedings (Cat. No.02CH37289), Cairns, QLD, Australia, 23–27 June 2002; Volume 4, pp. 2027–2032. [Google Scholar] [CrossRef]

- Bertoldi, B.; Junior, M.M.B.; Dall’Asta, M.S.; Greidanus, M.D.R. Modeling of SEPIC Converter with Non-Ideal Components in Continuous and Discontinuous Conduction Mode. In 2018 4th IEEE Southern Power Electronics Conference; IEEE: Piscataway, NJ, USA, 2018. [Google Scholar]

- Faifer, M.; Piegari, L.; Rossi, M.; Toscani, S. An Average Model of DC–DC Step-Up Converter Considering Switching Losses and Parasitic Elements. Energies 2021, 14, 7780. [Google Scholar] [CrossRef]

- Abid, R.; Masmoudi, F.; Ben Salem, F.; Derbel, N. Modeling and simulation of conventional DC-DC converters deticated to photovoltaic applications. In Proceedings of the 2016 7th International Renewable Energy Congress (IREC), Hammamet, Tunisia, 22–24 March 2016; pp. 1–6. [Google Scholar]

- Chander, S.; Agarwal, P.; Gupta, I. Design, modeling and simulation of DC-DC converter. In Proceedings of the 2010 Conference Proceedings IPEC, Singapore, 27–29 October 2010; pp. 456–461. [Google Scholar]

- CISPR 16-2-1:2014+AMD1:2017; Specification for Radio Disturbance and Immunity Measuring Apparatus and Methods—Part 2-1: Methods of Measurement of Disturbances and Immunity—Conducted Disturbance Measurements. International Electrotechnical Commission: Geneva, Switzerland, 2017.

- Bosi, M.; Sanchez, A.-M.; Pajares, F.; Garcia, I.; Accensi, J.; Regue, J. Common- and Differential-Mode Conducted Emissions Measurements using Conventional Receivers versus FFT-Based Receivers. IEEE Electromagn. Compat. Mag. 2022, 11, 55–63. [Google Scholar] [CrossRef]

| Symbol | Description | Value |

|---|---|---|

| CPAR | Parasitic capacitance | 14 pF |

| Lpar1 | Parasitic inductance | 56 nH |

| Lpar2 | Parasitic inductance | 1 nH |

| rS, rD, rC, rL | Parasitic resistances | 200 mΩ |

| Symbol | Description | Value |

|---|---|---|

| CPAR | Parasitic capacitance | 10 pF |

| Lpar1 | Parasitic inductance | 199 nH |

| Lpar2 | Parasitic inductance | 199 nH |

| rS, rD, rC, rL | Parasitic resistances | 200 mΩ |

| Symbol | Description | Value |

|---|---|---|

| CPAR | Parasitic capacitance | 21 pF |

| Lpar1 | Parasitic inductance | 33 nH |

| Lpar2 | Parasitic inductance | 9 nH |

| rS, rD, rC1, rL1, rC2, rL2 | Parasitic resistances | 200 mΩ |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bosi, M.; Sánchez, A.-M.; Pajares, F.J.; Campanini, A.; Peretto, L. PLF Design for DC-DC Converters Based on Accurate IL Estimations. Energies 2023, 16, 2085. https://doi.org/10.3390/en16052085

Bosi M, Sánchez A-M, Pajares FJ, Campanini A, Peretto L. PLF Design for DC-DC Converters Based on Accurate IL Estimations. Energies. 2023; 16(5):2085. https://doi.org/10.3390/en16052085

Chicago/Turabian StyleBosi, Marco, Albert-Miquel Sánchez, Francisco Javier Pajares, Alessandro Campanini, and Lorenzo Peretto. 2023. "PLF Design for DC-DC Converters Based on Accurate IL Estimations" Energies 16, no. 5: 2085. https://doi.org/10.3390/en16052085