An Improved Cascaded Boost Converter with an Ultra-High Voltage Gain Suitable for Dielectric Quality Tests

Abstract

1. Introduction

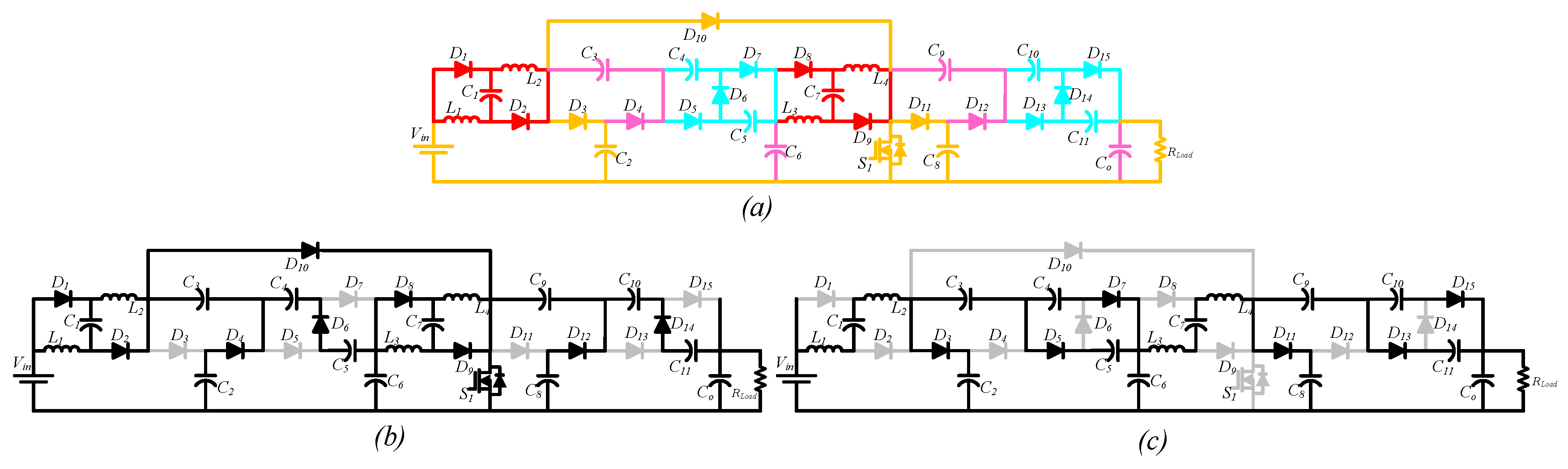

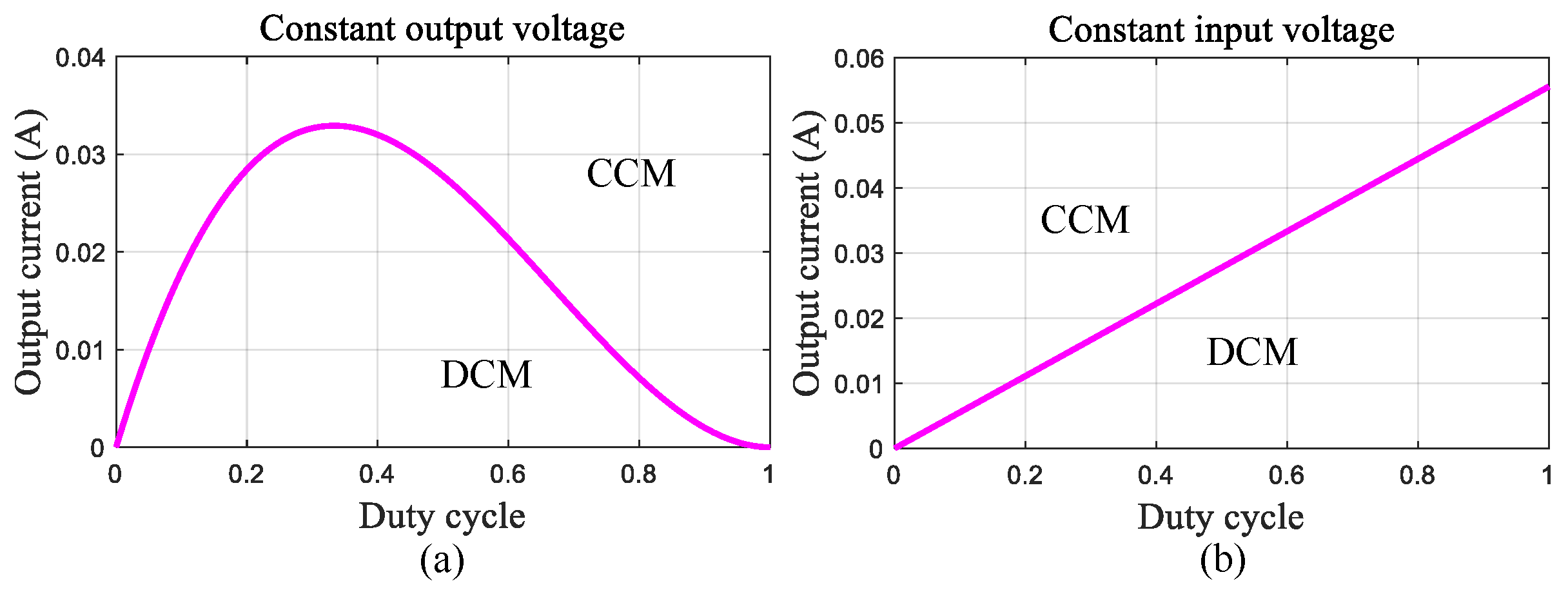

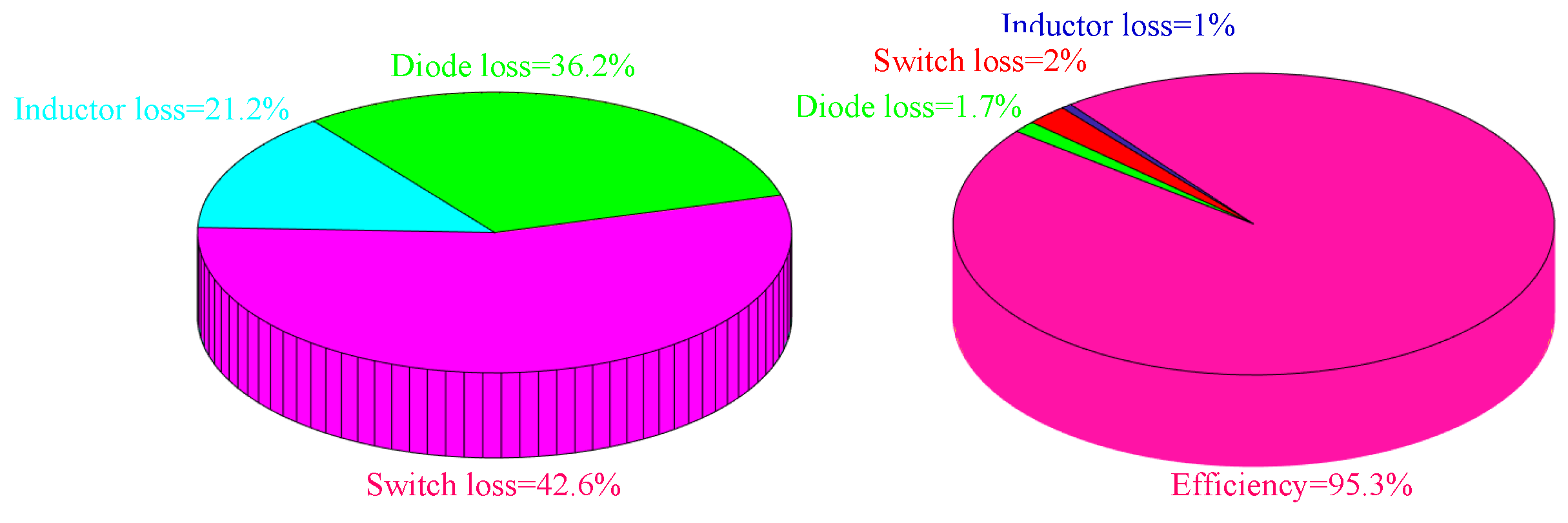

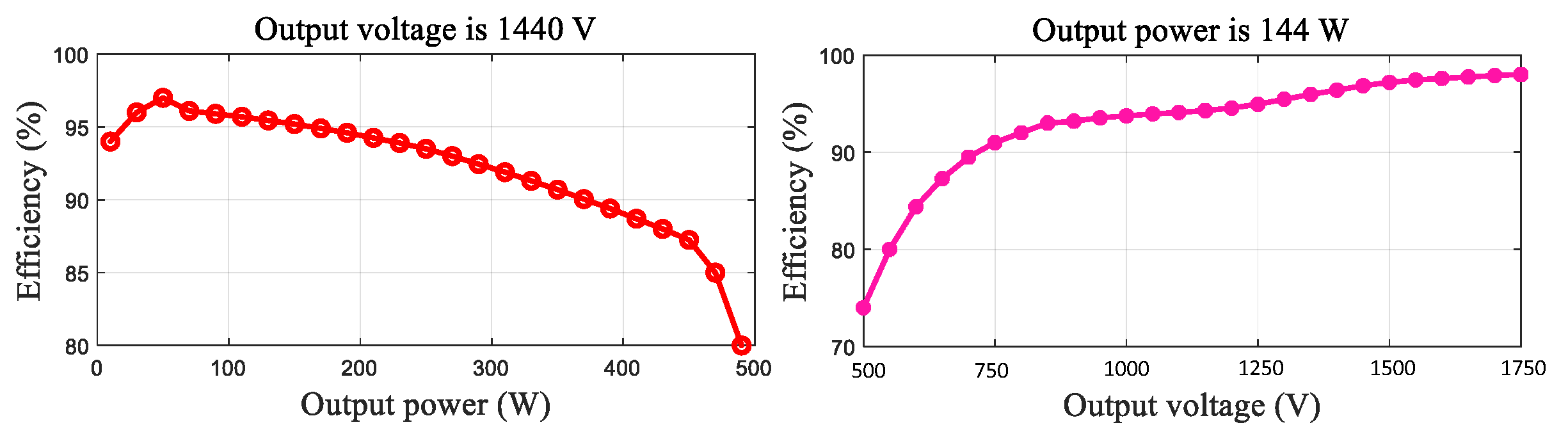

2. Proposed Topology in the Ideal Mode

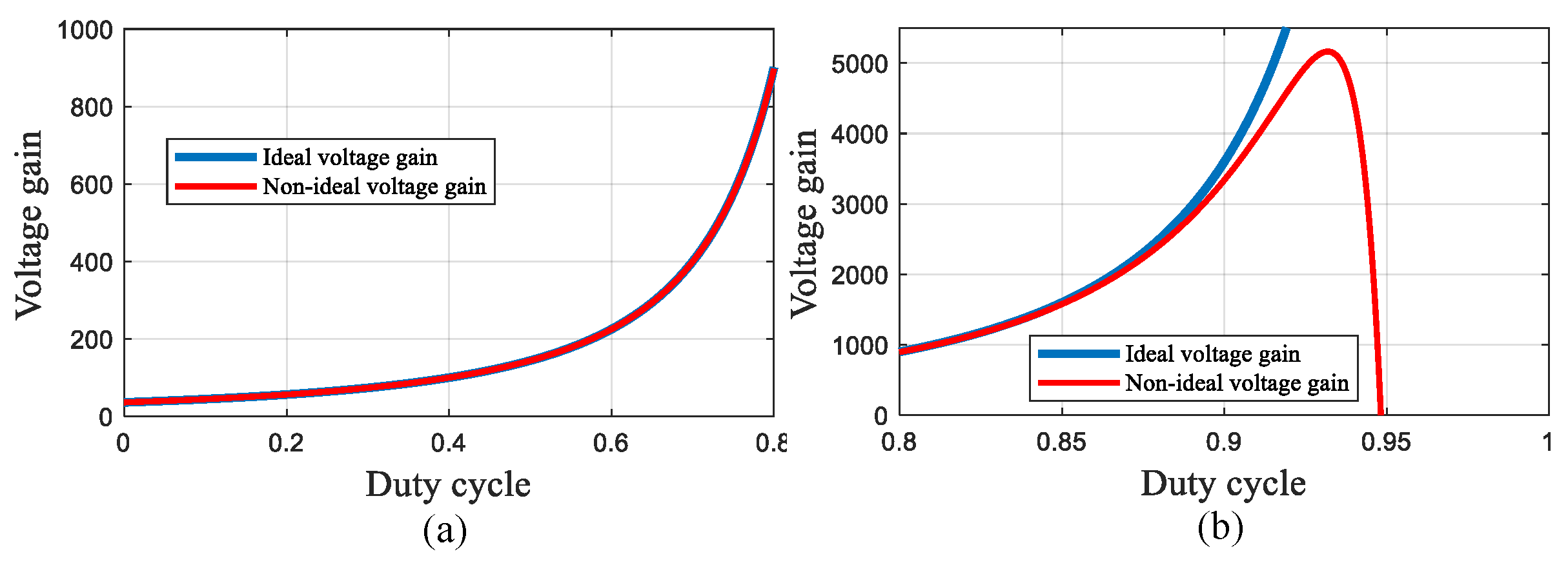

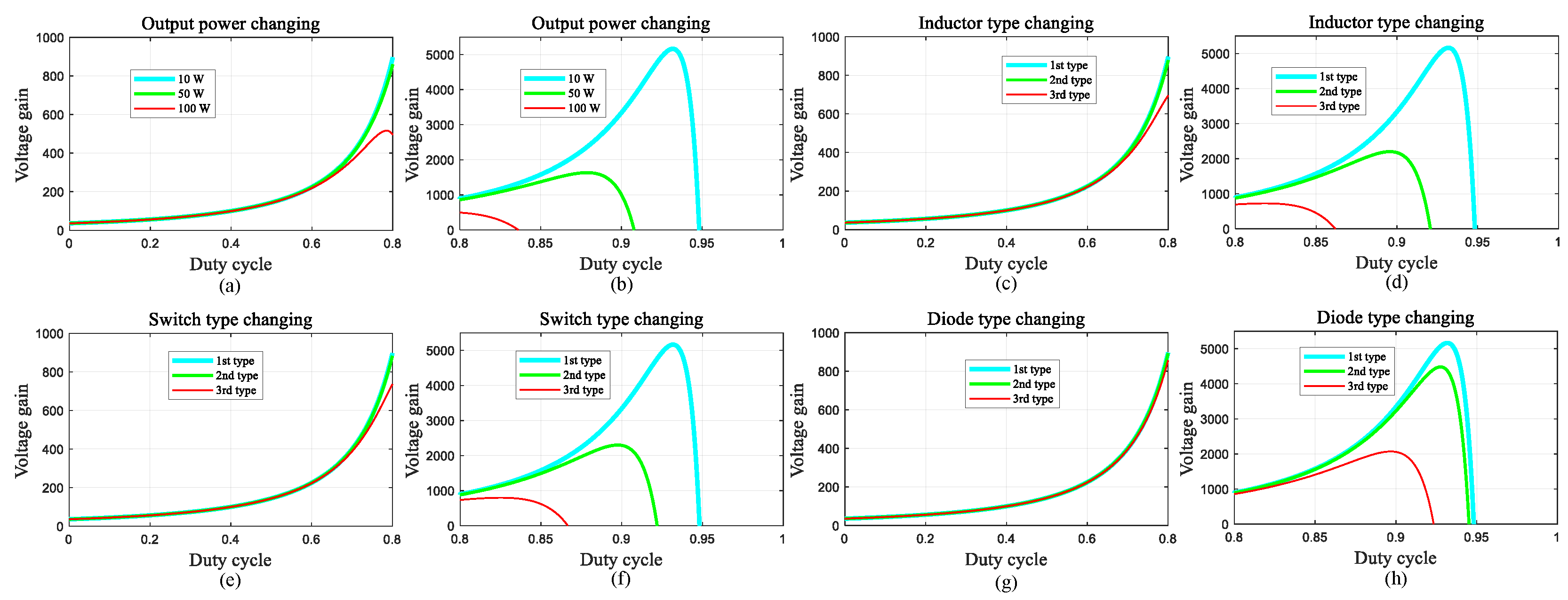

3. Non-Ideal Voltage Gain and Efficiency

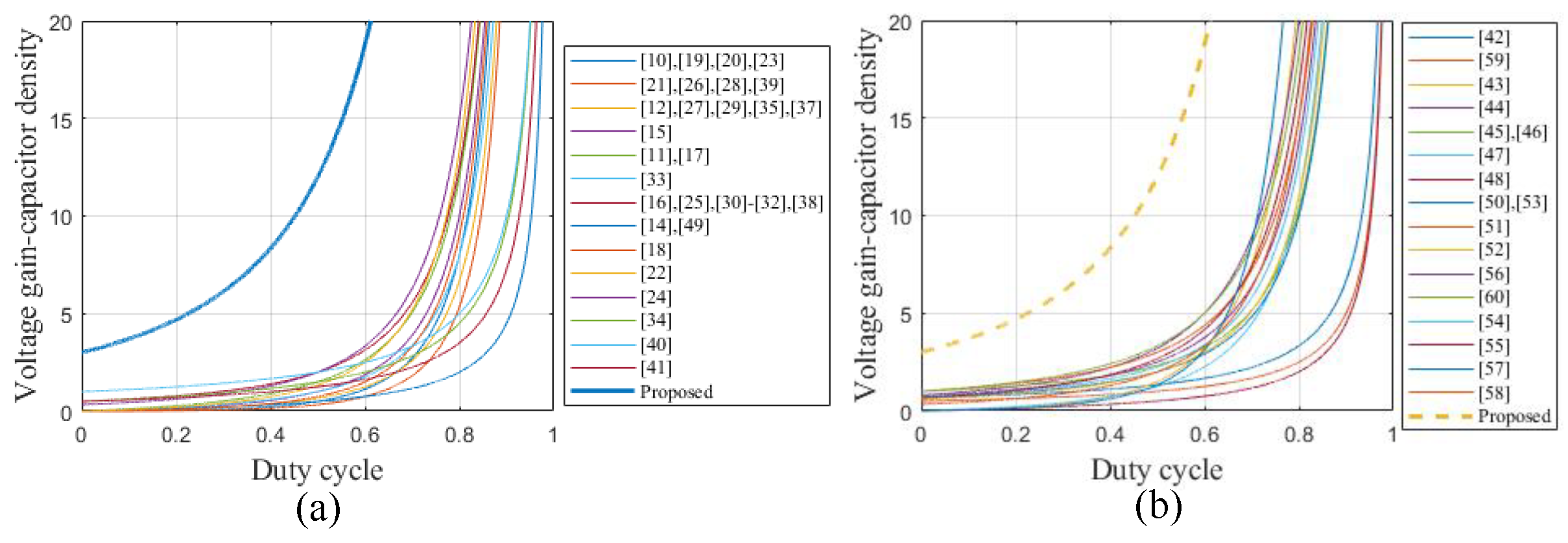

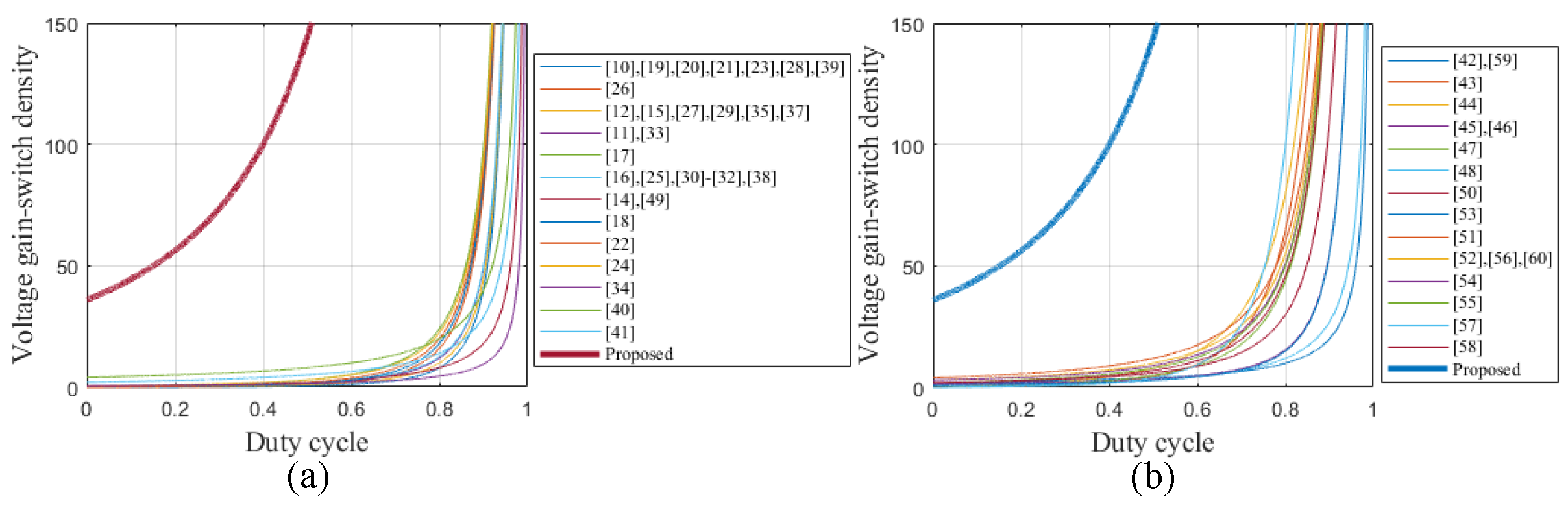

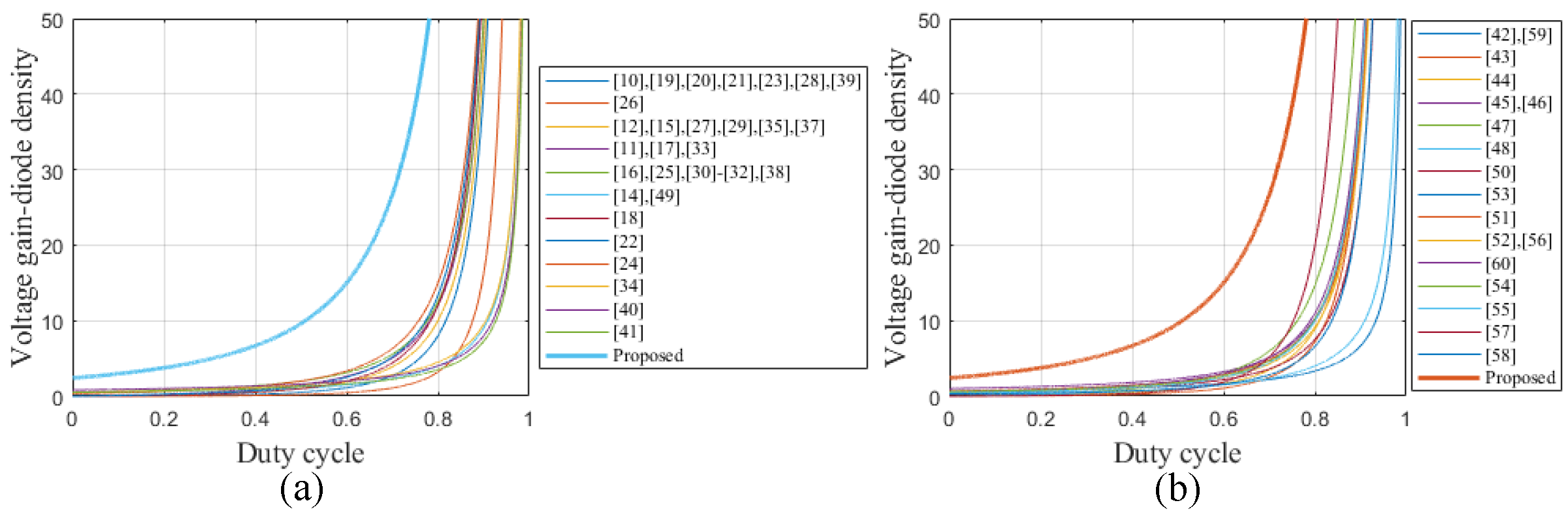

4. Voltage Gain and Voltage Gain Density Comparison of the Proposed Topology with Other High-Gain Topologies

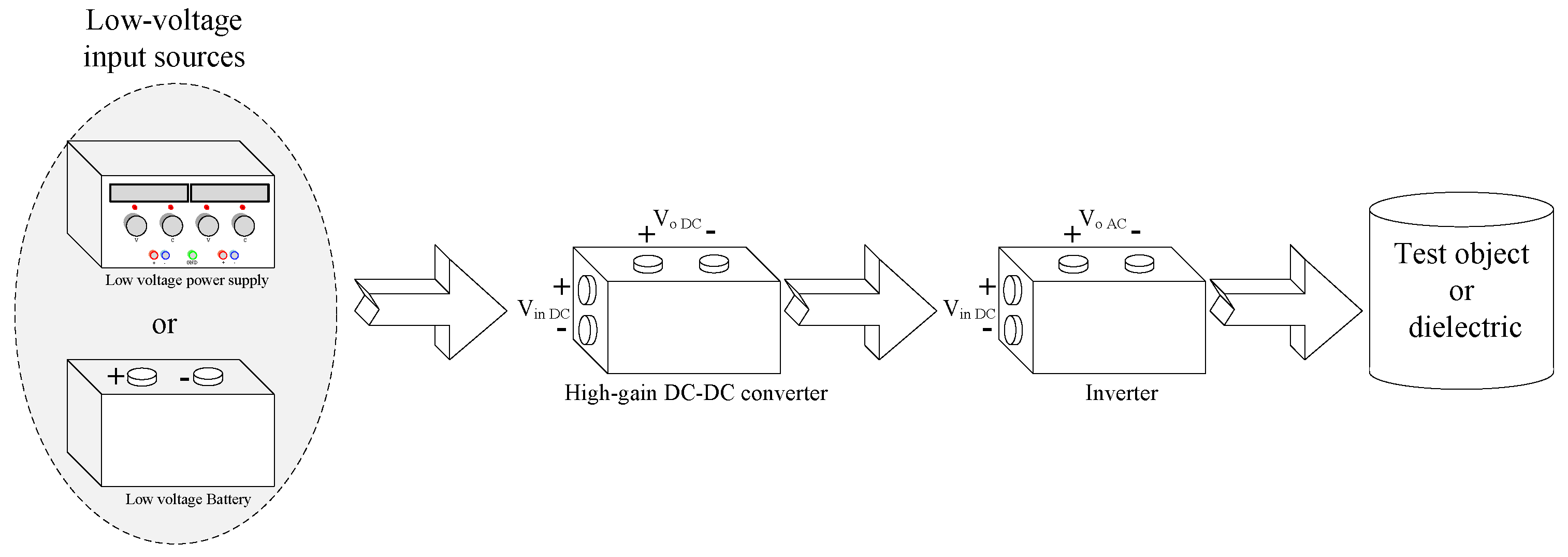

5. Application of the Proposed Topology

6. Experimental Results

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Mohammadi, F.; Gharehpetian, G.B.; Rastegar, H.; Farhadi-Kangarlu, M. Non-isolated Step-up DC-DC Converter Based on Switched Capacitor Cells. CSEE J. Power Energy Syst. 2023, 9, 1161–1172. [Google Scholar] [CrossRef]

- Forouzesh, M.; Siwakoti, Y.P.; Gorji, S.A.; Blaabjerg, F.; Lehman, B. Step-Up DC–DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications. IEEE Trans. Power Electron. 2017, 32, 9143–9178. [Google Scholar] [CrossRef]

- Hakemibarabadi, A.; Gorji, S.A.; Sera, D.; Walker, G. DZ-Source Converter: A Duality Inspiration of Z-Source Converter for Current-Source High-Conversion Ratio Applications. In Proceedings of the 2022 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 9–13 October 2022; pp. 1–4. [Google Scholar] [CrossRef]

- Imanlou, A.; Seifi Najmi, E.; Babaei, E. A new high voltage gain DC-DC converter based on active switched-inductor technique. Int. J. Circuit Theory Appl. 2024, 52, 634–657. [Google Scholar] [CrossRef]

- Hasanpour, S.; Nouri, T.; Shaneh, M. Analysis and Design of a New Ultra-Step-Up DC–DC Converter with Reduced Voltage Stress for Renewable Energy Systems Applications. Iran J. Sci. Technol. Trans. Electr. Eng. 2023, 48, 817–830. [Google Scholar] [CrossRef]

- Hasanpour, S.; Lee, S.S. New Step-Up DC/DC Converter with Ripple-Free Input Current. IEEE Trans. Power Electron. 2024, 39, 2811–2821. [Google Scholar] [CrossRef]

- Hasanpour, S.; Lee, S.S. A New Quadratic DC/DC Converter with Ultra-High Voltage Gain. IEEE Trans. Power Electron. 2024, 39, 8800–8812. [Google Scholar] [CrossRef]

- Sun, D.; Ge, B.; Yan, X.; Bi, D.; Zhang, H.; Liu, Y.; Abu-Rub, H.; Ben-Brahim, L.; Peng, F.Z. Modeling, Impedance Design, and Efficiency Analysis of Quasi- Z Source Module in Cascaded Multilevel Photovoltaic Power System. IEEE Trans. Ind. Electron. 2014, 61, 6108–6117. [Google Scholar] [CrossRef]

- Mizani, A.; Shoushtari, M.; Shoulaie, A. A Novel Quadratic High Step-up DC-DC converter. In Proceedings of the 2020 11th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 4–6 February 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Miao, S.; Wang, F.; Ma, X. A New Transformerless Buck–Boost Converter with Positive Output Voltage. IEEE Trans. Ind. Electron. 2016, 63, 2965–2975. [Google Scholar] [CrossRef]

- Ding, S.; Wang, F. A New Negative Output Buck–Boost Converter with Wide Conversion Ratio. IEEE Trans. Ind. Electron. 2017, 64, 9322–9333. [Google Scholar] [CrossRef]

- Maroti, P.K.; Padmanaban, S.; Wheeler, P.; Blaabjerg, F.; Rivera, M. Modified high voltage conversion inverting cuk DC-DC converter for renewable energy application. In Proceedings of the 2017 IEEE Southern Power Electronics Conference (SPEC), Puerto Varas, Chile, 4–7 December 2017; pp. 1–5. [Google Scholar] [CrossRef]

- Valdez-Resendiz, J.E.; Rosas-Caro, J.C.; Mayo-Maldonado, J.C.; Llamas-Terres, A. Quadratic boost converter based on stackable switching stages. IET Power Electron. 2018, 11, 1373–1381. [Google Scholar] [CrossRef]

- Ahmadi, M.; Hosseinpour, M.; Mousavi-Aghdam, S.R.; Sedaghati, F. A High Conversion Ratio Transformerless Buck-Boost Converter with Continuous Input Current. In Proceedings of the 2021 12th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tabriz, Iran, 2–4 February 2021; pp. 1–7. [Google Scholar] [CrossRef]

- García-Vite, P.M.; Soriano-Rangel, C.A.; Rosas-Caro, J.C.; Mancilla–David, F. A DC–DC converter with quadratic gain and input current ripple cancelation at a selectable duty cycle. Renew. Energy 2017, 101, 431–436. [Google Scholar] [CrossRef]

- Wang, F. A novel quadratic Boost converter with low current and voltage stress on power switch for fuel-cell system applications. Renew. Energy 2018, 115, 836–845. [Google Scholar] [CrossRef]

- Mostaan, A.; Gorji, S.A.; Soltani, M.N.; Ektesabi, M. A novel single switch transformerless quadratic DC/DC buck-boost converter. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Allahverdinejad, B.; Modaberi, S.A.; Ajami, A. A Non-isolated Buck-Boost DC–DC Converter with Continuous Input Current and Wide Conversion Ratio Range for Photovoltaic Applications. In Proceedings of the 2022 13th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 1–3 February 2022; pp. 491–497. [Google Scholar] [CrossRef]

- Rosas-Caro, J.C.; Sanchez, V.M.; Valdez-Resendiz, J.E.; Mayo-Maldonado, J.C.; Beltran-Carbajal, F.; Valderrabano-Gonzalez, A. Quadratic buck-boost converter with positive output-voltage and continuous input-current. In Proceedings of the 2018 International Conference on Electronics, Communications and Computers (CONIELECOMP), Cholula, Mexico, 21–23 February 2018; pp. 152–158. [Google Scholar] [CrossRef]

- Rosas-Caro, J.C.; Valdez-Resendiz, J.E.; Mayo-Maldonado, J.C.; Alejo-Reyes, A.; Valderrabano-Gonzalez, A. Quadratic buck–boost converter with positive output voltage and minimum ripple point design. IET Power Electron. 2018, 11, 1306–1313. [Google Scholar] [CrossRef]

- Sarikhani, A.; Allahverdinejad, B.; Hamzeh, M.; Afjei, E. A continuous input and output current quadratic buck-boost converter with positive output voltage for photovoltaic applications. Sol. Energy 2019, 188, 19–27. [Google Scholar] [CrossRef]

- Sarikhani, A.; Allahverdinejad, B.; Hamzeh, M. A Nonisolated Buck–Boost DC–DC Converter with Continuous Input Current for Photovoltaic Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 804–811. [Google Scholar] [CrossRef]

- Loera-Palomo, R.; Morales-Saldaña, J.A.; Rivero, M.; Álvarez-Macías, C.; Hernández-Jacobo, C.A. Noncascading Quadratic Buck-Boost Converter for Photovoltaic Applications. Micromachines 2021, 12, 984. [Google Scholar] [CrossRef] [PubMed]

- Naresh, S.V.K.; Peddapati, S.; Alghaythi, M.L. Non-Isolated High Gain Quadratic Boost Converter Based on Inductor’s Asymmetric Input Voltage. IEEE Access 2021, 9, 162108–162121. [Google Scholar] [CrossRef]

- Gupta, N.; Bhaskar, M.S.; Almakhles, D.; Sanjeevikumar, P.; Blaabjerg, F.; Leonowicz, Z. Two-Tier Converter: A New Structure of High Gain DC-DC Converter with Reduced Voltage Stress. In Proceedings of the 2020 IEEE International Conference on Environment and Electrical Engineering and 2020 IEEE Industrial and Commercial Power Systems Europe (EEEIC/I&CPS Europe), Madrid, Spain, 9–12 June 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Zhang, N.; Zhang, G.; See, K.W.; Zhang, B. A Single-Switch Quadratic Buck–Boost Converter with Continuous Input Port Current and Continuous Output Port Current. IEEE Trans. Power Electron. 2018, 33, 4157–4166. [Google Scholar] [CrossRef]

- Maroti, P.K.; Padmanaban, S.; Holm-Nielsen, J.B.; Bhaskar, M.S.; Meraj, M.; Iqbal, A. A New Structure of High Voltage Gain SEPIC Converter for Renewable Energy Applications. IEEE Access 2019, 7, 89857–89868. [Google Scholar] [CrossRef]

- Gholizadeh, H.; Salehi, M.; Rafiee, Z.; Afjei, E.; Hamzeh, M. A Transformer less Quadratic Buck-Boost Converter with Wide Range of Output Voltage and Low Switch Stresses. In Proceedings of the 2020 11th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 4–6 February 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Gholizadeh, H.; Aboufazeli, S.; Rafiee, Z.; Afjei, E.; Hamzeh, M. A Non-Isolated High Gain DC-DC Converters with Positive Output Voltage and Reduced Current Stresses. In Proceedings of the 2020 11th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 4–6 February 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Golizedeh, H.; Hashemi, M.R.; Rafiee, Z.; Hamzeh, M.; Afjei, E. A Quadratic Boost Converter with Continuous Input Current and Suitable for Photo Voltaic Solar Panels. In Proceedings of the 2020 28th Iranian Conference on Electrical Engineering (ICEE), Tabriz, Iran, 4–6 August 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Afjei, E.; Siadatan, A.; Rezaei-Zare, A.; Gholizadeh, H. A Quadratic Boost Converter with Continuous Input Current and Low Normalized Voltage/Current Stresses. In Proceedings of the 2022 International Symposium on Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM), Sorrento, Italy, 22–24 June 2022; pp. 395–401. [Google Scholar] [CrossRef]

- Sharifi Shahrivar, R.; Gholizadeh, H.; Siadatan, A.; Afjei, S.E. Design and Implementation of a Modified Boost Topology with High Voltage Ratio and Efficiency Besides the Lower Semiconductors Stresses. Res. Technol. Electr. Ind. 2022, 1, 75–84. [Google Scholar] [CrossRef]

- Gholizadeh, H.; Gorji, S.A.; Afjei, E.; Sera, D. Design and Implementation of a New Cuk-Based Step-Up DC–DC Converter. Energies 2021, 14, 6975. [Google Scholar] [CrossRef]

- Rahimi, T.; Islam, M.R.; Gholizadeh, H.; Mahdizadeh, S.; Afjei, E. Design and Implementation of a High Step-Up DC-DC Converter Based on the Conventional Boost and Buck-Boost Converters with High Value of the Efficiency Suitable for Renewable Application. Sustainability 2021, 13, 10699. [Google Scholar] [CrossRef]

- Totonchi, N.; Gholizadeh, H.; Afjei, E.; Hamzeh, M. A Novel Transformer less High Gain DC-DC Converter with Continuous Input Current and Suitable for Photo Voltaic Panels. In Proceedings of the 2020 11th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 4–6 February 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Marzoni, A.T.; Amini, S.; Gholizadeh, H.; Kalamialhashem, S.M.; Afjei, E. A Quadratic DC-DC converter with Continuous Input Current And Selectable Duty Cycle to Provide A Zero Current Switching of Switch Suitable for renewable Applications. In Proceedings of the 2022 9th Iranian Conference on Renewable Energy and Distributed Generation (ICREDG), Mashhad, Iran, 23–24 February 2022; pp. 1–5. [Google Scholar] [CrossRef]

- Monfared, M.T.; Gholizadeh, H.; Amini, S.; Kalamialhashem, S.M.; Afjei, S.A.A.; Afjei, S.E. A Modified Zeta DC-DC Converter with Higher Voltage Gain Besides Low Value of the Normalized Current Stresses. In Proceedings of the 2022 13th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 1–3 February 2022; pp. 269–274. [Google Scholar] [CrossRef]

- Monfared, M.T.; Gholizadeh, H.; Ben-Brahim, L. New Enhanced Family of QBC Topologies: Mitigating Capacitor Stress and Increasing Voltage Gain. In Proceedings of the 2024 IEEE 8th Energy Conference (ENERGYCON), Doha, Qatar, 4–7 March 2024; pp. 1–6. [Google Scholar] [CrossRef]

- Gholizadeh, H.; Gorji, S.A.; Sera, D. A Quadratic Buck-Boost Converter with Continuous Input and Output Currents. IEEE Access 2023, 11, 22376–22393. [Google Scholar] [CrossRef]

- Banaei, M.R.; Ajdar Faeghi Bonab, H. High-efficiency transformerless buck–boost DC–DC converter. Int. J. Circuit Theory Appl. 2017, 45, 1129–1150. [Google Scholar] [CrossRef]

- Shokri, G.; Naderi, E.; SeyedShenava, S. Active and Reactive Power Control of Grid-Connected PV Power Systems based on HGNISS DC-DC Converter and SMDPC Strategy. In Proceedings of the 2020 11th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 4–6 February 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Ghabeli Sani, S.; Mohammadi, F.; Banaei, M.R.; Farhadi-Kangarlu, M. Design and implementation of a new high step-up DC-DC converter for renewable applications. Int. J. Circuit Theory Appl. 2019, 47, 464–482. [Google Scholar] [CrossRef]

- Amir, A.; Che, H.S.; Amir, A.; Khateb, A.E.; Rahim, N.A. Transformerless high gain boost and buck-boost DC-DC converters based on extendable switched capacitor (SC) cell for stand-alone photovoltaic system. Sol. Energy 2018, 171, 212–222. [Google Scholar] [CrossRef]

- Sanjeevikumar, P.; Maroti, P.K.; Blaabjerg, F.; Holm-Nielsen, J.B.; Ionel, D.M.; He, J. Modified CUK Converter with Two Switched Inductor Module Configurations for Photovoltaic Application: Part-II. In Proceedings of the 2020 IEEE International Conference on Environment and Electrical Engineering and 2020 IEEE Industrial and Commercial Power Systems Europe (EEEIC / I&CPS Europe), Madrid, Spain, 9–12 June 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Maroti, P.K.; Al-Ammari, R.; Iqbal, A.; Ben-Brahim, L.; Padmanaban, S.; Abu-Rub, H. A Novel High Gain Configurations of Modified SEPIC Converter for Renewable Energy Applications. In Proceedings of the 2019 IEEE 28th International Symposium on Industrial Electronics (ISIE), Vancouver, BC, Canada, 12–14 June 2019; pp. 2503–2508. [Google Scholar] [CrossRef]

- Lee, S.S.; Chu, B.; Lim, C.S.; Lee, K.B. Two-Inductor Non-Isolated DC-DC Converter with High Step-Up Voltage Gain. J. Power Electron. 2019, 19, 1069–1073. [Google Scholar] [CrossRef]

- Varesi, K.; Hassanpour, N.; Saeidabadi, S. Novel high step-up DC–DC converter with increased voltage gain per devices and continuous input current suitable for DC microgrid applications. Int. J. Circuit Theory Appl. 2020, 48, 1820–1837. [Google Scholar] [CrossRef]

- Hosseinpour, M.; Ahmadi, M.; Seifi, A.; Mousavi-Aghdam, S.R. A new transformerless semi-quadratic buck–boost converter based on combination of Cuk and traditional buck–boost converters. Int. J. Circuit Theory Appl. 2022, 50, 3926–3948. [Google Scholar] [CrossRef]

- Banaei, M.R.; Sani, S.G. Analysis and Implementation of a New SEPIC-Based Single-Switch Buck–Boost DC–DC Converter with Continuous Input Current. IEEE Trans. Power Electron. 2018, 33, 10317–10325. [Google Scholar] [CrossRef]

- Gholizadeh, H.; Sharifi Shahrivar, R.; Hashemi, M.R.; Afjei, E.; A. Gorji, S. Design and Implementation a Single-Switch Step-Up DC-DC Converter Based on Cascaded Boost and Luo Converters. Energies 2021, 14, 3584. [Google Scholar] [CrossRef]

- Mahdizadeh, S.; Gholizadeh, H.; Shahrivar, R.; Afjei, E.; Mosallanejad, A. An ultra high step-up DC-DC converter based on VMC, POSLLC, and boost converter. IET Power Electron. 2022, 15, 901–918. [Google Scholar] [CrossRef]

- Rahimi, T.; Ding, L.; Gholizadeh, H.; Shahrivar, R.S.; Faraji, R. An Ultra High Step-Up DC–DC Converter Based on the Boost, Luo, and Voltage Doubler Structure: Mathematical Expression, Simulation, and Experimental. IEEE Access 2021, 9, 132011–132024. [Google Scholar] [CrossRef]

- Mahdizadeh, S.; Gholizadeh, H.; Gorji, S.A. A Power Converter Based on the Combination of Cuk and Positive Output Super Lift Lou Converters: Circuit Analysis, Simulation and Experimental Validation. IEEE Access 2022, 10, 52899–52911. [Google Scholar] [CrossRef]

- Totonchi, N.; Gholizadeh, H.; Mahdizadeh, S.; Afjei, E. A High Step up DC-DC Converter Based on the Cascade Boost, Voltage Multiplier Cell and Self Lift Luo Converter. In Proceedings of the 2020 10th Smart Grid Conference (SGC), Kashan, Iran, 16–17 December 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Totonchi, N.; Gholizadeh, H.; Afjei, E. A Transformer-less Double Quadratic Boost Converter with Positive Output Polarity and Non Zero Input Current. In Proceedings of the 2020 28th Iranian Conference on Electrical Engineering (ICEE), Tabriz, Iran, 4–6 August 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Gholizadeh, H.; Ben-Brahim, L. A New Non-Isolated High-Gain Single-Switch DC-DC Converter Topology with a Continuous Input Current. Electronics 2022, 11, 2900. [Google Scholar] [CrossRef]

- Monfared, M.T.; Gholizadeh, H.; Kalamialhashem, S.M.; Amini, S.; Afjei, S.A.A.; Afjei, S.E. A Cubic Transformer-less DC-DC Converter with Continuous Input Current: Mathematical model, Simulation, and Experimental. In Proceedings of the 2022 13th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 1–3 February 2022; pp. 19–25. [Google Scholar] [CrossRef]

- Gholizadeh, H.; Ben-Brahim, L. A High-Gain Single-Switch DC-DC Converter Based on Cascaded Boost and Voltage Lift Technique. In Proceedings of the 2024 IEEE 8th Energy Conference (ENERGYCON), Doha, Qatar, 4–7 March 2024; pp. 1–6. [Google Scholar] [CrossRef]

- Gorji, S.A.; Gholizadeh, H. A Modified Positive Output Super-Lift Luo DC-DC Converter with Improved Voltage Boost Ability. In Proceedings of the 2022 5th International Conference on Renewable Energy and Power Engineering (REPE), Beijing, China, 28–30 September 2022; pp. 282–286. [Google Scholar] [CrossRef]

- Gorji, S.A.; Gholizadeh, H.; Sera, D. A New Non-Isolated High-Gain Single-Switch DC-DC Converter with Continuous Input Current. In Proceedings of the IECON 2023- 49th Annual Conference of the IEEE Industrial Electronics Society, Singapore, 16–19 October 2023; pp. 1–5. [Google Scholar] [CrossRef]

- Alkhaldi, A.; Elkhateb, A.; Laverty, D. Voltage Lifting Techniques for Non-Isolated DC/DC Converters. Electronics 2023, 12, 718. [Google Scholar] [CrossRef]

- Jalilyan, S.; Abbasi, V.; Varmenjeh, A.R.; Ahmadian, S.; Gorji, S.A. High Voltage-Gain Common-Ground Three-Port DC-DC Converter with Low Current Ripples on the PV Source for Standalone Applications. IEEE Access 2024, 12, 80896–80909. [Google Scholar] [CrossRef]

- Gorji, S.A.; Sahebi, H.G.; Movahed, M.; Ektesabi, M. Multi-Input Boost DC-DC Converter with Continuous Input-Output Current for Renewable Energy Systems. In Proceedings of the 2019 IEEE 4th International Future Energy Electronics Conference (IFEEC), Singapore, 25–28 November 2019; pp. 1–5. [Google Scholar] [CrossRef]

- Shaabani, M.; Mirzaei, A.; Rezvanyvardom, M.; Khosravi, F.; Gorji, S.A. A Hybrid Switched-Inductor/Switched-Capacitor DC-DC Converter with High Voltage Gain Using a Single Switch for Photovoltaic Application. Energies 2023, 16, 5524. [Google Scholar] [CrossRef]

- Taghavi, S.S.; Rezvanyvardom, M.; Mirzaei, A.; A. Gorji, S. High Step-Up Three-Level Soft Switching DC-DC Converter for Photovoltaic Generation Systems. Energies 2023, 16, 41. [Google Scholar] [CrossRef]

- Mahdizadeh, A.H.; Kashani, M.; Soltani, M.; Hajizadeh, A.; Gorji, S.A. A Quadratic Boost Converter Suitable for Fuel Cell-Powered Electric Vehicles. In Proceedings of the IECON 2023- 49th Annual Conference of the IEEE Industrial Electronics Society, Singapore, 16–19 October 2023; pp. 1–6. [Google Scholar] [CrossRef]

- Alilou, S.M.; Ahmadi, S.; Maalandish, M.; Hosseini, S.H. A Transformerless Single-Switch DC-DC Boost Converter Suitable for Renewable Energy Applications. In Proceedings of the 2022 30th International Conference on Electrical Engineering (ICEE), Tehran, Iran, 17–19 May 2022; pp. 221–226. [Google Scholar] [CrossRef]

- Azmoon-Asmarood, S.; Maalandish, M.; Shoghli, I.; Nazemi-Oskuee, S.H.R.; Hosseini, S.H. A non-isolated high step-up MIMO DC-DC converter for renewable energy applications. IET Power Electron. 2022, 15, 953–962. [Google Scholar] [CrossRef]

- Maalandish, M.; Hosseini, S.H.; Sabahi, M.; Rostami, N.; Khooban, M.-H. High step-up multi input–multi output DC–DC converter with high controllability for battery charger/EV applications. IET Power Electron. 2023, 16, 2606–2623. [Google Scholar] [CrossRef]

- Radmanesh, H.; Jashnani, H.; Pourjafar, S.; Maalandish, M. A dual-output single-input non-isolated DC-DC converter with reduced semiconductors stress. Int. J. Circuit Theory Appl. 2023, 51, 594–610. [Google Scholar] [CrossRef]

- Hassani, M.Y.; Maalandish, M.; Hosseini, S.H. A New Single-Input Multioutput Interleaved High Step-Up DC–DC Converter for Sustainable Energy Applications. IEEE Trans. Power Electron. 2021, 36, 1544–1552. [Google Scholar] [CrossRef]

- Maalandish, M.; Hosseini, S.H.; Pourjafar, S.; Nouri, S.; Hashemzadeh, S.M.; Marangalu, M.G. A Non-isolated High Step-Up DC-DC Converter Recommended for Photovoltaic Systems. In Proceedings of the 2021 12th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tabriz, Iran, 2–4 February 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Radmanesh, H.; Maalandish, M.; Pourjafar, S. A Non-Isolated High Step-up Two-Input Single Output DC-DC Converter with Less Number of Components. In Proceedings of the 2022 13th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 1–3 February 2022; pp. 574–579. [Google Scholar] [CrossRef]

- Radmanesh, H.; Jashnani, H.; Pourjafar, S.; Maalandish, M. Analyze and Implementation of High Gain DC-DC Topology Recommended for Renewable Power Generation. In Proceedings of the 2022 13th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 1–3 February 2022; pp. 294–299. [Google Scholar] [CrossRef]

- Hassani, M.Y.; Maalandish, M.; Hosseini, S.H. A Single-Switch High Step-Up DC–DC Converter with Low Input Current Ripple for Renewable Energy Applications. In Proceedings of the 2022 13th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 1–3 February 2022; pp. 186–190. [Google Scholar] [CrossRef]

- Shalbaf, A.A.; Shahidi, N.; Hemati, M. A high-gain interleaved DC-DC converter with reduced components for EV charging application. Comput. Electr. Eng. Part A 2024, 118, 109316. [Google Scholar] [CrossRef]

- Mollajafari, M.; Mohammadiazar, F.; Akbari, E.; Sheykhi, E.; Chaoui, H. A New Voltage-Multiplier-Based Power Converter Configuration Suitable for Renewable Energy Sources and Sustainability Applications. Sustainability 2022, 14, 16698. [Google Scholar] [CrossRef]

- Hayat, A.; Sibtain, D.; Murtaza, A.F.; Shahzad, S.; Jajja, M.S.; Kilic, H. Design and Analysis of Input Capacitor in DC–DC Boost Converter for Photovoltaic-Based Systems. Sustainability 2023, 15, 6321. [Google Scholar] [CrossRef]

- Alghaythi, M.L. A Non-Isolated High Voltage Gain DC–DC Converter Suitable for Sustainable Energy Systems. Sustainability 2023, 15, 12058. [Google Scholar] [CrossRef]

- Subbulakshmy, R.; Palanisamy, R.; Alshahrani, S.; Saleel, C.A. Implementation of Non-Isolated High Gain Interleaved DC-DC Converter for Fuel Cell Electric Vehicle Using ANN-Based MPPT Controller. Sustainability 2024, 16, 1335. [Google Scholar] [CrossRef]

- Almalaq, Y.; Matin, M. Three Topologies of a Non-Isolated High Gain Switched-Inductor Switched-Capacitor Step-Up Cuk Converter for Renewable Energy Applications. Electronics 2018, 7, 94. [Google Scholar] [CrossRef]

- Dimitrov, B.; Hayatleh, K.; Barker, S.; Collier, G.; Sharkh, S.; Cruden, A. A Buck-Boost Transformerless DC–DC Converter Based on IGBT Modules for Fast Charge of Electric Vehicles. Electronics 2020, 9, 397. [Google Scholar] [CrossRef]

- Huang, X.; Wang, H.; Zhou, Y.; Zhang, X.; Wang, Y.; Xu, H. Photovoltaic Power Plant Collection and Connection to HVDC Grid with High Voltage DC/DC Converter. Electronics 2021, 10, 3098. [Google Scholar] [CrossRef]

- Meshael, H.; Elkhateb, A.; Best, R. Topologies and Design Characteristics of Isolated High Step-Up DC–DC Converters for Photovoltaic Systems. Electronics 2023, 12, 3913. [Google Scholar] [CrossRef]

- Shahir, F.M.; Aberoumandazar, M.; Babaei, E. High Gain DC-DC Boost Converter Applied in Hybrid System of Photovoltaic and Battery. In Proceedings of the 2021 International Symposium on Devices, Circuits and Systems (ISDCS), Higashihiroshima, Japan, 3–5 March 2021; pp. 1–4. [Google Scholar] [CrossRef]

- Abolhassani, P.; Maalandish, M.; Nadermohammadi, A.; Sharifian, M.B.B.; Feyzi, M.R.; Hosseini, S.H. A high step-up high step-down coupled inductor based bidirectional DC–DC converter with low voltage stress on switches. IET Power Electron. 2024, 17, 802–823. [Google Scholar] [CrossRef]

- Maalandish, M.; Babaei, E.; Abolhasani, P.; Gheisarnejad, M.; Khooban, M.-H. Ultra high step-up soft-switching DC/DC converter using coupled inductor and interleaved technique. IET Power Electron. 2023, 16, 1320–1338. [Google Scholar] [CrossRef]

- Nadermohammadi, A.; Maalandish, M.; Seifi, A.; Abolhassani, P.; Hosseini, S.H.; Farsadi, M. A non-isolated single-switch ultra-high step-up DC–DC converter with coupled inductor and low-voltage stress on switch. IET Power Electron. 2024, 17, 251–265. [Google Scholar] [CrossRef]

- Pourjafar, S.; Sedaghati, F.; Shayeghi, H.; Maalandish, M. High step-up DC–DC converter with coupled inductor suitable for renewable applications. IET Power Electron. 2019, 12, 92–101. [Google Scholar] [CrossRef]

- Pourjafar, S.; Madadi Kojabadi, H.; Maalandish, M.; Abarzadeh, M.; Blaabjerg, F. Non-Isolated Coupled Inductor Based DC-DC Converter with High Voltage Conversion Ratio Recommended for Renewable Applications. Electr. Power Compon. Syst. 2021, 48, 1695–1707. [Google Scholar] [CrossRef]

- Pourjafar, S.; Shayeghi, H.; Hashemzadeh, S.M.; Sedaghati, F.; Maalandish, M. A non-isolated high step-up DC–DC converter using magnetic coupling and voltage multiplier circuit. IET Power Electron. 2021, 14, 1637–1655. [Google Scholar] [CrossRef]

- Sharma, P.; Hasanpour, S.; Kumar, R. A new soft-switching high step-up DC–DC converter with low voltage stress. Energy Sci. Eng. 2024, 12, 3062–3073. [Google Scholar] [CrossRef]

- Nouri, T.; Hasanpour, S.; Lee, S.S. A Semi-Quadratic Trans-Inverse High Step-Up DC-DC Converter for Renewable Energy Applications. IEEE Trans. Power Electron. 2024. [Google Scholar] [CrossRef]

- Hasanpour, S. A novel soft-switching quadratic high voltage gain trans-inverse DC/DC converter. IET Power Electron. 2024, 1–16. [Google Scholar] [CrossRef]

- Hasanpour, S.; Mostaan, A.; Haghighi, S.K.S. Dual-Output Classic Buck and Buck-Boost Converter with Fast Dynamic Response. IEEE J. Emerg. Sel. Top. Ind. Electron. 2024, 1–11. [Google Scholar] [CrossRef]

- Hasanpour, S.; Siwakoti, Y.P.; Blaabjerg, F. Analysis of a New Soft-Switched Step-Up Trans-Inverse DC/DC Converter Based on Three-Winding Coupled-Inductor. IEEE Trans. Power Electron. 2022, 37, 2203–2215. [Google Scholar] [CrossRef]

- Esmaeili, S.; Hasanpour, S.; Hafezi, H. New High Step-Up Coupled Dual Winding Quadratic Enhanced SEPIC DC-DC Converter. In Proceedings of the 2021 International Conference on Smart Energy Systems and Technologies (SEST), Vaasa, Finland, 6–8 September 2021; pp. 1–6. [Google Scholar] [CrossRef]

- Hasanpour, S.; Nouri, T.; Blaabjerg, F.; Siwakoti, Y.P. High Step-Up SEPIC-Based Trans-Inverse DC–DC Converter with Quasi-Resonance Operation for Renewable Energy Applications. IEEE Trans. Ind. Electron. 2023, 70, 485–497. [Google Scholar] [CrossRef]

- Hasanpour, S.; Siwakoti, Y.P.; Blaabjerg, F. A New High Efficiency High Step-Up DC/DC Converter for Renewable Energy Applications. IEEE Trans. Ind. Electron. 2023, 70, 1489–1500. [Google Scholar] [CrossRef]

- Hasanpour, S. New Structure of Single-Switch Ultra-High-Gain DC/DC Converter for Renewable Energy Applications. IEEE Trans. Power Electron. 2022, 37, 12715–12728. [Google Scholar] [CrossRef]

- Hasanpour, S.; Forouzesh, M.; Siwakoti, Y. Full Soft-Switching Ultra-High Gain DC/DC Converter Using Three-Winding Coupled-Inductor with Modular Scalability for Renewable Energy Applications. AUT J. Electr. Eng. 2022, 54, 49–66. [Google Scholar] [CrossRef]

- Upadhyay, P.; Sharma, P.; Khandelwal, S.; Kumar, R.; Hassanpour, S. An active clamp coupled inductor-based soft-switched quadratic boost converter. Int. J. Circuit Theory Appl. 2023, 51, 2141–2162. [Google Scholar] [CrossRef]

- Sharma, P.; Upadhyay, P.; Kumar, R.; Hassanpour, S. ZCS-ZVS Operation of a Double Frequency High-Voltage Gain Boost Converter. In Proceedings of the 2022 IEEE 19th India Council International Conference (INDICON), Kochi, India, 24–26 November 2022; pp. 1–6. [Google Scholar] [CrossRef]

- Esmaeili, S.; Shekari, M.; Rasouli, M.; Hasanpour, S.; Khan, A.A.; Hafezi, H. High Gain Magnetically Coupled Single Switch Quadratic Modified SEPIC DC-DC Converter. IEEE Trans. Ind. Appl. 2023, 59, 3593–3604. [Google Scholar] [CrossRef]

- Hasanpour, S.; Nouri, T. New Coupled-Inductor High-Gain DC/DC Converter with Bipolar Outputs. IEEE Trans. Ind. Electron. 2024, 71, 2601–2613. [Google Scholar] [CrossRef]

- Hasanpour, S.; Siwakoti, Y.P.; Blaabjerg, F. A New Soft-Switched High Step-Up Trans-Inverse DC/DC Converter Based on Built-In Transformer. IEEE Open J. Power Electron. 2023, 4, 381–394. [Google Scholar] [CrossRef]

- Mostaan, A.; Esmaeili, S.; Hasanpour, S.; Taleshani, T.B.; Khan, A.A. A Symmetric Bipolar Quadratic Buck–Boost Converter with Synchronous Triple Switches. IEEE J. Emerg. Sel. Top. Ind. Electron. 2023, 4, 1055–1062. [Google Scholar] [CrossRef]

- Hasanpour, S.; Siwakoti, Y.P.; Blaabjerg, F. A new soft-switching high gain DC/DC converter with bipolar outputs. IET Power Electron. 2024, 17, 144–156. [Google Scholar] [CrossRef]

- Wu, Y.-E.; Chiu, P.-N. A High-Efficiency Isolated-Type Three-Port Bidirectional DC/DC Converter for Photovoltaic Systems. Energies 2017, 10, 434. [Google Scholar] [CrossRef]

- Premkumar, M.; Subramaniam, U.; Haes Alhelou, H.; Siano, P. Design and Development of Non-Isolated Modified SEPIC DC-DC Converter Topology for High-Step-Up Applications: Investigation and Hardware Implementation. Energies 2020, 13, 3960. [Google Scholar] [CrossRef]

- Bakeer, A.; Chub, A.; Vinnikov, D.; Rosin, A. Wide Input Voltage Range Operation of the Series Resonant DC-DC Converter with Bridgeless Boost Rectifier. Energies 2020, 13, 4220. [Google Scholar] [CrossRef]

- Zheng, W.; Hu, C.; Zhao, B.; Su, X.-B.; Wang, G.; Hou, X.-W.; Gu, B. A Two-Stage DC/DC Isolated High-Voltage Converter with Zero-Voltage Switching and Zero-Current Switching Applied in Electronic Power Conditioners. Energies 2022, 15, 6378. [Google Scholar] [CrossRef]

- Ataullah, H.; Iqbal, T.; Khalil, I.U.; Ali, U.; Blazek, V.; Prokop, L.; Ullah, N. Analysis of the Dual Active Bridge-Based DC-DC Converter Topologies, High-Frequency Transformer, and Control Techniques. Energies 2022, 15, 8944. [Google Scholar] [CrossRef]

- Bathala, K.; Kishan, D.; Harischandrappa, N. Soft Switched Current Fed Dual Active Bridge Isolated Bidirectional Series Resonant DC-DC Converter for Energy Storage Applications. Energies 2023, 16, 258. [Google Scholar] [CrossRef]

- Chen, S.-J.; Yang, S.-P.; Huang, C.-M.; Huang, P.-S. Analysis and Design of a New High Voltage Gain Interleaved DC–DC Converter with Three-Winding Coupled Inductors for Renewable Energy Systems. Energies 2023, 16, 3958. [Google Scholar] [CrossRef]

- Kang, H.-W.; Lee, H.-S.; Rhee, J.-H.; Lee, K.-A. DC Voltage Source Based on a Battery of Supercapacitors with a Regulator in the Form of an Isolated Boost LCC Resonant Converter. Energies 2023, 16, 6721. [Google Scholar] [CrossRef]

- Xue, Y.; Yang, G. A Wide-Output-Range DC-DC Converter and Minimum Loss Collaborative Control Strategy. Energies 2024, 17, 499. [Google Scholar] [CrossRef]

- Sucameli, M.; Adragna, C. LLC Resonant Converters as Isolated Power Factor Corrector Pre-Regulators—Analysis and Performance Evaluation. Energies 2023, 16, 7114. [Google Scholar] [CrossRef]

- Chen, S.-H.; Chen, C.-T.; Lin, Y.-F. Dual-Coupled-Inductor-Based High-Step-Up Boost Converter with Active-Clamping and Zero-Voltage Switching. Energies 2024, 17, 2018. [Google Scholar] [CrossRef]

- Lichev, A.; Madankov, Y.; Mihov, V.; Spirov, D. Bidirectional Resonant Power Converter for Hybrid Energy Systems. Eng. Proc. 2024, 70, 3. [Google Scholar] [CrossRef]

- Alsaleem, A.; Alsakran, F.; Simões, M.G. An Isolated High Voltage Boost Current-Fed DC–DC Converter Based on 1:1 Transformer Multiplier Cells and ZVS Operation. Electronics 2020, 9, 102. [Google Scholar] [CrossRef]

- Maheri, H.M.; Heris, P.C.; Saadatizadeh, Z.; Babaei, E.; Vinnikov, D. A New Coupled-Inductor-Based Buck/Boost DC/DC Converter with Soft Switching for DC Microgrid Applications. In Proceedings of the 2021 IEEE 15th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), Florence, Italy, 14–16 July 2021; pp. 1–6. [Google Scholar] [CrossRef]

- Bektas, S.; Shahir, F.M.; Babaei, E. New High Step-Up DC-DC Converter in PV System: Performance and Analysis. In 11th International Conference on Theory and Application of Soft Computing, Computing with Words and Perceptions and Artificial Intelligence—ICSCCW-2021; Aliev, R.A., Kacprzyk, J., Pedrycz, W., Jamshidi, M., Babanli, M., Sadikoglu, F.M., Eds.; Springer: Berlin/Heidelberg, Germany, 2021. [Google Scholar]

- Hashemzadeh, S.M.; Babaei, E.; Hosseini, S.H.; Sabahi, M. Design and Analysis of a New Coupled Inductor-Based Interleaved High Step-Up DC-DC Converter for Renewable Energy Applications. Int. Trans. Electr. Energy Syst. 2022, 2022, 7618242. [Google Scholar] [CrossRef]

- Maheri, H.M.; Saadatizadeh, Z.; Heris, P.C.; Babaei, E.; Vinnikov, D. A New High Step-Up Switched-Capacitor/inductor Based DC-DC Converter. In Proceedings of the 2021 IEEE 62nd International Scientific Conference on Power and Electrical Engineering of Riga Technical University (RTUCON), Riga, Latvia, 15–17 November 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Rajabi, A.; Mohammadzadeh Shahir, F.; Babaei, E. Designing a novel voltage-lift technique based non-isolated boost DC-DC converter with high voltage gain. Int. Trans. Electr. Energy Syst. 2021, 31, e13213. [Google Scholar] [CrossRef]

- Babazadeh, Y.; Sabahi, M.; Babaei, E.; Kai, S. A New Continuous Input Current Nonisolated Bidirectional Interleaved Buck-Boost DC-DC Converter. Int. Trans. Electr. Energy Syst. 2022, 2022, 9453913. [Google Scholar] [CrossRef]

- Hosseinzadehlish, M.; Hashemzadeh, S.M.; Pourjafar, S.; Babaei, E. A Single Switch High Step-Up DC-DC Converter Based on Tri-Winding Coupled Inductor for Renewable Energy Applications. Int. Trans. Electr. Energy Syst. 2022, 2022, 4175292. [Google Scholar] [CrossRef]

- Falahi, F.; Babaei, E.; Bagheri, S. Soft-Switched Interleaved High Step-Up Non-isolated DC-DC Converter with High Voltage Gain Ratio. In Proceedings of the 2022 13th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 1–3 February 2022; pp. 128–133. [Google Scholar] [CrossRef]

- Alizadeh, D.; Babaei, E. Non-Isolated Bidirectional DC-DC Soft-Switching Converter without Auxiliary Switches. In Proceedings of the 2022 13th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 1–3 February 2022; pp. 346–350. [Google Scholar] [CrossRef]

- Alizadeh, D.; Babaei, E.; Sabahi, M. High Step-Up Quadratic Impedance Source DC-DC Converter Based on Coupled Inductor. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 5930–5939. [Google Scholar] [CrossRef]

- Hosseinzadeh, M.A.; Sarebanzadeh, M.; Khalilian, M.; Kennel, R.; Garcia, C.; Babaei, E.; Rodriguez, J. A New Power Converter Design for Electrical Vehicle Inductive Wireless Power Transfer Charging with Zero Common-Mode Current. In Proceedings of the 2023 IEEE Wireless Power Technology Conference and Expo (WPTCE), San Diego, CA, USA, 4–8 June 2023; pp. 1–6. [Google Scholar] [CrossRef]

- Aalami, M.; Babaei, E.; Zadeh, S.G. Coupled Inductor Assisted High-Voltage Gain Half-Bridge Z-Source Inverter. IEEE Open J. Ind. Electron. Soc. 2023, 4, 176–188. [Google Scholar] [CrossRef]

- Falahi, F.; Allahyari, H.; Babaei, E. An Improved High Step-up Non Isolated DC-DC Converter: Steady-State Analysis, Design and Simulation. In Proceedings of the 2023 14th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Babol, Iran, 31 January–2 February 2023; pp. 1–6. [Google Scholar] [CrossRef]

- Hashemzadeh, S.M.; Hosseini, S.H.; Babaei, E.; Sabahi, M. Design and modelling of a new three winding coupled inductor based high step-up DC–DC converter for renewable energy applications. IET Power Electron. 2022, 15, 1322–1339. [Google Scholar] [CrossRef]

- Hashemzadeh, S.M.; Hosseini, S.H.; Babaei, E.; Sabahi, M. A soft switched high step-up DC-DC converter based on VMC and coupled inductor for photovoltaic energy applications. IET Renew. Power Gener. 2023, 17, 1583–1596. [Google Scholar] [CrossRef]

- Pashaie, R.; Sabahi, M.; Babaei, E. An interleaved high step-down coupled inductor based quadratic DC-DC converter. IET Power Electron. 2023, 16, 1558–1572. [Google Scholar] [CrossRef]

- Pourali, F.; Babaei, E.; Alizadeh, D.; Sabahi, M. An extendable step-up/down DC-DC converter based on switched capacitors. IET Power Electron. 2023, 16, 2138–2149. [Google Scholar] [CrossRef]

- Hashemzadeh, S.M.; Al-Hitmi, M.A.; Aghaei, H.; Marzang, V.; Iqbal, A.; Babaei, E.; Hosseini, S.H.; Islam, S. An ultra-high voltage gain interleaved converter based on three-winding coupled inductor with reduced input current ripple for renewable energy applications. IET Renew. Power Gener. 2024, 18, 141–151. [Google Scholar] [CrossRef]

- Karimi, K.; Babaei, E.; Karimi, M.; Alizadeh, D.; Mousavi, S.M.J. An interleaved high step-up DC–DC converter based on coupled-inductor. IET Power Electron. 2024, 17, 473–485. [Google Scholar] [CrossRef]

- Alizadeh, D.; Babaei, E.; Sabahi, M.; Cecati, C. A Family of High Step-Up Interleaved DC–DC Converters Based on the Coupled Inductors. IEEE Trans. Ind. Electron. 2024, 1–11. [Google Scholar] [CrossRef]

- Saadatizadeh, Z.; Babaei, E.; Hosseini, S.H. Double-input triple-output non-isolated DC–DC converter based on coupled inductor with high step-up output voltages. Int. J. Circuit Theory Appl. 2024, 52, 3703–3733. [Google Scholar] [CrossRef]

- Alizadeh, D.; Babaei, E.; Sabahi, M.; Cecati, C. Hybrid interleaved DC-DC step-up converter based on coupled inductor. Int. J. Circuit Theory Appl. 2024, 52, 2655–2685. [Google Scholar] [CrossRef]

- Nikbakht, M.; Abbaszadeh, K.; Abbasian, S.; Allahyari, H.; Gorji, S.A. An Ultra-Step-Up Quadratic Boost DC–DC Converter Based on Coupled Inductors and Quasi-Resonance Operation. J. Emerg. Sel. Top. Ind. Electron. 2023, 4, 1096–1109. [Google Scholar] [CrossRef]

- Moradi, A.; Gorji, S.A.; Hakemi, A.; Ganjavi, A.; Sera, D. Study of a DC Micro-Gird Configuration to Produce Hydrogen (DCMG-H2). In Proceedings of the 2022 IEEE 7th Southern Power Electronics Conference (SPEC), Nadi, Fiji, 5–8 December 2022; pp. 1–5. [Google Scholar] [CrossRef]

- Shalmaei, A.H.M.; Gorji, S.A. A Non-inverting Transformerless Semi-Quadratic Buck-Boost Converter. In Proceedings of the 2022 12th International Conference on Power, Energy and Electrical Engineering (CPEEE), Shiga, Japan, 25–27 February 2022; pp. 113–119. [Google Scholar] [CrossRef]

- Gorji, S.A.; Mostaan, A.; Tran My, H.; Ektesabi, M. Non-isolated buck–boost dc–dc converter with quadratic voltage gain ratio. IET Power Electron. 2019, 12, 1425–1433. [Google Scholar] [CrossRef]

- Kaye, R.; Gorji, S.A.; Kalam, A. Multi-Input DC-DC Boost Converter with Voltage Multiplier Cells and Continuous Input-Output Current. In Proceedings of the 2022 IEEE PES 14th Asia-Pacific Power and Energy Engineering Conference (APPEEC), Melbourne, Australia, 20–23 November 2022; pp. 1–5. [Google Scholar] [CrossRef]

- Tran, V.-T.; Nguyen, M.-K.; Choi, Y.-O.; Cho, G.-B. Switched-Capacitor-Based High Boost DC-DC Converter. Energies 2018, 11, 987. [Google Scholar] [CrossRef]

- Karthikeyan, M.; Elavarasu, R.; Ramesh, P.; Bharatiraja, C.; Sanjeevikumar, P.; Mihet-Popa, L.; Mitolo, M. A Hybridization of Cuk and Boost Converter Using Single Switch with Higher Voltage Gain Compatibility. Energies 2020, 13, 2312. [Google Scholar] [CrossRef]

- Ullah, Q.; Busarello, T.D.C.; Brandao, D.I.; Simões, M.G. Design and Performance Evaluation of SMC-Based DC-DC Converters for Microgrid Applications. Energies 2023, 16, 4212. [Google Scholar] [CrossRef]

- de Sá, F.L.; Ruiz-Caballero, D.; Dal’Agnol, C.; da Silva, W.R.; Mussa, S.A. High Static Gain DC–DC Double Boost Quadratic Converter. Energies 2023, 16, 6362. [Google Scholar] [CrossRef]

- Mihov, V.; Lichev, A.; Madankov, Y.; Spirov, D. Examination of Two-Quadrant DC-DC Converter with Single-Ended LC Output Filter. Eng. Proc. 2024, 70, 8. [Google Scholar] [CrossRef]

- Maheri, H.M.; Shahir, F.M.; Babaei, E. A New Transformer-Less Single Switch Boost DC-DC Converter with Lower Stress. In Proceedings of the 2020 IEEE 61th International Scientific Conference on Power and Electrical Engineering of Riga Technical University (RTUCON), Riga, Latvia, 5–7 November 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Ding, B.; Li, Z.; Li, Z.; Xue, Y.; Chang, X.; Su, J.; Jin, X.; Sun, H. A CCP-based distributed cooperative operation strategy for multi-agent energy systems integrated with wind, solar, and buildings. Appl. Energy 2024, 365, 123275. [Google Scholar] [CrossRef]

- Zhang, H.; Zhai, X.; Zhang, J.; Bai, X.; Li, Z. Mechanism Analysis of the Effect of the Equivalent Proportional Coefficient of Inertia Control for a Doubly Fed Wind Generator on Frequency Stability in Extreme Environments. Sustainability 2024, 16, 4965. [Google Scholar] [CrossRef]

| Topology | L | C | S | D | All |

|---|---|---|---|---|---|

| [10] | 2 | 3 | 2 | 2 | 8 |

| [11] | 2 | 2 | 2 | 2 | 8 |

| [12] | 3 | 3 | 1 | 3 | 10 |

| [13] | 2 | 2 | 1 | 3 | 8 |

| [14] | 3 | 4 | 1 | 2 | 10 |

| [15] | 2 | 2 | 2 | 2 | 8 |

| [16] | 2 | 2 | 2 | 2 | 8 |

| [17] | 2 | 2 | 1 | 3 | 8 |

| [18] | 3 | 4 | 2 | 3 | 12 |

| [19] | 2 | 2 | 2 | 2 | 8 |

| [20] | 2 | 2 | 2 | 2 | 8 |

| [21] | 3 | 3 | 2 | 2 | 10 |

| [22] | 2 | 3 | 2 | 3 | 10 |

| [23] | 2 | 2 | 2 | 2 | 8 |

| [24] | 2 | 3 | 2 | 3 | 10 |

| [25] | 2 | 2 | 2 | 2 | 8 |

| [26] | 3 | 3 | 1 | 5 | 12 |

| [27] | 3 | 3 | 1 | 3 | 10 |

| [28] | 3 | 3 | 2 | 2 | 10 |

| [29] | 3 | 3 | 2 | 2 | 10 |

| [30] | 2 | 2 | 2 | 2 | 8 |

| [31] | 2 | 2 | 2 | 2 | 8 |

| [32] | 2 | 2 | 2 | 2 | 8 |

| [33] | 3 | 3 | 2 | 2 | 10 |

| [34] | 2 | 2 | 2 | 2 | 8 |

| [35] | 3 | 3 | 2 | 2 | 10 |

| [36] | 2 | 2 | 2 | 2 | 8 |

| [37] | 3 | 3 | 2 | 2 | 10 |

| [38] | 2 | 2 | 2 | 2 | 8 |

| [39] | 3 | 3 | 2 | 2 | 10 |

| Proposed | 4 | 12 | 1 | 15 | 32 |

| L | C | S | D | All | |

|---|---|---|---|---|---|

| [41] | 2 | 4 | 1 | 5 | 12 |

| [42] | 3 | 4 | 1 | 4 | 12 |

| [43] | 1 | 3 | 1 | 3 | 8 |

| [44] | 5 | 3 | 1 | 9 | 18 |

| [45] | 5 | 5 | 1 | 7 | 18 |

| [46] | 2 | 3 | 2 | 3 | 10 |

| [47] | 2 | 3 | 2 | 3 | 10 |

| [48] | 3 | 4 | 2 | 3 | 12 |

| [49] | 3 | 6 | 1 | 3 | 13 |

| [40] | 3 | 4 | 1 | 2 | 10 |

| [50] | 2 | 3 | 1 | 4 | 10 |

| [51] | 3 | 4 | 1 | 6 | 14 |

| [52] | 3 | 5 | 1 | 6 | 15 |

| [53] | 2 | 3 | 2 | 3 | 10 |

| [54] | 3 | 4 | 1 | 5 | 13 |

| [55] | 3 | 3 | 1 | 5 | 12 |

| [56] | 3 | 4 | 1 | 6 | 14 |

| [57] | 3 | 3 | 1 | 5 | 12 |

| [58] | 3 | 3 | 1 | 5 | 12 |

| [59] | 2 | 4 | 1 | 3 | 10 |

| [60] | 3 | 3 | 1 | 5 | 12 |

| proposed | 4 | 12 | 1 | 15 | 32 |

| Topology | |||||

|---|---|---|---|---|---|

| [10] | 0.5 | 0.5 | 0.5 | 0.5 | 0.125 |

| [11] | 1.5 | 1.5 | 1.5 | 1.5 | 0.375 |

| [12] | 0.66 | 0.66 | 2 | 0.66 | 0.2 |

| [13] | 2 | 2 | 4 | 1.33 | 0.5 |

| [14] | 0.66 | 0.5 | 2 | 1 | 0.2 |

| [15] | 1 | 1 | 1 | 1 | 0.25 |

| [16] | 2 | 2 | 2 | 2 | 0.5 |

| [17] | 1.5 | 1.5 | 1.5 | 1.5 | 0.375 |

| [18] | 1 | 0.75 | 1.5 | 1 | 0.25 |

| [19] | 0.5 | 0.5 | 0.5 | 0.5 | 0.125 |

| [20] | 0.5 | 0.5 | 0.5 | 0.5 | 0.125 |

| [21] | 0.33 | 0.33 | 0.5 | 0.5 | 0.1 |

| [22] | 2 | 1.3 | 2 | 1.3 | 0.4 |

| [23] | 0.5 | 0.5 | 0.5 | 0.5 | 0.125 |

| [24] | 3 | 2 | 3 | 2 | 0.5 |

| [25] | 2 | 2 | 2 | 2 | 0.5 |

| [26] | 0.33 | 2 | 2 | 2 | 0.5 |

| [27] | 0.66 | 0.66 | 1 | 1 | 0.2 |

| [28] | 0.33 | 2 | 2 | 2 | 0.5 |

| [29] | 0.33 | 0.33 | 0.5 | 0.5 | 0.1 |

| [30] | 2 | 2 | 2 | 2 | 0.5 |

| [31] | 2 | 2 | 2 | 2 | 0.5 |

| [32] | 2 | 2 | 2 | 2 | 0.5 |

| [33] | 1 | 1 | 1.5 | 1.5 | 0.3 |

| [34] | 1.5 | 1.5 | 1.5 | 1.5 | 0.375 |

| [35] | 0.67 | 0.67 | 1 | 1 | 0.2 |

| [36] | 2 | 2 | 2 | 2 | 0.5 |

| [37] | 0.66 | 0.66 | 1 | 1 | 0.2 |

| [38] | 2 | 2 | 2 | 2 | 0.5 |

| [39] | 0.33 | 0.33 | 0.5 | 0.5 | 0.1 |

| [41] | 4 | 2 | 8 | 1.6 | 0.75 |

| [42] | 1.66 | 1.25 | 5 | 1.25 | 0.42 |

| [43] | 4 | 1.3 | 4 | 1.3 | 0.5 |

| [44] | 0.9 | 1.5 | 4.5 | 0.5 | 0.25 |

| [45] | 1.6 | 1.6 | 8 | 1.14 | 0.44 |

| [46] | 3.5 | 2.33 | 3.5 | 2.33 | 0.7 |

| [47] | 3.5 | 2.33 | 3.5 | 2.33 | 0.7 |

| [48] | 1.66 | 1.25 | 2.5 | 1.66 | 0.42 |

| [49] | 1 | 0.5 | 3 | 1 | 0.23 |

| [40] | 0.66 | 0.5 | 2 | 1 | 0.2 |

| [50] | 3 | 2 | 6 | 1.5 | 0.6 |

| [51] | 4 | 3 | 12 | 2 | 0.85 |

| [52] | 3.33 | 2 | 10 | 1.66 | 0.66 |

| [53] | 3 | 2 | 3 | 2 | 0.6 |

| [54] | 3 | 2.25 | 9 | 1.8 | 0.69 |

| [55] | 2.66 | 2.66 | 8 | 1.6 | 0.75 |

| [56] | 3.33 | 2.5 | 10 | 1.66 | 0.69 |

| [5] | 1.33 | 1.33 | 4 | 0.8 | 0.33 |

| [58] | 2.33 | 2.33 | 7 | 1 | 0.5 |

| [59] | 2 | 1 | 4 | 1.33 | 0.4 |

| [60] | 3.33 | 3.33 | 10 | 2 | 0.83 |

| Proposed | 36 | 12 | 144 | 9.6 | 4.5 |

| Inductor | Capacitor | Diode | Switch |

|---|---|---|---|

| EC type | MKT | DTV56F | IRF450 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gholizadeh, H.; Shahrivar, R.S.; Amini, S.; Rahimi, T. An Improved Cascaded Boost Converter with an Ultra-High Voltage Gain Suitable for Dielectric Quality Tests. Energies 2024, 17, 3861. https://doi.org/10.3390/en17153861

Gholizadeh H, Shahrivar RS, Amini S, Rahimi T. An Improved Cascaded Boost Converter with an Ultra-High Voltage Gain Suitable for Dielectric Quality Tests. Energies. 2024; 17(15):3861. https://doi.org/10.3390/en17153861

Chicago/Turabian StyleGholizadeh, Hossein, Reza Sharifi Shahrivar, Saeed Amini, and Tohid Rahimi. 2024. "An Improved Cascaded Boost Converter with an Ultra-High Voltage Gain Suitable for Dielectric Quality Tests" Energies 17, no. 15: 3861. https://doi.org/10.3390/en17153861

APA StyleGholizadeh, H., Shahrivar, R. S., Amini, S., & Rahimi, T. (2024). An Improved Cascaded Boost Converter with an Ultra-High Voltage Gain Suitable for Dielectric Quality Tests. Energies, 17(15), 3861. https://doi.org/10.3390/en17153861