Overlap Time Compensation and Characteristic Analysis for Current Source Photovoltaic Grid-Connected Inverter

Abstract

:1. Introduction

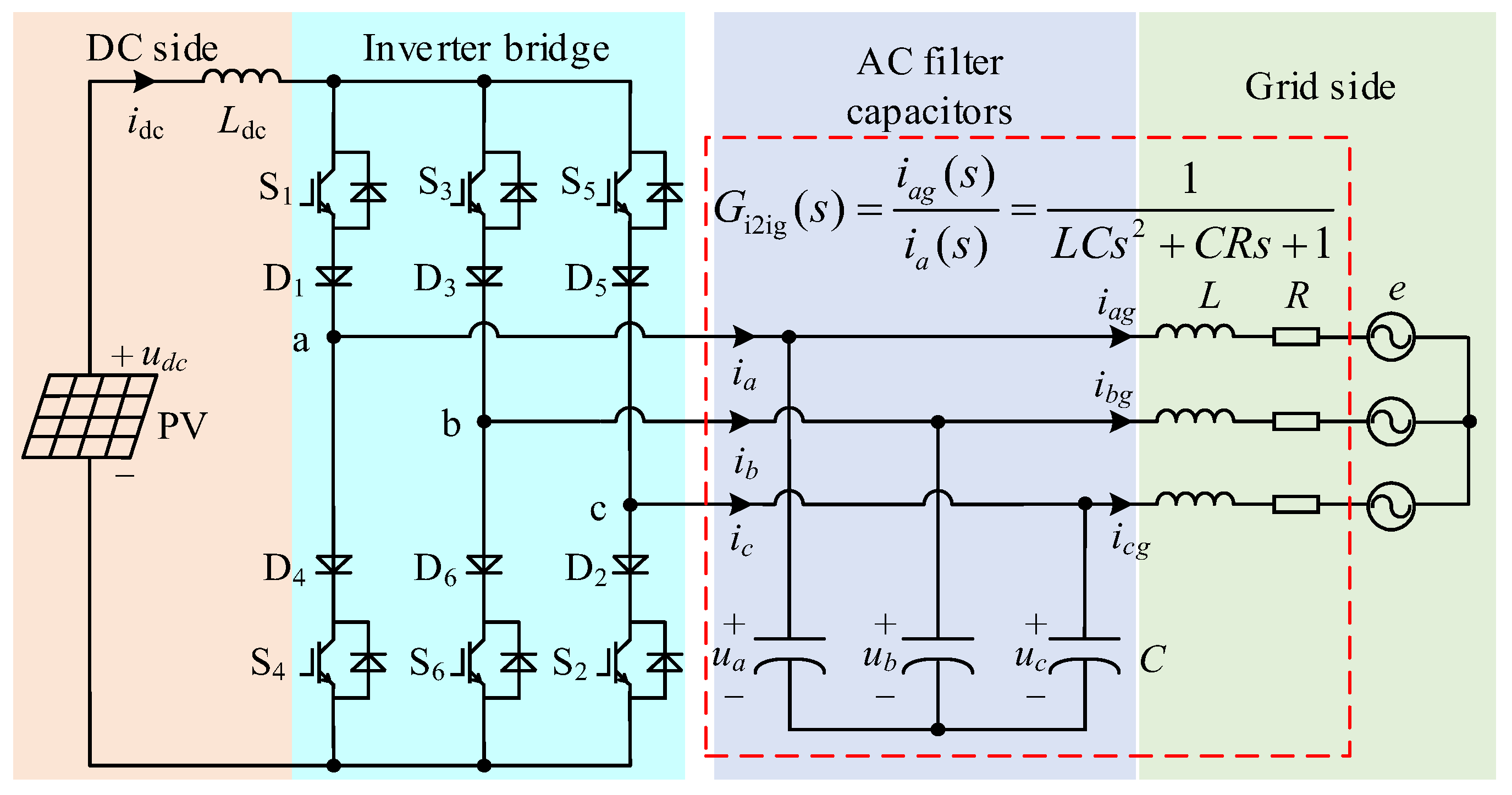

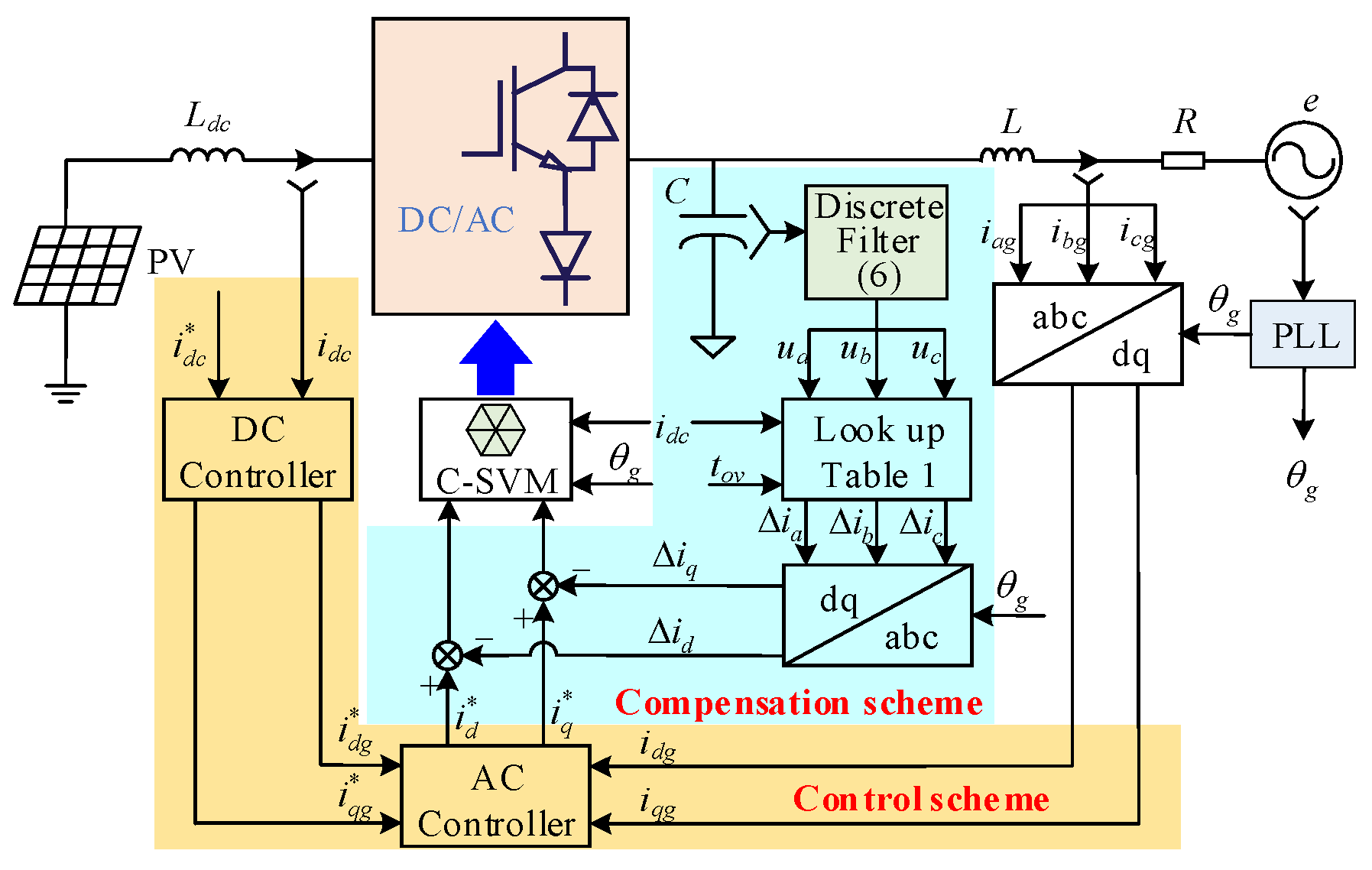

2. Topology, SVPWM Scheme and Overlap Time Generation of CSI

2.1. Topology of CSI

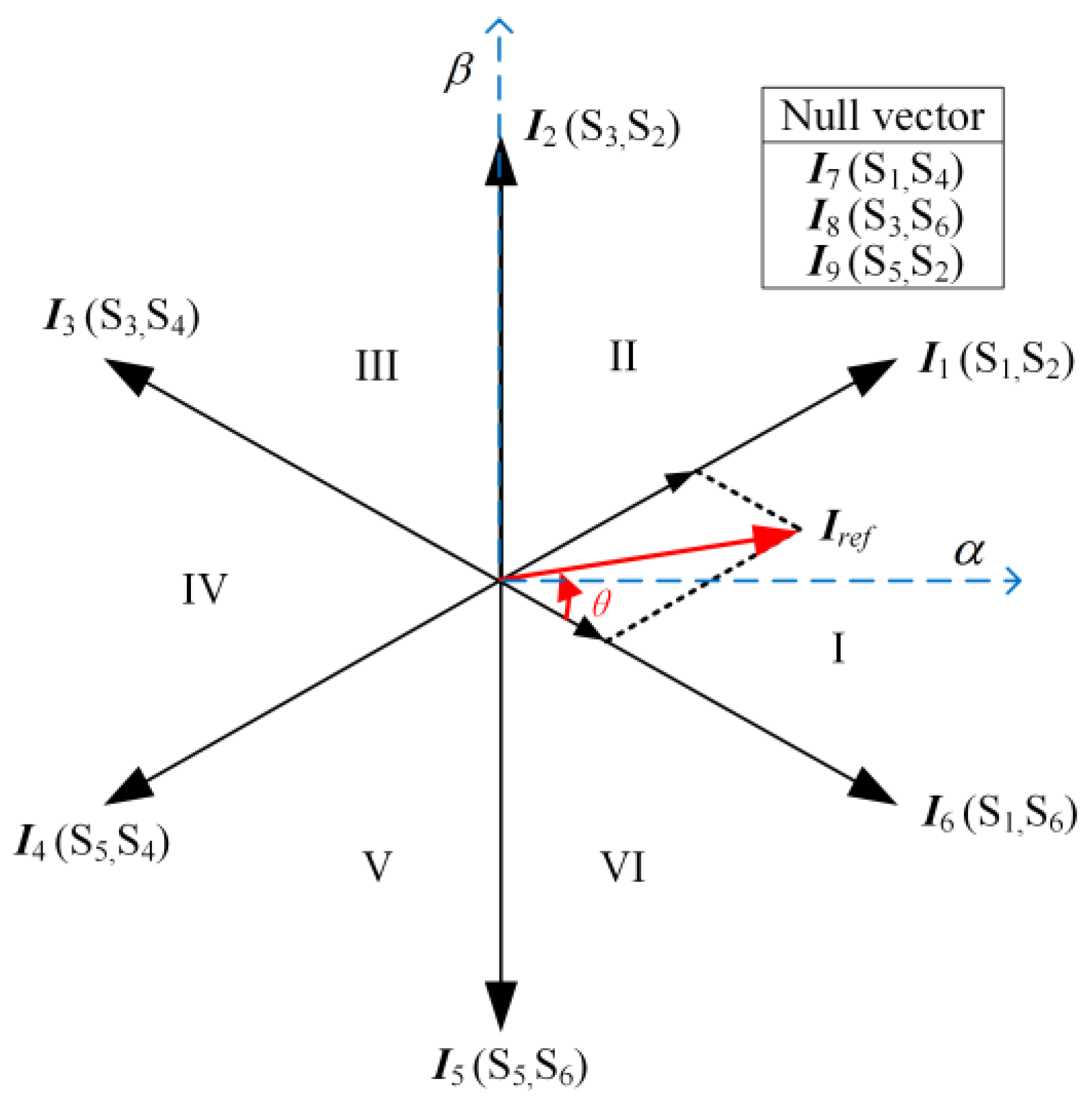

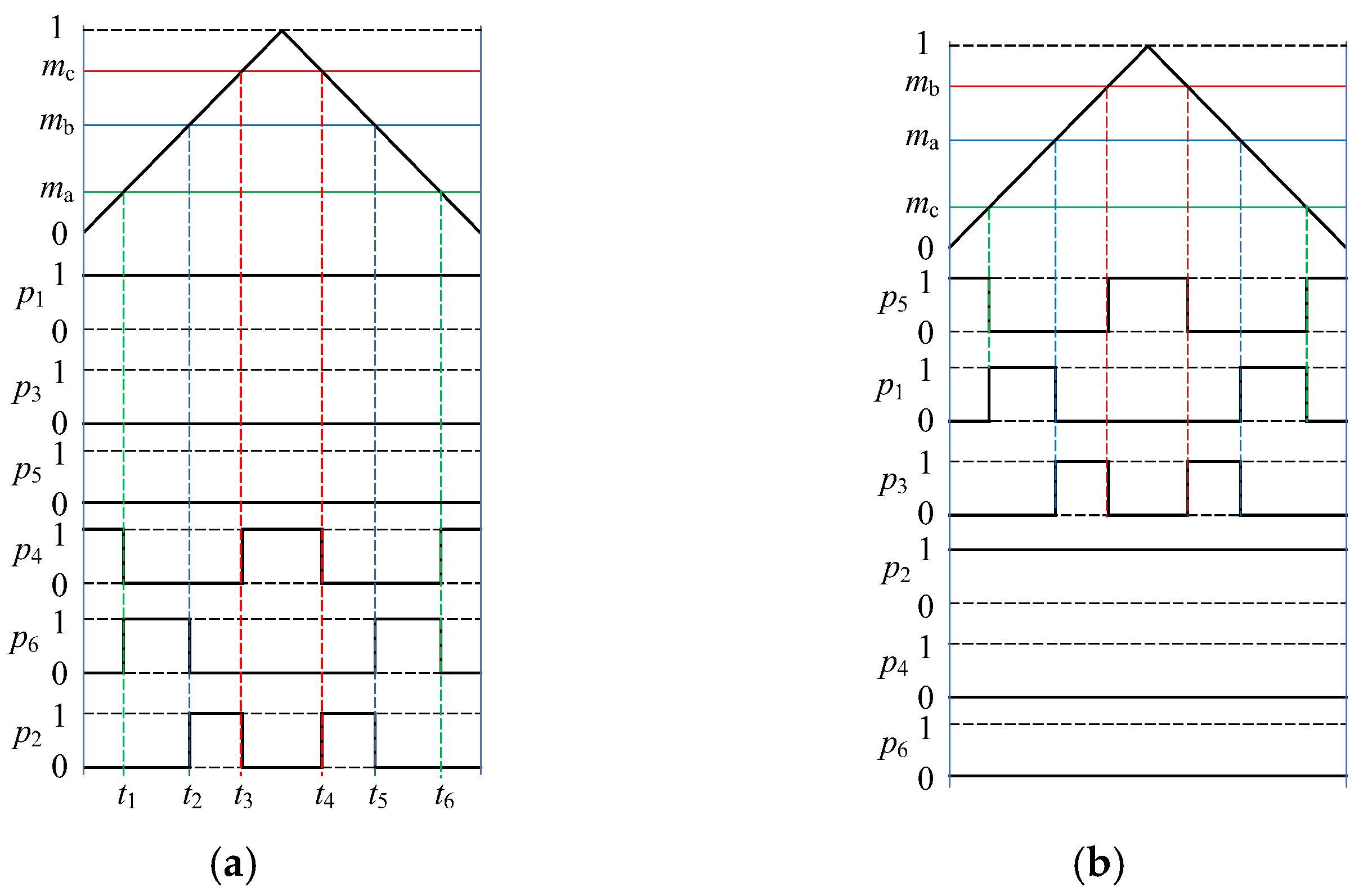

2.2. SVM Scheme of CSI

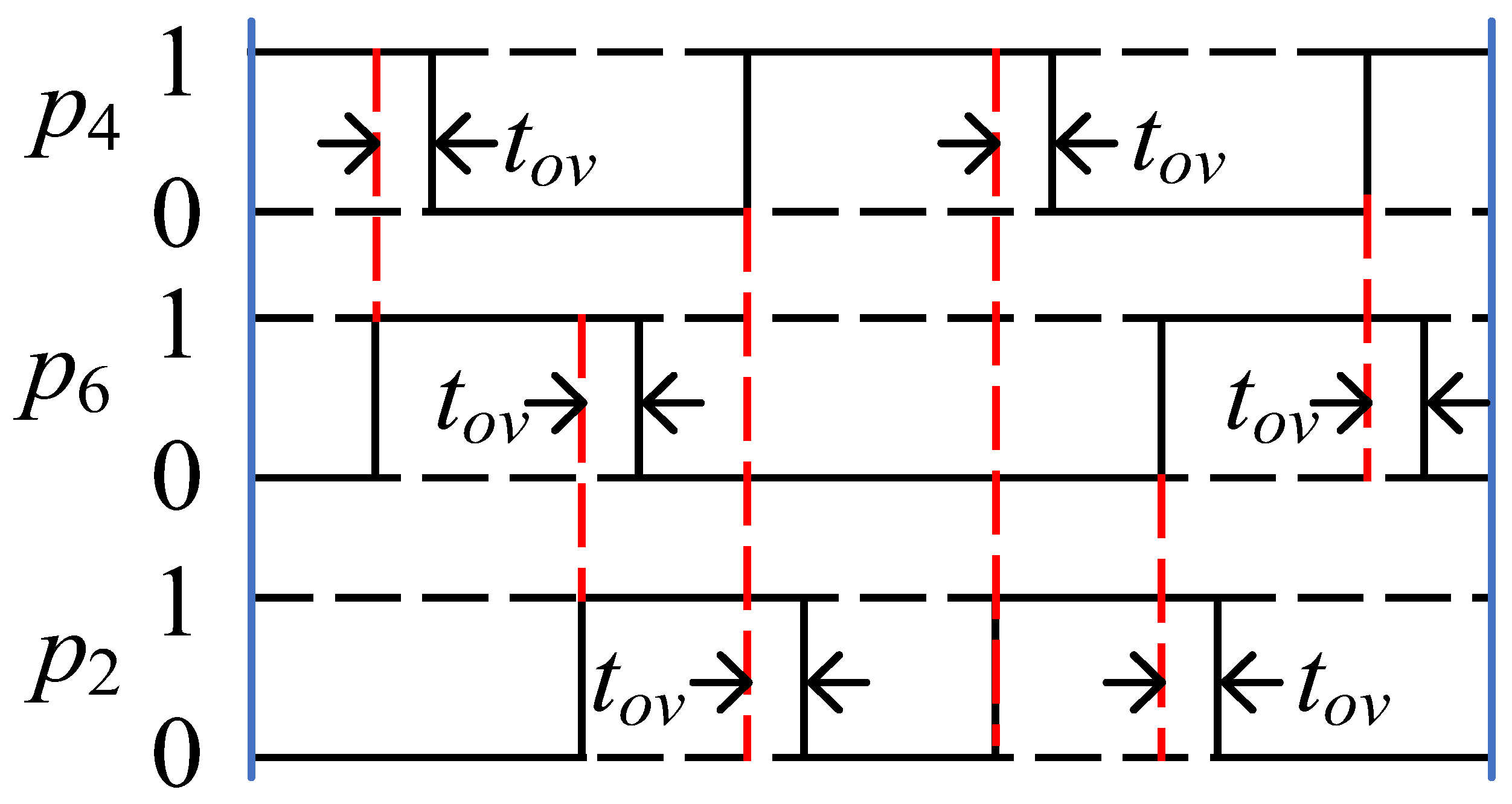

2.3. Overlap Time Generation Mechanism

3. Analysis of Overlap Time Effect

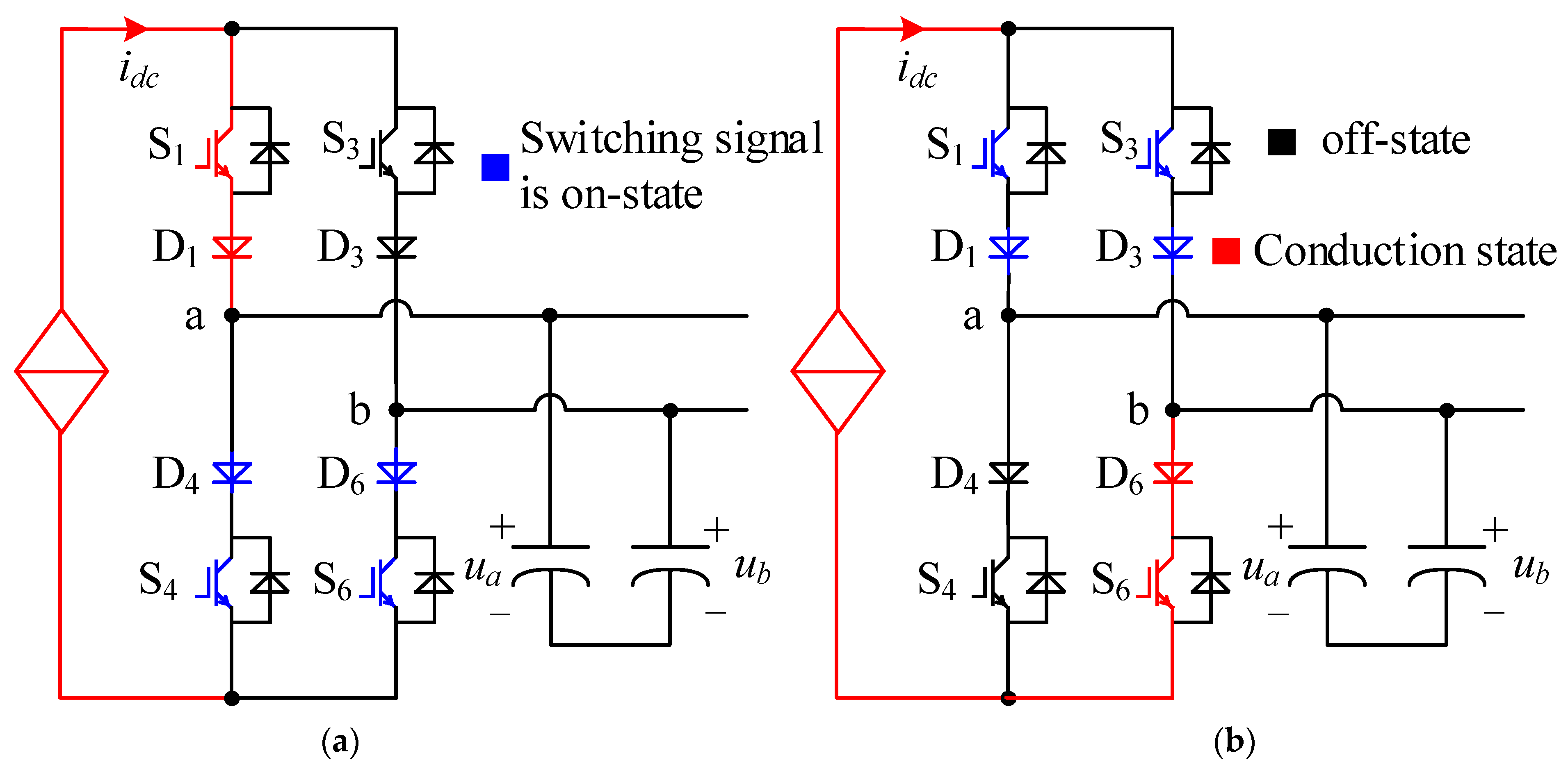

3.1. Commutation Characteristics during the Overlap Time

- When the target current vector is located in Sector I, III, or V, the commutation occurs among the lower bridge arms (S4, S6, and S2). DC-link current only flows through the switching tube and diode whose phase voltage is higher, so the nonlinear current will not be generated if the sequence of commutation is from high voltage to low voltage;

- When the target current vector is located in Sector II, IV, or VI, the commutation occurs among the upper bridge arms (S1, S3, and S5). DC-link current only flows through the switching tube and diode whose phase voltage is lower, so the nonlinear current will not be generated if the sequence of commutation is from low voltage to high voltage.

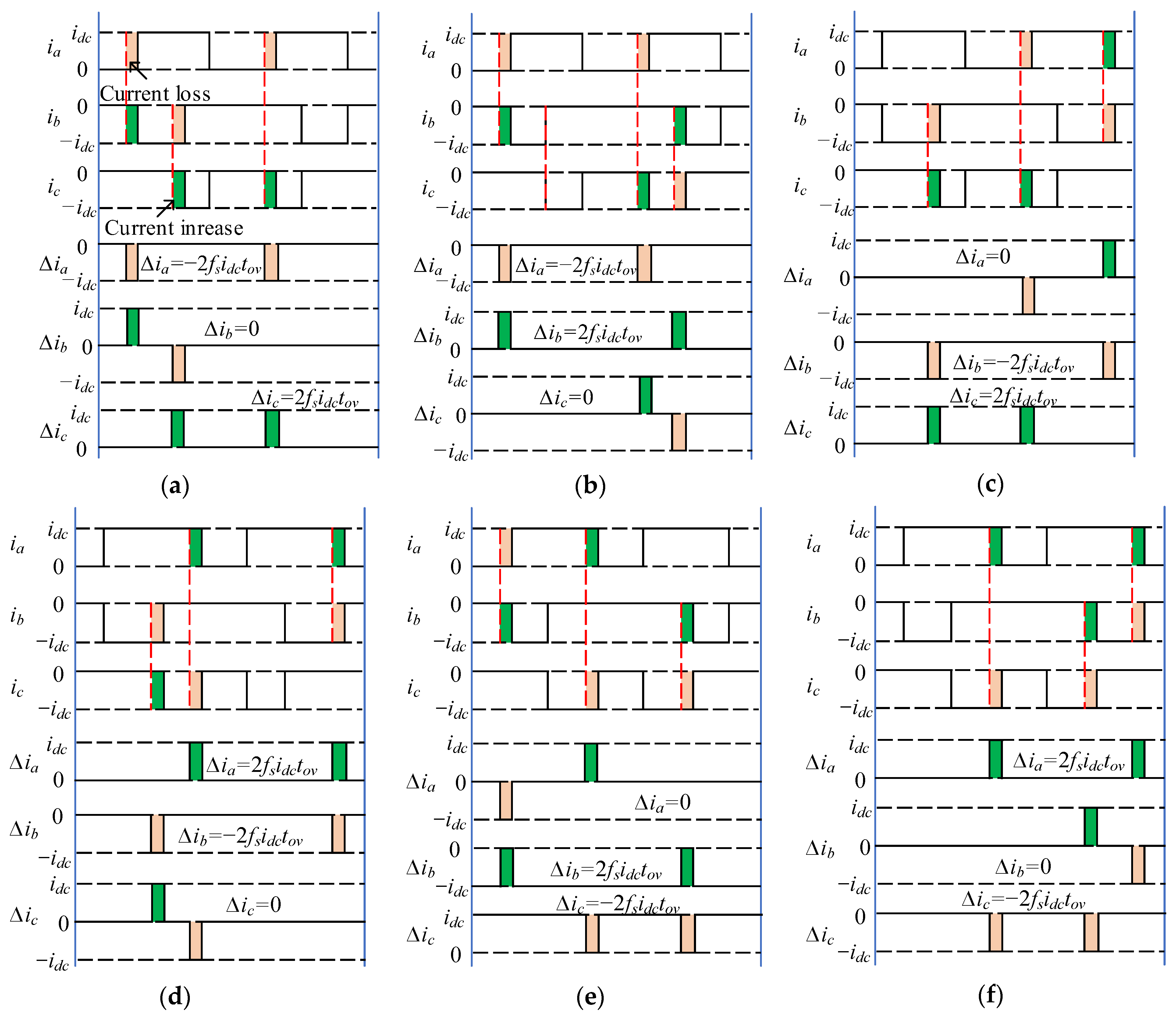

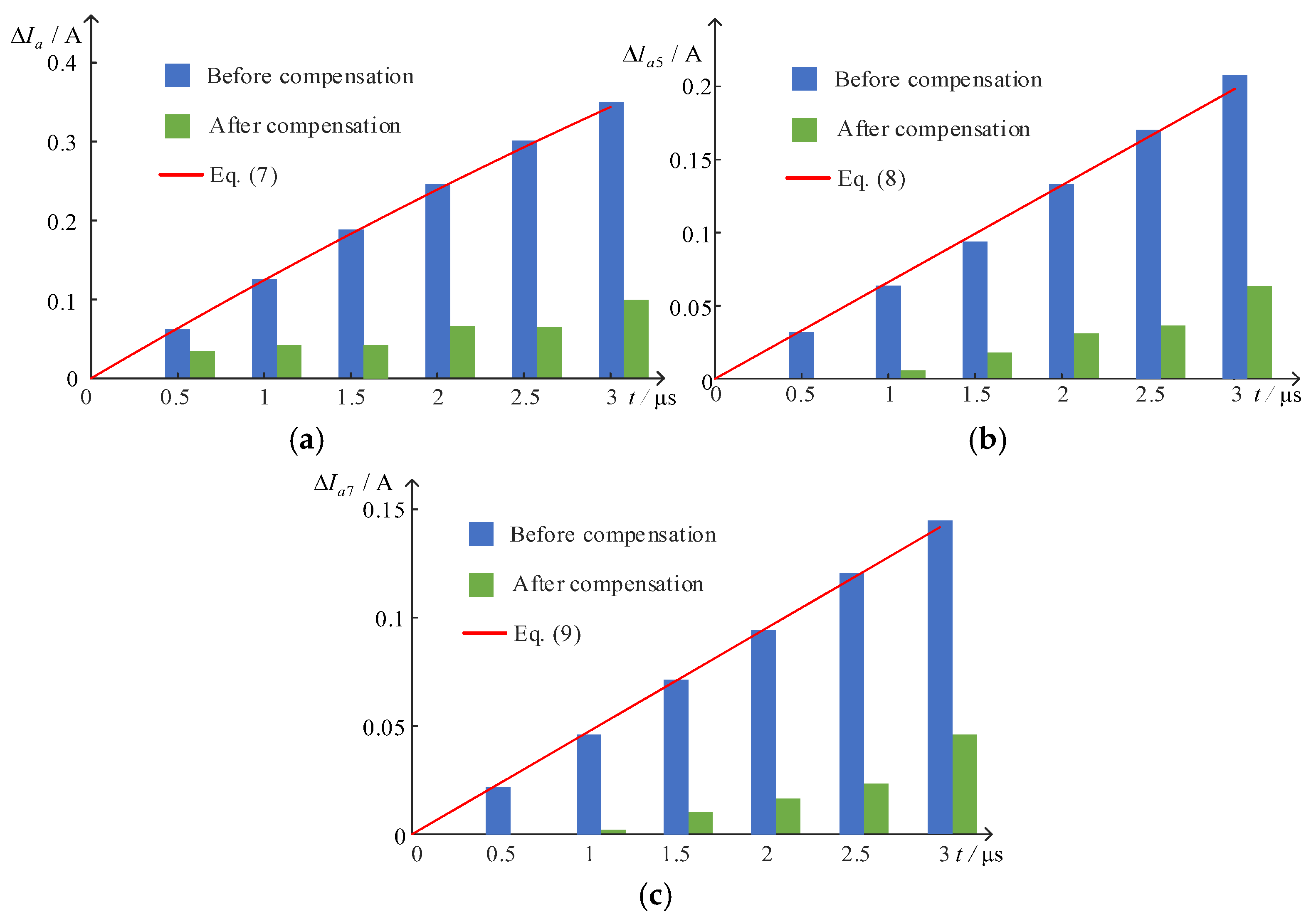

3.2. Current Error Caused by the Overlap Time in a Carrier Period

4. Analysis of Harmonic Characteristics and Compensation Method for Overlap Time

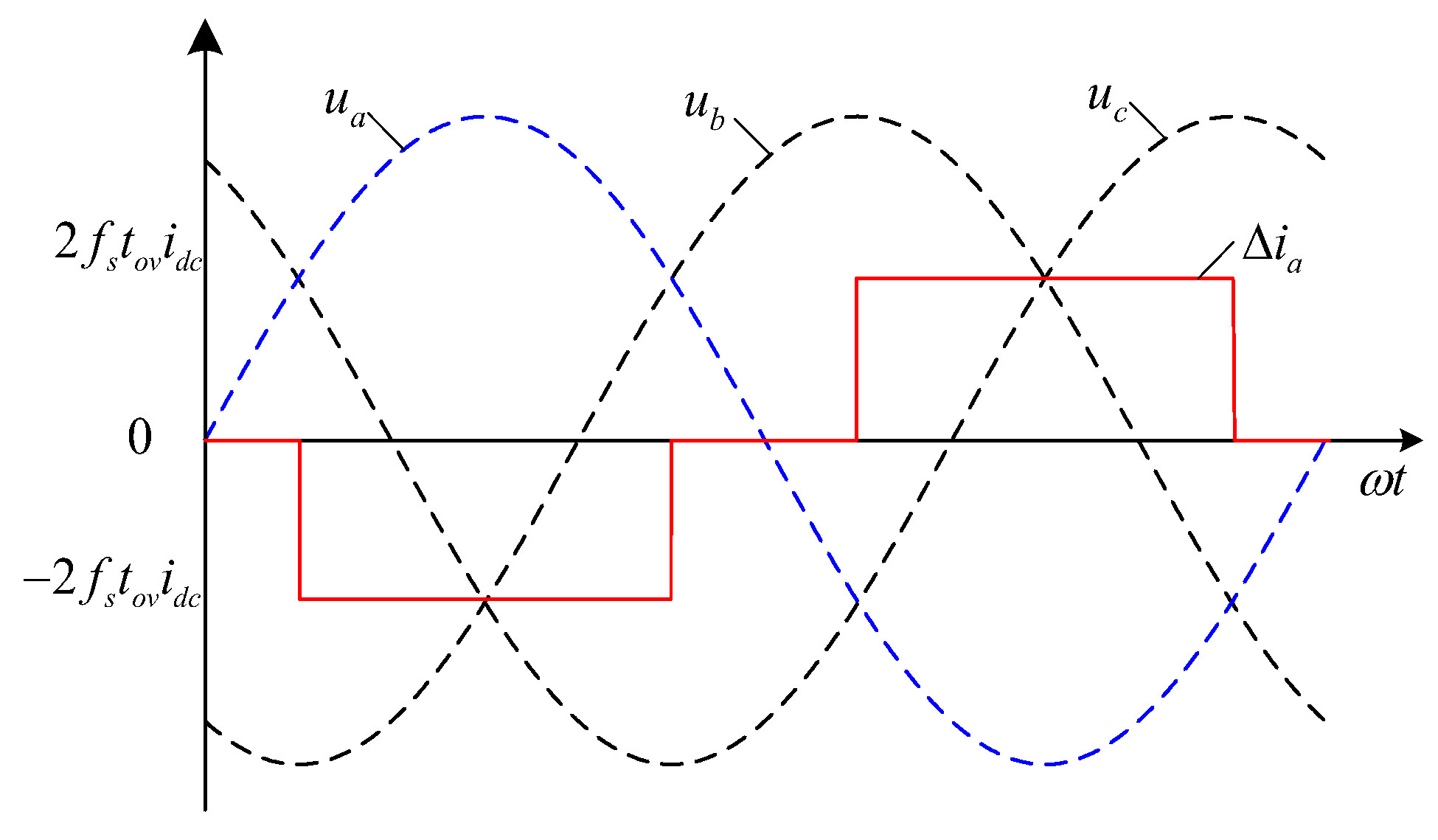

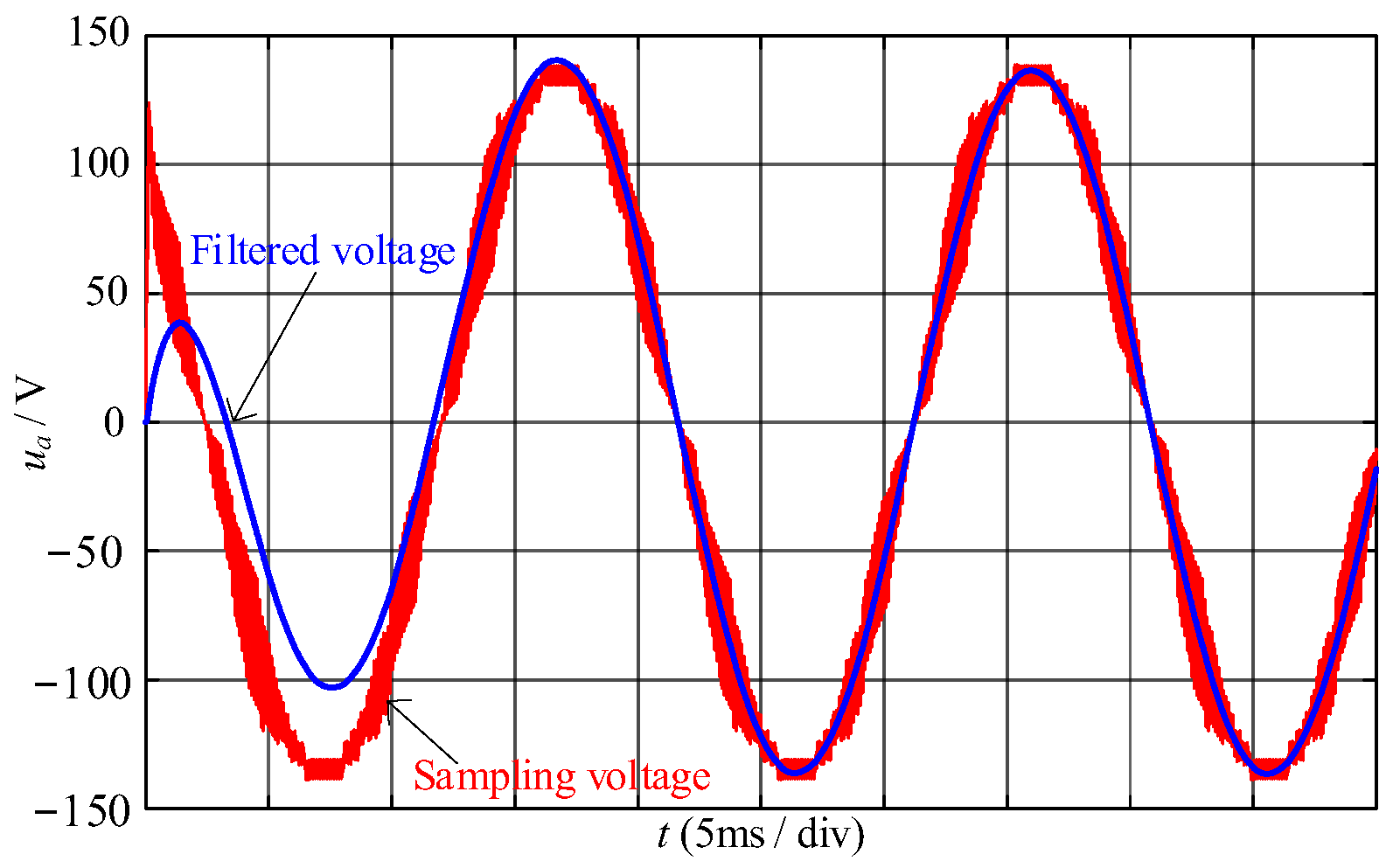

4.1. Harmonic Characteristics for Overlap Time

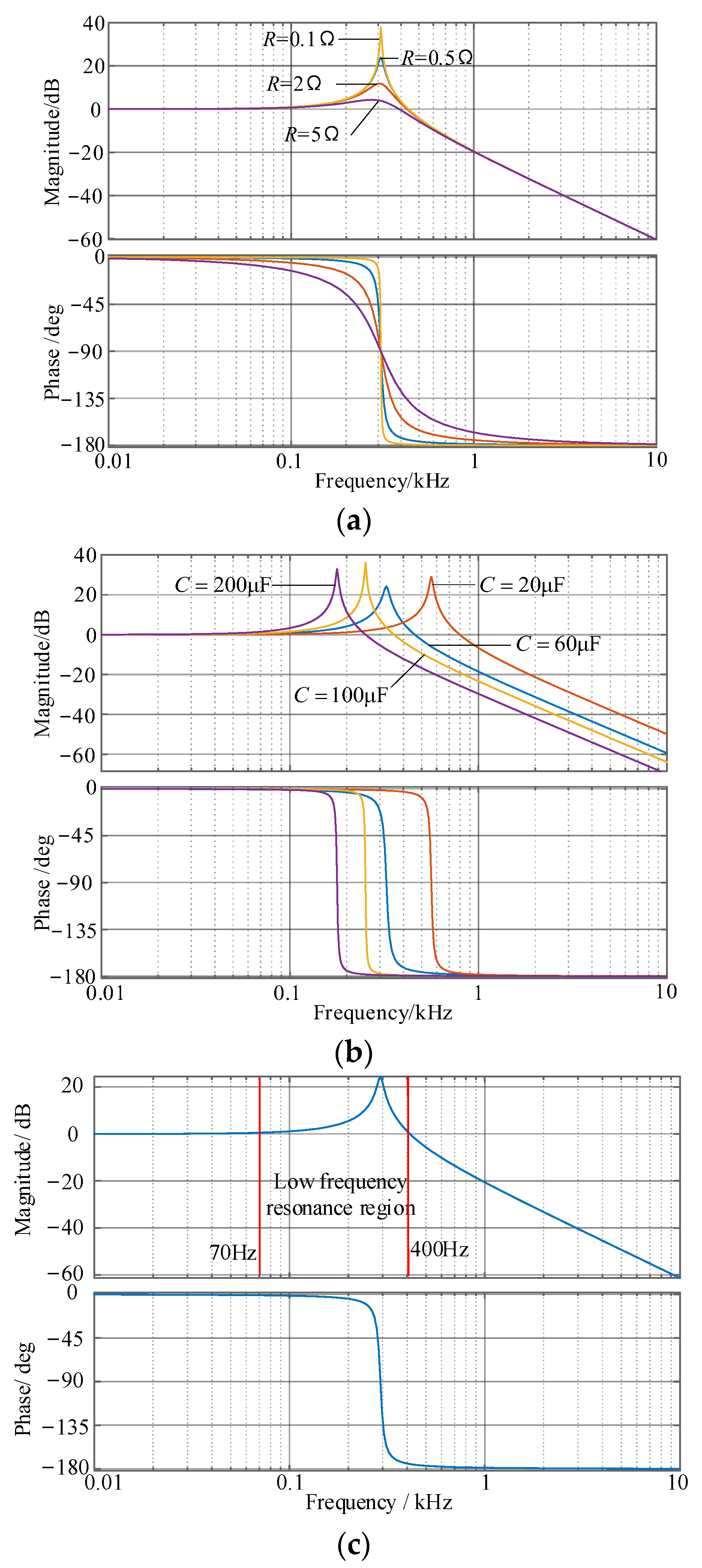

4.2. Parameters Design for L, C, and R

4.3. Analysis of Harmonic Losses Caused by Overlap Time

4.4. Compensation Scheme of the Overlap Time

5. Simulation and Experimental Verification

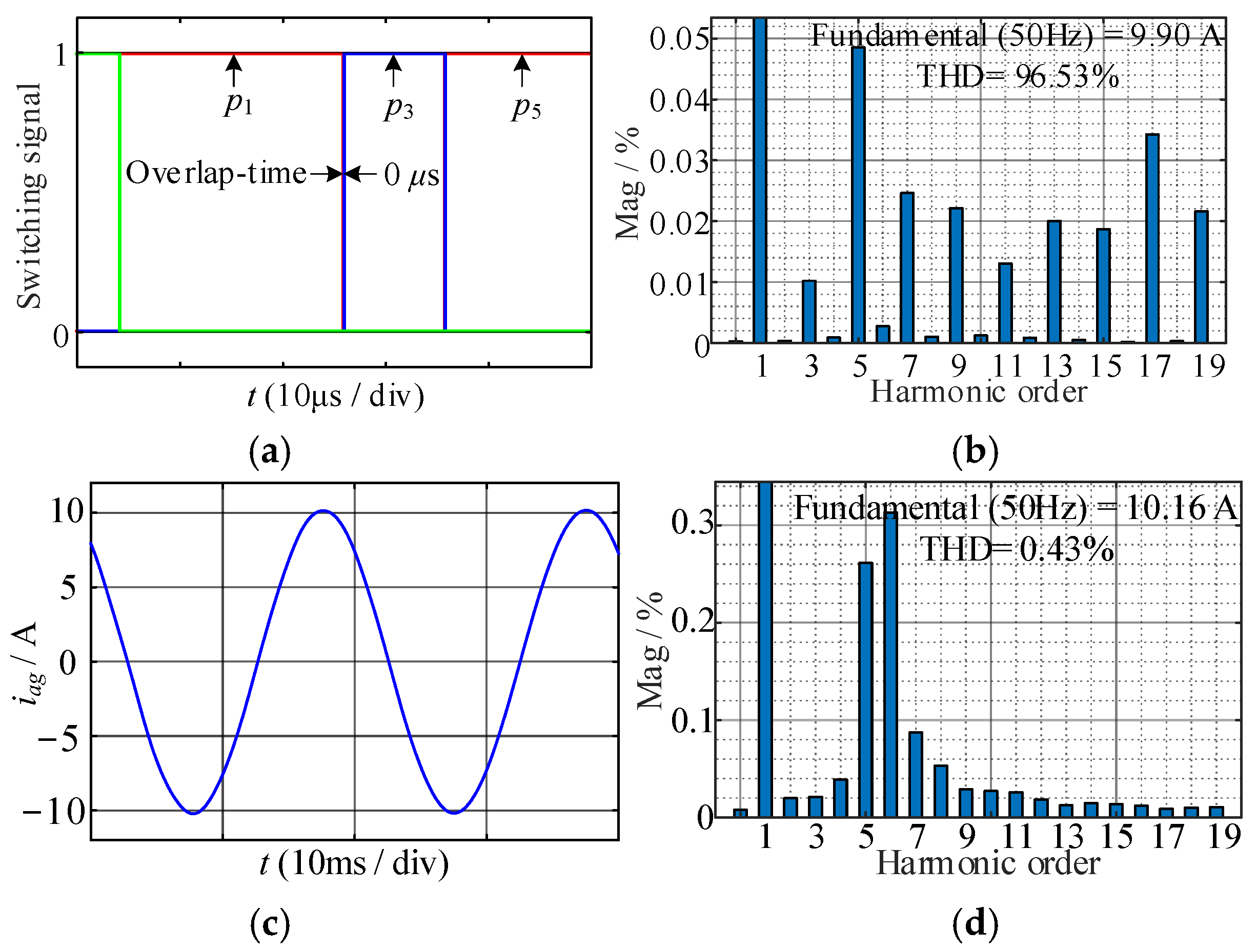

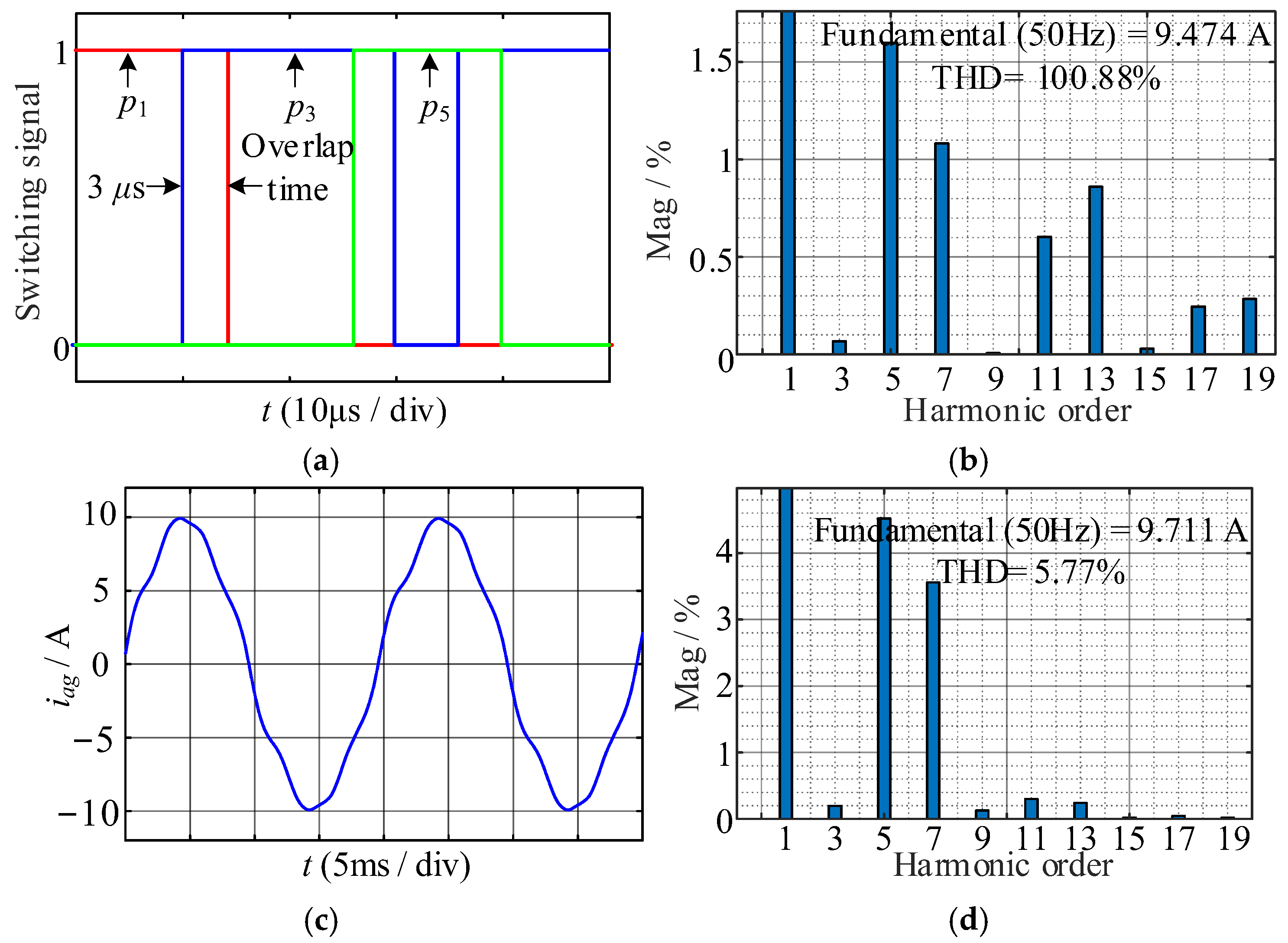

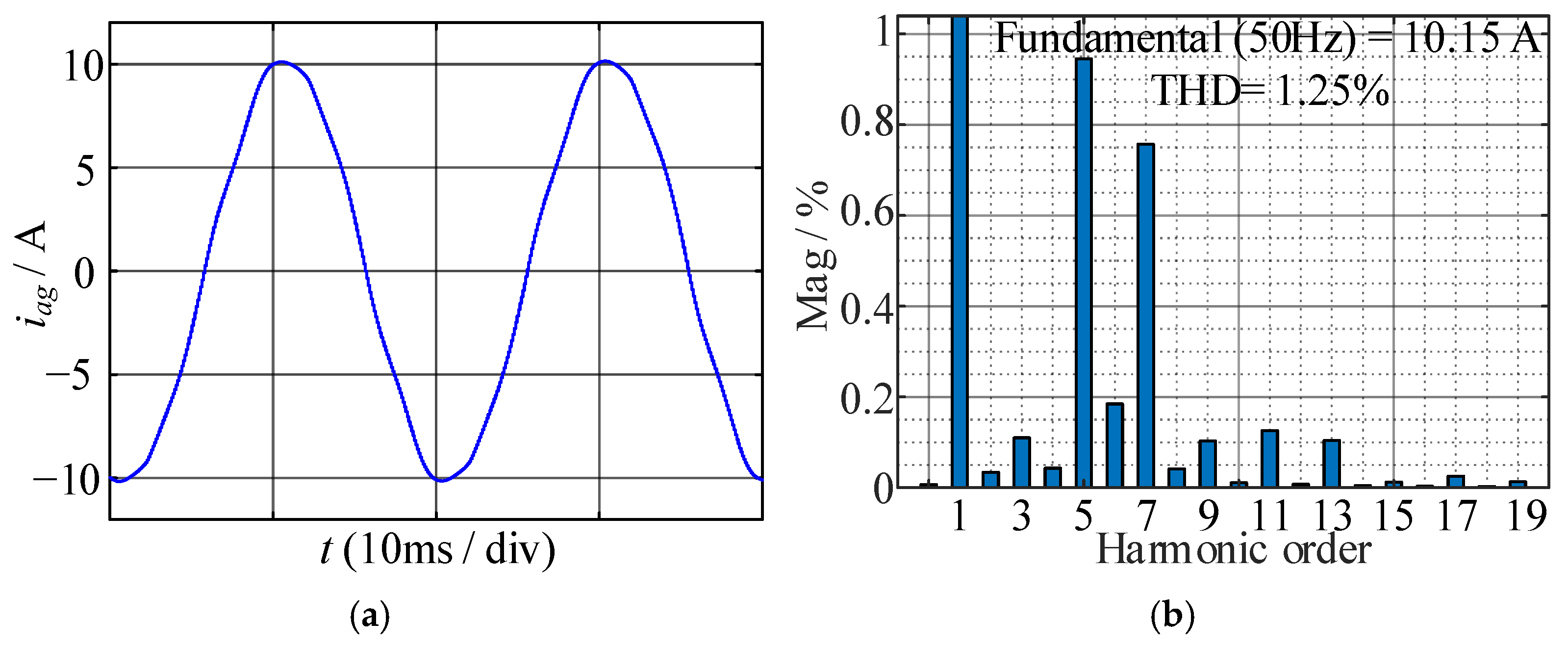

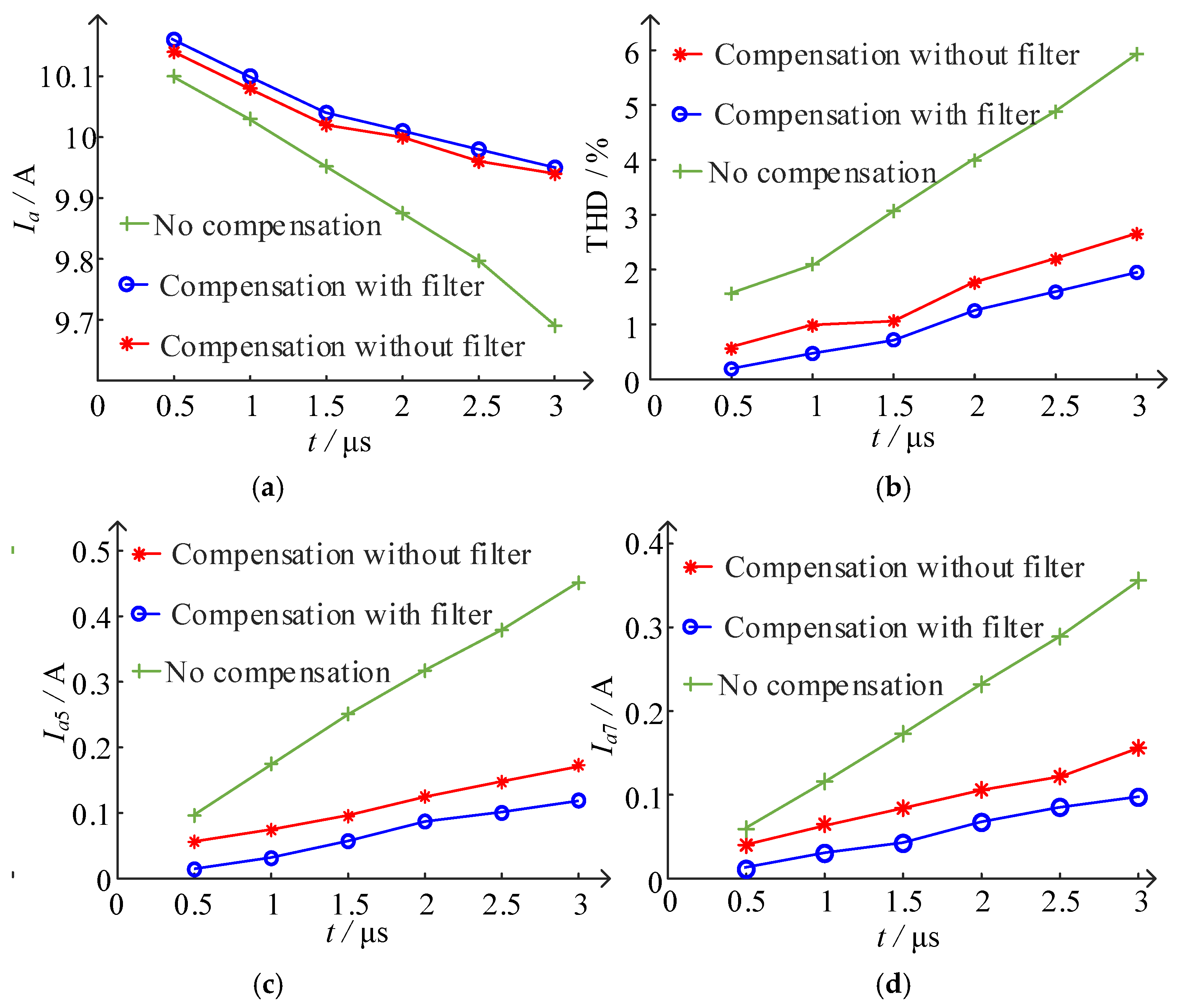

5.1. Simulation Results and Analysis

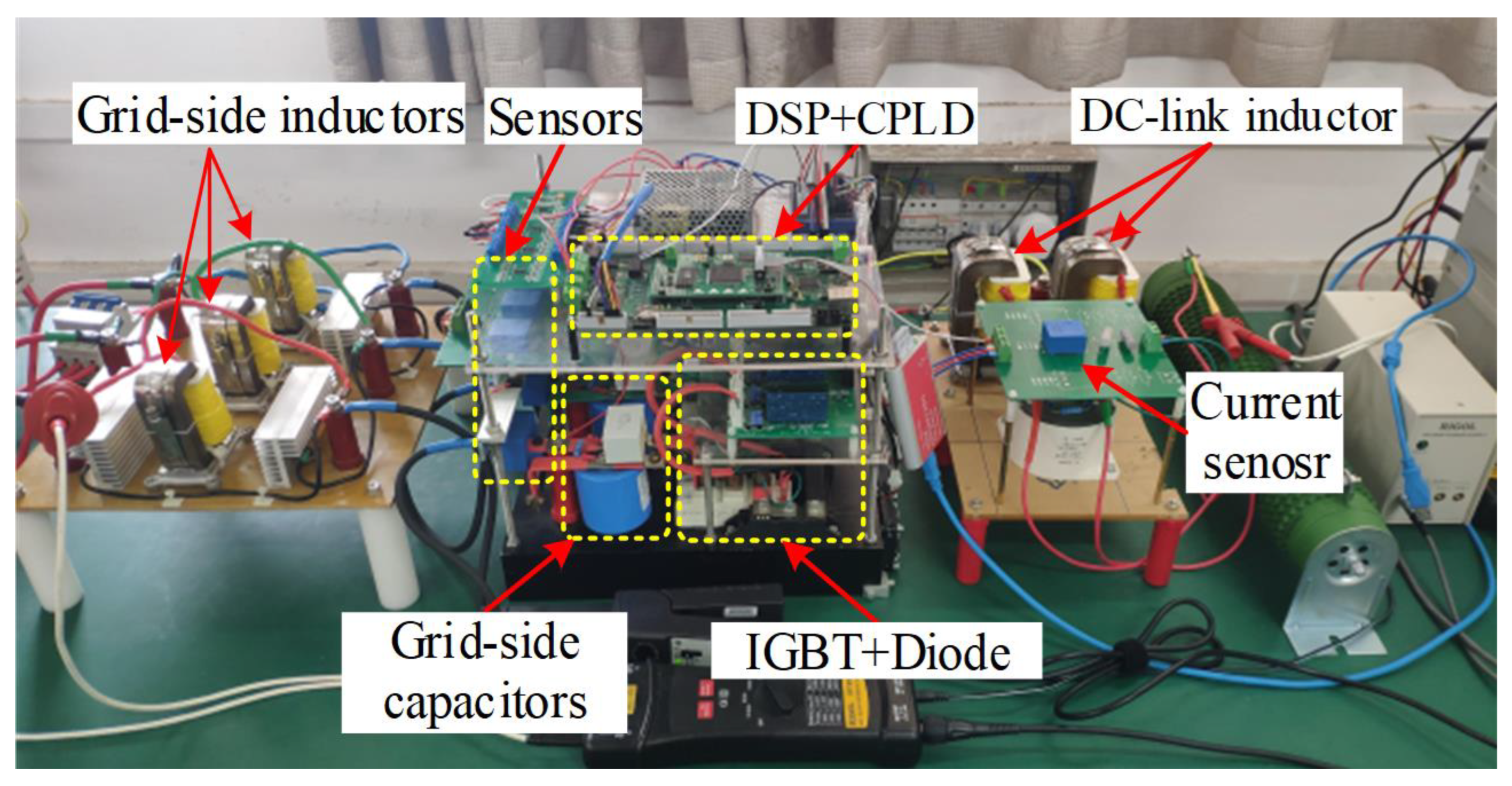

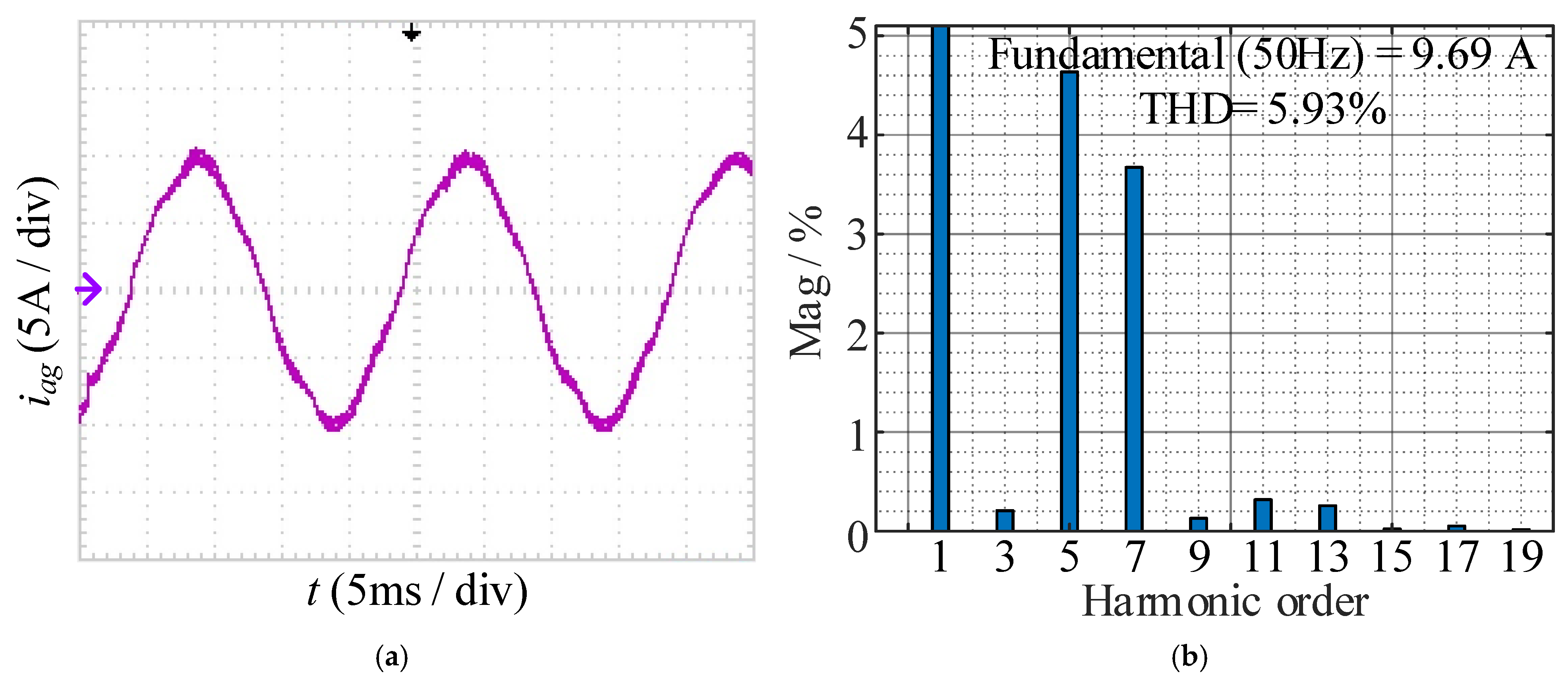

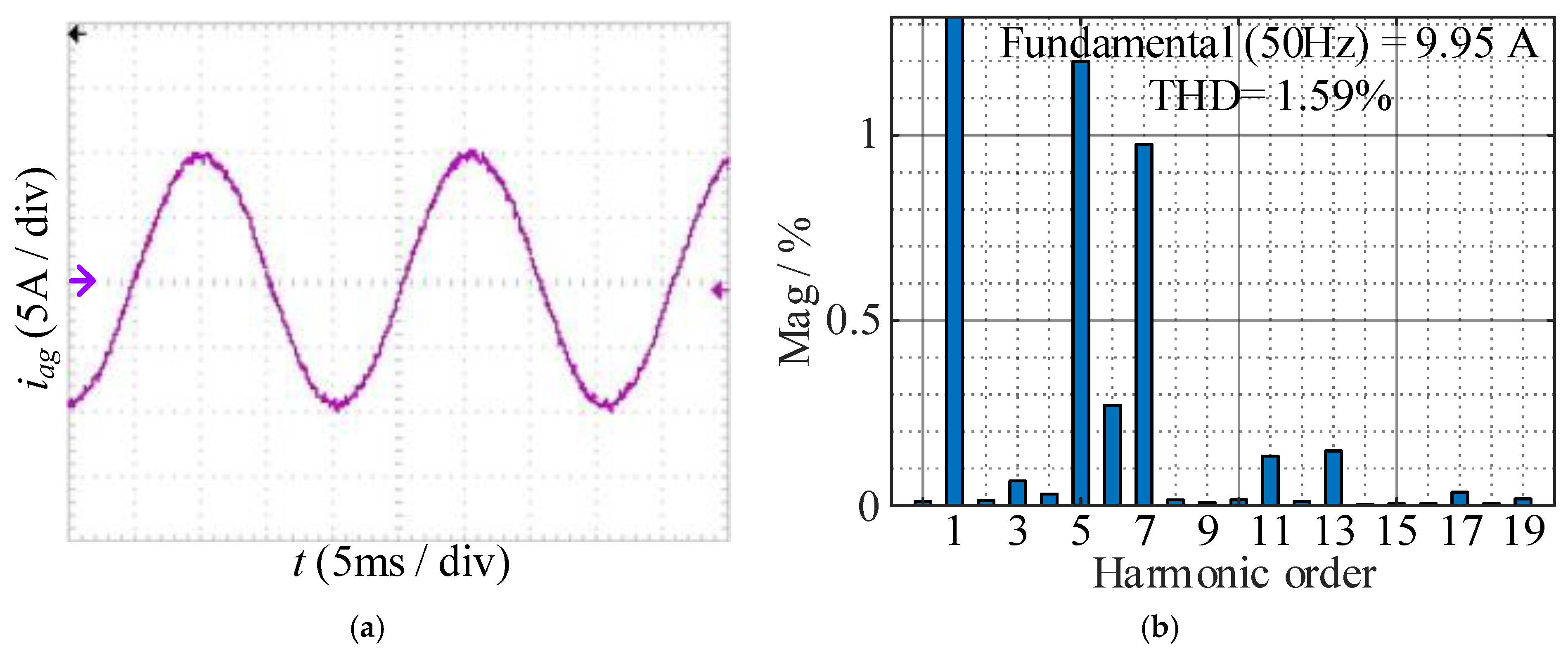

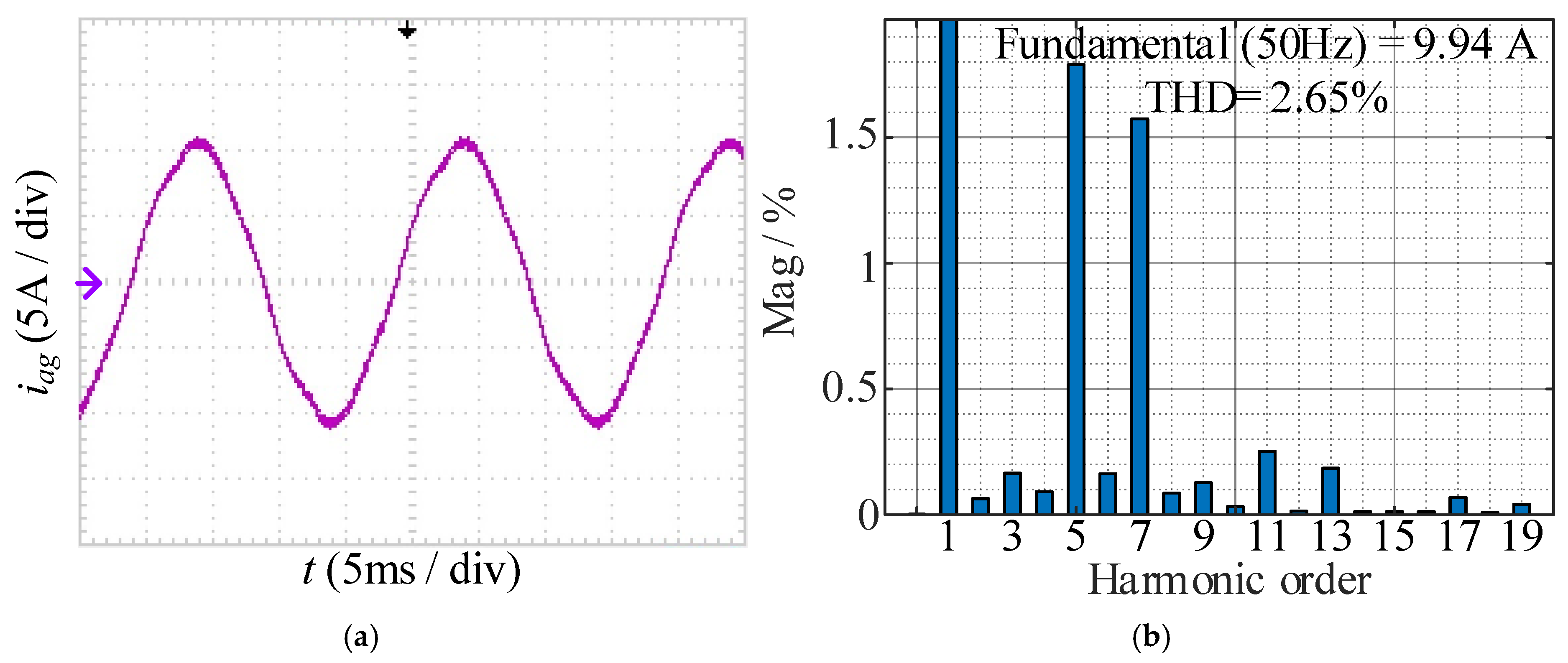

5.2. Experimental Results and Analysis

6. Conclusions

- (1)

- The current error during the overlap time is only determined by the relation of the AC-side voltage; it is not related to the sector of the target current vector.

- (2)

- The overlap time leads to a decrease in the fundamental wave and an increase in the low-order odd harmonics in the inverter-side current. Due to the LC resonance, the fifth and seventh harmonics in the grid-side current will further increase.

- (3)

- Since the AC-side voltage can be accurately obtained, the nonlinear errors caused by the overlap time can be significantly reduced by the proposed compensation scheme.

- (4)

- The proposed approach is dependent on the sampling accuracy of the filter capacitor voltage. Further research can focus on the control system bandwidth design and active damping method to suppress the harmonic distortion caused by the overlap time, eliminating the need for the sampling of the voltage.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Dong, Z.; Wen, H.; Song, Z.; Liu, C. 3-D SVM for Three-Phase Open-End Winding Drives with Common DC Bus. IEEE Trans. Power Electron. 2023, 38, 9340–9346. [Google Scholar] [CrossRef]

- Song, P.; Liu, Y.; Liu, C. Research on Parameter Design and Control Method for Current Source Inverter–Fed IM Drive Systems. Machines 2022, 10, 922. [Google Scholar] [CrossRef]

- Liu, J.; Yang, M.; Tao, W. Impedance-Based Stability Analysis of Grid-Tied Photovoltaic System With Superconducting Magnetic Energy Storage System. IEEE Trans. Appl. Supercond. 2021, 31, 1–4. [Google Scholar] [CrossRef]

- Lin, Z.; Ruan, X.; Zhang, H.; Wu, L. A Generalized Real-Time Computation Method with Dual-Sampling Mode to Eliminate the Computation Delay in Digitally Controlled Inverters. IEEE Trans. Power Electron. 2021, 37, 5186–5195. [Google Scholar] [CrossRef]

- Freddy, T.K.S.; Rahim, N.A.; Hew, W.-P.; Che, H.S. Modulation techniques to reduce leakage current in three-phase transformerless H7 photovoltaic inverter. IEEE Trans. Ind. Electron. 2014, 62, 322–331. [Google Scholar] [CrossRef]

- Zhao, T.; Zhang, X.; Mao, W.; Wang, F.; Xu, J.; Gu, Y. A Modified Hybrid Modulation Strategy for Suppressing DC Voltage Fluctuation of Cascaded H-Bridge Photovoltaic Inverter. IEEE Trans. Ind. Electron. 2017, 65, 3932–3941. [Google Scholar] [CrossRef]

- Xing, L.; Wei, Q. Series-Connected Current Source Inverters with Less Switches. IEEE Trans. Power Electron. 2019, 35, 5553–5556. [Google Scholar] [CrossRef]

- Wang, W.; Gao, F.; Yang, Y.; Blaabjerg, F. An Eight-Switch Five-Level Current Source Inverter. IEEE Trans. Power Electron. 2019, 34, 8389–8404. [Google Scholar] [CrossRef]

- He, J.; Li, Q.; Zhang, C.; Han, J.; Wang, C. Quasi-Selective Harmonic Elimination (Q-SHE) Modulation-Based DC Current Balancing Method for Parallel Current Source Converters. IEEE Trans. Power Electron. 2018, 34, 7422–7436. [Google Scholar] [CrossRef]

- Rajeev, M.; Agarwal, V. Single Phase Current Source Inverter With Multiloop Control for Transformerless Grid–PV Interface. IEEE Trans. Ind. Appl. 2018, 54, 2416–2424. [Google Scholar] [CrossRef]

- Chen, D.; Jiang, J.; Qiu, Y.; Zhang, J.; Huang, F. Single-Stage Three-Phase Current-Source Photovoltaic Grid-Connected Inverter High Voltage Transmission Ratio. IEEE Trans. Power Electron. 2016, 32, 7591–7601. [Google Scholar] [CrossRef]

- Azghandi, M.A.; Barakati, S.M.S.; Yazdani, A. Impedance-Based Stability Analysis and Design of a Fractional-Order Active Damper for Grid-Connected Current-Source Inverters. IEEE Trans. Sustain. Energy 2020, 12, 599–611. [Google Scholar] [CrossRef]

- Miao, Y.; Liao, W.; Huang, S.; Liu, P.; Wu, X.; Song, P.; Li, G. DC-Link Current Minimization Scheme for IM Drive System Fed by Bidirectional DC Chopper-Based CSI. IEEE Trans. Transp. Electrif. 2022, 9, 2839–2850. [Google Scholar] [CrossRef]

- Guo, X.-Q.; Sui, S.; Wang, B.; Zhang, W. A Current-Based Approach for Short-Circuit Fault Diagnosis in Closed-Loop Current Source Inverter. IEEE Trans. Ind. Electron. 2019, 67, 7941–7950. [Google Scholar] [CrossRef]

- Guo, X.; Du, S.; Diao, N.; Hua, C.; Blaabjerg, F. Three-Dimensional Space Vector Modulation for Four-Leg Current-Source Inverters. IEEE Trans. Power Electron. 2023, 38, 13122–13132. [Google Scholar] [CrossRef]

- Zhang, Y.; Yang, T.; Miao, Y. Research on the Modulation and Control Strategy for a Novel Single-Phase Current Source Inverter. Energies 2023, 16, 6729. [Google Scholar] [CrossRef]

- Barakat, M. Novel chaos game optimization tuned-fractional-order PID fractional-order PI controller for load–frequency control of interconnected power systems. Prot. Control Mod. Power Syst. 2022, 7, 1–20. [Google Scholar] [CrossRef]

- Chierchie, F.; Paolini, E.E.; Stefanazzi, L. Dead-Time Distortion Shaping. IEEE Trans. Power Electron. 2019, 34, 53–63. [Google Scholar] [CrossRef]

- Ding, L.; Li, Y.W.; Zargari, N.R. Discrete-time SMO sensorless control of current source converter-fed PMSM drives with low switching frequency. IEEE Trans. Ind. Electron. 2020, 68, 2120–2129. [Google Scholar] [CrossRef]

- Hwang, S.-H.; Kim, J.-M. Dead Time Compensation Method for Voltage-Fed PWM Inverter. IEEE Trans. Energy Convers. 2010, 25, 1–10. [Google Scholar] [CrossRef]

- Lee, J.-H.; Sul, S.-K. Inverter Nonlinearity Compensation Through Deadtime Effect Estimation. IEEE Trans. Power Electron. 2021, 36, 10684–10694. [Google Scholar] [CrossRef]

- Wang, W.; Gao, F.; Yang, Y.; Blaabjerg, F. Operation and modulation of H7 current-source inverter with hybrid SiC and Si semiconductor switches. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 6, 387–399. [Google Scholar] [CrossRef]

- Gaber, M.; Abdel-Rahim, O.M.; Orabi, M. Novel Overlap Method to Eliminate Vector Deviation Error in SVM of Current Source Inverters. IEEE Trans. Power Electron. 2020, 36, 2320–2333. [Google Scholar] [CrossRef]

- Guo, B.; Xu, F.; Zhang, Z.; Xu, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J. Compensation of Input Current Distortion in Three-phase Buck Rectifiers. In Proceedings of the 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 17–21 March 2013; pp. 930–938. [Google Scholar]

- Qin, H.; Zhang, X.; Zhu, Z.; Ma, C.; Xu, H. Influence of overlap-time on the ac grid-side current of current source PWM rectifier and restraining method. Trans. China Electrotech. Soc. 2016, 31, 142–152. [Google Scholar]

- Geng, Y.; Deng, R.; Dong, W.; Wang, K.; Liu, H.; Wu, X. An Overlap-Time Compensation Method for Current-Source Space-Vector PWM Inverters. IEEE Trans. Power Electron. 2017, 33, 3192–3203. [Google Scholar] [CrossRef]

- Guo, X. A Novel CH5 Inverter for Single-Phase Transformerless Photovoltaic System Applications. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 1197–1201. [Google Scholar] [CrossRef]

- Guo, Q.; Liu, H.; Peng, D.; Liu, Q. A Current-Source Charging System Considering the Characteristics of Battery. Trans. China Electrotech. Soc. 2016, 31, 16–25. [Google Scholar]

- Guo, Q.; Zhou, C.; Li, S. A Multiple Loops Control Strategy Based on DC Link Voltage of Current Source PWM Rectifiers. Trans. China Electrotech. Soc. 2022, 37, 2051–2063. [Google Scholar]

| Relation of AC Voltage | ∆ia | ∆ib | ∆ic |

|---|---|---|---|

| ua > ub > uc | −2fstovidc | 0 | 2fstovidc |

| ua > uc > ub | −2fstovidc | 2fstovidc | 0 |

| ub > ua > uc | 0 | −2fstovidc | 2fstovidc |

| ub > uc > ua | 2fstovidc | −2fstovidc | 0 |

| uc > ua > ub | 0 | 2fstovidc | −2fstovidc |

| uc > ub > ua | 2fstovidc | 0 | −2fstovidc |

| Overlap- Time (μs) | Fundamental Amplitude(A) | Fifth Harmonic Amplitude (A) | Seventh Harmonic Amplitude (A) | THD (%) |

|---|---|---|---|---|

| 0 | 9.90 | 0.005 | 0.003 | 96.53 |

| 0.5 | 9.835 | 0.037 | 0.025 | 97.20 |

| 1 | 9.776 | 0.069 | 0.049 | 97.89 |

| 1.5 | 9.713 | 0.098 | 0.074 | 98.61 |

| 2 | 9.656 | 0.140 | 0.097 | 99.35 |

| 2.5 | 9.592 | 0.175 | 0.122 | 100.09 |

| 3 | 9.543 | 0.213 | 0.148 | 100.88 |

| Overlap- Time (μs) | Fundamental Amplitude(A) | Fifth Harmonic Amplitude (A) | Seventh Harmonic Amplitude (A) | THD (%) |

|---|---|---|---|---|

| 0.5 | 9.897 | 0.005 | 0.003 | 96.55 |

| 1 | 9.896 | 0.009 | 0.005 | 96.56 |

| 1.5 | 9.896 | 0.017 | 0.009 | 96.57 |

| 2 | 9.890 | 0.028 | 0.018 | 96.57 |

| 2.5 | 9.890 | 0.041 | 0.027 | 96.57 |

| 3 | 9.876 | 0.068 | 0.049 | 96.65 |

| 0.5 | 9.897 | 0.005 | 0.003 | 96.55 |

| Category | Part Number | Parameter |

|---|---|---|

| AC voltage simulator | Chroma 61830 | 100 V |

| DC input voltage | DS1020 | 50 V |

| Controller | TMS320F28335 + CPLD | / |

| Voltage sensor | LV28-P | / |

| Current sensor | LA200-p | / |

| Switching tube | FF100R12RT4 | / |

| Diode | MEA75-12DA | / |

| DC-link inductance | / | 8 mH |

| AC-side inductance | / | 4 mH |

| AC-side capacitance | / | 66 µF |

| AC-side resistance | / | 0.5 Ω |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xu, C.; Liu, P.; Miao, Y. Overlap Time Compensation and Characteristic Analysis for Current Source Photovoltaic Grid-Connected Inverter. Energies 2024, 17, 1768. https://doi.org/10.3390/en17071768

Xu C, Liu P, Miao Y. Overlap Time Compensation and Characteristic Analysis for Current Source Photovoltaic Grid-Connected Inverter. Energies. 2024; 17(7):1768. https://doi.org/10.3390/en17071768

Chicago/Turabian StyleXu, Cheng, Ping Liu, and Yiru Miao. 2024. "Overlap Time Compensation and Characteristic Analysis for Current Source Photovoltaic Grid-Connected Inverter" Energies 17, no. 7: 1768. https://doi.org/10.3390/en17071768

APA StyleXu, C., Liu, P., & Miao, Y. (2024). Overlap Time Compensation and Characteristic Analysis for Current Source Photovoltaic Grid-Connected Inverter. Energies, 17(7), 1768. https://doi.org/10.3390/en17071768