Monolithic Integration of Nano-Ridge Engineered InGaP/GaAs HBTs on 300 mm Si Substrate

Abstract

:1. Introduction

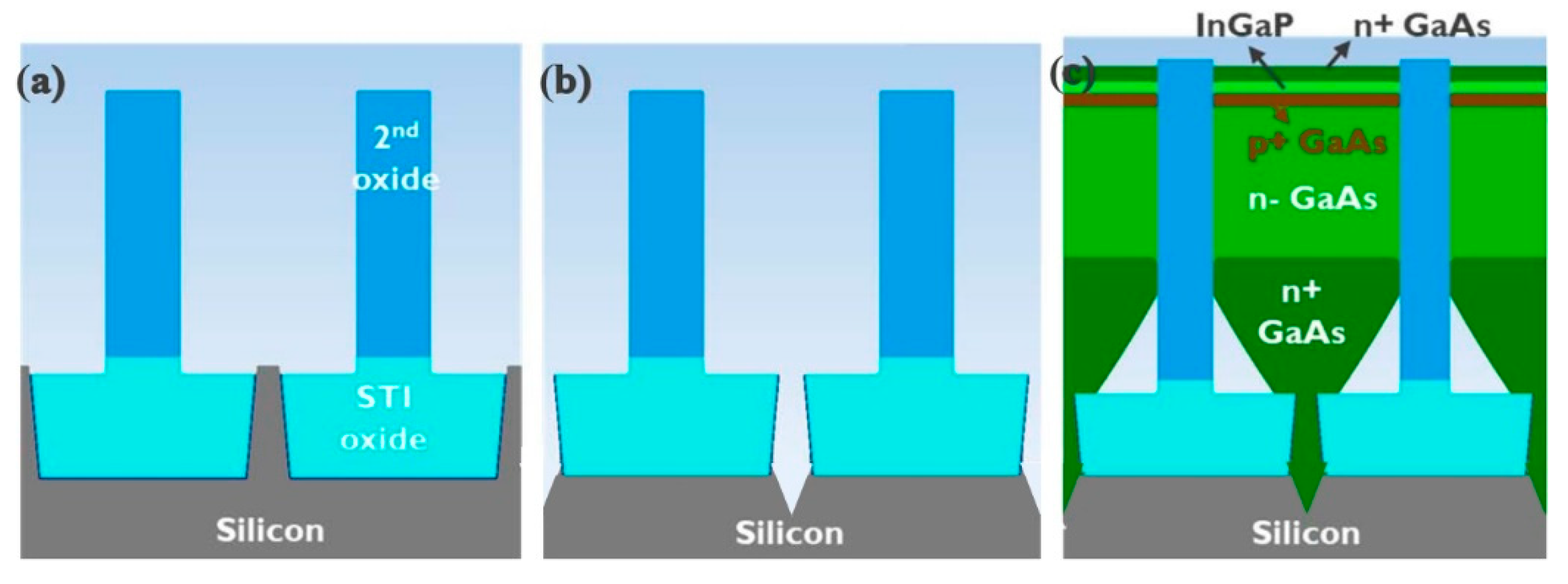

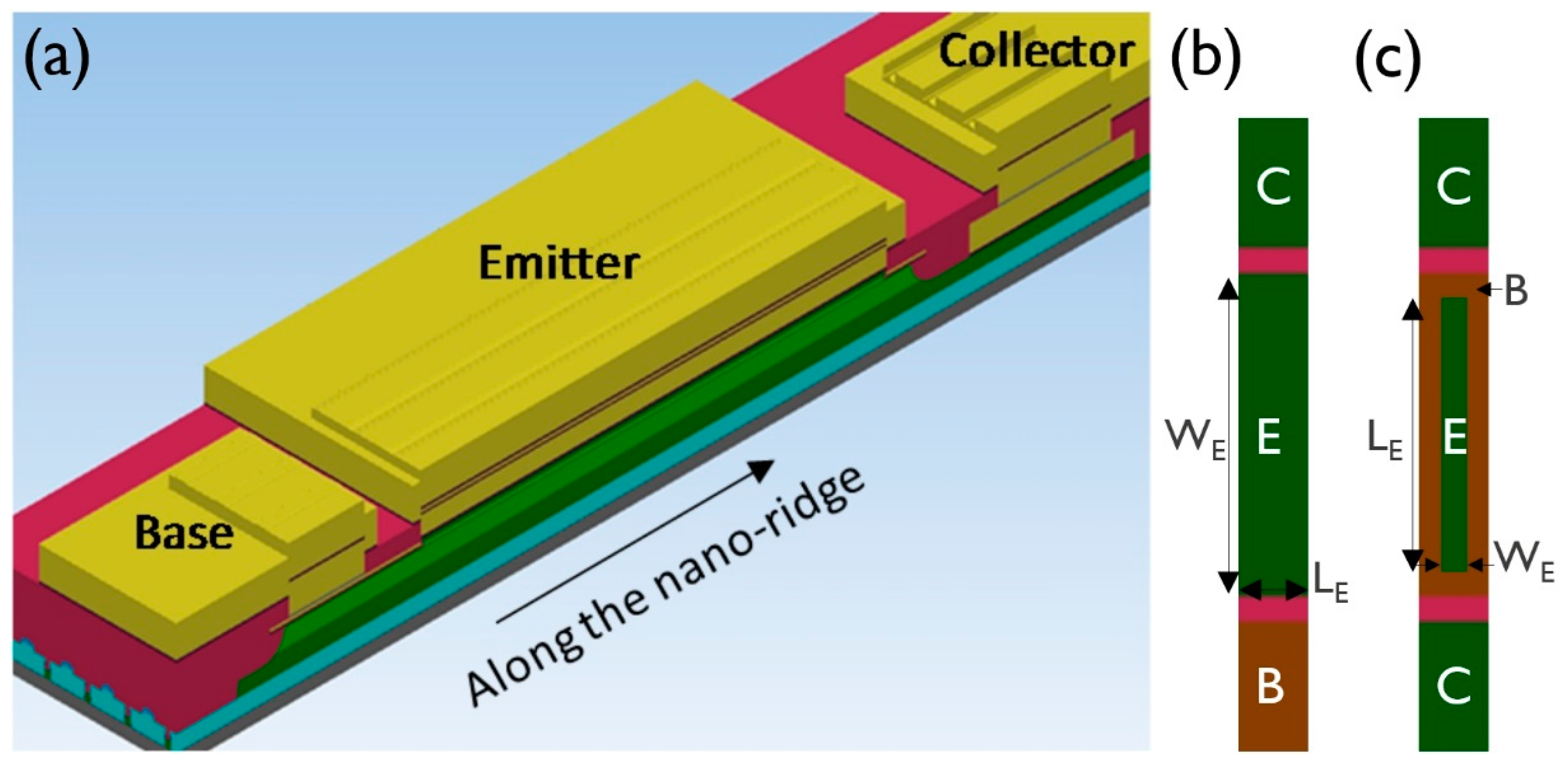

2. Materials and Methods

3. Results and Discussion

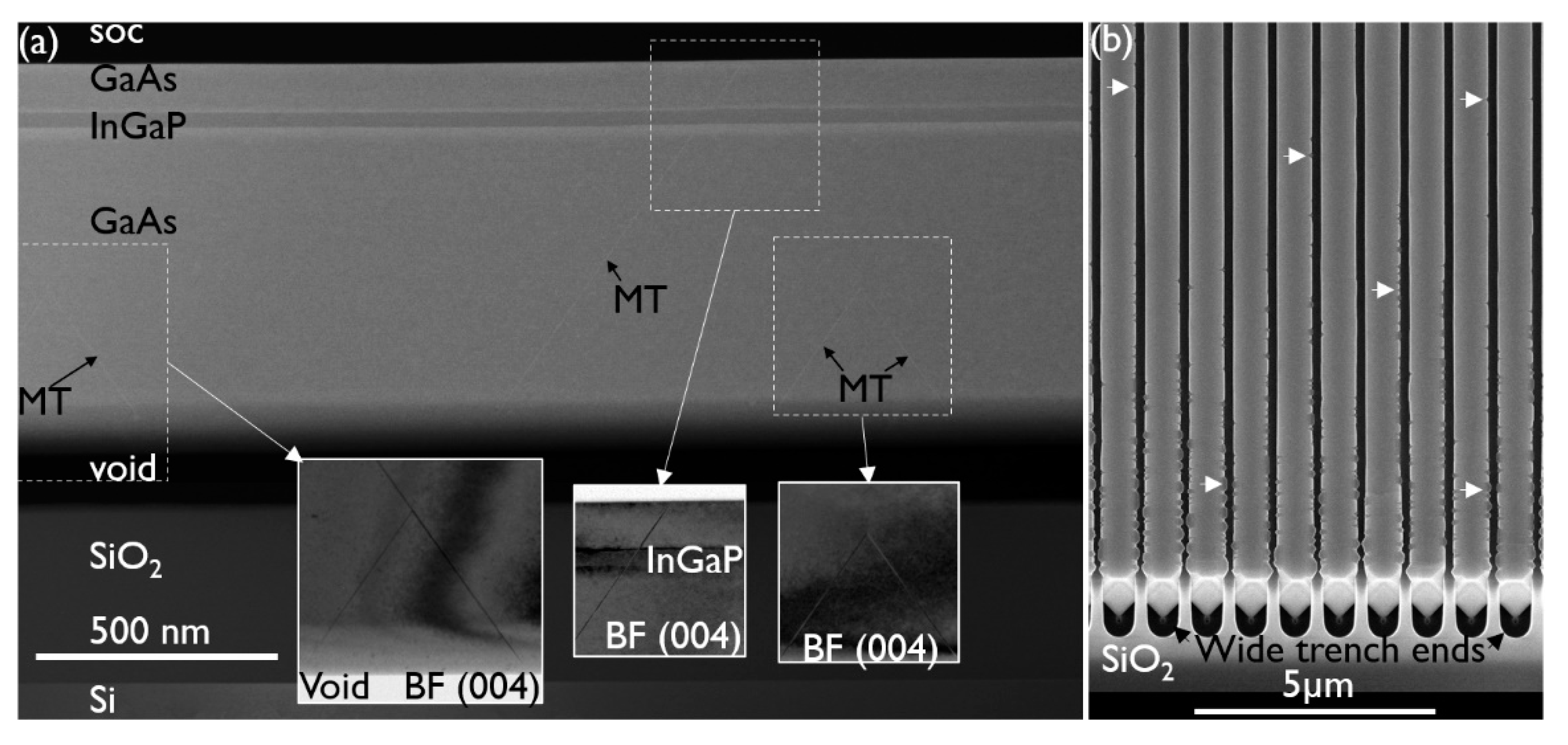

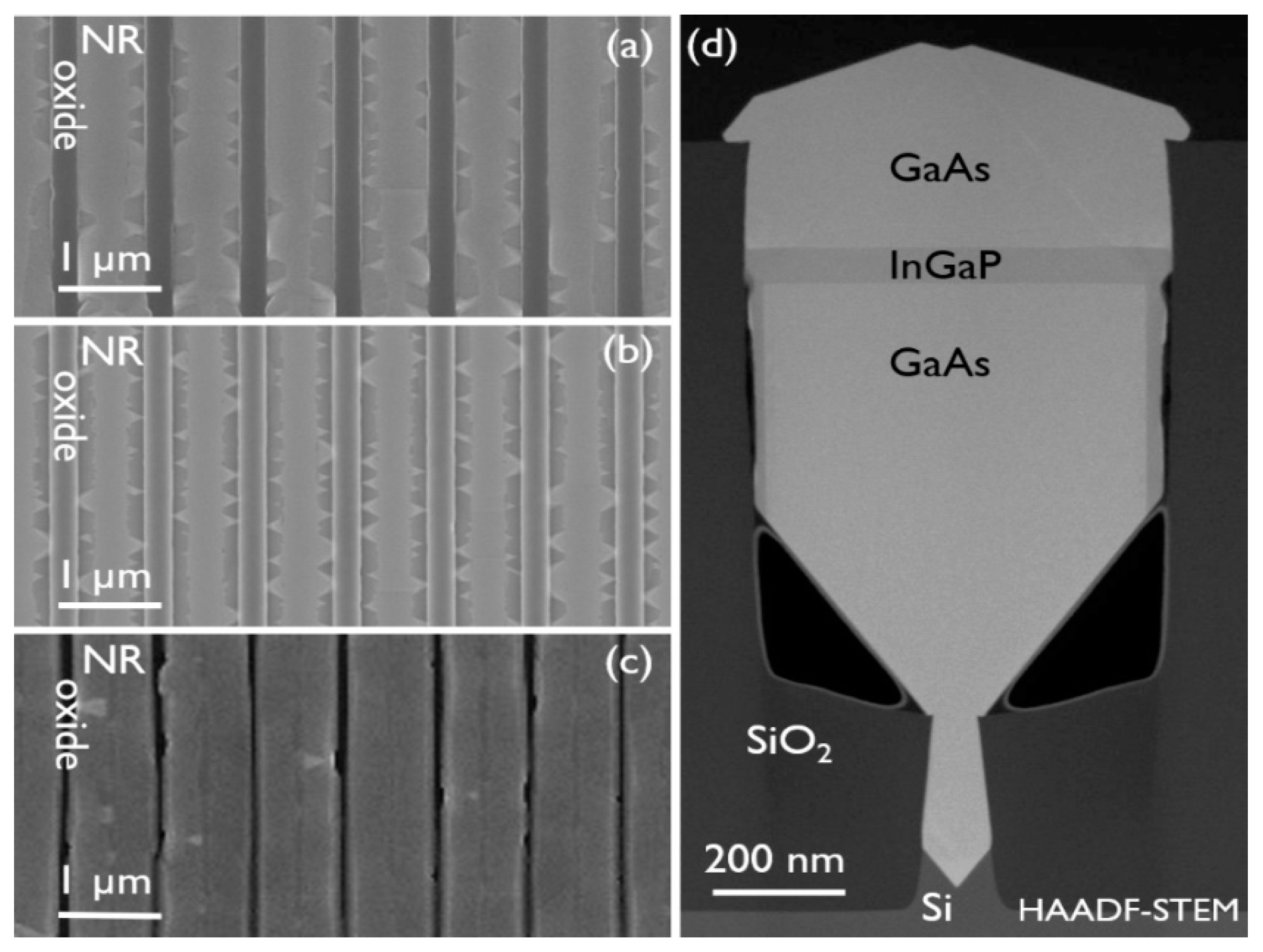

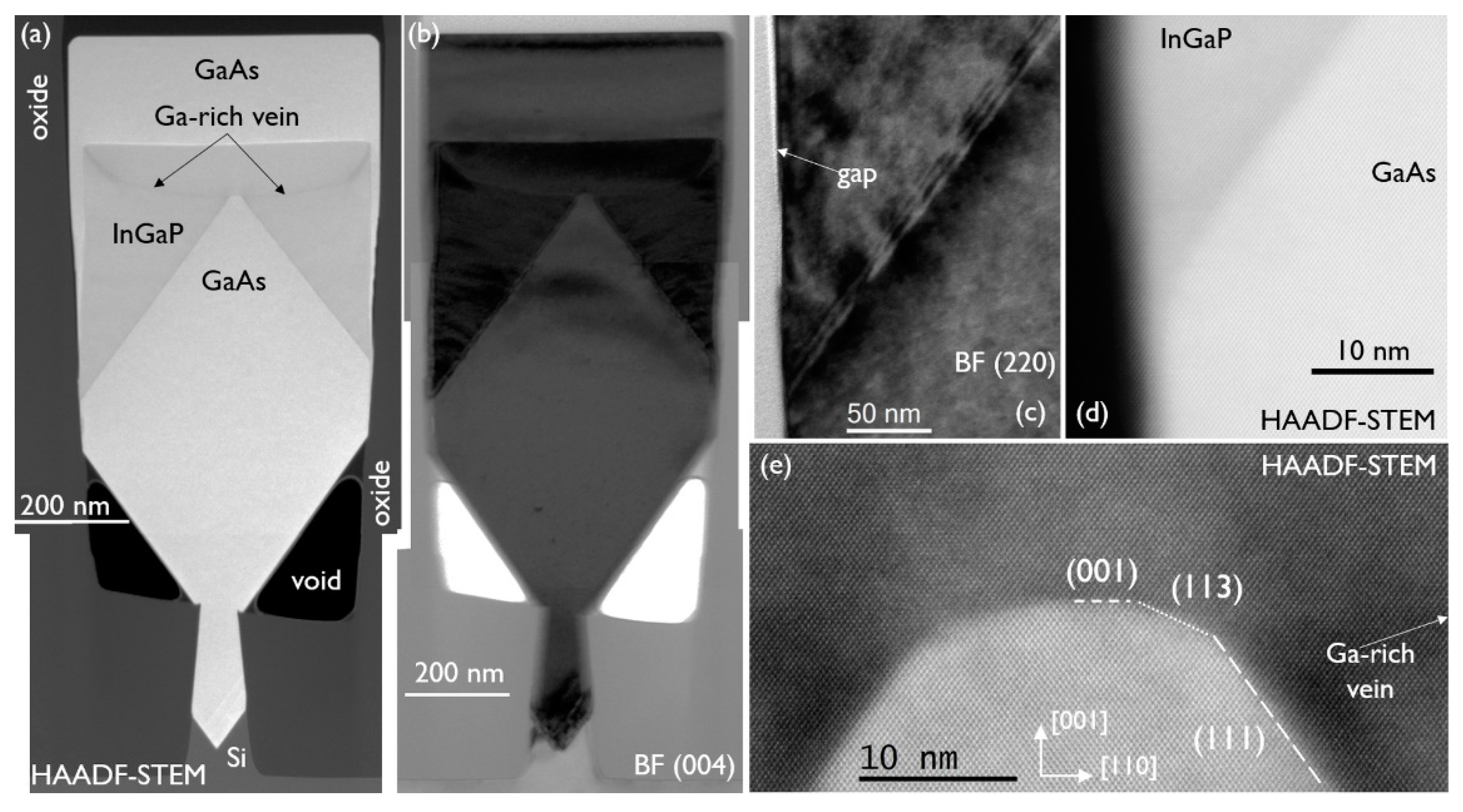

3.1. Structural Analysis of InGaP/GaAs HBT Stack

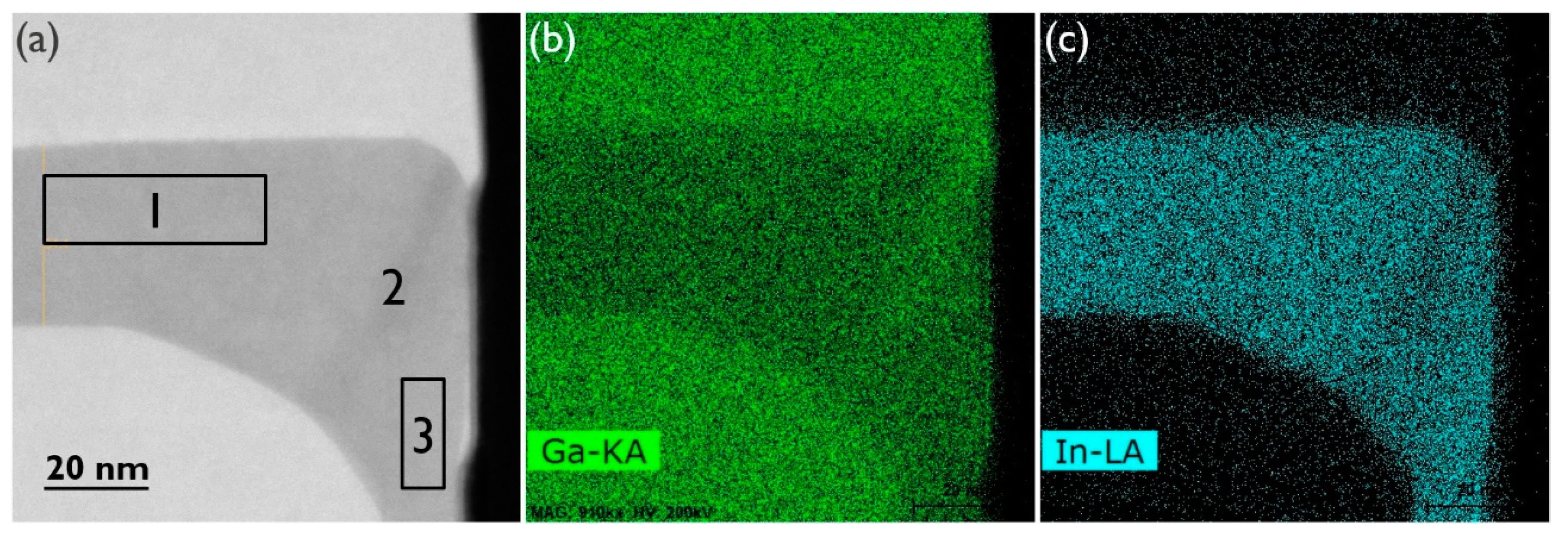

3.2. Systematic Growth Study into the Origin of the Observed Defectiveness

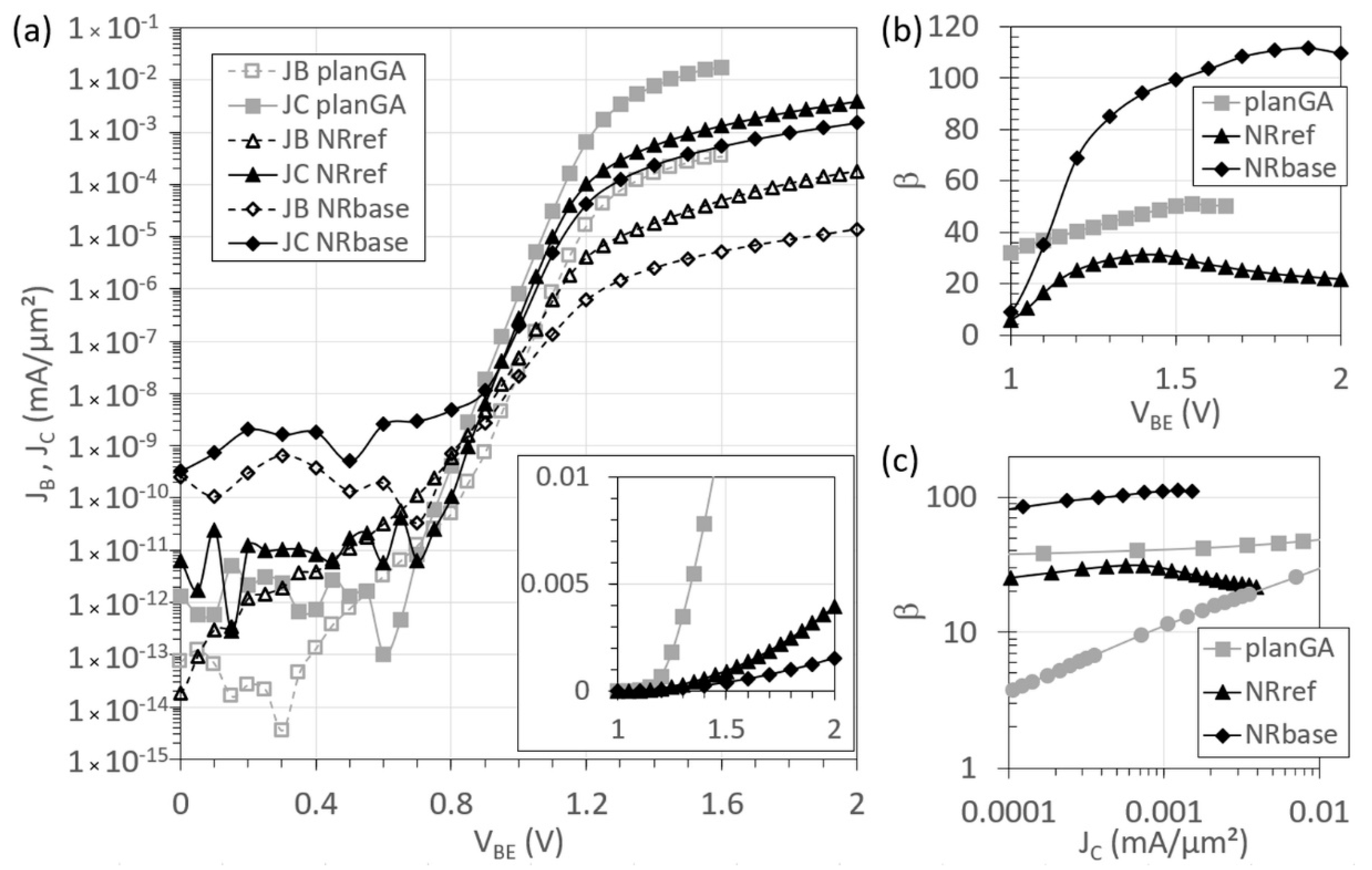

3.3. InGaP/GaAs HBT Device Performance

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Asbeck, P.M.; Rostomyan, N.; Ozen, M.; Rabet, B.; Jayamon, J.A. Power Amplifiers for mm-Wave 5G Applications: Technology Comparisons and CMOS-SOI Demonstration Circuits. IEEE Trans. Microw. Theory Tech. 2019, 67, 3099–3109. [Google Scholar] [CrossRef]

- Parvais, B.; Peralagu, U.; Vais, A.; Alian, A.; Witters, L.; Mols, Y.; Walke, A.; Ingels, M.; Yu, H.; Putcha, V.; et al. (Invited) Advanced Transistors for High Frequency Applications. ECS Trans. 2020, 97, 27–38. [Google Scholar] [CrossRef]

- Green, D.S.; Dohrman, C.L.; Demmin, J.; Zheng, Y.; Chang, T.-H. A Revolution on the Horizon from DARPA: Heterogeneous Integration for Revolutionary Microwave\/Millimeter-Wave Circuits at DARPA: Progress and Future Directions. IEEE Microw. Mag. 2017, 18, 44–59. [Google Scholar] [CrossRef]

- Hamada, H.; Nosaka, H.; Tsutsumi, T.; Sugiyama, H.; Matsuzaki, H.; Song, H.J.; Itami, G.; Fujimura, T.; Abdo, I.; Okada, K. Millimeter-Wave InP Device Technologies for Ultra-High Speed Wireless Communications toward beyond 5G. In Proceedings of the IEEE International Electron Devices Meeting (IEDM) 2019, San Francisco, CA, USA, 7–11 December 2019; pp. 182–185. [Google Scholar] [CrossRef]

- Wang, H.; Huang, T.-Y.; Sasikanth Mannem, N.; Lee, J.; Garay, E.; Munzer, D.; Liu, E.; Liu, Y.; Lin, B.; Eleraky, M.; et al. Power Amplifiers Performance Survey 2000-Present. Available online: https://gems.ece.gatech.edu/PA_survey.html (accessed on 14 April 2021).

- Oka, T.; Hirata, K.; Ouchi, K.; Uchiyama, H.; Mochizuki, K.; Nakamura, T. InGaP/GaAs HBT’s with high-speed and low-current operation fabricated using WSi/Ti as the base electrode and burying SiO2 in the extrinsic collector. In Proceedings of the IEEE International Electron Devices Meeting (IEDM) 1997, Washington, DC, USA, 7–10 December 1997; pp. 739–742. [Google Scholar] [CrossRef]

- Fitzgerald, E.; Bulsara, M.T.; Bai, Y.; Cheng, C.; Liu, W.K.; Lubyshev, D.; Fastenau, J.; Wu, Y.; Urtega, M.; Ha, W.; et al. Monolithic III-V/Si Integration. ECS Trans. 2009, 19, 345–350. [Google Scholar] [CrossRef]

- Collaert, N.; Alian, A.; De Jaeger, B.; Peralagu, U.; Vais, A.; Walke, A.; Witters, L.; Yu, H.; Capogreco, E.; Devriendt, K.; et al. Fabrication challenges and opportunities for high-mobility materials: From CMOS applications to emerging derivative technologies. In Proceedings of the Advanced Etch Technology for Nanopatterning VIII, SPIE Advanced Lithography 2019, San Jose, CA, USA, 20 March 2019; Volume 10963, pp. 1096305-1–1096305-9. [Google Scholar] [CrossRef]

- Then, H.W.; Huang, C.Y.; Krist, B.; Jun, K.; Lin, K.; Nidhi, N.; Michaelos, T.; Mueller, B.; Paul, R.; Peck, J.; et al. 3D heterogeneous integration of high performance high-K metal gate GaN NMOS and Si PMOS transistors on 300 mm high-resistivity Si substrate for energy-efficient and compact power delivery, RF (5G and beyond) and SoC applications. In Proceedings of the IEEE International Electron Devices Meeting (IEDM) 2019, San Francisco, CA, USA, 7–11 December 2019; pp. 2019–2022. [Google Scholar] [CrossRef]

- LaRoche, J.R.; Hoke, W.E.; Kazior, T.E.; Lubyshev, D.; Fastenau, J.M.; Liu, W.K.; Urteaga, M.; Ha, W.; Bergman, J.; Choe, M.J.; et al. Monolithically integrated III-V and Si CMOS devices on silicon on lattice engineered substrates (SOLES). In Proceedings of the International Conference on Compound Semiconductor Manufacturing Technology (CS MANTECH) 2009, Tampa, FL, USA, 18–21 May 2009; pp. 2–5. [Google Scholar]

- Thiam, A.; Roelens, Y.; Coinon, C.; Avramovic, V.; Grandchamp, B.; Ducatteau, D.; Wallart, X.; Maneux, C.; Zaknoune, M. InP HBT thermal management by transferring to high thermal conductivity silicon substrate. IEEE Electron Device Lett. 2014, 35, 1010–1012. [Google Scholar] [CrossRef]

- Kunert, B.; Mols, Y.; Baryshniskova, M.; Waldron, N.; Schulze, A.; Langer, R. How to control defect formation in monolithic III/V hetero-epitaxy on (100) Si? A critical review on current approaches. Semicond. Sci. Technol. 2018, 33, 93002. [Google Scholar] [CrossRef]

- Waldron, N.; Merckling, C.; Guo, W.; Ong, P.; Teugels, L.; Ansar, S.; Tsvetanova, D.; Sebaai, F.; Van Dorp, D.H.; Milenin, A.; et al. An InGaAs/InP quantum well finfet using the replacement fin process integrated in an RMG flow on 300mm Si substrates. Dig. Tech. Pap. Symp. VLSI Technol. 2014, 1, 1–2. [Google Scholar] [CrossRef]

- Kunert, B.; Guo, W.; Mols, Y.; Langer, R.; Barla, K. Integration of III/V Hetero-structures by Selective Area Growth on Si for Nano- and Optoelectronic. ECS Trans. 2016, 75, 409–419. [Google Scholar] [CrossRef]

- Van Thourhout, D.; Shi, Y.; Baryshnikova, M.; Mols, Y.; Kuznetsova, N.; De Koninck, Y.; Pantouvaki, M.; Van Campenhout, J.; Langer, R.; Kunert, B. Nano-ridge laser monolithically grown on (001) Si. In Semiconductors and Semimetals, Future Directions in Silicon Photonics; Elsevier: Amsterdam, The Netherlands, 2019; Volume 101, pp. 283–304. ISBN 9780128188576. [Google Scholar]

- Shi, Y.; Wang, Z.; Van Campenhout, J.; Pantouvaki, M.; Guo, W.; Kunert, B.; Van Thourhout, D. Optical pumped InGaAs/GaAs nano-ridge laser epitaxially grown on a standard 300-mm Si wafer. Optica 2017, 4, 1468. [Google Scholar] [CrossRef]

- Shi, Y.; Baryshnikova, M.; Mols, Y.; Marianna, P.; van Campenhout, J.; Kunert, B.; van Thourhout, D. Loss-coupled DFB nano-ridge laser monolithically grown on a standard 300-mm Si wafer. Opt. Express 2021, 29, 14649–14657. [Google Scholar] [CrossRef]

- Vais, A.; Alcotte, R.; Ingels, M.; Wambacq, P.; Parvais, B.; Langer, R.; Kunert, B.; Waldron, N.; Collaert, N.; Witters, L.; et al. First demonstration of III-V HBTs on 300 mm Si substrates using nano-ridge engineering. In Proceedings of the IEEE International Electron Devices Meeting (IEDM) 2019, San Francisco, CA, USA, 7–11 December 2019; pp. 9.1.1–9.1.4. [Google Scholar] [CrossRef]

- Yadav, S.; Vais, A.; Elkashlan, R.Y.; Witters, L.; Vondkar, K.; Mols, Y.; Walke, A.; Yu, H.; Alcotte, R.; Ingels, M.; et al. DC and RF Characterization of Nano-ridge HBT Technology Integrated on 300 mm Si Substrates. In Proceedings of the 2020 15th European Microwave Integrated Circuits Conference (EuMIC 2020) 2020, Utrecht, The Netherlands, 11–12 January 2021; pp. 89–92. [Google Scholar]

- Ozdemir, C.I.; De Koninck, Y.; Yudistira, D.; Kuznetsova, N.; Baryshnikova, M.; Van Thourhout, D.; Kunert, B.; Pantouvaki, M.; Van Campenhout, J. 0.3pA Dark Current and 0.65A/W Responsivity 1020nm InGaAs/GaAs Nano-Ridge Waveguide Photodetector Monolithically Integrated on a 300-mm Si Wafer. In Proceedings of the 2020 European Conference on Optical Communications (ECOC), Brussels, Belgium, 6–10 December 2020; pp. 1–4. [Google Scholar] [CrossRef]

- Syshchyk, O.; Hsu, B.; Yu, H.; Motsnyi, V.; Vais, A.; Kunert, B.; Mols, Y.; Alcotte, R.; Puybaret, R.; Waldron, N.; et al. Deep-Level Transient Spectroscopy of GaAs Nanoridge Diodes Grown on Si Substrates. Phys. Rev. Appl. 2020, 14, 024093. [Google Scholar] [CrossRef]

- Baryshnikova, M.; Mols, Y.; Ishii, Y.; Alcotte, R.; Han, H.; Hantschel, T.; Richard, O.; Pantouvaki, M.; Van Campenhout, J.; Van Thourhout, D.; et al. Nano-Ridge Engineering of GaSb for the Integration of InAs/GaSb Heterostructures on 300 mm (001) Si. Crystals 2020, 10, 330. [Google Scholar] [CrossRef] [Green Version]

- Kunert, B.; Alcotte, R.; Mols, Y.; Baryshnikova, M.; Waldron, N.; Collaert, N.; Langer, R. Application of an Sb Surfactant in InGaAs Nano-ridge Engineering on 300 mm Silicon Substrates. Cryst. Growth Des. 2021, 21, 1657–1665. [Google Scholar] [CrossRef]

- Collaert, N.; Alian, A.; Chen, S.H.; Deshpande, V.; Ingels, M.; Putcha, V.; Sibaja-Hernandez, A.; Van Liempd, B.; Vais, A.; Vandooren, A.; et al. Semiconductor Technologies for next Generation Mobile Communications. In Proceedings of the 2018 14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT) 2018, Qingdao, China, 31 October–3 November 2018; pp. 1–4. [Google Scholar]

- Rodwell, M.J.W.; Fang, Y.; Rode, J.; Wu, J.; Markman, B.; Suran Brunelli, S.T.; Klamkin, J.; Urteaga, M. 100–340 GHz Systems: Transistors and Applications. Tech. Dig. Int. Electron Devices Meet. IEDM 2019, 14.3.1–14.3.4. [Google Scholar] [CrossRef]

- Nakamura, T. 5G Evolution and 6G. Available online: https://www.nttdocomo.co.jp/english/binary/pdf/corporate/technology/whitepaper_6g/DOCOMO_6G_White_PaperEN_20200124.pdf (accessed on 16 April 2021). [CrossRef]

- Guo, W.; Mols, Y.; Belz, J.; Beyer, A.; Volz, K.; Schulze, A.; Langer, R.; Kunert, B. Anisotropic relaxation behavior of InGaAs/GaAs selectively grown in narrow trenches on (001) Si substrates. J. Appl. Phys. 2017, 122, 025303. [Google Scholar] [CrossRef]

- Mols, Y.; Bogdanowicz, J.; Favia, P.; Lagrain, P.; Guo, W.; Bender, H.; Kunert, B. Structural analysis and resistivity measurements of InAs and GaSb fins on 300 mm Si for vertical (T)FET. J. Appl. Phys. 2019, 125, 245107. [Google Scholar] [CrossRef]

- Heidelberger, C.; Fitzgerald, E.A. GaAsP/InGaP HBTs grown epitaxially on Si substrates: Effect of dislocation density on DC current gain. J. Appl. Phys. 2018, 123, 161532. [Google Scholar] [CrossRef]

- Ito, H.; Nakajima, O.; Furuta, T.; Harris, J.S. Influence of Dislocations on the DC Characteristics of AlGaAs/GaAs Heterojunction Bipolar Transistors. IEEE Electron Device Lett. 1992, 13, 232–234. [Google Scholar] [CrossRef]

- Liu, W.; Kim, S. A High-Gain AlGaAs/GaAs Heterojunction Bipolar Transistor Grown on Silicon Substrate. Jpn. J. Appl. Phys. 1992, 31, 2656–2659. [Google Scholar] [CrossRef]

- Won, T.; Litton, C.W.; Morkoç, H.; Yariv, A. A High-Gain GaAs/AlGaAs n-p-n Heterojunction Bipolar Transistor on (100) Si Grown by Molecular Beam Epitaxy. IEEE Electron Device Lett. 1988, 9, 405–407. [Google Scholar] [CrossRef]

- Loke, W.K.; Lee, K.H.; Wang, Y.; Tan, C.S.; Fitzgerald, E.A.; Yoon, S.F. MOCVD growth of InGaP/GaAs heterojunction bipolar transistors on 200 mm Si wafers for heterogeneous integration with Si CMOS. Semicond. Sci. Technol. 2018, 33, 115011. [Google Scholar] [CrossRef]

- Khai, L.W.; Geok Ing, N.; Fitzgerald, E.A.; Soon Fatt, Y.; Yue, W.; Kwang Hong, L.; Zhihong, L.; Hanlin, X.; Siau Ben, C.; Eng Kian, K.L.; et al. High-Frequency Characteristics of InGaP/GaAs Double Heterojunction Bipolar Transistor Epitaxially Grown on 200 mm Ge/Si Wafers. IEEE J. Electron Devices Soc. 2020, 8, 122–125. [Google Scholar] [CrossRef]

| Layer | V/III | N (cm−3) | Remark |

| GaAs | 30 | 8 × 1018 | no contact |

| InGaP_1 | 40 | undoped | no contact |

| GaAs_1 | 30 | 2 × 1016 | no contact |

| InGaP_2 | 40 | undoped | no contact |

| GaAs_2 | 30 | 2 × 1016 | no contact |

| InGaP_3 | 40 | 9 × 1018 | no contact |

| GaAs_3 | 30 | 2 × 1018 | no contact |

| InGaP_4 | 80 | undoped | contact |

| GaAs_4 | 30 | undoped | contact |

| InGaP_5 | 40 | undoped | contact, 2 × growth rate |

| GaAs_5 | 30 | undoped | contact |

| Ref. | Substrate | TDD | AE | Emitter | Base Doping & Thickness | βmax | JC | VCB | |

|---|---|---|---|---|---|---|---|---|---|

| (cm−2) | (µm2) | (cm−3) | (nm) | (mA/µm2) | (V) | ||||

| Won [32] | Si | – | 2500 | AlGaAs | 1 × 1019 | 150 | 45 | 0.02 | (0) |

| Ito [30] | GaAs * | ≤3 × 105 108 | 13 | AlGaAs | 1 × 1019 | † 80 | 90 25 | 0.25 | (0) |

| Liu [31] | Si | – | 80–160 40 | AlGaAs | 5 × 1018 | 100 † 100 | 45 ~100 | 0.1 1 | 0 |

| Heidelberger [29] | (Ge/)Si | ~2 × 107 | 2827 | InGaP | 7 × 1017 | 90 | 60 | 0.035 | 0 |

| Loke [33] | (Ge/)Si | ~2 × 107 | 2000 | InGaP | 1.9 × 1019 | 55 | 95 | 0.05 | 3.3 |

| Loke [34] | (Ge/)Si | ~2 × 107 | 48 | InGaP | 3 × 1019 | 55 | 55 | 0.08 | 0.3 |

| NRref | Si | <106 | 531 | InGaP | 7.5 × 1019 | 20 | 31 | 5.7 × 10−4 | 0 |

| NRbase | Si | <106 | 208 | InGaP | 3 × 1019 | 20 | 112 | 1.2 × 10−3 | 0 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mols, Y.; Vais, A.; Yadav, S.; Witters, L.; Vondkar, K.; Alcotte, R.; Baryshnikova, M.; Boccardi, G.; Waldron, N.; Parvais, B.; et al. Monolithic Integration of Nano-Ridge Engineered InGaP/GaAs HBTs on 300 mm Si Substrate. Materials 2021, 14, 5682. https://doi.org/10.3390/ma14195682

Mols Y, Vais A, Yadav S, Witters L, Vondkar K, Alcotte R, Baryshnikova M, Boccardi G, Waldron N, Parvais B, et al. Monolithic Integration of Nano-Ridge Engineered InGaP/GaAs HBTs on 300 mm Si Substrate. Materials. 2021; 14(19):5682. https://doi.org/10.3390/ma14195682

Chicago/Turabian StyleMols, Yves, Abhitosh Vais, Sachin Yadav, Liesbeth Witters, Komal Vondkar, Reynald Alcotte, Marina Baryshnikova, Guillaume Boccardi, Niamh Waldron, Bertrand Parvais, and et al. 2021. "Monolithic Integration of Nano-Ridge Engineered InGaP/GaAs HBTs on 300 mm Si Substrate" Materials 14, no. 19: 5682. https://doi.org/10.3390/ma14195682

APA StyleMols, Y., Vais, A., Yadav, S., Witters, L., Vondkar, K., Alcotte, R., Baryshnikova, M., Boccardi, G., Waldron, N., Parvais, B., Collaert, N., Langer, R., & Kunert, B. (2021). Monolithic Integration of Nano-Ridge Engineered InGaP/GaAs HBTs on 300 mm Si Substrate. Materials, 14(19), 5682. https://doi.org/10.3390/ma14195682