Performance Enhancement in N2 Plasma Modified AlGaN/AlN/GaN MOS-HEMT Using HfAlOX Gate Dielectric with Γ-Shaped Gate Engineering

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Hu, J.; Zhang, Y.; Sun, M.; Piedra, D.; Chowdhury, N.; Palacios, T. Materials and processing issues in vertical GaN power electronics. Mater. Sci. Semicond. Process. 2018, 78, 75–84. [Google Scholar] [CrossRef] [Green Version]

- Ardaravičius, L.; Matulionis, A.; Liberis, J.; Kiprijanovic, O.; Ramonas, M.; Eastman, L.F.; Shealy, J.R.; Vertiatchikh, A. Electron drift velocity in AlGaN/GaN channel at high electric fields. Appl. Phys. Lett. 2003, 83, 4038–4040. [Google Scholar] [CrossRef]

- Basu, S.; Singh, P.K.; Sze, P.W.; Wang, Y.H. AlGaN/GaN Metal oxide-semiconductor high electron mobility transistor with liquid phase deposited Al2O3 as gate dielectric. J. Electrochem. Soc. 2010, 157, 947–951. [Google Scholar] [CrossRef]

- Borga, M.; Meneghini, M.; Benazzi, D.; Canato, E.; Püsche, R.; Derluyn, J.; Abid, I.; Medjdoub, F.; Meneghessoa, G.; Zanoni, E. Buffer breakdown in GaN-on-Si HEMTs: A comprehensive study based on a sequential growth experiment. Microelectron. Reliab. 2019, 100, 1–5. [Google Scholar] [CrossRef]

- Mazumder, S.; Wang, Y.H. Investigation of HfSiOX Passivation Effect on AlGaN/GaN HEMT. In Proceedings of the 2020 International Symposium on Devices, Circuits and Systems (ISDCS), Howrah, India, 4–6 March 2020; pp. 1–4. [Google Scholar]

- Jun, L.; Zhao, S.L.; Mi, M.H.; Hou, B.; Yang, X.L.; Zhang, J.C.; Ma, X.H.; Hao, Y. Trap states induced by reactive ion etching in AlGaN/GaN high-electron-mobility transistors. Chin. Phys. B 2015, 24, 117305. [Google Scholar]

- Im, K.S.; Ha, J.B.; Kim, K.W.; Lee, J.S.; Kim, D.S.; Choi, H.C.; Lee, J.H. AlGaN/GaN-based normally-off GaN MOSFET with stress controlled 2DEG source and drain. Phys. Status Solidi 2010, 7, 2013–2015. [Google Scholar] [CrossRef]

- Xu, Z.; Wang, J.; Cai, Y.; Liu, J.; Jin, C.; Yang, Z.; Wang, M.; Yu, M.; Xie, B.; Wu, W.; et al. Enhancement mode (E-Mode) AlGaN/GaN MOSFET with 10−13 A/mm leakage current and 1012 ON/ OFF current ratio. IEEE Electron Device Lett. 2014, 35, 1200–1202. [Google Scholar] [CrossRef]

- Han, K.; Zhu, L. GaN MOSHEMT employing HfO2 as a gate dielectric with partially etched barrier. Semicond. Sci. Technol. 2017, 32, 095004. [Google Scholar] [CrossRef]

- Adak, S.; Swain, S.K.; Singh, A.; Pardeshi, H.; Pati, S.K.; Sarkar, C.K. Study of HfAlO/AlGaN/GaN MOS-HEMT with source field plate structure for improved breakdown voltage. Phys. E 2014, 64, 152–157. [Google Scholar] [CrossRef]

- Min, B.J.; Yoon, S.; Won, K.T.; Lam, L.J. Enhancement of magnetic properties in (Ga,Mn)N nanowires due to plasma treatment. Appl. Phys. Lett. 2006, 89, 152113. [Google Scholar]

- Mazumder, S.; Li, S.H.; Wu, Z.G.; Wang, Y.H. Combined Implications of UV/O3 Interface Modulation with HfSiOX Surface Passivation on AlGaN/AlN/GaN MOS-HEMT. Crystals 2021, 11, 136. [Google Scholar] [CrossRef]

- Tsurumi, N.; Ueno, H.; Murata, T.; Ishida, H.; Uemoto, Y.; Ueda, T.; Inoue, K.; Tanaka, T. AlN passivation over AlGaN/GaN HFETs for surface heat spreading. IEEE Trans. Electron. 2010, 57, 980–985. [Google Scholar] [CrossRef]

- Dutta, G.; Das Gupta, N.; Das Gupta, A. Effect of Sputtered-Al2O3 Layer Thickness on the Threshold Voltage of III-Nitride MIS-HEMTs. IEEE Trans. Electron. 2016, 63, 1450–1458. [Google Scholar] [CrossRef]

- Zhou, H.; Lou, X.; Kim, S.B.; Chabak, K.D.; Gordon, R.G.; Ye, P.D. Enhancement-mode AlGaN/GaN fin-MOSHEMTs on Si substrate with atomic layer epitaxy MgCaO. IEEE Electron Device Lett. 2017, 38, 1294–1297. [Google Scholar] [CrossRef]

- Yue, Y.; Hao, Y. AlGaN/GaN MOS-HEMT with HfO2 Dielectric and Al2O3 Interfacial Passivation Layer Grown by Atomic Layer Deposition. IEEE Electron Device Lett. 2008, 29, 838–840. [Google Scholar] [CrossRef]

- Byun, Y.C.; Lee, J.G.; Meng, X.; Lee, J.S. Low temperature (100 °C) atomic layer deposited-ZrO2 for recessed gate GaN HEMTs on Si. Appl. Phys. Lett. 2017, 111, 082905. [Google Scholar] [CrossRef]

- Wu, T.Y.; Lin, S.K.; Sze, P.W.; Huang, J.J.; Chien, W.C.; Hu, C.C.; Tsai, M.J.; Wang, Y.H. AlGaN/GaN MOSHEMTs With Liquid-Phase-Deposited TiO2 as Gate Dielectric. IEEE Trans. Electron Devices 2009, 56, 2911–2916. [Google Scholar] [CrossRef]

- Shen, L.; Zhang, D.; Cheng, X. Performance Improvement and Current Collapse Suppression of Al2O3/AlGaN/GaN HEMTs Achieved by Fluorinated Graphene Passivation. IEEE Electron Device Lett. 2017, 38, 596–599. [Google Scholar] [CrossRef]

- Li, S.; Hu, Q.; Wang, X.; Li, T. Improved Interface Properties and Dielectric Breakdown in Recessed AlGaN/GaN MOSHEMTs Using HfSiOx as Gate Dielectric. IEEE Electron Device Lett. 2019, 40, 295–298. [Google Scholar] [CrossRef]

- Shi, Y.T.; Xu, W.Z.; Zeng, C.K.; Ren, F.F.; Ye, J.D.; Zhou, D.; Chen, D.J.; Zhang, R.; Zheng, Y.; Lu, H. High-k HfO2-Based AlGaN/GaN MIS-HEMTs With Y2O3 Interfacial Layer for High Gate Controllability and Interface Quality. IEEE J. Electron Devices Soc. 2019, 8, 15–19. [Google Scholar] [CrossRef]

- Murugapandiyan, P.; Mohanbabu, A.; Rajya Lakshmi, V.; Ramakrishnan, V.N.; Varghese, A.; Wasim, M.; Baskaran, S.; Kumar, R.S.; Janakiraman, V. Performance analysis of HfO2/InAlN/AlN/GaN HEMT with AlN buffer layer for high power microwave applications. J. Sci. Adv. Mater. Devices 2020, 5, 192–198. [Google Scholar] [CrossRef]

- Cui, X.; Cheng, W.; Hua, Q.; Liang, R.; Hu, W.; Wang, Z.L. Enhanced performances of AlGaN/GaN HEMTs with dielectric engineering of HfZrOx. Nano Energy 2020, 68, 104361. [Google Scholar] [CrossRef]

- Rastogi, A.C.; Sharma, R.N. Structural and electrical characteristics of metal-insulator-semiconductor diodes based on Y2O3 dielectric thin films on silicon. J. Appl. Phys. 1992, 71, 5041. [Google Scholar] [CrossRef]

- Jung, H.S.; Lee, S.A.; Rha, S.H.; Lee, S.Y.; Kim, H.K.; Kim, D.H.; Oh, K.H.; Park, J.M.; Kim, W.H.; Song, M.W.; et al. Impacts of Zr Composition in Hf1-xZrxOy Gate Dielectrics on Their Crystallization Behavior and Bias-Temperature-Instability Characteristics. IEEE Trans. Electron. 2011, 58, 2094–2103. [Google Scholar] [CrossRef]

- Zhu, W.J.; Tamagawa, T.; Gibson, M.; Furukawa, T.; Ma, T.P. Effect of Al Inclusion in HfO2 on the Physical and Electrical Properties of the Dielectrics. IEEE Electron Device Lett. 2002, 23, 649–651. [Google Scholar] [CrossRef]

- Colon, A.; Shi, J. High-K insulating materials for AlGaN/GaN metal insulator semiconductor heterojunction field effect transistors. Solid State Electron. 2014, 99, 25–30. [Google Scholar] [CrossRef]

- Lin, J.; Monaghan, S.; Cherkaoui, K.; Povey, I.M.; Sheehan, B.; Hurley, P.K. Examining the relationship between capacitance-voltage hysteresis and accumulation frequency dispersion in InGaAs metal-oxide semiconductor structures based on the response to post-metal annealing. Microelectron. Eng. 2017, 178, 204–208. [Google Scholar] [CrossRef]

- Mohanbabu, A.; Mohankumar, N.; Godwin Raj, D.; Sarkar, P. Efficient III-Nitride MIS-HEMT devices with high-k gate dielectric for high-power switching boost converter circuits. Superlattice Microstruct. 2017, 103, 270–284. [Google Scholar] [CrossRef]

- Liu, L.; Xi, Y.; Ahn, S.; Ren, F.; Gila, B.P.; Pearton, S.J.; Kravchenko, I.I. Characteristics of gate leakage current and breakdown voltage of AlGaN/GaN high electron mobility transistors after postprocess annealing. J. Vac. Sci. Technol. B Microelectron. Nanom. Struct. 2014, 32, 1–5. [Google Scholar] [CrossRef]

- Liu, S.C.; Chen, B.Y.; Lin, Y.C.; Hsieh, T.E.; Wang, H.C.; Chang, E.Y. GaN MIS-HEMTs with Nitrogen Passivation for Power Device Applications. IEEE Electron Device Lett. 2014, 35, 1001–1003. [Google Scholar]

- Zheng, Y.Y.; Yue, H.; Cheng, Z.J.; Qian, F.; Yu, N.J.; Hua, M.X. A study on Al2O3 passivation in GaN MOS-HEMT by pulsed stress. Chin. Phys. B 2008, 17, 1405. [Google Scholar] [CrossRef]

- Cai, Y.; Zhou, Y.; Lau, K.M.; Chen, K.J. Enhancement-Mode AlGaN/GaN HEMTs with Low On-Resistance and Low Knee Voltage. IEEE Trans. Electron. 2006, 89, 1025–1030. [Google Scholar] [CrossRef]

- Rahman, M.M.; Kim, J.G.; Kim, D.H.; Kim, T.W. Characterization of Al Incorporation into HfO2 Dielectric by Atomic Layer Deposition. Micromechanics 2019, 10, 361. [Google Scholar]

- Kalb, W.L.; Batlogg, B. Calculating the trap density of states in organic field-effect transistors from experiment: A comparison of different methods. Phys. Rev. B 2010, 81, 1–13. [Google Scholar] [CrossRef] [Green Version]

- Marron, T.; Takashima, S. Impact of annealing on ALD Al2O3 gate dielectric for GaN MOS devices. Phys. Status Solidi C 2012, 9, 907–910. [Google Scholar] [CrossRef]

- Wang, Q.; Cheng, X.; Zheng, L.; Shen, L.; Li, J.; Zhang, D.; Qian, R.; Yu, Y. Interface engineering of an AlNO/AlGaN/GaN MIS diode induced by PEALD alternate insertion of AlN in Al2O3. RSC Adv. 2017, 7, 11745–11751. [Google Scholar] [CrossRef] [Green Version]

- Reddy, M.S.P.; Park, W.S.; Im, K.S.; Lee, J.H. Dual-surface modification of AlGaN/GaN HEMTs using TMAH and piranha solutions for enhancing current and 1/f-Noise Characteristics. IEEE J. Electron Devices Soc. 2018, 6, 791–796. [Google Scholar] [CrossRef]

- Medjdoub, F.; Sarazin, N.; Tordjman, M.; Magis, M.; di Forte-Poisson, M.A.; Knez, M.; Delos, E.; Gaquiere, C.; Delage, S.L.; Kohn, E. Characteristics of Al2O3/AlInN/GaN MOSHEMT. Electron. Lett. 2007, 43, 691–692. [Google Scholar] [CrossRef]

- Suria, A.J.; Yalamarthy, A.S.; Heuser, T.A.; Bruefach, A.; Chapin, C.A.; So, H.; Senesky, D.G. Thickness engineering of atomic layer deposited Al2O3 films to suppress interfacial reaction and diffusion of Ni/Au gate metal in AlGaN/GaN HEMTs up to 600 C in air. App. Phys. Lett. 2017, 110, 253505. [Google Scholar] [CrossRef]

- Freedsman, J.J.; Egawa, T.; Yamaoka, Y.; Yano, Y.; Ubukata, A.; Tabuchi, T.; Matsumoto, K. Normally-OFF Al2O3/AlGaN/GaN MOS-HEMT on 8 in. Si with Low Leakage Current and High Breakdown Voltage (825 V). Appl. Phys. Express 2014, 7, 041003. [Google Scholar]

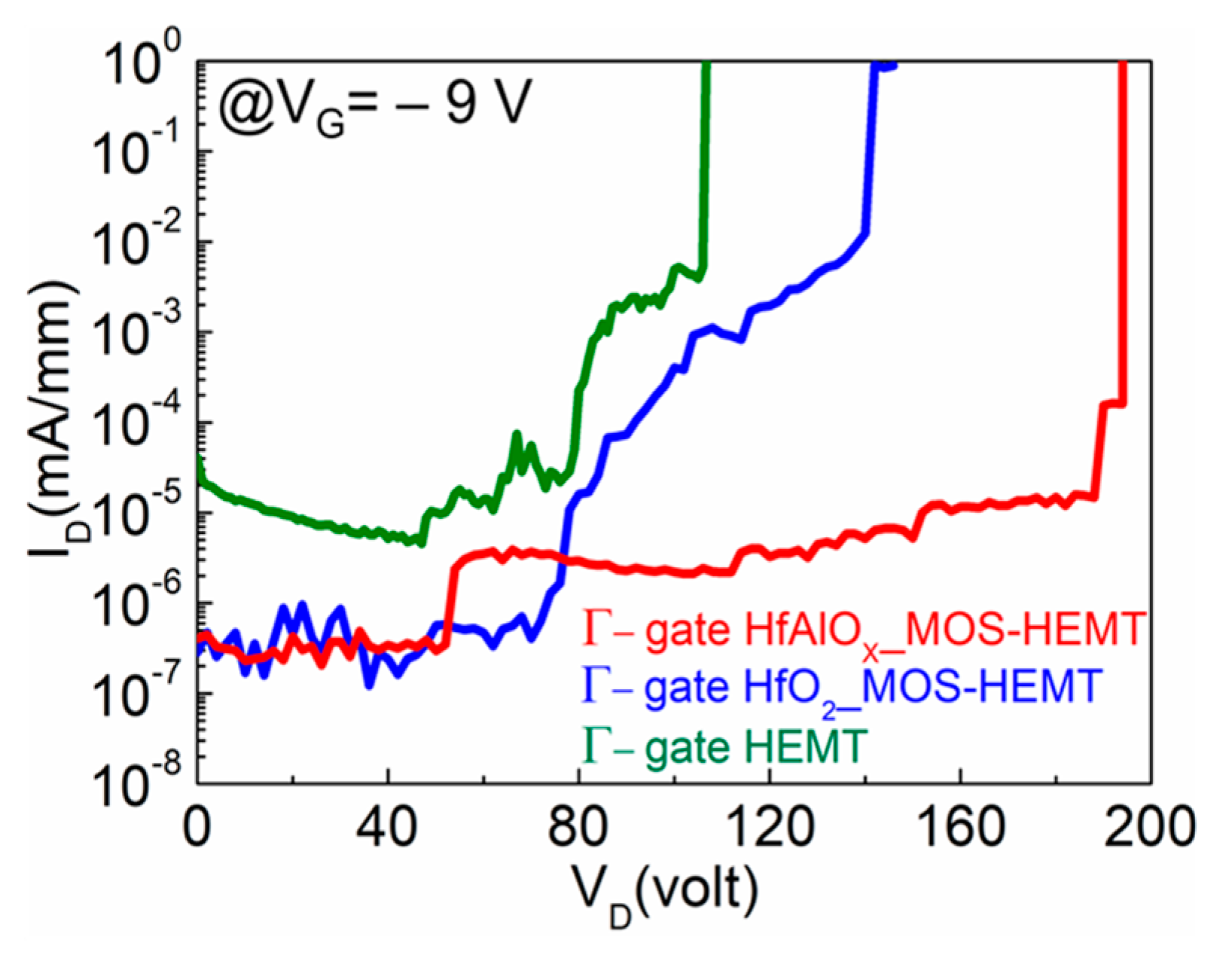

| Parameters | Non-Recessed HEMT | Partially-Recessed HEMT | Partially-Recessed HfO2 MOS-HEMT | Partially-Recessed HfAlOX MOS-HEMT |

|---|---|---|---|---|

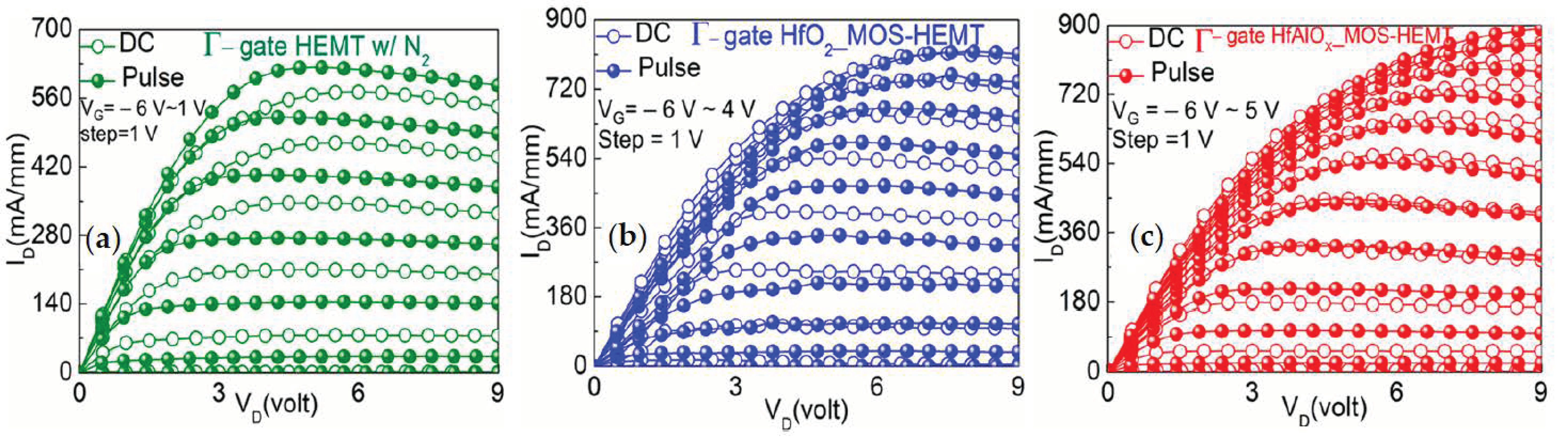

| IDMAX (mA/mm) | 520 (VG = 1 V) | 570 (VG = 1 V) | 775 (VG = 4 V) | 870 (VG = 5 V) |

| VTH (V) | −4.9 | −3.55 | −3.41 | −3.55 |

| GMMAX (mS/mm) (@ VD = 4 V) | 114 | 139 | 116 | 118 |

| SS (mV/dec) | 110 | 101 | 86 | 90 |

| ION/IOFF | 1.04 | 2.9 | 2.3 | 1.8 |

| IG (A/mm) (@VG =−12 V) | ||||

| Current collapse (%) | - | 18 | 13 | 4 |

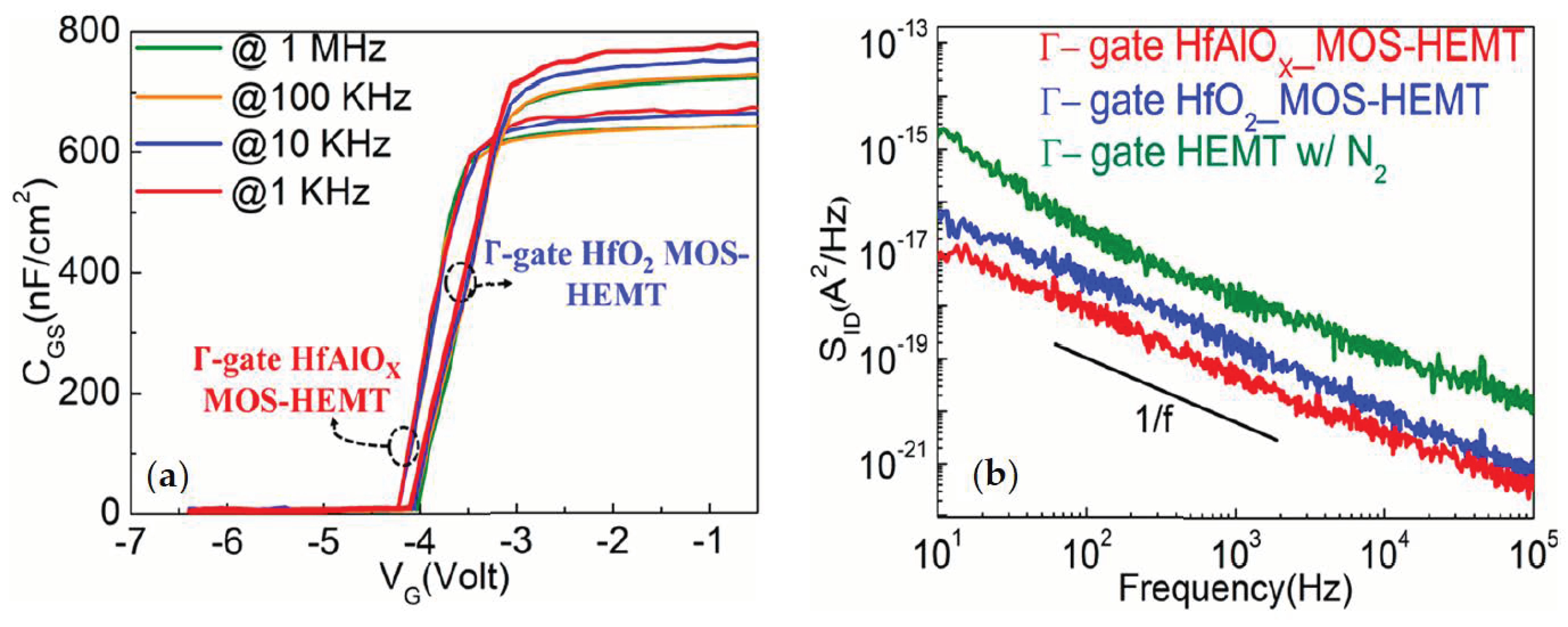

| Dit () | - | |||

| Hysteresis (∆V) (V) | - | - | 0.48 | 0.15 |

| VBR (V) | - | 107 | 145 | 195 |

| Parameters | Ref. [21] | Ref. [23] | Ref. [39] | Ref. [40] | Ref. [41] | This Work |

|---|---|---|---|---|---|---|

| Epi structure | GaN/AlGaN/GaN | GaN/AlGaN/AlN/GaN | AlInN/AlN/GaN | GaN/AlGaN/GaN | GaN/AlGaN/AlN/GaN | GaN/AlGaN/AlN/GaN |

| LG (µm) | 1 | 5 | 0.2 | 50 | 1.5 | 0.5 |

| Dielectric materials | HfO2/Y2O3 | HfZrOX | Al2O3 | Al2O3 | Al2O3 | HfAlOX |

| Dielectric Thickness (nm) | 12/1 | 20 | 5 | 50 | 20 | 10 |

| IDMAX (mA/mm) | 600 | 705 | 1150 | ~160 | 300 | 870 |

| GMMAX (mS/mm) | 4.5 (@VD = 0.05 V) | 54 (@VD = 10 V) | 185 | 77 (@VD = 15 V) | 79 (@VD = 8 V) | 118 (@VD = 4 V) |

| SS (mV/dec) | 70 | 85 | - | - | 74 | 90 |

| ION/IOFF | 109 | 106 | - | - | 1.8 | |

| IG | 10−10 A/mm (@VG = −9 V) | ~10−7 A/mm (@VG = −10 V) | ~10−4 A/mm (@ VG = −15 V) | > 10−5 A/m2 (@ VG = −5 V) | 10−11 A/mm (@ VG = -6 V) | A/mm (@VG = −12 V) |

| Current collapse (%) | - | < 9% | - | - | - | ~4% |

| Dit (cm−2·eV−1) | 1012 | 1.1 109 | - | - | - | 1.8 1012 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, S.-K.; Mazumder, S.; Wu, Z.-G.; Wang, Y.-H. Performance Enhancement in N2 Plasma Modified AlGaN/AlN/GaN MOS-HEMT Using HfAlOX Gate Dielectric with Γ-Shaped Gate Engineering. Materials 2021, 14, 1534. https://doi.org/10.3390/ma14061534

Yang S-K, Mazumder S, Wu Z-G, Wang Y-H. Performance Enhancement in N2 Plasma Modified AlGaN/AlN/GaN MOS-HEMT Using HfAlOX Gate Dielectric with Γ-Shaped Gate Engineering. Materials. 2021; 14(6):1534. https://doi.org/10.3390/ma14061534

Chicago/Turabian StyleYang, Shun-Kai, Soumen Mazumder, Zhan-Gao Wu, and Yeong-Her Wang. 2021. "Performance Enhancement in N2 Plasma Modified AlGaN/AlN/GaN MOS-HEMT Using HfAlOX Gate Dielectric with Γ-Shaped Gate Engineering" Materials 14, no. 6: 1534. https://doi.org/10.3390/ma14061534

APA StyleYang, S.-K., Mazumder, S., Wu, Z.-G., & Wang, Y.-H. (2021). Performance Enhancement in N2 Plasma Modified AlGaN/AlN/GaN MOS-HEMT Using HfAlOX Gate Dielectric with Γ-Shaped Gate Engineering. Materials, 14(6), 1534. https://doi.org/10.3390/ma14061534