Charge Trap States of SiC Power TrenchMOS Transistor under Repetitive Unclamped Inductive Switching Stress

Abstract

:1. Introduction

2. Experimental

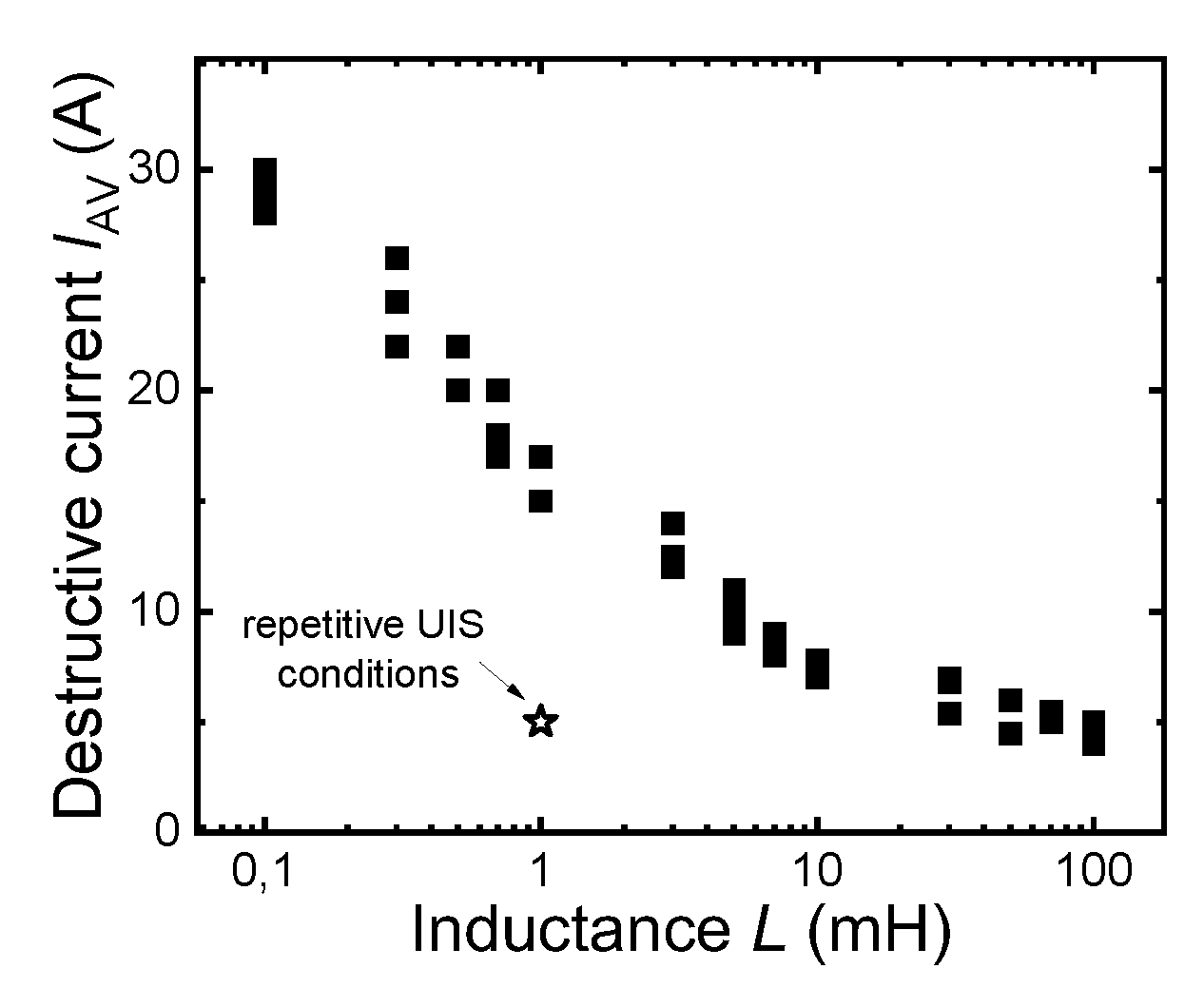

3. Repetitive UIS Stress

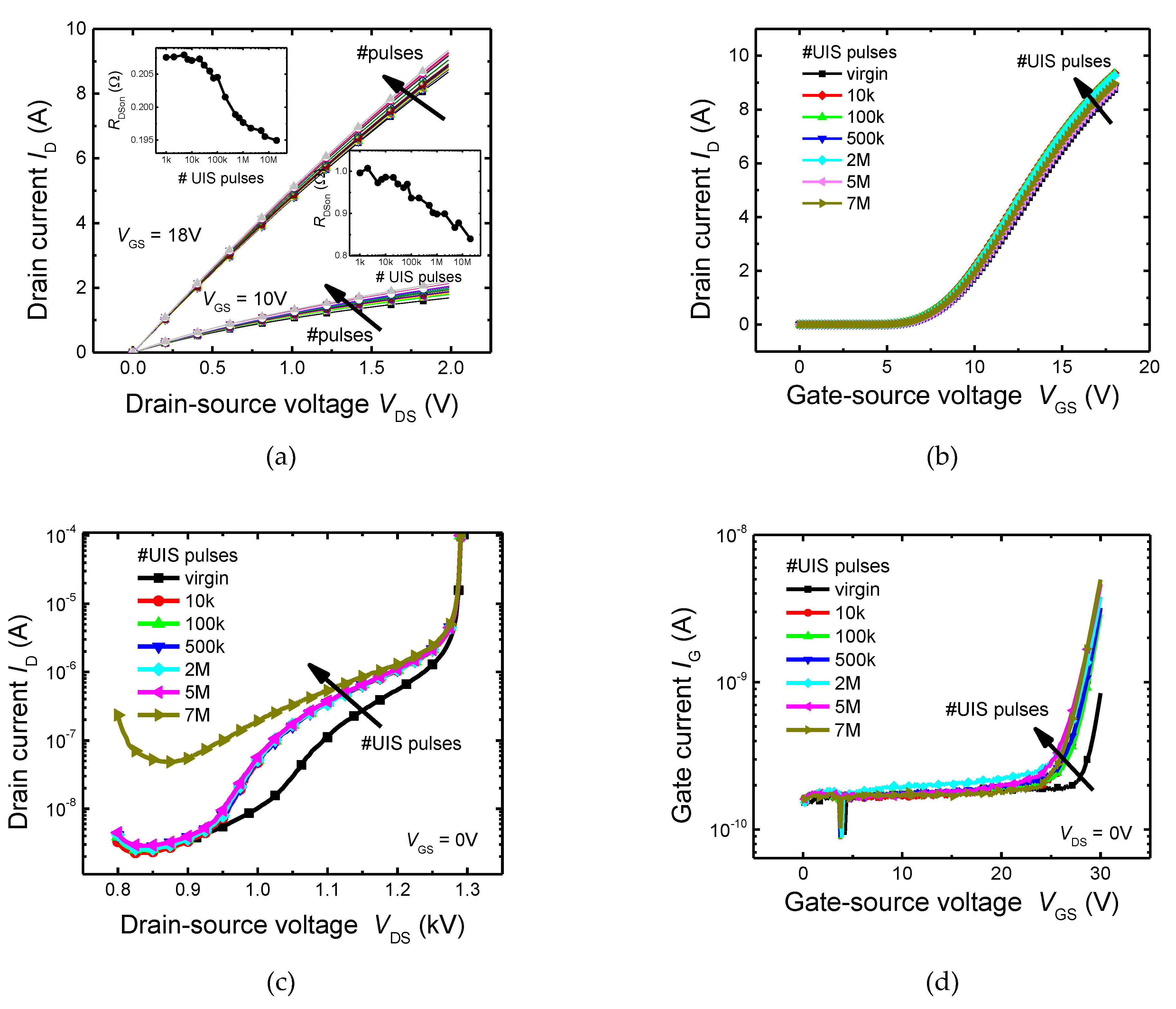

3.1. Impact on I-V and C-V Characteristics

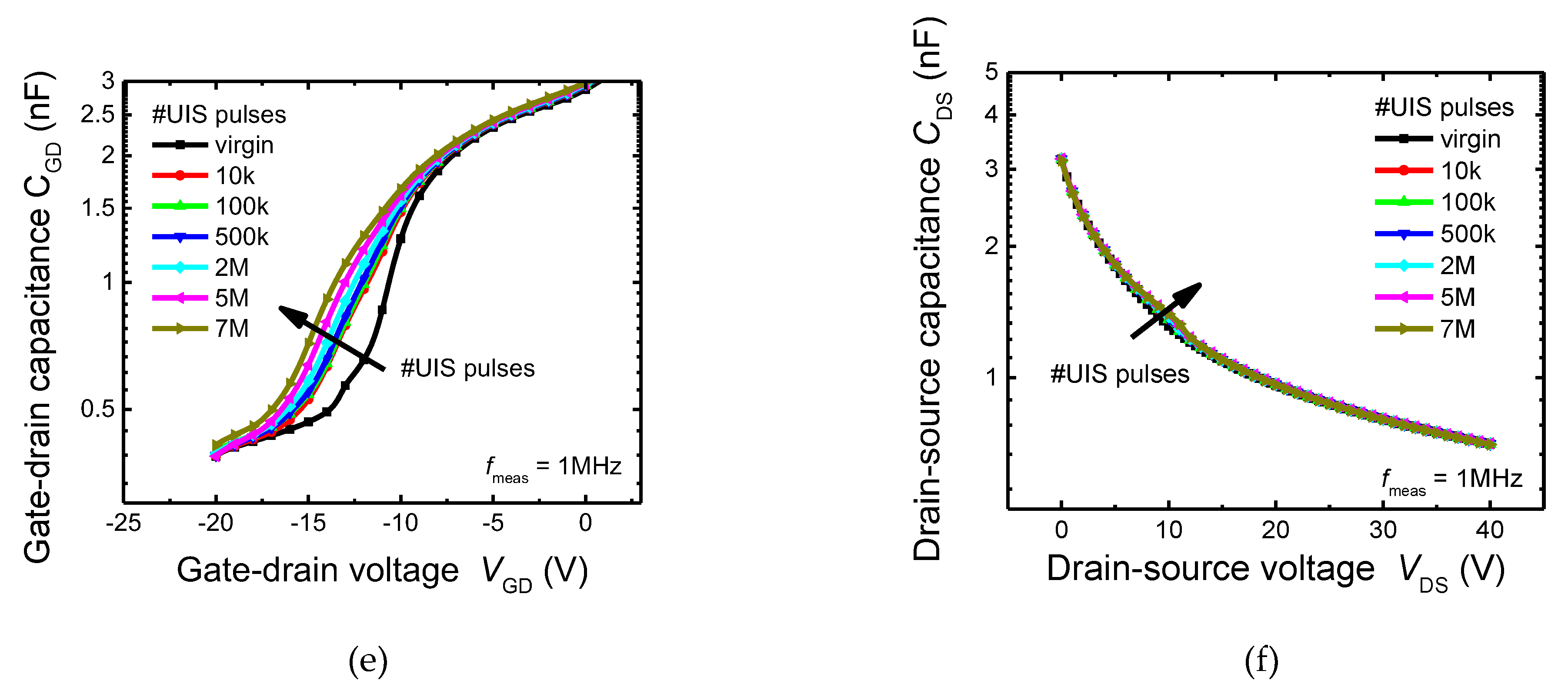

3.2. Impact on Switching Performance

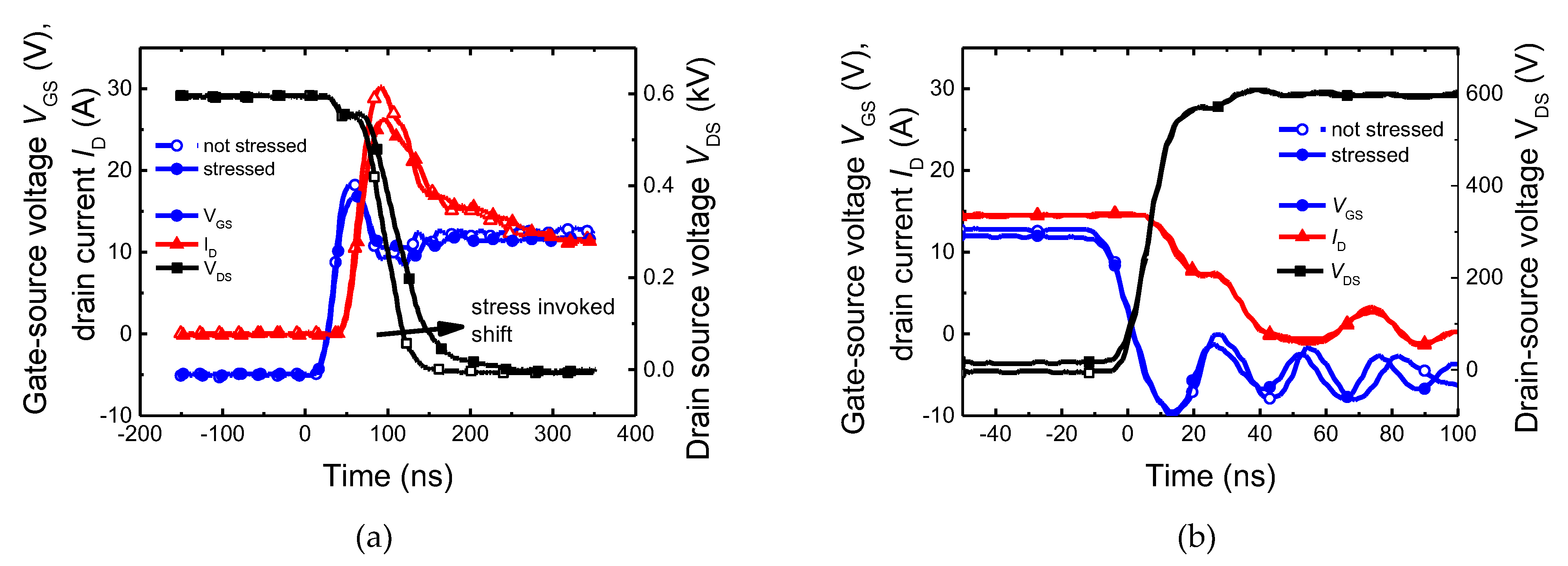

4. Defect Analysis

5. Conclusions

Supplementary Materials

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Batunlu, C.; Alrweq, M.; Albarbar, A. Effects of power tracking algorithms on lifetime of power electronic devices used in solar systems. Energies 2016, 9, 884. [Google Scholar] [CrossRef] [Green Version]

- Liu, S.; Gu, C.; Wei, J.; Qian, Q.; Sun, W.; Huang, A.Q. Repetitive unclamped-inductive-switching-induced electrical parameters degradations and simulation optimizations for 4H-SiC MOSFETs. IEEE Trans. Electron. Devices 2016, 63, 4331–4338. [Google Scholar] [CrossRef]

- Martinella, C.; Alía, R.G.; Stark, R.; Coronetti, A.; Cazzaniga, C.; Kastriotou, M.; Kadi, Y.; Gaillard, R.; Grossner, U.; Javanainen, A. Impact of terrestrial neutrons on the reliability of SiC VD-MOSFET technologies. IEEE Trans. Nucl. Sci. 2021, 68, 634–641. [Google Scholar] [CrossRef]

- Hazra, S.; Madhusoodhanan, S.; Moghaddam, G.K.; Hatua, K.; Bhattacharya, S. Design considerations and performance evaluation of 1200-V 100-A SiC MOSFET-based two-level voltage source converter. IEEE Trans. Ind. Appl. 2016, 52, 4257–4268. [Google Scholar] [CrossRef]

- Lutz, J.; Baburske, R. Some aspects on ruggedness of SiC power devices. Microelectron. Reliab. 2014, 54, 49–56. [Google Scholar] [CrossRef]

- Castellazzi, A.; Fayyaz, A.; Romano, G.; Yang, L.; Riccio, M.; Irace, A. SiC power MOSFETs performance, robustness and technology maturity. Microelectron. Reliab. 2016, 58, 164–176. [Google Scholar] [CrossRef]

- Siemieniec, R.; Peters, D.; Esteve, R.; Bergner, W.; Kück, D.; Aichinger, T.; Basler, T.; Zippelius, B. A SiC trench MOSFET concept offering improved channel mobility and high reliability. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; p. P-1. [Google Scholar]

- Marek, J.; Chvála, A.; Donoval, D.; Príbytný, P.; Molnár, M.; Mikolášek, M. Compact model of power MOSFET with temperature dependent Cauer RC network for more accurate thermal simulations. Solid-State Electron. 2014, 94, 44–50. [Google Scholar] [CrossRef]

- McDonald, T.; Soldano, M.; Murray, A.; Avram, T. Power MOSFET Avalanche Design Guidelines; Application Note AN-1005; International Rectifier Location: El Segundo, CA, USA, 2000. [Google Scholar]

- Laska, T.; Hille, F.; Pfirsch, F.; Jereb, R.; Bassler, M. Long term stability and drift phenomena of different trench IGBT structures under repetitive switching tests. In Proceedings of the 19th International Symposium on Power Semiconductor Devices and IC’s (ISPSD 2007), Jeju, Korea, 27–31 May 2007; pp. 1–4. [Google Scholar]

- Weiss, S.; Kassing, R. Deep Level Transient Fourier Spectroscopy (DLTFS)—A technique for the analysis of deep level properties. Solid-State Electron. 1988, 31, 1733–1742. [Google Scholar] [CrossRef]

- Janzén, E.; Gali, A.; Henry, A.; Ivanov, I.G.; Magnusson, B.; Son, N.T. Defects in SIC. In Defects in Microelectronic Materials and Devices; Fleetwood, D.M., Schrimpf, R.D., Eds.; CRC Press: Boca Raton, FL, USA, 2008; pp. 615–671. [Google Scholar]

- Achtziger, N.; Witthuhn, W. Selected Aspects of Radiotracer Deep Level Transient Spectroscopy. In Silicon Carbide; Choyke, W.J., Matsunami, H., Pensl, G., Eds.; Springer: Berlin/Heidelberg, Germany, 2004; pp. 537–562. [Google Scholar]

- Achtziger, N.; Witthuhn, W. Band-gap states of Ti, V, and Cr in 4 H-SiC: Identification and characterization by elemental transmutation of radioactive isotopes. Phys. Rev. B 1998, 57, 12181. [Google Scholar] [CrossRef]

- Achtziger, N.; Pasold, G.; Sielemann, R.; Hülsen, C.; Grillenberger, J.; Witthuhn, W. Tungsten in silicon carbide: Band-gap states and their polytype dependence. Phys. Rev. B 2000, 62, 12888. [Google Scholar] [CrossRef]

- Hemmingsson, C.G.; Son, N.T.; Ellison, A.; Zhang, J.; Janzén, E. Negative-U centers in 4 H silicon carbide. Phys. Rev. B 1998, 58, R10119–R10122. [Google Scholar] [CrossRef]

- Hemmingsson, C.; Son, N.T.; Kordina, O.; Bergman, J.P.; Janzén, E.; Lindström, J.L.; Savage, S.; Nordell, N. Deep level defects in electron-irradiated 4H SiC epitaxial layers. J. Appl. Phys. 1997, 81, 6155–6159. [Google Scholar] [CrossRef]

- Capan, I.; Brodar, T.; Coutinho, J.; Ohshima, T.; Markevich, V.P.; Peaker, A.R. Acceptor levels of the carbon vacancy in 4 H-SiC: Combining Laplace deep level transient spectroscopy with density functional modeling. J. Appl. Phys. 2018, 124, 245701. [Google Scholar] [CrossRef] [Green Version]

- Gelczuk, Ł.; Dąbrowska-Szata, M.; Kolkovsky, V.; Sochacki, M.; Szmidt, J.; Gotszalk, T. Origin and anomalous behavior of dominant defects in 4H-SiC studied by conventional and Laplace deep level transient spectroscopy. J. Appl. Phys. 2020, 127, 064503. [Google Scholar] [CrossRef]

- Capan, I.; Brodar, T.; Pastuovi’c, Z.; Siegele, R.; Ohshima, T.; Sato, S.I.; Makino, T.; Snoj, L.; Radulovi´c, V.; Coutinho, J.; et al. Double negatively charged carbon vacancy at the h- and k-sites in 4H-SiC: Combined Laplace-DLTS and DFT study. J. Appl. Phys. 2018, 123, 161597. [Google Scholar] [CrossRef]

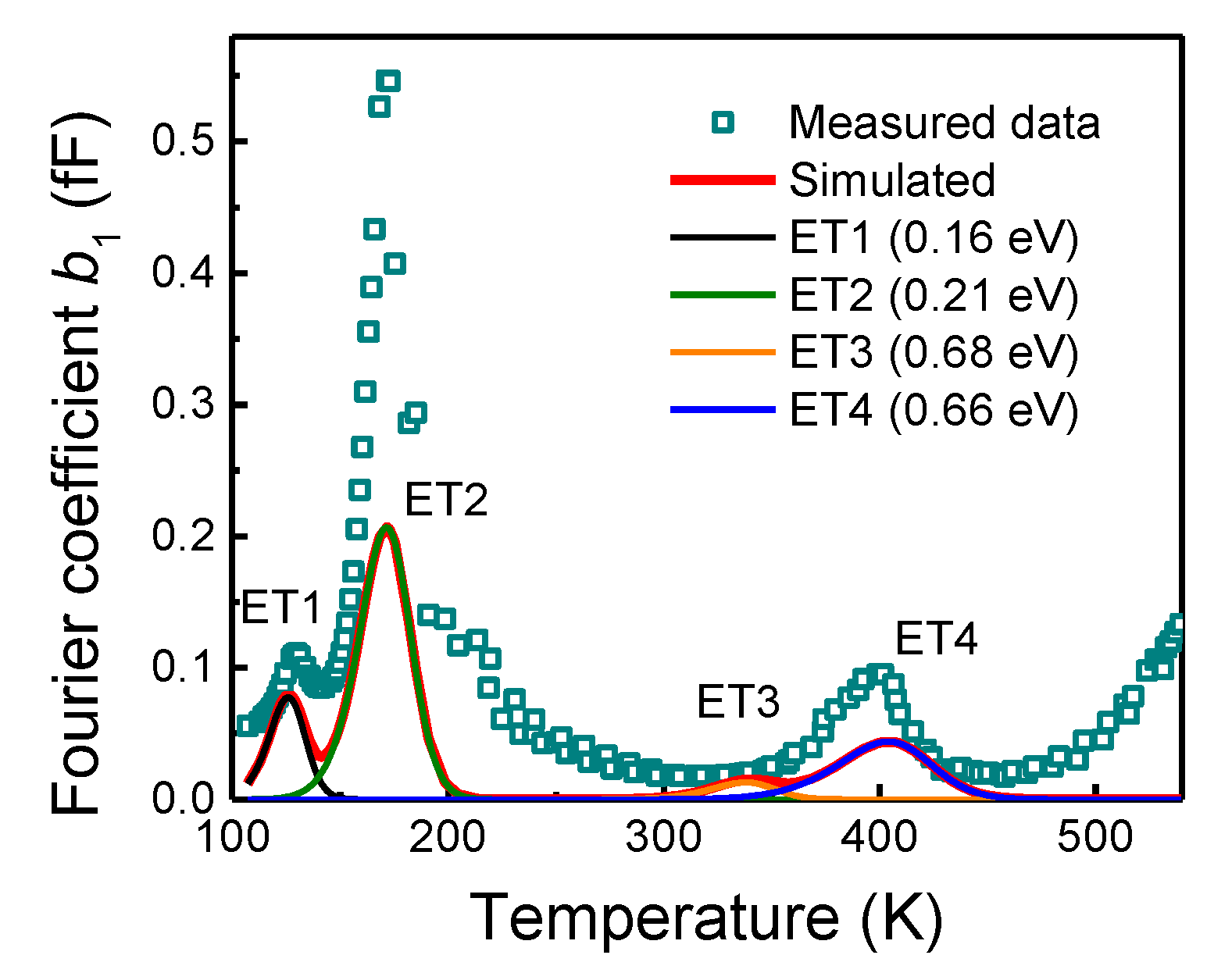

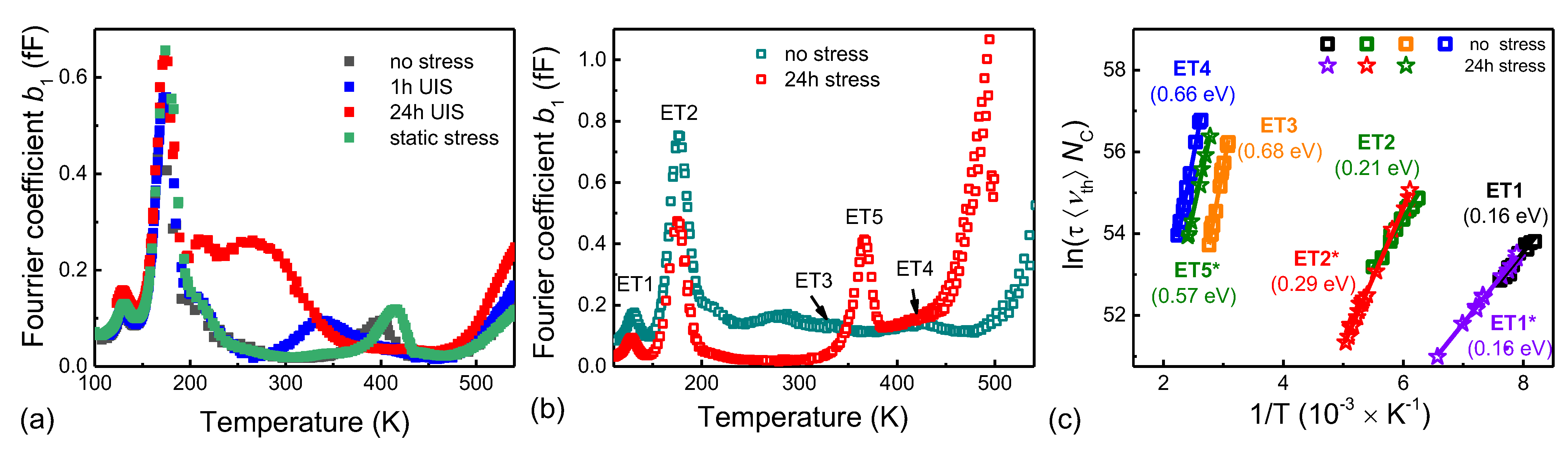

| Trap | Ec-Et (eV) | σ (cm2) | Possible Origin |

|---|---|---|---|

| ET1 | 0.16 ± 0.01 | 1.27 × 10−17 (0.39~3.91 × 10−17) | metal impurity |

| ET1* | 0.16 ± 0.00 | 1.11 × 10−17 (0.81~1.52 × 10−17) | |

| ET2 | 0.21 ± 0.01 | 4.06 × 10−18 (2.44~6.75 × 10−18) | metal impurity |

| ET2* | 0.29 ± 0.00 | 1.12 × 10−15 (0.88~1.44 × 10−15) | |

| ET3 | 0.68 ± 0.01 | 1.37 × 10−14 (0.86~2.18 × 10−14) | transition () |

| ET4 | 0.66 ± 0.01 | 1.11 × 10−16 (0.73~1.69 × 10−16) | transition () |

| ET5* | 0.57 ± 0.02 | 3.39 × 10−17 (1.92~5.99 × 10−17) | transition () |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Marek, J.; Kozarik, J.; Minarik, M.; Chvála, A.; Matus, M.; Donoval, M.; Stuchlikova, L.; Weis, M. Charge Trap States of SiC Power TrenchMOS Transistor under Repetitive Unclamped Inductive Switching Stress. Materials 2022, 15, 8230. https://doi.org/10.3390/ma15228230

Marek J, Kozarik J, Minarik M, Chvála A, Matus M, Donoval M, Stuchlikova L, Weis M. Charge Trap States of SiC Power TrenchMOS Transistor under Repetitive Unclamped Inductive Switching Stress. Materials. 2022; 15(22):8230. https://doi.org/10.3390/ma15228230

Chicago/Turabian StyleMarek, Juraj, Jozef Kozarik, Michal Minarik, Aleš Chvála, Matej Matus, Martin Donoval, Lubica Stuchlikova, and Martin Weis. 2022. "Charge Trap States of SiC Power TrenchMOS Transistor under Repetitive Unclamped Inductive Switching Stress" Materials 15, no. 22: 8230. https://doi.org/10.3390/ma15228230