Reliability Evaluation of Board-Level Flip-Chip Package under Coupled Mechanical Compression and Thermal Cycling Test Conditions

Abstract

:1. Introduction

2. Board-Level Thermal Cycling Tests

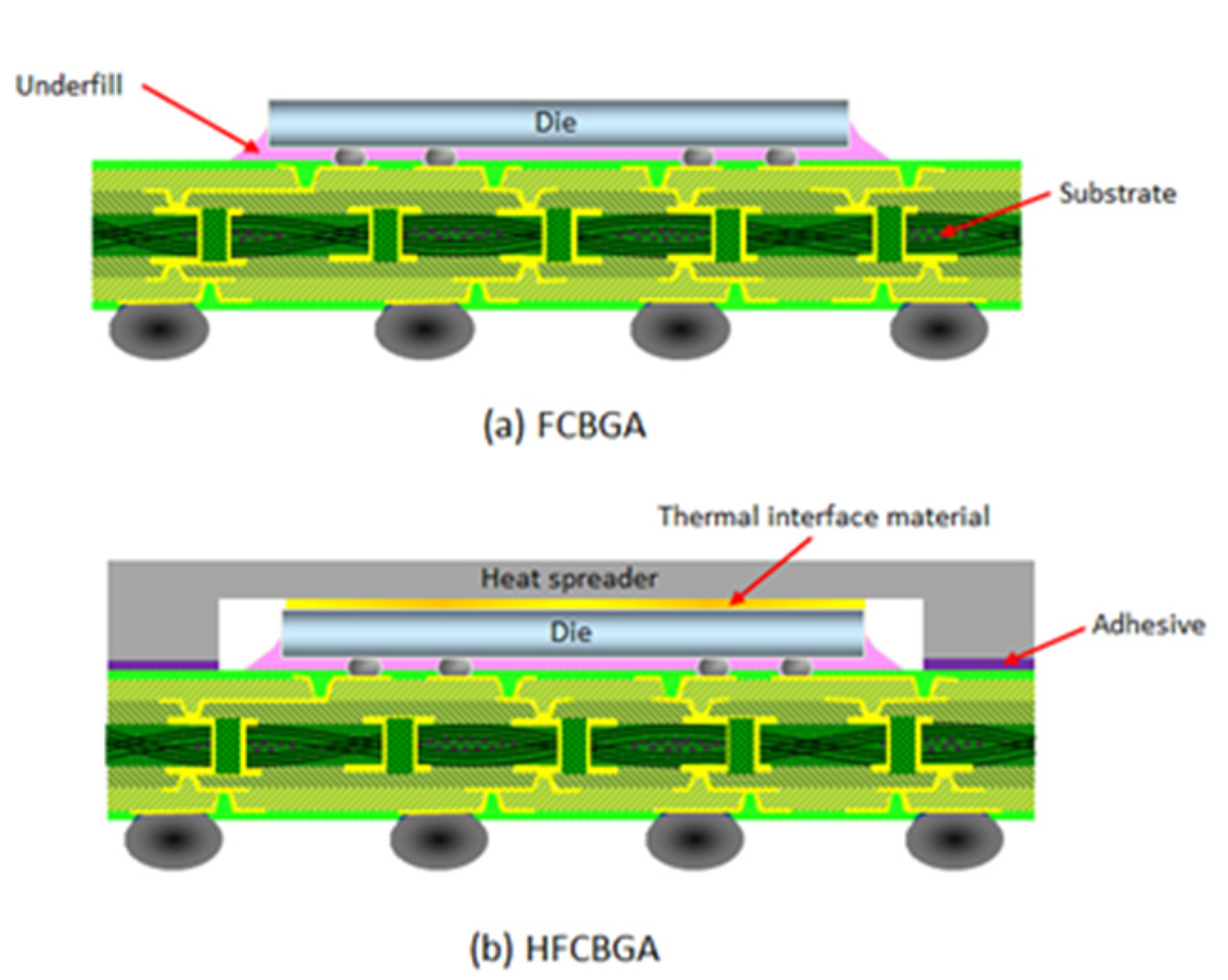

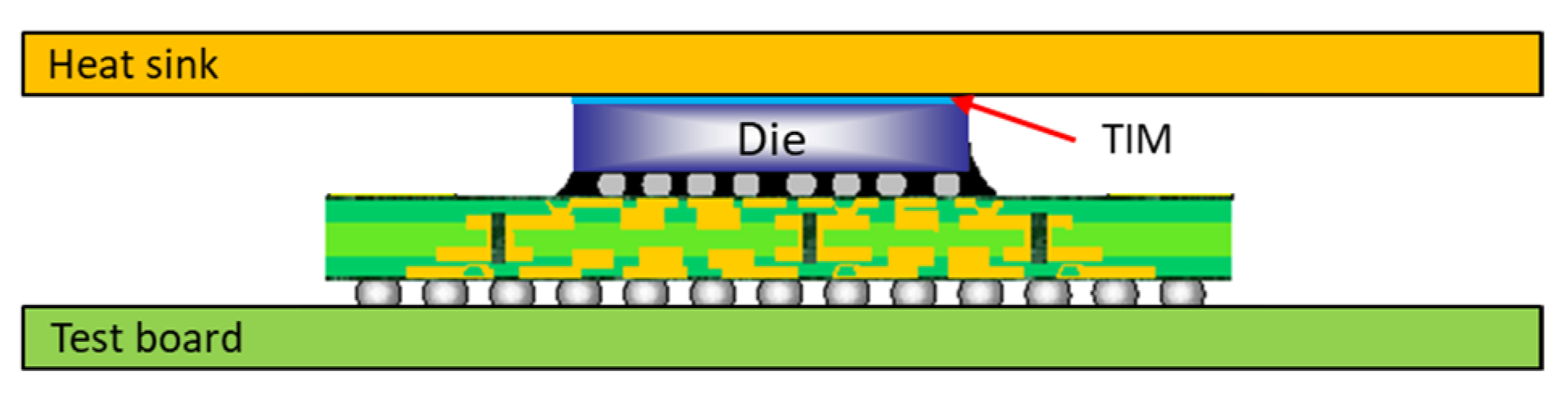

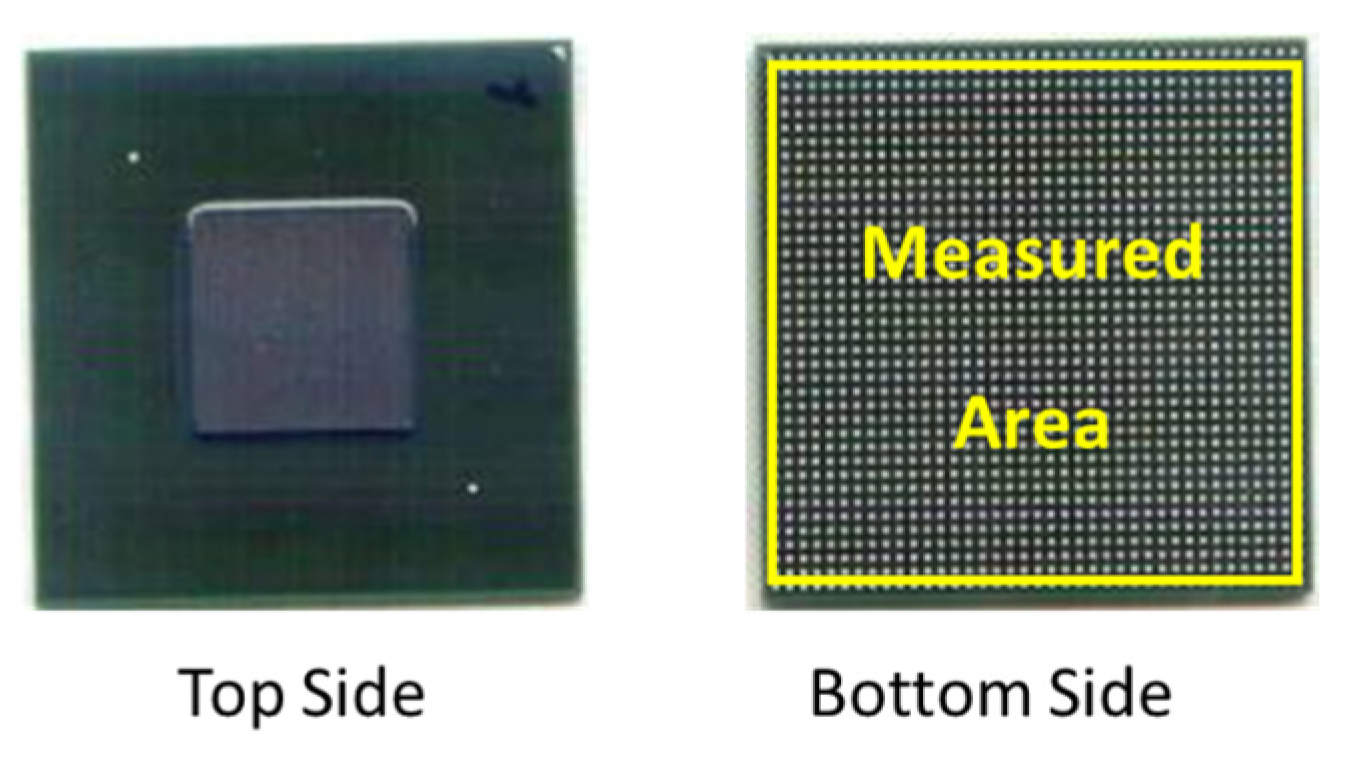

2.1. Test Vehicle Structure

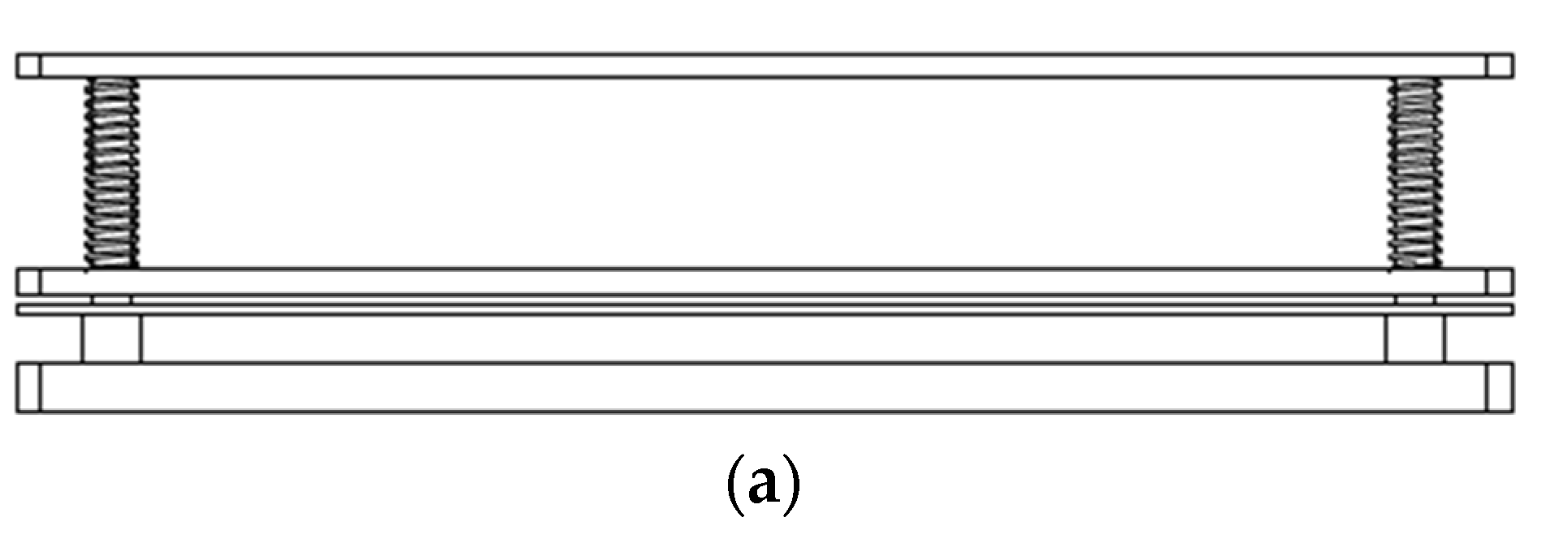

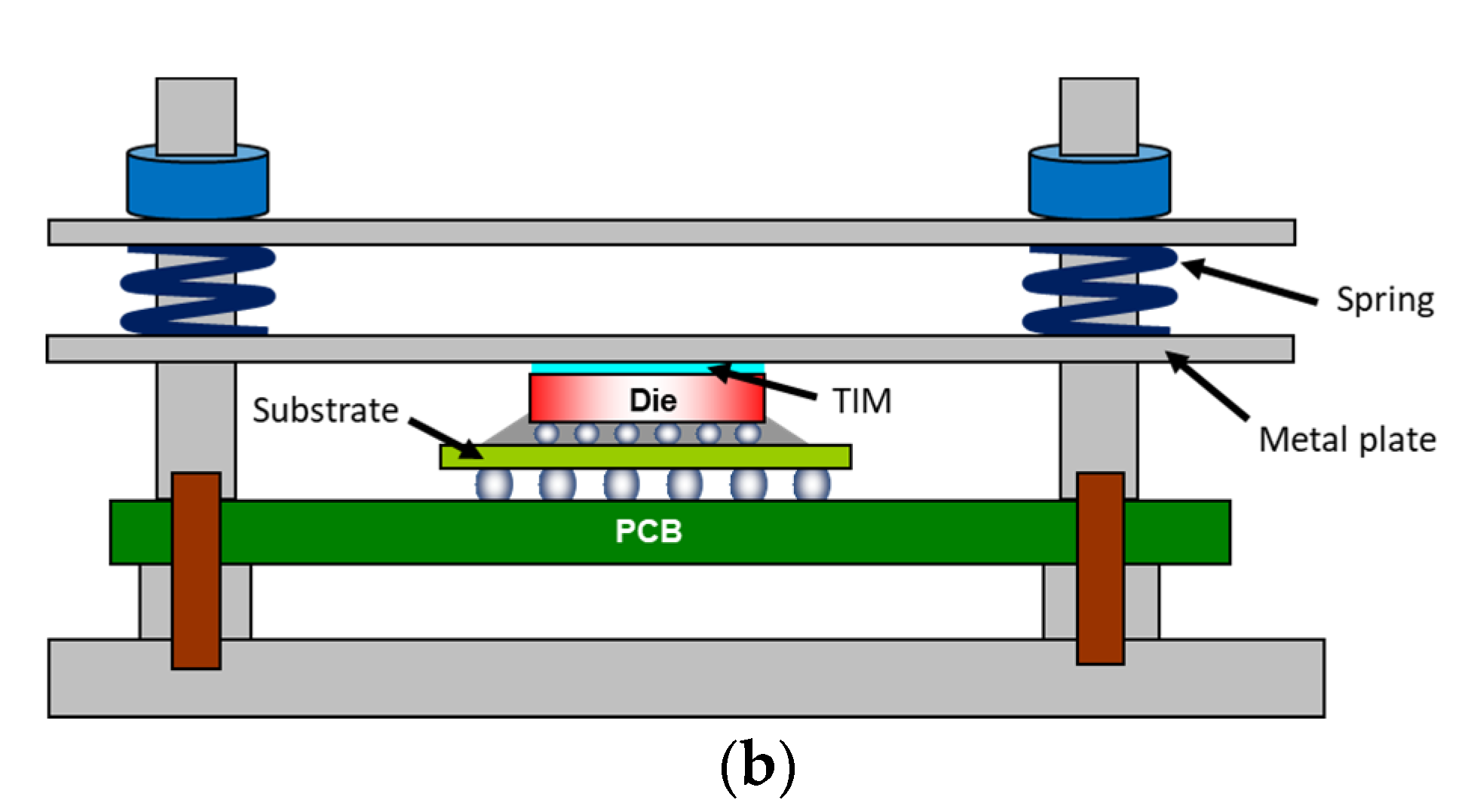

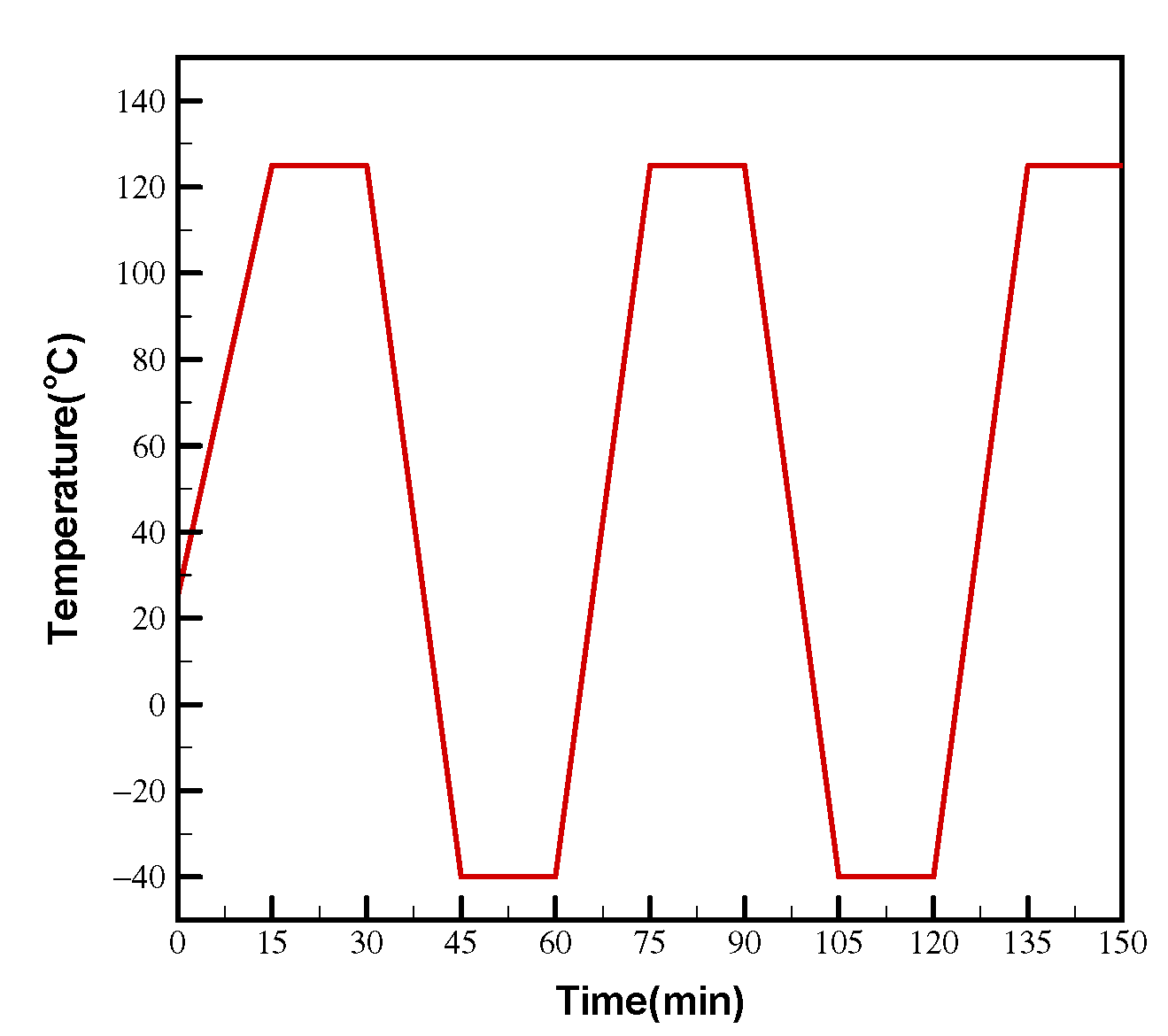

2.2. Thermal Cycling Tests

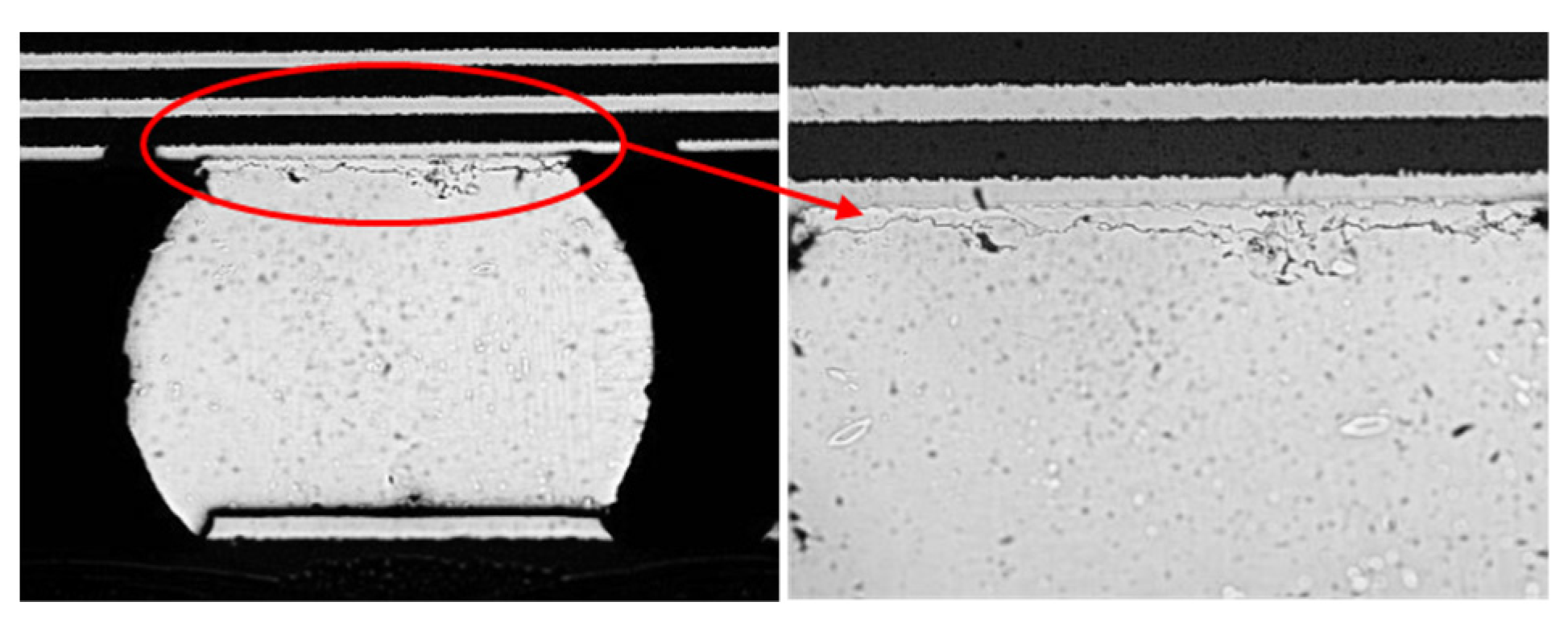

2.3. Thermal Cycling Test Results

3. Coupled Mechanical Compression and Thermal Cycling Simulation

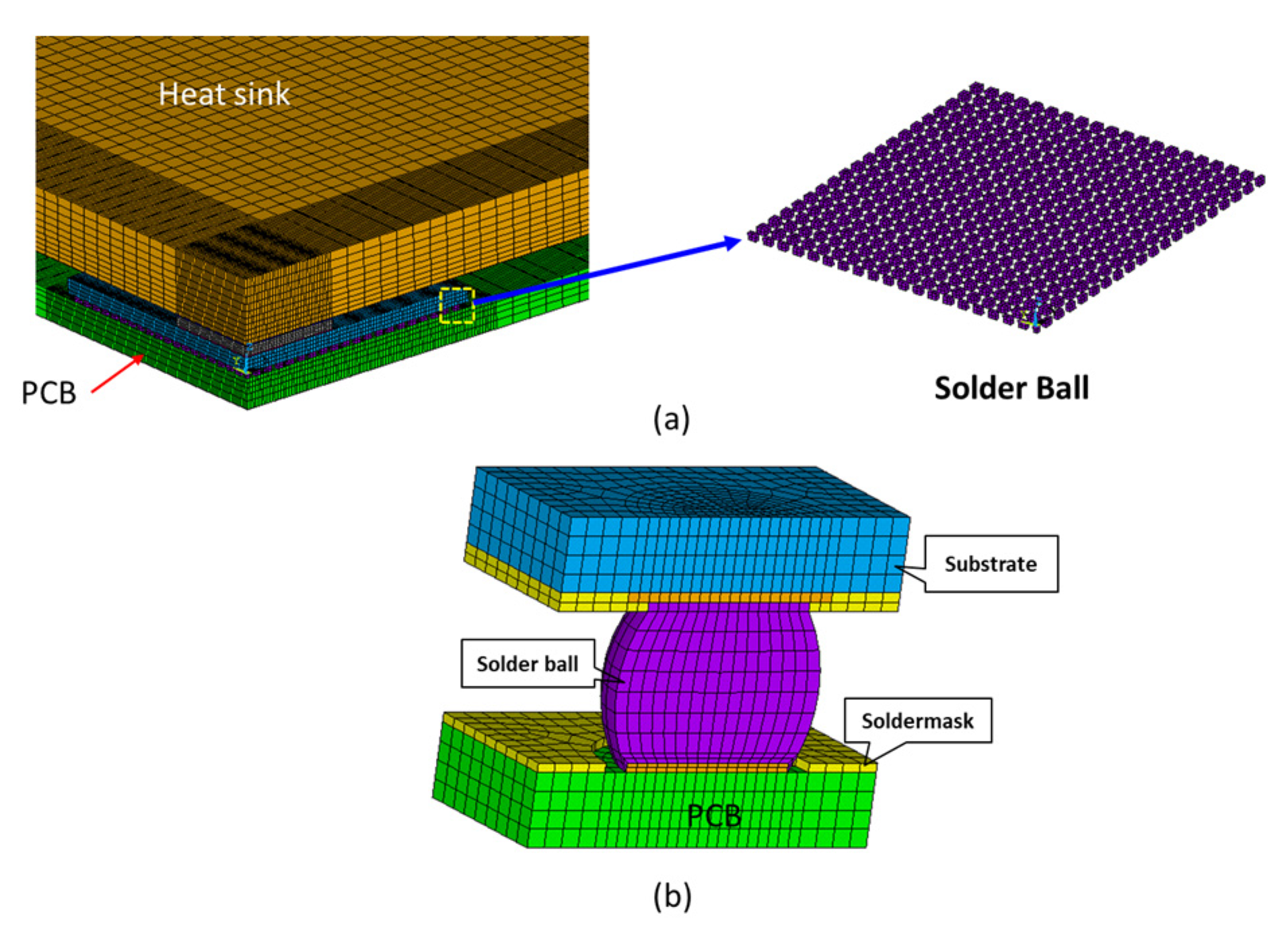

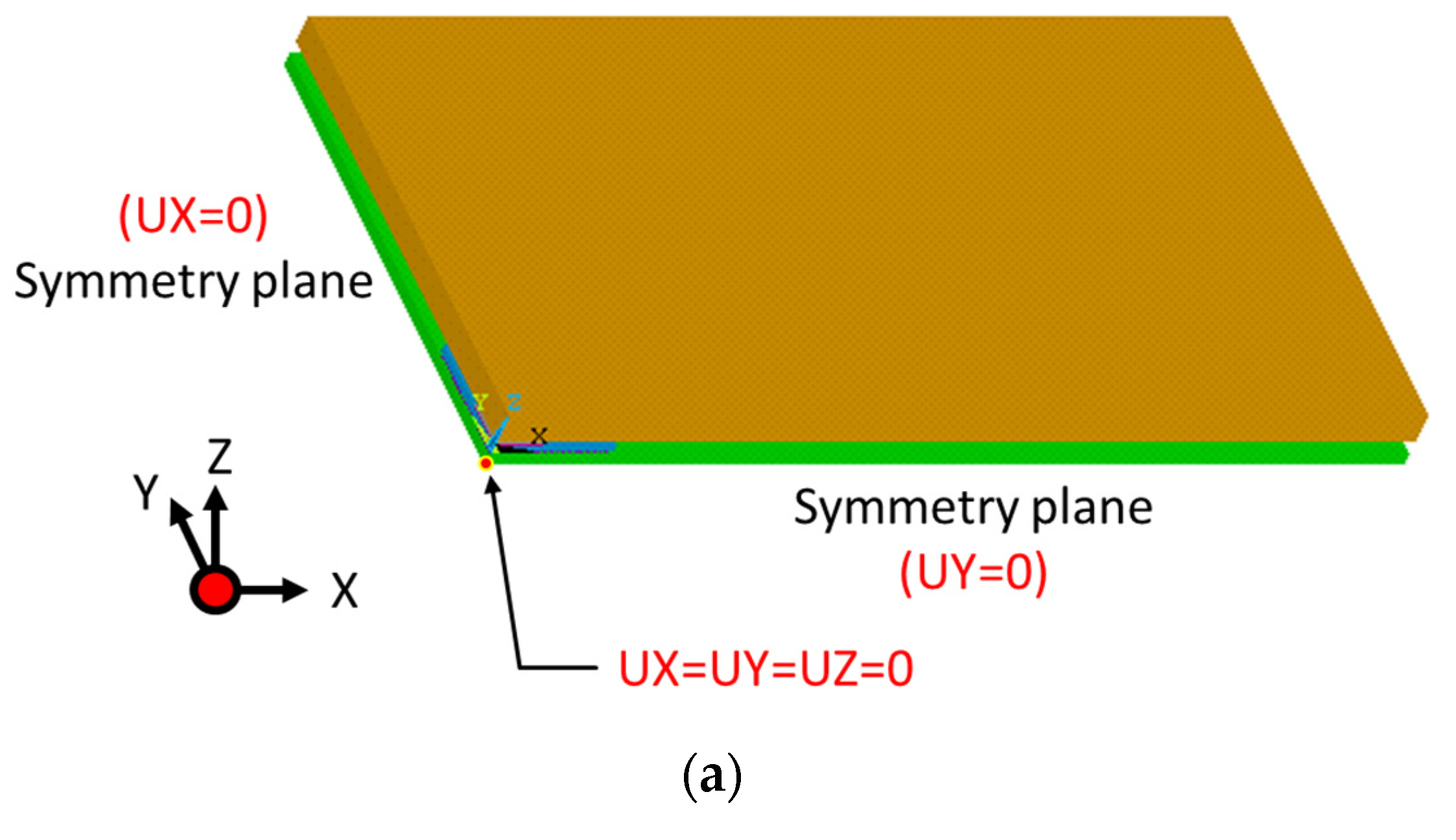

3.1. Finite-Element Modeling

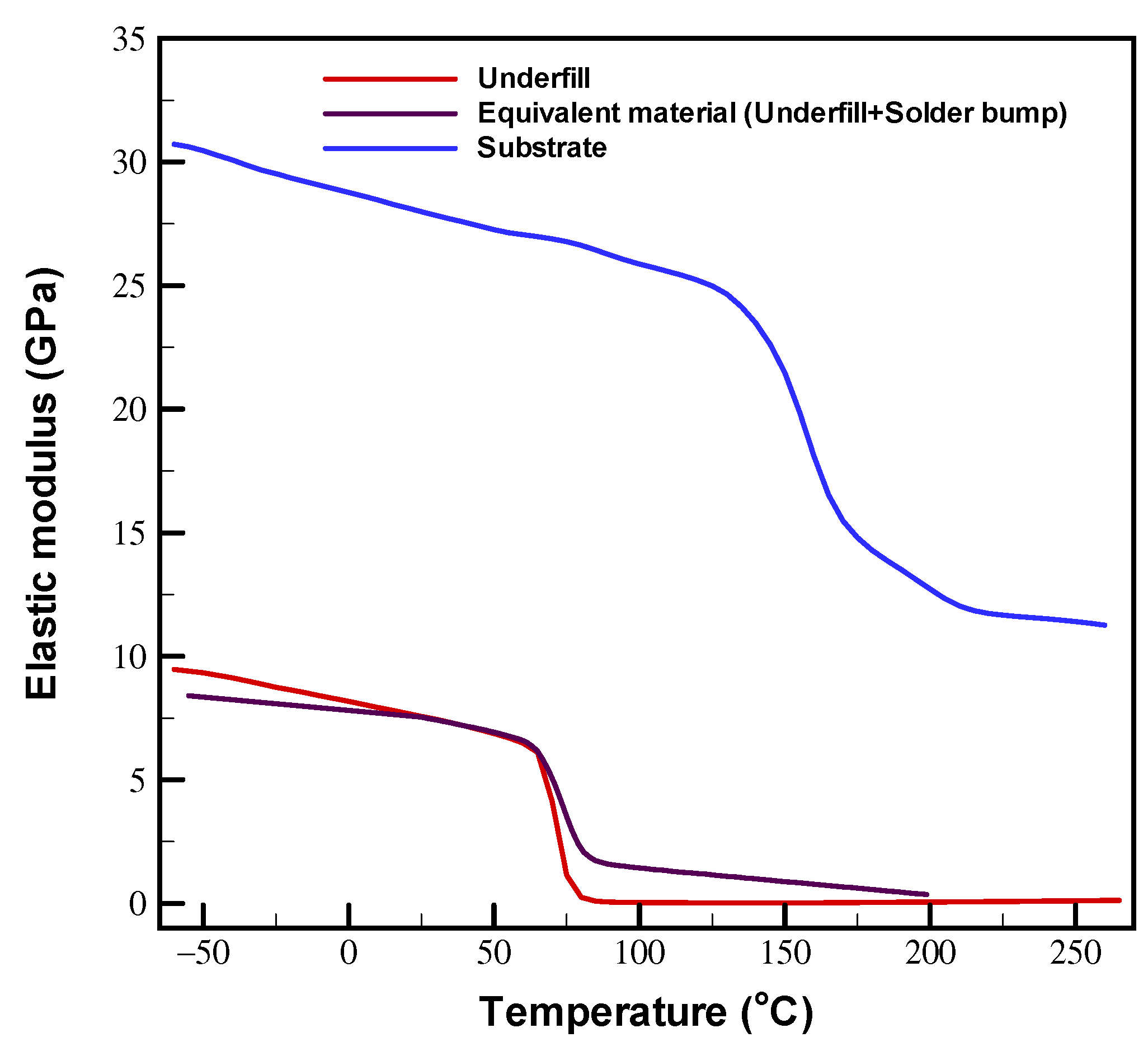

3.2. Material Properties

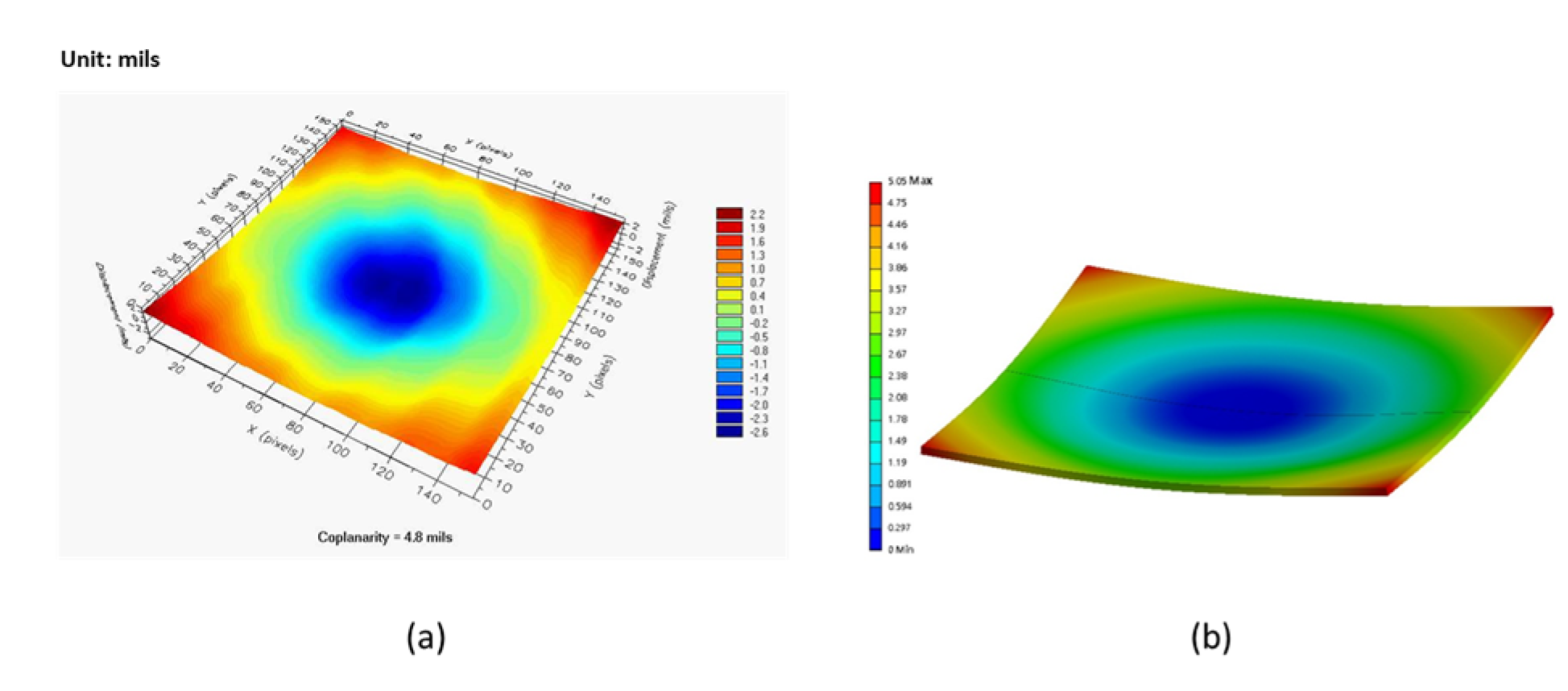

3.3. Verification of Simulation Model

3.4. Solder Joint Reliability Analysis

3.5. Effects of Heat Sink

4. Conclusions

- The board-level TCT results have shown that fracture occurs at the outermost corner solder ball joint in the BGA irrespective of whether or not a heat sink is attached to the package. However, the severity of the solder ball cracking increases under the additional load imposed by the heat sink. Consequently, the number of cycles to first failure is significantly reduced.

- The CSED within the solder balls at the outermost corners of the BGA increases with both the addition of the heat sink to the FCBGA assembly and an increasing distance of the loading force position from the center of the heat sink. A greater loading distance increases the compressive force acting on the BGA as the result of the bending moment, and is thus detrimental to the TCT reliability of the FCBGA assembly.

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Lau, J.H. TSV Manufacturing Yield and Hidden Costs for 3D IC Integration. In Proceedings of the Electronic Components and Technology Conference, Las Vegas, NV, USA, 1–4 June 2010; pp. 1031–1042. [Google Scholar]

- Lee, C.-C.; Hung, C.; Cheung, C.; Yang, P.-F.; Kao, C.-L.; Chen, D.-L.; Shih, M.-K.; Chien, C.-L.C.; Hsiao, Y.-H.; Chen, L.-C.; et al. An Overview of the Development of a GPU with integrated HBM on Silicon Interposer. In Proceedings of the Electronic Components and Technology Conference, Las Vegas, NV, USA, 31 May–3 June 2016; pp. 1439–1444. [Google Scholar]

- Wu, Z.-J.; Carey, C.; Donavan, S.; Hunt, D.; Justison, P.; Anemikos, T.; Cincotta, J.; Gagnon, H.; Chacon, O.; Martel, R.; et al. Chip-Package Interaction Challenges for Large Die Applications. In Proceedings of the Electronic Components and Technology Conference, San Diego, CA, USA, 29 May–1 June 2018; pp. 656–662. [Google Scholar]

- Shih, M.-K.; Lai, W.; Liao, T.; Chen, K.; Chen, D.-L.; Hung, C.P. Thermal and Mechanical Characterization of 2.5-D and Fan-Out Chip on Substrate Chip-First and Chip-Last Packages. IEEE Trans. Compon. Packag. Manuf. Technol. 2022, 12, 297–305. [Google Scholar] [CrossRef]

- Wang, T.H.; Chen, H.-Y.; Lee, C.-C.; Lai, Y.-S. High-powered thermal gel degradation evaluation on board-level HFCBGA subjected to reliability tests. Microelectron. Eng. 2011, 88, 3101–3107. [Google Scholar] [CrossRef]

- Zhang, H.Y.; Zhang, X.W.; Lau, B.L.; Lim, S.; Ding, L.; Yu, M.B.; Lee, Y.J. Thermal characterization and simulation study of 2.5D packages with multi-chip module on through silicon interposer. In Proceedings of the Electronics Packaging Technology Conference, Las Vegas, NV, USA, 28–31 May 2013; pp. 363–368. [Google Scholar]

- Morgan, A.; Choobineh, L.; Fresne, D.; Hopkins, D.C. Numerical and experimental determination of temperature distribution in 3D stacked power devices. In Proceedings of the International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems, San Francisco, CA, USA, 29 August–1 September 2017; pp. 363–368. [Google Scholar]

- Silveira, J.V.T.; Li, Z.; Yang, B.; Yasui, R.; Shinoda, T.; Fushinobu, K. Analysis of heat transfer from a heat dissipating device on a substrate. In Proceedings of the InterSociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, Las Vegas, NV, USA, 28–31 May 2019; pp. 446–450. [Google Scholar]

- Hu, I.; Tsai, J.-C.; Cheng, F.; Yen, S.-F.; Shih, M.-K.; Tarng, D.; Pai, B.; Hung, C. High Power Large Size HFCBGA Thermal Characterization. In Proceedings of the Electronics Packaging Technology Conference, Singapore, 4–6 December 2019; pp. 467–471. [Google Scholar]

- Nayini, M.; Horn, T.; Patel, J.; Burrell, L. Coupled thermal-mechanical simulation methodology to estimate BGA reliability of 2.5D Packages. In Proceedings of the Electronic Components and Technology Conference, Orlando, FL, USA, 3–30 June 2020; pp. 1653–1658. [Google Scholar]

- Loeblein, M.; Tsang, S.H.; Han, Y.; Zhang, X.; Teo, E.H.T. Heat Dissipation Enhancement of 2.5D Package with 3D Graphene & 3D Boron Nitride Networks as Thermal Interface Material (TIM). In Proceedings of the Electronic Components and Technology Conference, Las Vegas, NV, USA, 31 May–3 June 2016; pp. 707–713. [Google Scholar]

- Huang, Y.L.; Chung, C.K.; Lin, C.; Yu, K.H.; Lin, R.J.; Hong, W. Highly Thermal Dissipation for Large HPC Package Using Liquid Metal Materials. In Proceedings of the Electronic Components and Technology Conference, Virtual, 1 June–4 July 2021; pp. 1102–1108. [Google Scholar]

- Chen, H.; Lim, T.G.; Tang, G. Thermal Challenges and Design Considerations in Heterogeneous Integrated Through-Silicon-interposer Platform for III-V HEMT Flip Chip. In Proceedings of the Electronic Components and Technology Conference, San Diego, CA, USA, 31 May–3 June 2022; pp. 1030–1035. [Google Scholar]

- Han, Y.; Li, H.; Lim, S.S.H.; Kawano, M. Thermal Analysis of 2.5D Package in High Power Application. In Proceedings of the Electronics Packaging Technology Conference, Singapore, 4–6 December 2019; pp. 402–405. [Google Scholar]

- Rajan, S.K.; Ramakrishnan, B.; Alissa, H.; Kim, W.; Belady, C.; Bakir, M.S. Integrated Silicon Microfluidic Cooling of a High-Power Overclocked CPU for Efficient Thermal Management. IEEE Access 2022, 10, 59259–59269. [Google Scholar] [CrossRef]

- Lin, P.-Y.; Kuo, S.-L.; Yan, K.; Chen, W.-M.; Liao, M.D.-D. Advanced Thermal Integration for HPC Packages with Two-Phase Immersion Cooling. In Proceedings of the Electronic Components and Technology Conference, San Diego, CA, USA, 31 May–3 June 2022; pp. 566–573. [Google Scholar]

- Su, P.-J.; Lin, D.; Lin, S.; Xu, X.-Z.; Lin, R.J.; Hung, L.-Y.; Wang, Y.-P. High Thermal Graphite TIM Solution Applied to Fan-Out Platform. In Proceedings of the Electronic Components and Technology Conference, San Diego, CA, USA, 31 May–3 June 2022; pp. 1224–1227. [Google Scholar]

- Mandal, R.; Chong, C.T. Mechanical modeling study for fan-out wafer level package parameters to enhance BGA TCoB life. In Proceedings of the Electronics Packaging Technology Conference, Singapore, 7–9 December 2021; pp. 589–593. [Google Scholar]

- Yang, H.-C.; Chiu, T.-C. Numerical implementation of a unified viscoplastic model for considering solder joint response under board-level temperature cycling. Comput. Model. Eng. Sci. 2021, 128, 639–668. [Google Scholar] [CrossRef]

- Afripin, A.; Hauck, T. Influence of Ball Grid Array Design Parameters on Solder Joint Reliability. In Proceedings of the International Electronics Manufacturing Technology Conference, Kuala Lumpur, Malaysia, 19–21 October 2022. [Google Scholar]

- Shao, S.; Niu, Y.; Wang, J.; Liu, R.; Park, S.; Lee, H.; Yip, L.; Refai-Ahmed, G. Design guideline on board-level thermomechanical reliability of 2.5D package. Microelectron. Reliab. 2020, 111, 113701. [Google Scholar] [CrossRef]

- Lau, J.H.; Ko, C.T.; Peng, C.Y.; Yang, K.M.; Xia, T.; Lin, P.B.; Chen, J.-J.; Huang, P.-C.; Tseng, T.-J.; Lin, E.; et al. Thermal cycling test and simulation of fan-out chip-last panel-level packaging for heterogeneous integration. J. Microelectron. Electron. Packag. 2020, 18, 29–39. [Google Scholar] [CrossRef]

- Ahmed, O.; Hutchinson, L.; Su, P.; Jiang, T. Effects of Heatsink Application and PCB Design Variations on BGA Solder Joint Reliability. In Proceedings of the Electronic Components and Technology Conference, Virtual, 1 June–4 July 2021; pp. 1001–1006. [Google Scholar]

- Ji, L.; Chai, T.C. Reliability life assessment and prediction for high density FOWLP package using finite element analysis and statistical approach. In Proceedings of the Electronic Components and Technology Conference, Virtual, 1 June–4 July 2021; pp. 1359–1365. [Google Scholar]

- Yang, J.; Cai, C.; Yin, P.; Pan, K.; Lai, Y.; Wang, J.; Park, S. Optimal thermo-mechanical reliability design of 2.5D lidless package. In Proceedings of the InterSociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, San Diego, CA, USA, 31 May–3 June 2022. [Google Scholar]

- IPC-9701A; Performance Test Methods and Qualification Requirements for Surface Mount Solder Attachments. IPC: Northbrook, IL, USA, 2002.

- JESD22-A104E; Temperature Cycling. JEDEC Solid State Technology Association: Arlington County, VA, USA, 2014.

- Shih, M.-K.; Huang, Y.-W.; Lin, G.-S. Next-Generation High-Density PCB Development by Fan-Out RDL Technology. IEEE Trans. Device Mater. Reliab. 2022, 22, 296–305. [Google Scholar] [CrossRef]

- Park, S.; Lee, H.C.; Sammakia, B.; Raghunathan, K. Predictive model for optimized design parameters in flip-chip packages and assemblies. IEEE Trans. Compon. Packag. Technol. 2007, 30, 294–301. [Google Scholar] [CrossRef]

- Lee, C.-C.; Wang, C.-W.; Chen, C.-Y. Comparison of Mechanical Modeling to Warpage Estimation of RDL-First Fan-Out Panel-Level Packaging. IEEE Trans. Compon. Packag. Manuf. Technol. 2022, 12, 1100–1108. [Google Scholar] [CrossRef]

- Dasgupta, A.; Oyan, C.; Barker, D.; Pecht, M. Solder Creep-Fatigue Analysis by an Energy-Partitioning Approach. ASME. J. Electron. Packag. 1992, 114, 152–160. [Google Scholar] [CrossRef]

- Zahn, B.A. Solder Joint Fatigue Life Model Methodology for 63Sn37Pb and 95.5Sn4Ag0.5Cu Materials. In Proceedings of the Electronic Components and Technology Conference, New Orleans, LA, USA, 27–30 May 2003; pp. 83–94. [Google Scholar]

- Hertzberg, R.W.; Hauser, F.E. Deformation and Fracture Mechanics of Engineering Materials, 4th ed.; John Wiley & Sons Inc.: New York, NY, USA, 1996. [Google Scholar]

- Schubert, A.; Dudek, R.; Auerswald, E.; Gollbardt, A.; Michel, B.; Reichl, H. Fatigue life models for SnAgCu and SnPb solder joints evaluated by experiments and simulation. In Proceedings of the Electronic Components and Technology Conference, New Orleans, LA, USA, 27–30 May 2003; pp. 603–610. [Google Scholar]

| Package size (mm) | 40 × 40 |

| Die size (mm) | 15.5 × 15.5 × 0.78 |

| Substrate thickness (mm) | 1.2 |

| Underfill thickness (μm) | 25 |

| Sample | Cycles to First Failure | |

|---|---|---|

| W/O Heat Sink | W/Heat Sink | |

| 1 | 3652 | 2694 |

| 2 | 3689 | 2496 |

| 3 | 3865 | 2587 |

| Component | E (GPa) | CTE (ppm/°C) | Tg (°C) | ν |

|---|---|---|---|---|

| Die | 131 | 2.8 | - | 0.30 |

| Solder mask | 2.7 | 50/140 | 100 | 0.30 |

| Underfill | Figure 12 | 32/110 | 70 | 0.30 |

| Substrate | Figure 12 | X/Y: 23.46 Z: 52.65/156.4 | 156 | 0.30 |

| Test board | X/Y: C0 = 27.924, C1 = −0.0372 Z: C0 = 12.203, C1 = −0.016 | X/Y: 16.5 Z: 67.2 | - | 0.39 |

| Solder Ball | 48.5@-55 °C 33@210 °C | 20 | - | 0.35 |

| TIM | 0.0083 | 14 | - | 0.35 |

| Heat spreader | 68 | 24 | - | 0.344 |

| Constant | Unit | Value |

|---|---|---|

| C1 | S−1 | 277,984 |

| C2 | MPa−1 | 0.02447 |

| C3 | n | 6.41 |

| C4 | K | 6489.7 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shih, M.-K.; Liu, Y.-H.; Lee, C.; Hung, C.P. Reliability Evaluation of Board-Level Flip-Chip Package under Coupled Mechanical Compression and Thermal Cycling Test Conditions. Materials 2023, 16, 4291. https://doi.org/10.3390/ma16124291

Shih M-K, Liu Y-H, Lee C, Hung CP. Reliability Evaluation of Board-Level Flip-Chip Package under Coupled Mechanical Compression and Thermal Cycling Test Conditions. Materials. 2023; 16(12):4291. https://doi.org/10.3390/ma16124291

Chicago/Turabian StyleShih, Meng-Kai, Yu-Hao Liu, Calvin Lee, and C. P. Hung. 2023. "Reliability Evaluation of Board-Level Flip-Chip Package under Coupled Mechanical Compression and Thermal Cycling Test Conditions" Materials 16, no. 12: 4291. https://doi.org/10.3390/ma16124291

APA StyleShih, M.-K., Liu, Y.-H., Lee, C., & Hung, C. P. (2023). Reliability Evaluation of Board-Level Flip-Chip Package under Coupled Mechanical Compression and Thermal Cycling Test Conditions. Materials, 16(12), 4291. https://doi.org/10.3390/ma16124291