Unified Modeling and Double-Loop Controller Design of Three-Level Boost Converter

Abstract

:1. Introduction

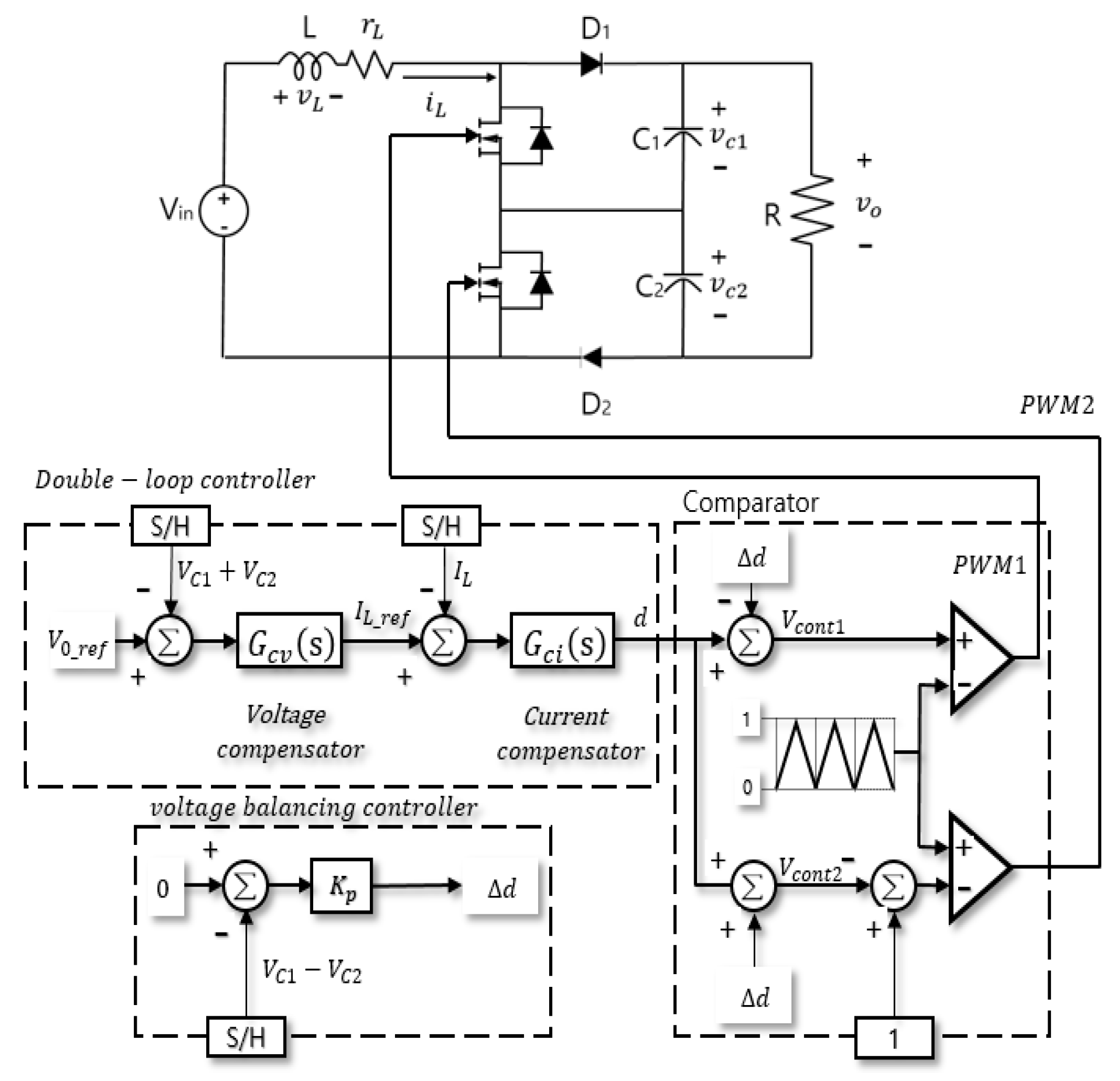

2. Proposed Unified Modeling of TLB Converter

Mode Analysis

- A.

- Mode 1 operation analysis

- B.

- Mode 2 system analysis

- C.

- Unified small-signal modeling

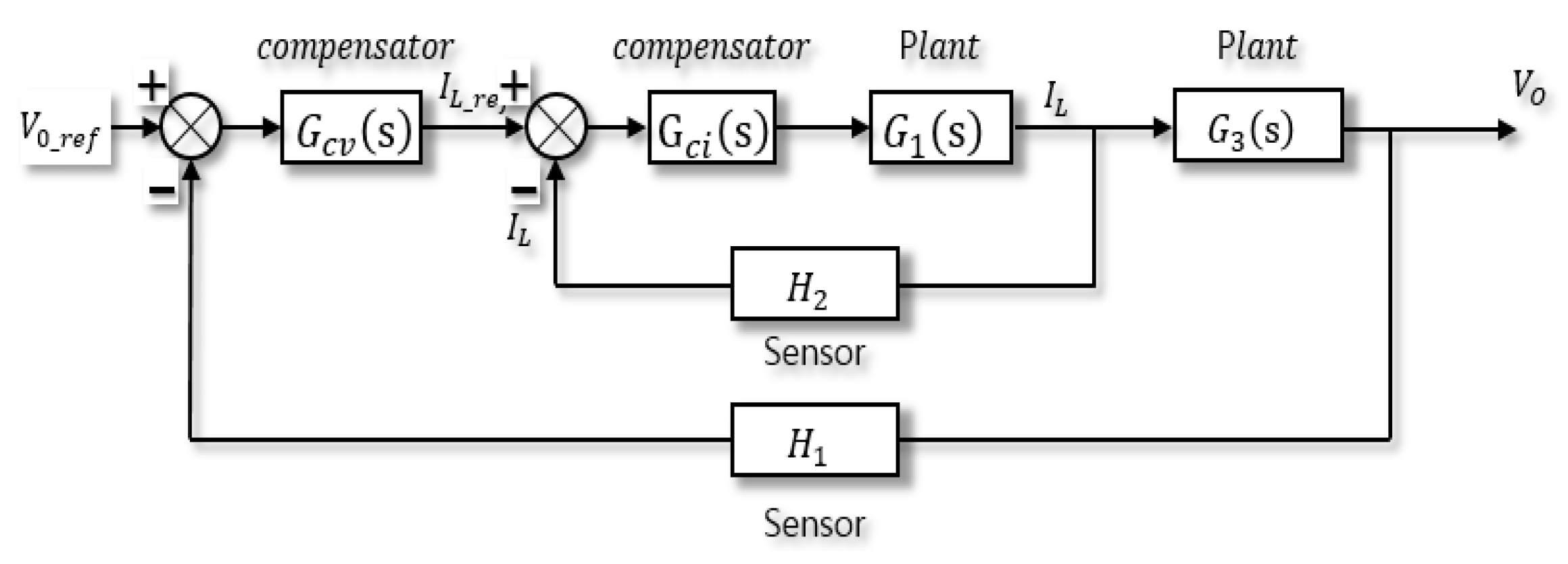

3. Controller Design

- A.

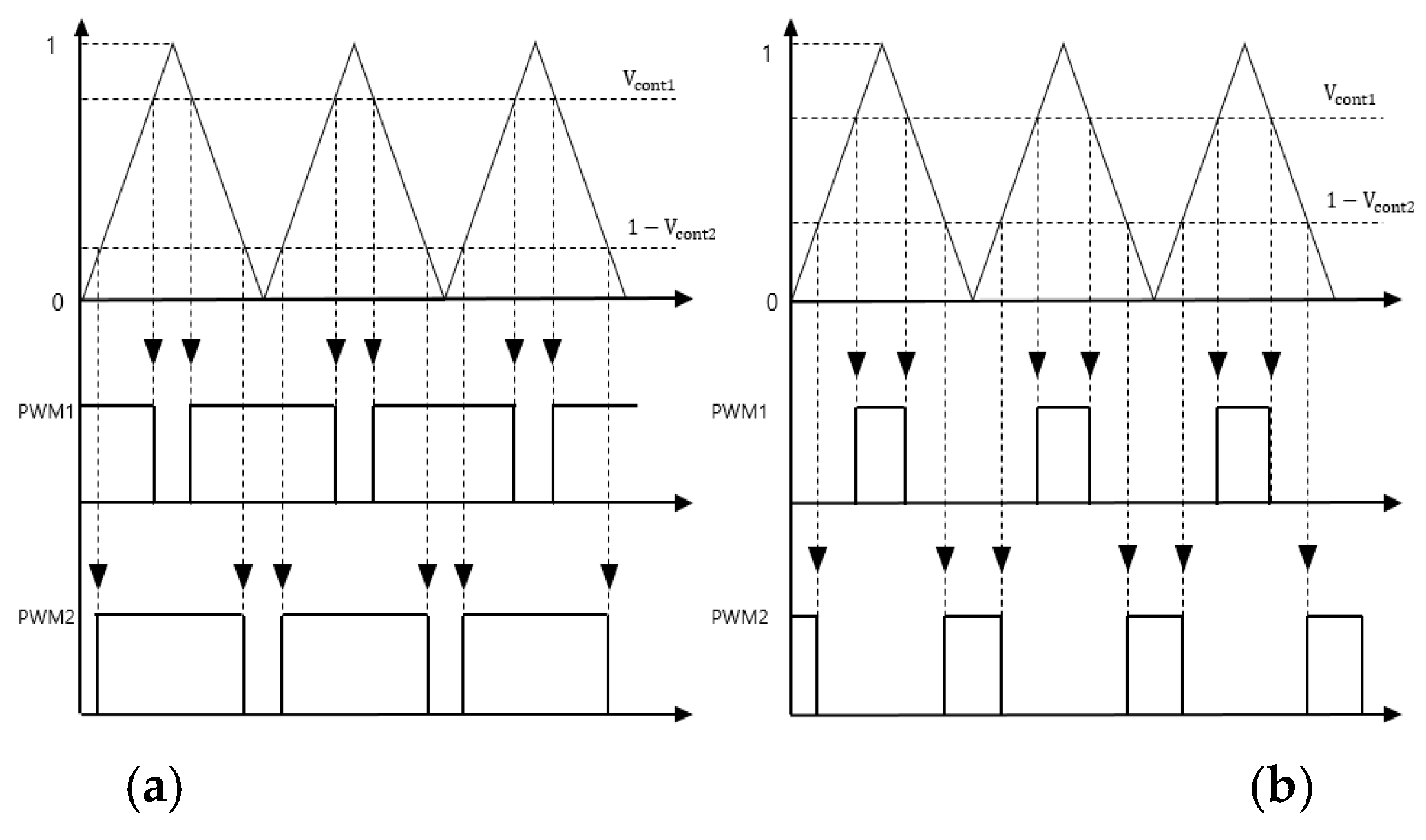

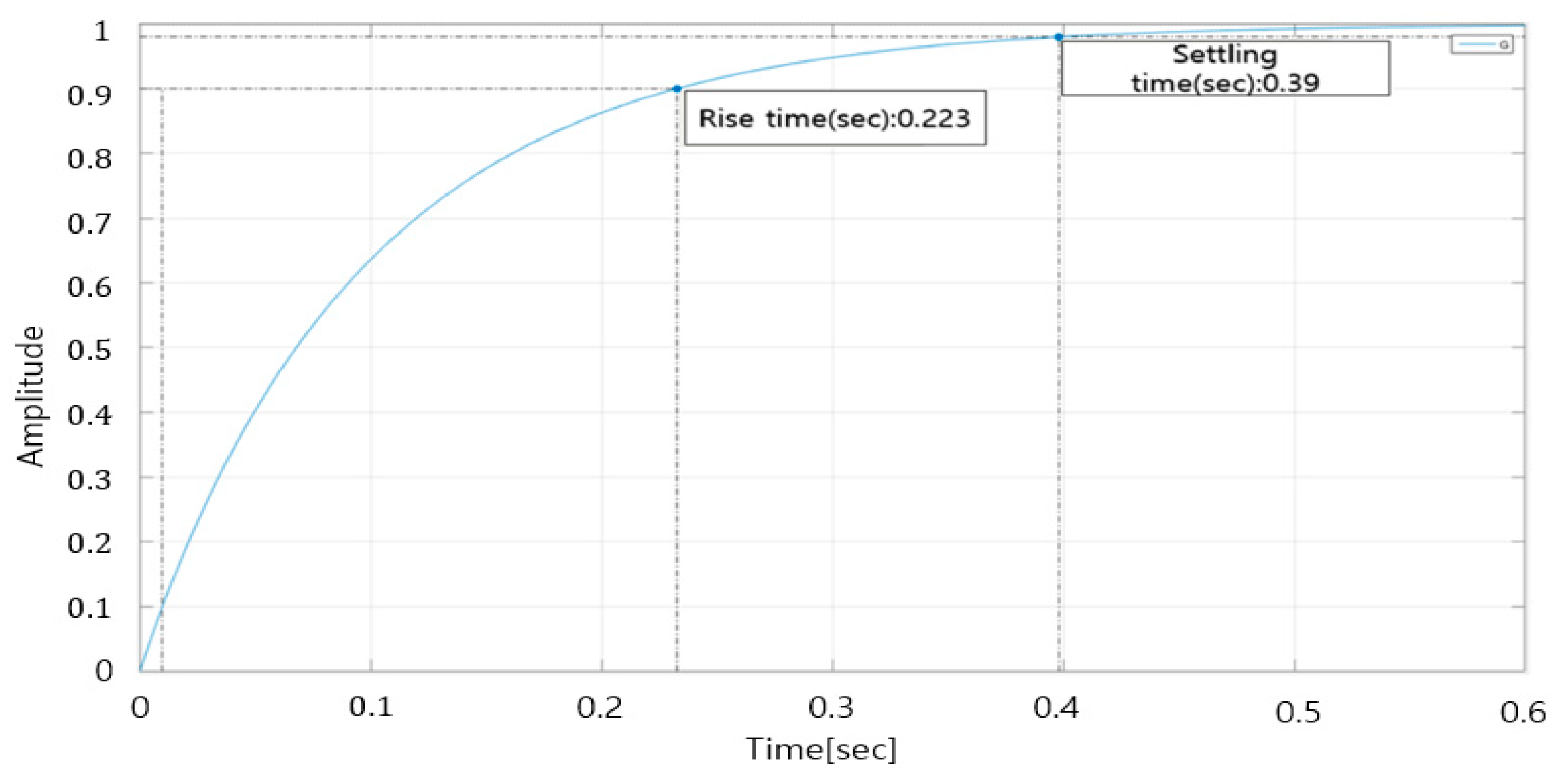

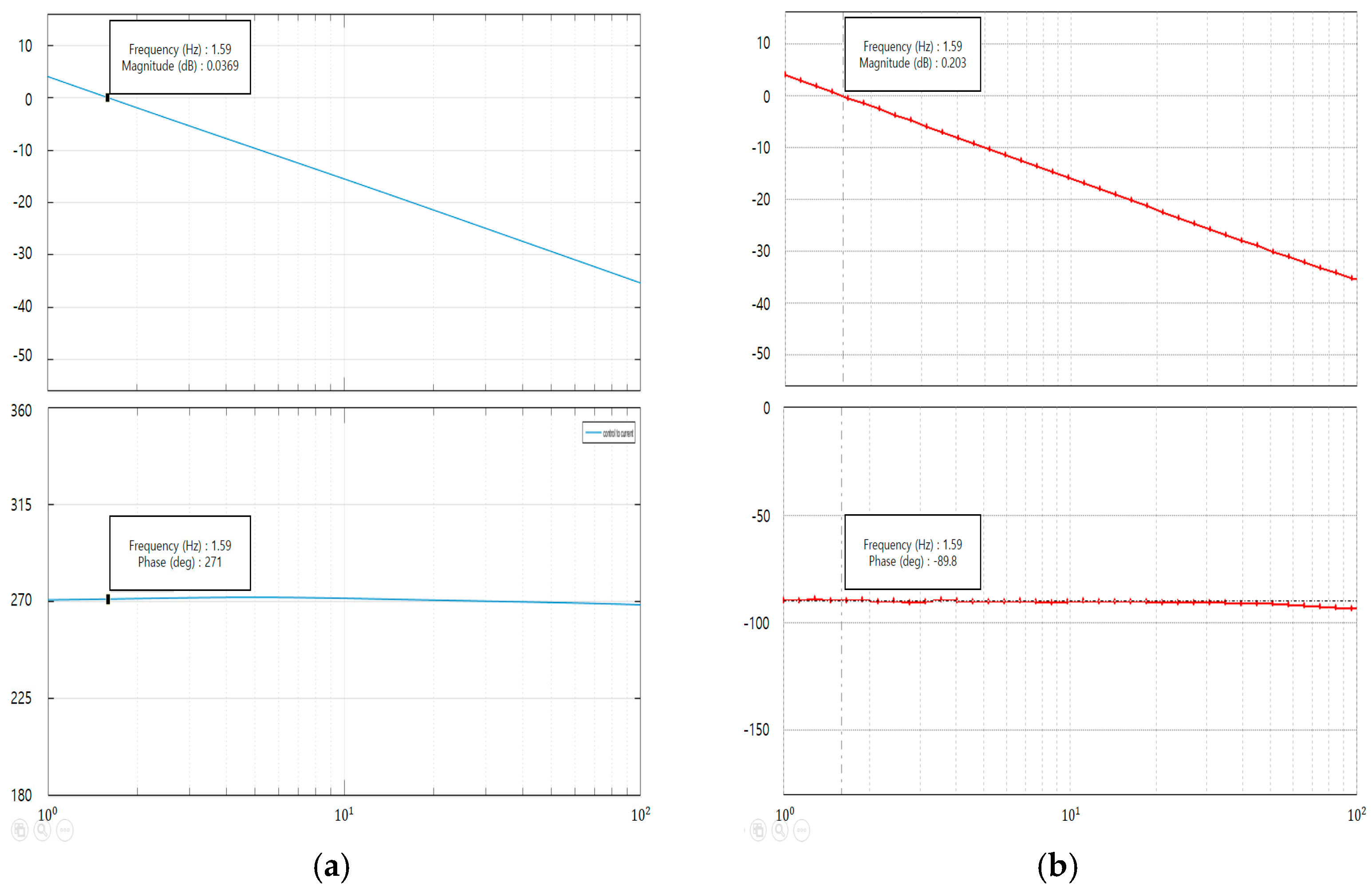

- Double-loop controller design

- B.

- Capacitor-voltage-balancing controller design

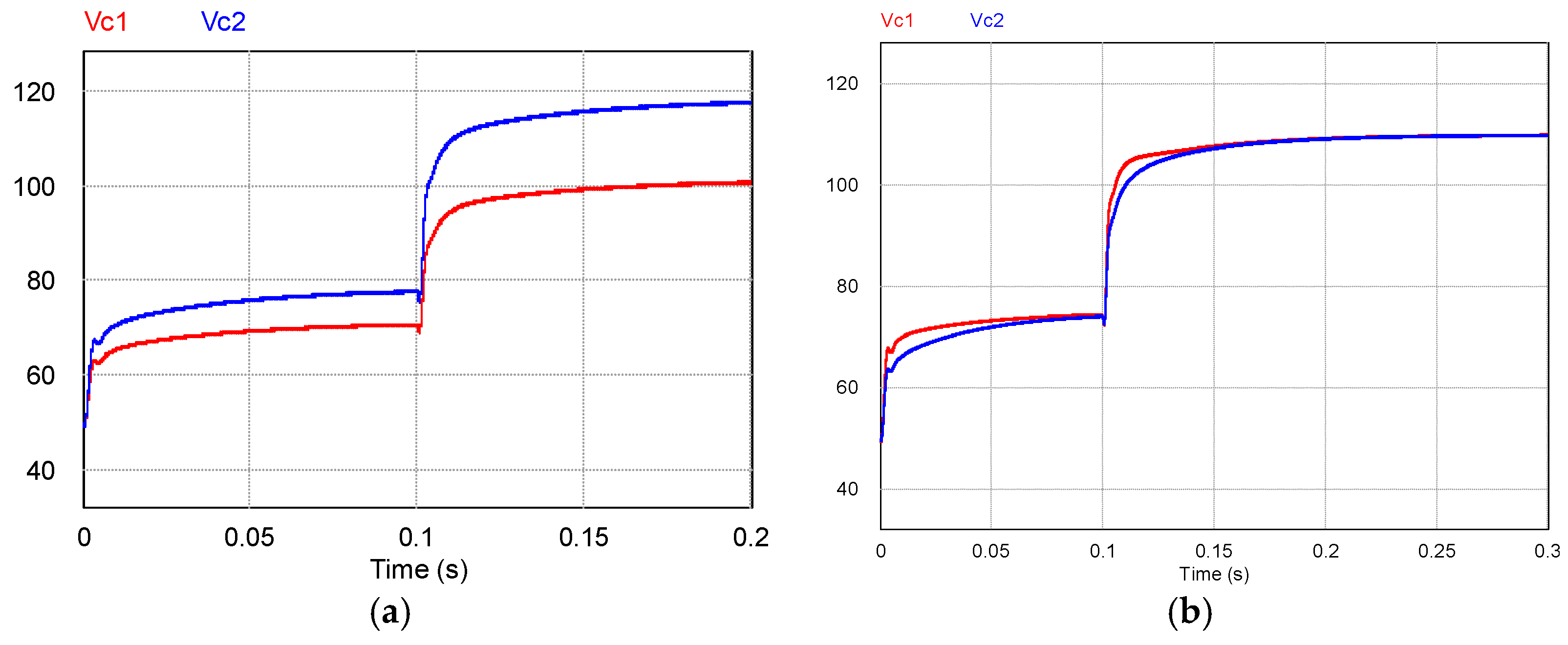

4. Simulation Results

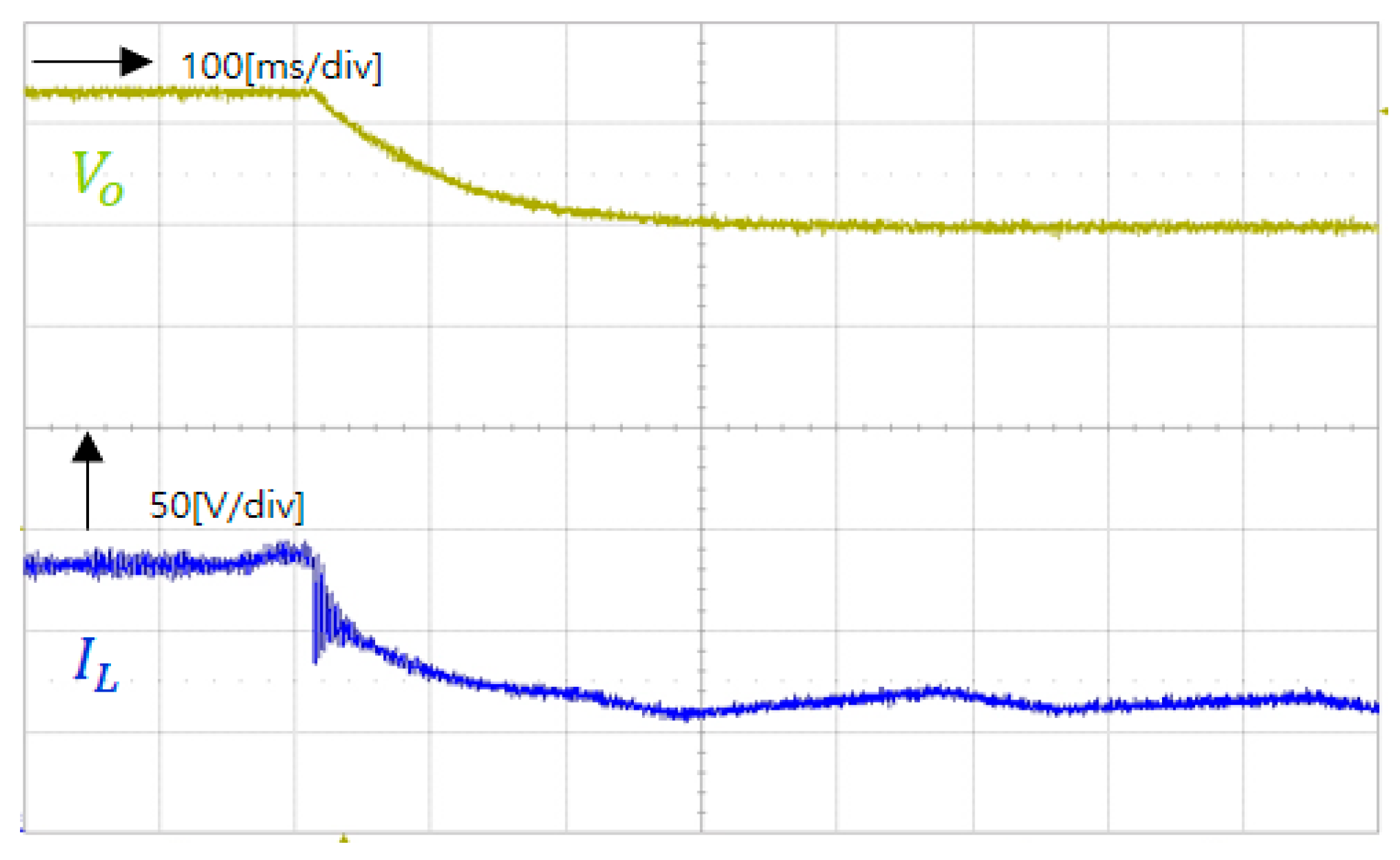

5. Experimental Validation

6. Discussion

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Nomenclature

| Output voltage, Sum of capacitor voltages | |

| Capacitor 1 voltage | |

| Capacitor 2 voltage | |

| Series capacitance of and () | |

| Inductor resistance | |

| Inductance | |

| Load resistance | |

| Duty ratio | |

| Inductor current | |

| Input voltage | |

| Small signal of inductor current | |

| Small signal of output voltage | |

| Small signal of duty ratio | |

| Steady-state value of inductor current | |

| Steady-state value of output voltage | |

| Steady-state value of duty ratio | |

| Control-to-current transfer function | |

| Control-to-voltage transfer function | |

| Current-to-voltage transfer function | |

| Control-to-unbalancing function | |

| Voltage controller | |

| Current controller | |

| Cutoff bandwidth | |

| PM | Phase margin |

References

- Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics, 2nd ed.; Kluwer: Norwell, MA, USA, 2001. [Google Scholar]

- Barazarte, R.Y.; González, G. Design of a Two-Level Boost Converter. In Proceedings of the Eleventh LACCEI Latin American and Caribbean Conference for Engineering and Technology, Boca Raton, FL, USA, 16 August 2013; pp. 1–8. [Google Scholar]

- Kim, S.-H.; Cha, H.-N.; Kim, H.-G.; Choi, B.-C. Clamp-mode Three-level High Voltage Gain Boost Converter using Coupled Inductor. Korean Inst. Power Electron. 2012, 17, 500–506. [Google Scholar] [CrossRef] [Green Version]

- Zhao, Q.; Lee, F.C. High-Efficiency, High Step-Up DC-DC Converters. IEEE Trans. Power Electron. 2003, 18, 65–73. [Google Scholar] [CrossRef] [Green Version]

- Li, W.; He, X. Review of Nonisolated High-Step-Up DC/DC Converters in Photovoltaic Grid-Connected Applications. IEEE Trans. Ind. Electron. 2011, 58, 1239–1250. [Google Scholar] [CrossRef]

- Palma, L.; Todorovic, M.H.; Enjeti, P.N. A high gain transformer-less DC-DC converter for fuel-cell application. In Proceedings of the IEEE 36th Power Electronics Specialists Conference, Dresden, Germany, 16 June 2005; pp. 2514–2520. [Google Scholar]

- Ismail, E.H.; Al-Saffar, M.A.; Sabzali, A.J. High conversion ratio dc–dc converters with reduced switch stress. IEEE Trans. Circuits Syst. I Regul. Pap. 2008, 55, 2139–2151. [Google Scholar] [CrossRef]

- Wai, R.-J.; Duan, R.-Y. High step-up converter with coupled-inductor. IEEE Trans. Power Electron. 2005, 20, 1025–1035. [Google Scholar] [CrossRef]

- Shen, M.; Peng, F.Z.; Tolbert, L.M. Multilevel dc-dc power conversion with multiple dc sources. IEEE Trans. Power Electron. 2008, 23, 420–426. [Google Scholar] [CrossRef]

- Kim, C.M.; Kim, J.S. Comparative Analysis of Efficiency and Power Density of Single-Phase and 3-Level Boost Converters for PV System. Korean Inst. Power Electron. 2020, 25, 127–132. [Google Scholar]

- Zhang, M.T.; Jiang, Y.; Lee, F.C.; Jovanovic, M.M. Single-phase three-level boost power factor correction converter. In Proceedings of the 10th Annual Applied Power Electronics Conference and Exposition, Dallas, TX, USA, 5–9 March 1995; pp. 434–439. [Google Scholar]

- Chen, H.C.; Lin, W.J. MPPT and Voltage Balancing Control with Sensing Only Inductor Current for Photovoltaic-Fed, Three-Level, Boost-Type Converters. IEEE Trans. Power Electron. 2014, 29, 29–35. [Google Scholar] [CrossRef]

- Yaramasu, V.; Wu, B. Three-level boost converter based medium voltage megawatt PMSG wind energy conversion systems. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Phoenix, AZ, USA, 17–22 September 2011; pp. 561–567. [Google Scholar]

- Lin, B.-R.; Lu, H.-H. A novel PWM scheme for single-phase three level power-factor-correction circuit. IEEE Trans. Ind. Electron. 2000, 47, 245–252. [Google Scholar]

- Wu, H.; He, X. Single phase three-level power factor correction circuit with passive lossless snubber. IEEE Trans. Power Electron. 2002, 17, 946–953. [Google Scholar]

- Lee, M.; Kim, J.-W.; Lai, J.-S. Small-signal Modeling of Three-Level Boost Rectifier and System Design for Medium-Voltage Solid-State Transformer. In Proceedings of the 2019 10th International Conference on Power Electronics and ECCE Asia, Busan, Republic of Korea, 27–30 May 2019. [Google Scholar]

- Kwon, J.M.; Kwon, B.H.; Nam, K.H. Three-Phase Photovoltaic System with Three-Level Boosting MPPT Control. IEEE Trans. Power Electron. 2008, 23, 2319–2327. [Google Scholar] [CrossRef] [Green Version]

- Lee, M.; Kim, J.-W.; Lai, J.-S. Derivation of CCM/DCM boundary and Ideal Duty-Ratio Feedforward for Three-level boost Rectifier. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 1173–1179. [Google Scholar]

- Chen, H.-C.; Liao, J.-Y. Design and Implementation of Sensorless Capacitor Voltage Balancing Control for Three-Level Boosting PFC. IEEE Trans. Power Electron. 2014, 29, 3808–3817. [Google Scholar] [CrossRef] [Green Version]

- Kim, J.; Yang, O. Three-Level Boost Converter Design for High Efficiency Photovoltaic Power Conditioning System. Adv. Sci. Technol. Lett. 2014, 51, 68–72. [Google Scholar]

- Zhao, E.; Han, Y.; Lin, X.; Liu, E.; Yang, P.; Zalhaf, A.S. Harmonic characteristics and control strategies of grid-connected photovoltaic inverters under weak grid conditions. Int. J. Electr. Power Energy Syst. 2022, 142 Pt B, 142. [Google Scholar] [CrossRef]

- Zhao, E.; Han, Y.; Lin, X.; Yang, P.; Blaabjerg, F.; Zalhaf, A.S. Impedance characteristics investigation and oscillation stability analysis for two-stage PV inverter under weak grid condition. Electr. Power Syst. Res. 2022, 209, 108053. [Google Scholar] [CrossRef]

| Symbol | Quantity | Value |

|---|---|---|

| Voltage compensator | ||

| Cutoff bandwidth | 10 [rad/s] | |

| PM | phase margin | 90 [deg] |

| Current compensator | ||

| Cutoff bandwidth | 3000 [rad/s] | |

| PM | phase margin | 60 [deg] |

| Parameter | Quantity | Unit |

|---|---|---|

| Output voltage | 217 [V] | |

| Input voltage | 100 [V] | |

| Inductance ESR | 0.3 [] | |

| Inductance | 1.0 [mH] | |

| Capacitance1 | 1200 [F] | |

| Capacitance2 | 1200 [F] | |

| Switching frequency | 20 [kHz] |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, K.-M.; Kim, I.-S. Unified Modeling and Double-Loop Controller Design of Three-Level Boost Converter. Sustainability 2023, 15, 1597. https://doi.org/10.3390/su15021597

Lee K-M, Kim I-S. Unified Modeling and Double-Loop Controller Design of Three-Level Boost Converter. Sustainability. 2023; 15(2):1597. https://doi.org/10.3390/su15021597

Chicago/Turabian StyleLee, Kyu-Min, and IL-Song Kim. 2023. "Unified Modeling and Double-Loop Controller Design of Three-Level Boost Converter" Sustainability 15, no. 2: 1597. https://doi.org/10.3390/su15021597