Design Optimization of Double-Gate Isosceles Trapezoid Tunnel Field-Effect Transistor (DGIT-TFET)

Abstract

:1. Introduction

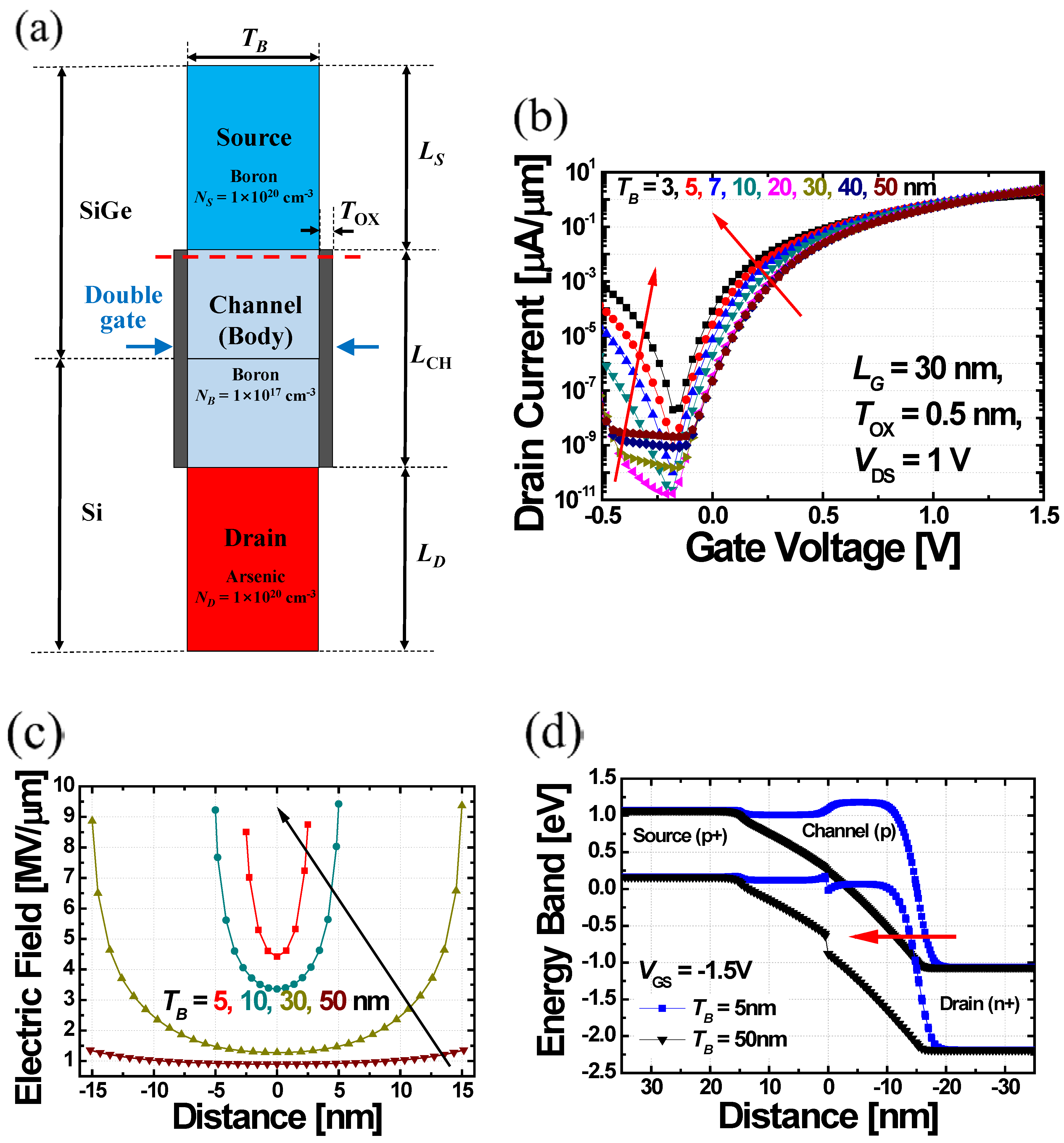

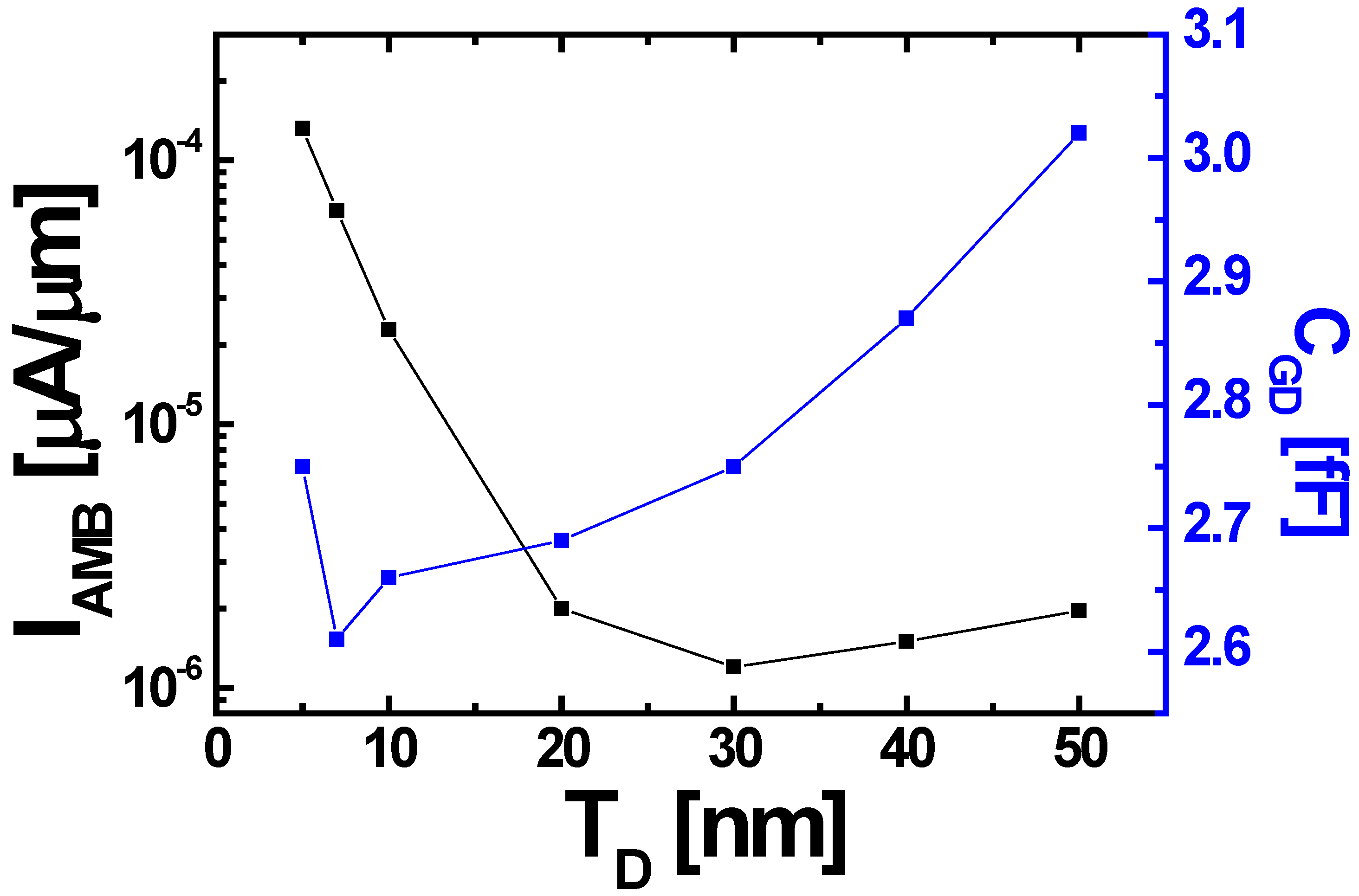

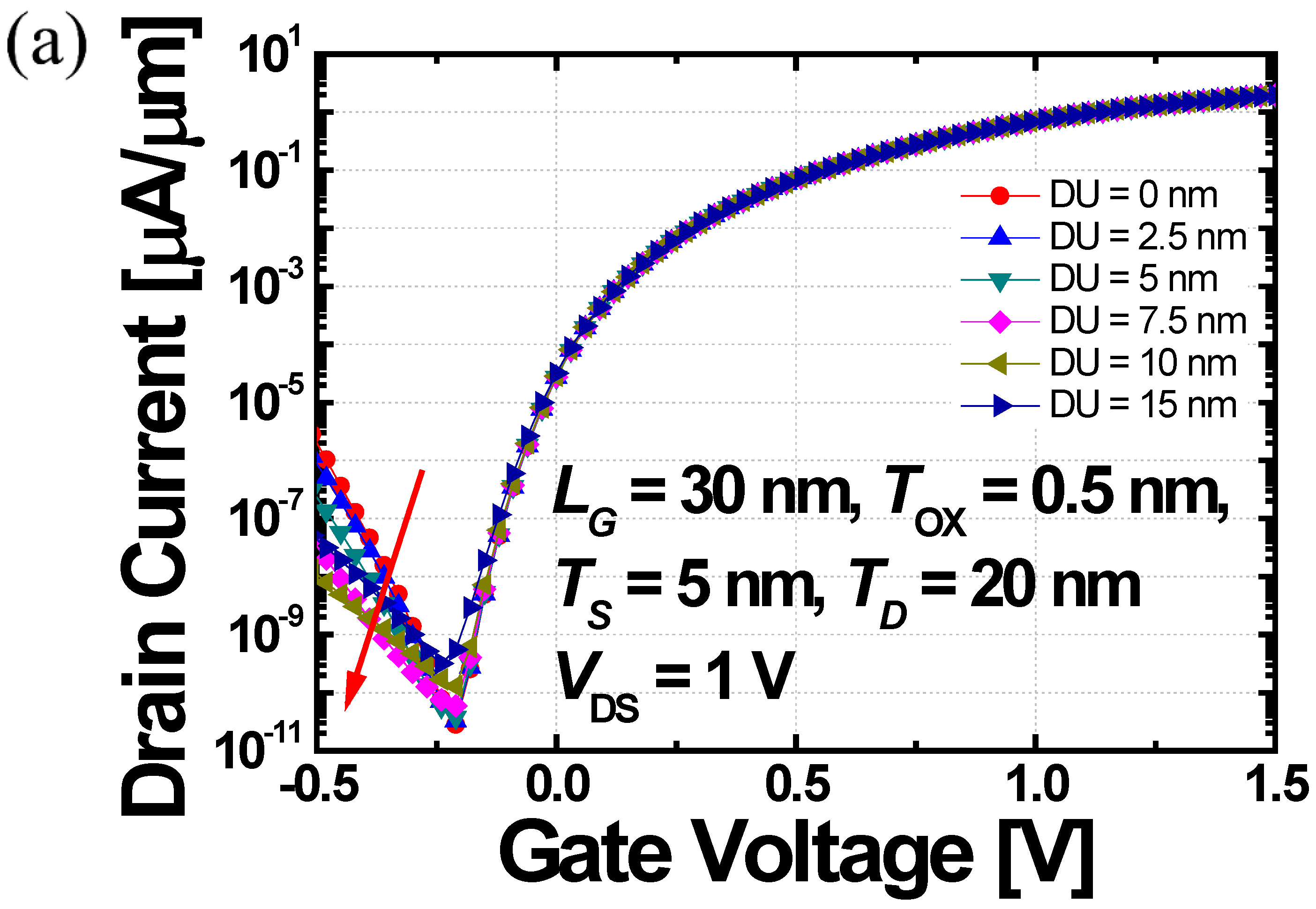

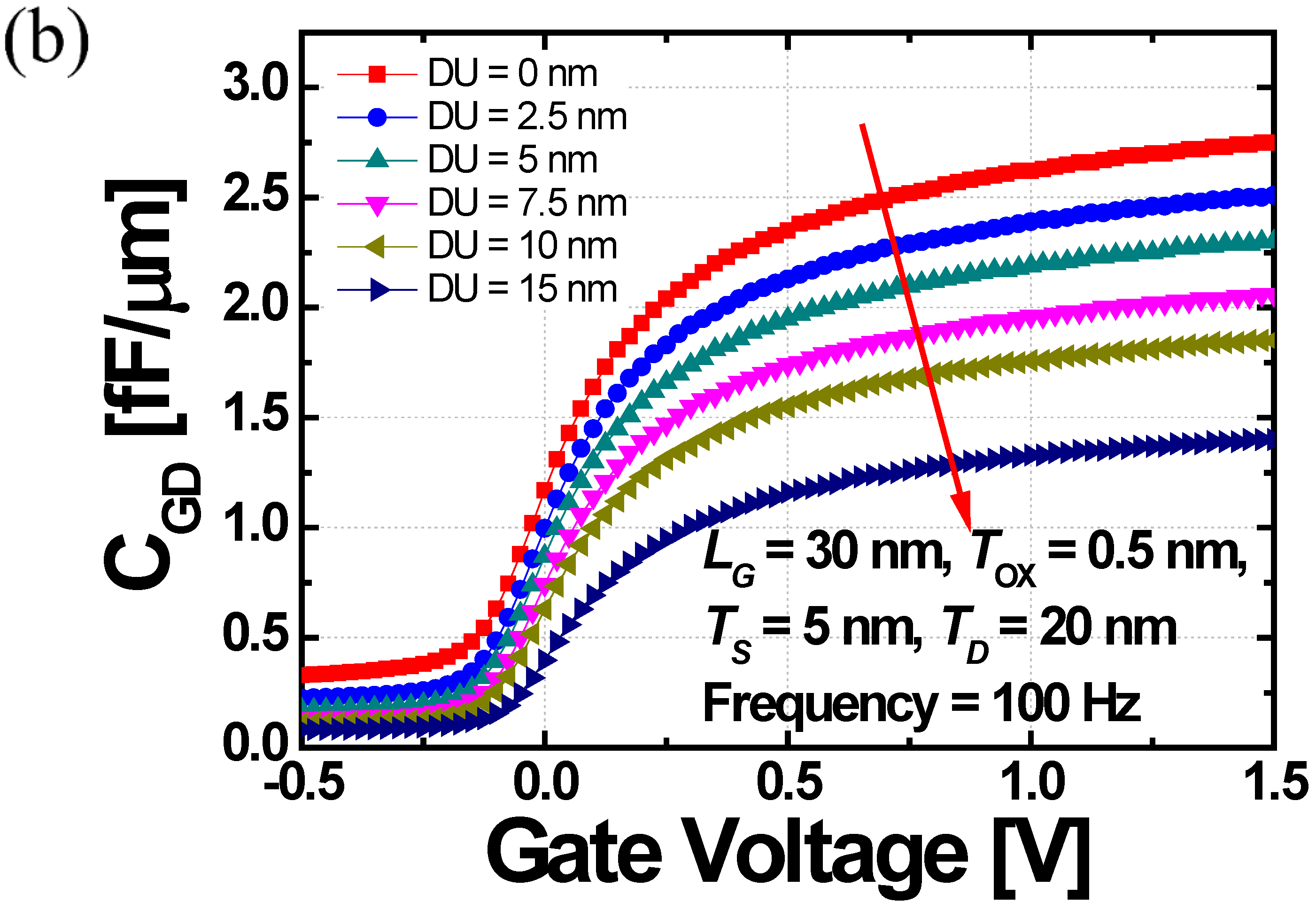

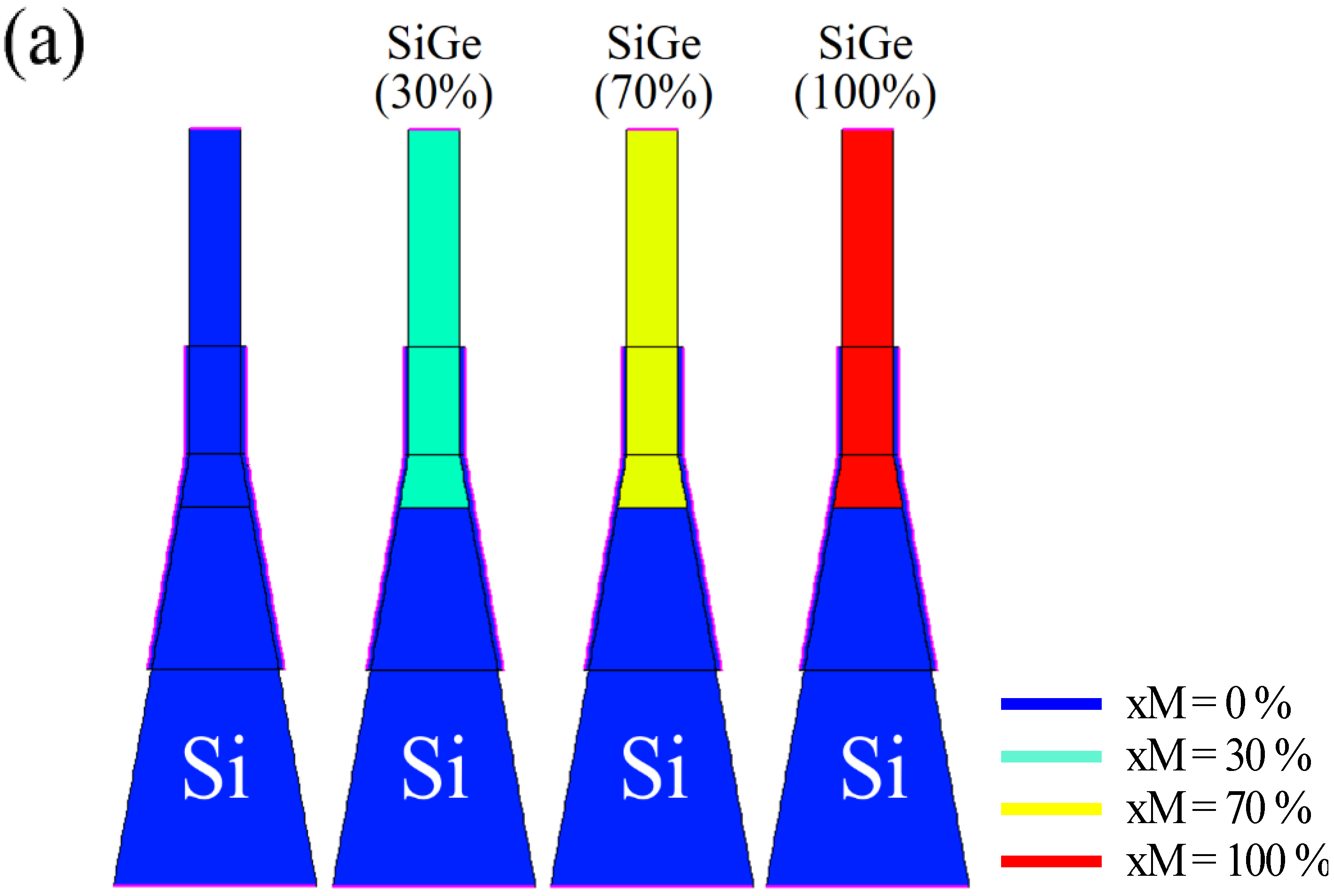

2. Double-Gate Isosceles Trapezoid TFET (DGIT-TFET)

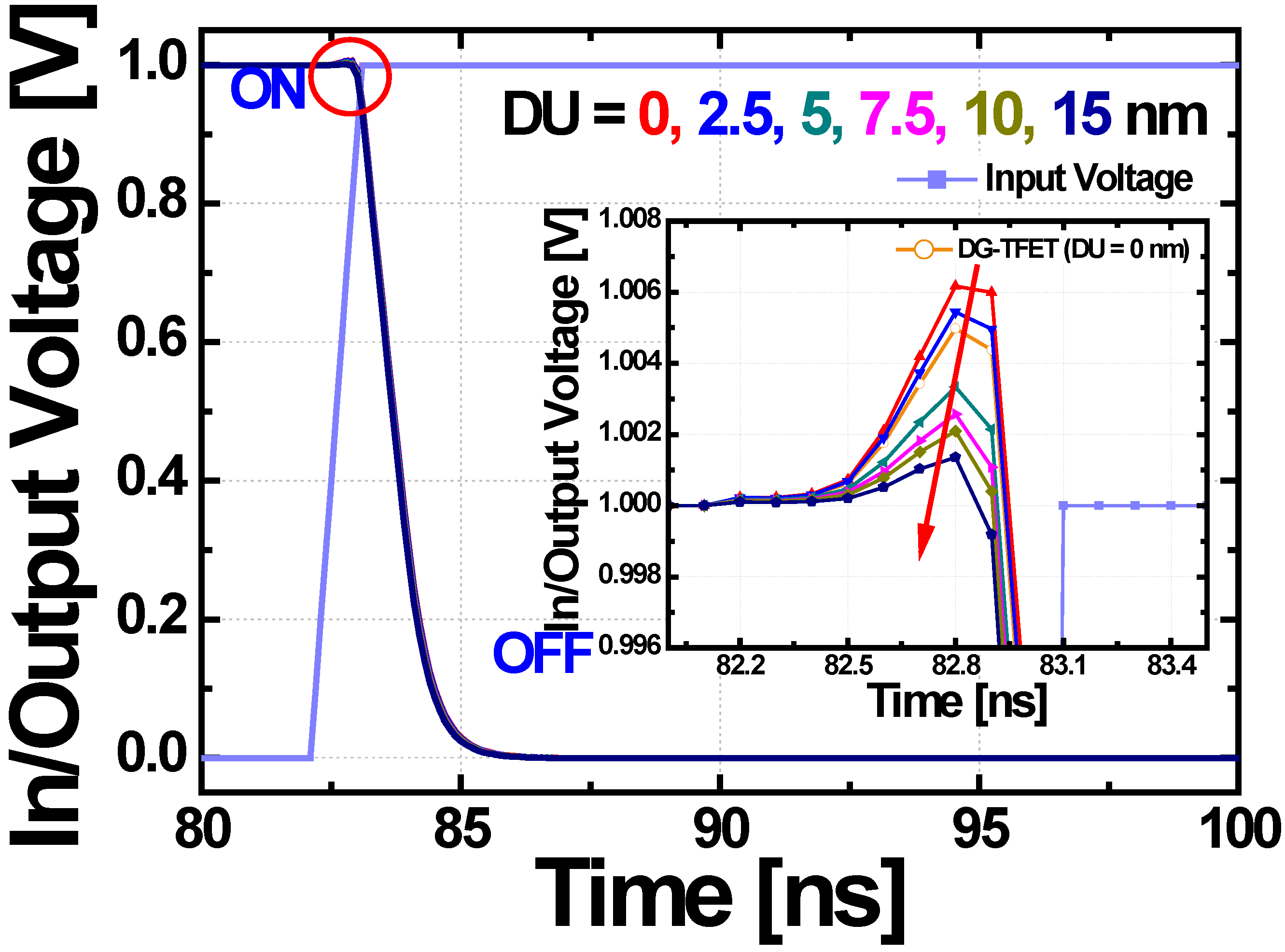

3. Design Optimization of DGIT-TFET

4. Summary

Author Contributions

Funding

Conflicts of Interest

References

- International Roadmap for Devices and Systems 2016. Available online: https://irds.ieee.org/reports (accessed on 13 September 2018).

- Haron, N.Z.; Hamdioui, S. Why is CMOS scaling coming to an END? In Proceedings of the IEEE 3rd International Design and Test Workshop, Monastir, Tunisia, 20–22 December 2008. [Google Scholar]

- BintiMdSallah, S.S.; Mohamed, H.; Mamun, M.; Amin, M.S. CMOS downsizing: Present, past and future. J. Appl. Sci. Res. 2012, 8, 4138–4146. [Google Scholar]

- Adrian, M. Ionescu and Heike Riel. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 2011, 479, 329–337. [Google Scholar] [CrossRef]

- Seabaugh, A.C.; Zhang, Q. Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 2010, 98, 2095–2110. [Google Scholar] [CrossRef]

- Boucart, K.; Ionescu, A.M. Double-gate tunnel FET with high-k gate dielectric. IEEE Trans. Electron Devices 2007, 54, 1725–1733. [Google Scholar] [CrossRef]

- Lu, H.; Seabaugh, A. Tunnel field-effect transistors: State-of-the-art. IEEE J. Electron Devices Soc. 2014, 2, 44–49. [Google Scholar] [CrossRef]

- Avci, U.E.; Morris, D.H.; Hasan, S.; Kotlyar, R.; Kim, R.; Rios, R.; Nikonov, D.E.; Young, I.A. Energy efficiency comparison of nanowire heterojunction TFET and Si MOSFET at Lg = 13 nm, including P-TFET and variation considerations. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 9–11 December 2013. [Google Scholar]

- Robbins, M.C.; Koester, S.J. Crystal-oriented black phosphorus TFETs with strong band-to-band-tunneling anisotropy and subthreshold slope nearing the thermionic limit. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017. [Google Scholar]

- Kwon, H.T.; Kim, S.W.; Lee, W.J.; Wee, D.H.; Kim, Y. A recessed-channel tunnel field-effect transistor (RTFET) with the asymmetric source and drain. JSTS 2016, 16, 635–640. [Google Scholar] [CrossRef]

- Kim, S.W.; Kim, J.H.; Liu, T.-J.K.; Choi, W.Y.; Park, By. Demonstration of L-shaped Tunnel Field-Effect Transistors. IEEE Trans. Electron Devices 2015, 63, 1774–1778. [Google Scholar] [CrossRef]

- Shih, P.-C.; Huang, H.-C.; Wang, C.-A.; Li, J.-Y. A novel vertical tunnel FET of band-to-band tunneling aligned with gate electric field with averaged SS of 28 mV/decade. In Proceedings of the Silicon Nanoelectronics Workshop (SNW), Kyoto, Japan, 4–5 June 2017; p. 45. [Google Scholar]

- Cristoloveanu, S.; Wan, J.; Zaslavsky, A. A review of sharp-switching devices for ultra-low power applications. IEEE J. Electron Devices Soc. 2016, 4, 215–226. [Google Scholar] [CrossRef]

- Choi, W.Y.; Park, B.G.; Lee, J.D. Tunneling Field-Effect Transistor (TFETs) With Subthreshold Swing (SS) Less Than 60 mV/dec. IEEE Electron Device Lett. 2007, 28, 743–745. [Google Scholar] [CrossRef]

- Wu, Y.-T.; Chiang, M.-H.; Chen, J.F.; Ding, F.; Connelly, D.; Liu, T.-J.K. High-Density SRAM Voltage Scaling Enabled by Inserted-Oxide FinFET Technology. In Proceedings of the IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, USA, 16–19 October 2017. [Google Scholar]

- Krishnamohan, T.; Kim, D.; Raghunathan, S.; Saraswat, K. Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and <60 mV/dec subthreshold slope. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008. [Google Scholar]

- Kuhn, K.J.; Murthy, A.; Kotlyar, R.; Kuhn, M. Past, Present and Future: SiGe and CMOS Transistor Scaling. ECS Trans. 2010, 33, 3–17. [Google Scholar]

- Kao, K.-H.; Verhulst, A.S.; Vandenberghe, W.G.; Soree, B.; Groeseneken, G.; de Meyer, K. Direct and Indirect Band-to-Band Tunneling in Germanium-Based TFETs. IEEE Trans. Electron Devices 2012, 59, 292–301. [Google Scholar] [CrossRef]

- Schenk, A.; Sant, S.; Moselund, K.; Riel, H. The impact of hetero-junction and oxide-interface traps on the performance of InAs/Si and InAs/GaAsSb nanowire tunnel FETs. In Proceedings of the International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Kamakura, Japan, 7–9 September 2017. [Google Scholar]

- Kunii, Y.; Inokuchi, E.Y. Vertical SiGe epitaxial growth system. Hitachi Rev. 2002, 51, 104–108. [Google Scholar]

- Narang, R.; Saxena, M.; Gupta, R.S.; Gupta, M. Assessment of ambipolar behavior of a tunnel FET and influence of structural modifications. J. Semicond. Technol. Sci. JSTS 2012, 12, 482–491. [Google Scholar] [CrossRef]

- Abdi, D.B.; Kumar, M.J. Controlling Ambipolar Current in Tunneling FETs Using Overlapping Gate-on-Drain. IEEE J. Electron Devices Soc. 2014, 2, 187–190. [Google Scholar] [CrossRef]

- Saurabh, S.; Kumar, M.J. Fundamentals of Tunnel Field-Effect Transistors; CRC Press: Boca Raton, FL, USA, 2016; p. 162. [Google Scholar]

- Kwon, D.W.; Kim, J.H.; Park, B.-G. Effects of drain doping concentration on switching characteristics of tunnel field-effect transistor inverters. Jpn. J. Appl. Phys. 2016, 55, 114201. [Google Scholar] [CrossRef]

- SentaurusTM Device User Guide, ver. K-2015.06, Synopsys Inc. Available online: http://www. sentaurus.dsod.pl/manuals/data/sdevice_ug.pdf (accessed on 13 September 2018).

- Pala, M.G.; Brocard, S. Exploiting Hetero-Junctions to Improve the Performance of III–V Nanowire Tunnel-FETs. IEEE Electron Devices Soc. 2015, 3, 115–121. [Google Scholar] [CrossRef]

- Kim, S.W.; Choi, W.Y. Hump Effects of Germanium/Silicon Heterojunction Tunnel Field-Effect Transistors. IEEE Trans. Electron Devices 2016, 63, 2583–2588. [Google Scholar] [CrossRef]

- Choi, W.Y.; Song, J.Y.; Lee, J.D.; Park, Y.J.; Park, B.-G. A novel biasing scheme for I-MOS (impact-ionization MOS) devices. IEEE Trans. Nanotechnol. 2005, 4, 322–325. [Google Scholar] [CrossRef]

- Sicard, E. Introducing 7-nm FinFET technology in Microwind. Arch. Ouvert. HAL 2017, 1–22. Available online: https://hal.archives-ouvertes.fr/hal-01558775/ (accessed on 20 January 2019).

- Yang, Y.; Tong, X.; Yang, L.-T.; Guo, P.-F.; Fan, L.; Yeo, Y.-C. Tunneling field-effect transistor: Capacitance components and modeling. IEEE Electron Device Lett. 2010, 31, 752–754. [Google Scholar] [CrossRef]

- Kwon, D.W.; Kim, J.H.; Park, E.; Lee, J.; Kim, S.; Park, B.-G. Switching Characteristics Analysis of Tunnel Field-Effect Transistor (TFET) Inverters. J. Nanosci. Nanotechnol. 2017, 17, 7134–7139. [Google Scholar] [CrossRef]

- Vandenberghe, W.G.; Verhulst, A.S. Tunnel Field-Effect Transistor with Gated Tunnel Barrier. U.S. Patent 8,120,115B2, 21 February 2012. [Google Scholar]

- Verhulst, A.S.; Vandenberghe, W.G.; Maex, K.; Groeseneken, G. Tunnel field-effect transistor without gate-drain overlap. Appl. Phys. Lett. 2007, 91, 053102. [Google Scholar] [CrossRef]

| Abbreviations | Definitions | Values |

|---|---|---|

| NS | source doping concentration | Boron, 1 × 1020 cm−3 |

| NB | channel doping concentration | Boron, 1 × 1017 cm−3 |

| ND | drain doping concentration | Arsenic, 1 × 1020 cm−3 |

| LCH | channel length | 30 nm |

| LS = LD | charge neutral region length | 20 nm |

| TOX | equivalent gate oxide thickness | 0.5 nm |

| TS | source region thickness | 5 nm |

| TD | drain region thickness | 20 nm |

| VDS | drain voltage | 1 V |

| gate work function | 4.0 eV |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gu, H.Y.; Kim, S. Design Optimization of Double-Gate Isosceles Trapezoid Tunnel Field-Effect Transistor (DGIT-TFET). Micromachines 2019, 10, 229. https://doi.org/10.3390/mi10040229

Gu HY, Kim S. Design Optimization of Double-Gate Isosceles Trapezoid Tunnel Field-Effect Transistor (DGIT-TFET). Micromachines. 2019; 10(4):229. https://doi.org/10.3390/mi10040229

Chicago/Turabian StyleGu, Hwa Young, and Sangwan Kim. 2019. "Design Optimization of Double-Gate Isosceles Trapezoid Tunnel Field-Effect Transistor (DGIT-TFET)" Micromachines 10, no. 4: 229. https://doi.org/10.3390/mi10040229

APA StyleGu, H. Y., & Kim, S. (2019). Design Optimization of Double-Gate Isosceles Trapezoid Tunnel Field-Effect Transistor (DGIT-TFET). Micromachines, 10(4), 229. https://doi.org/10.3390/mi10040229