Physical and Electrical Analysis of Poly-Si Channel Effect on SONOS Flash Memory

Abstract

:1. Introduction

2. Experiments

3. Results and Discussion

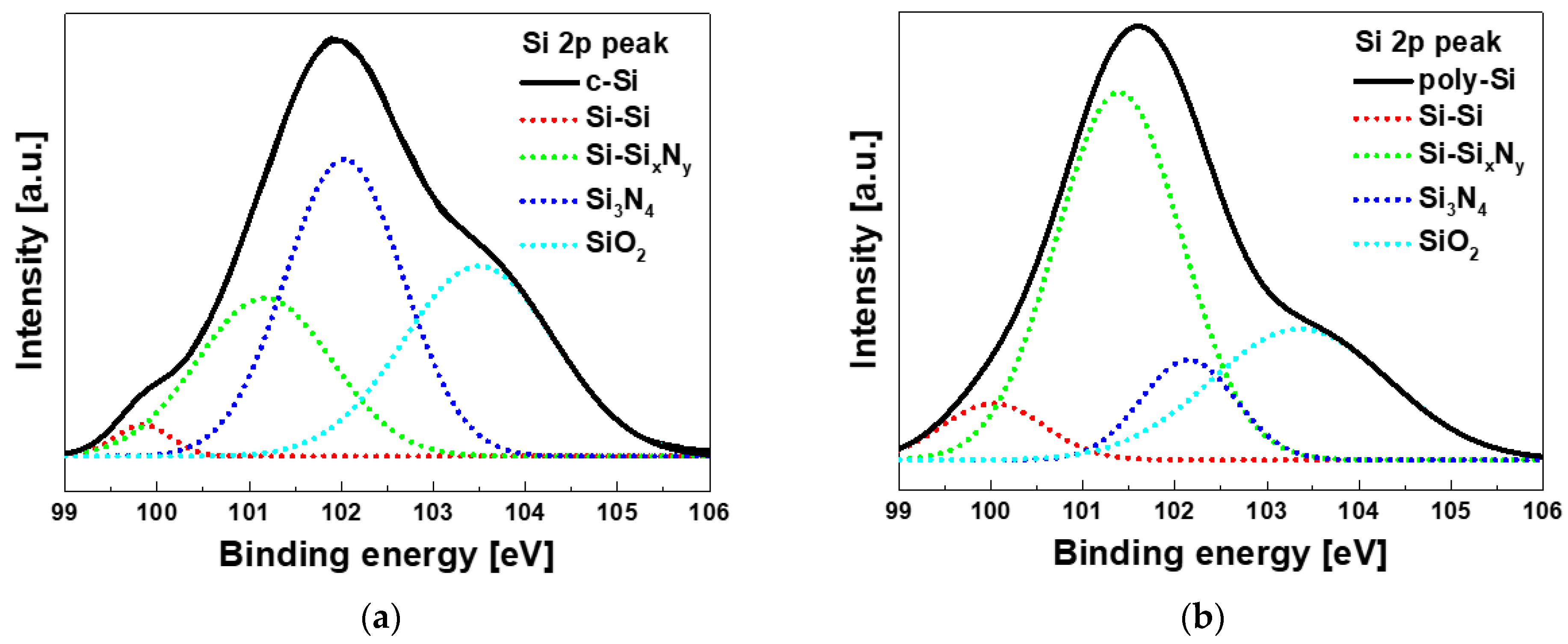

3.1. Physical Characteristic Analysis

XPS Analysis

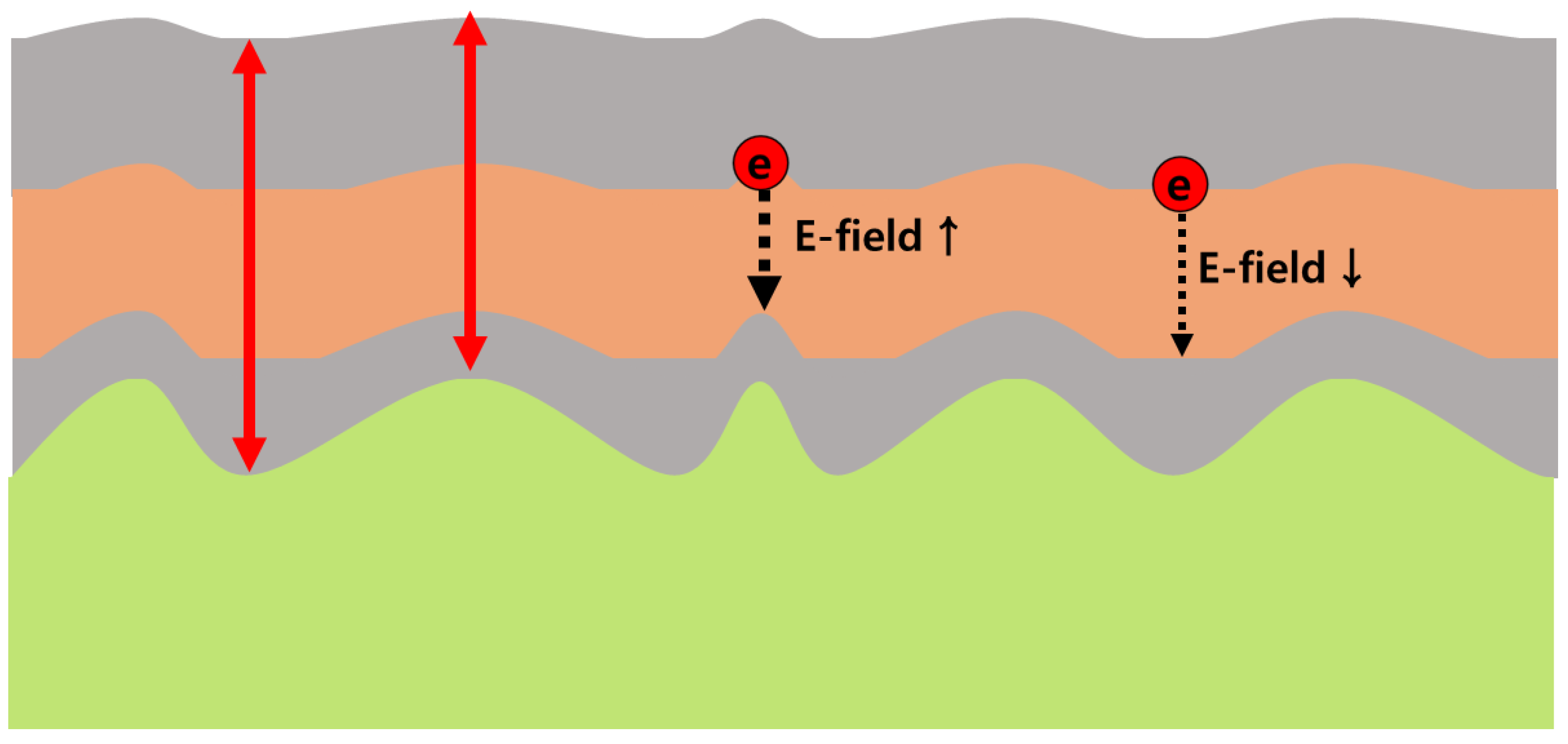

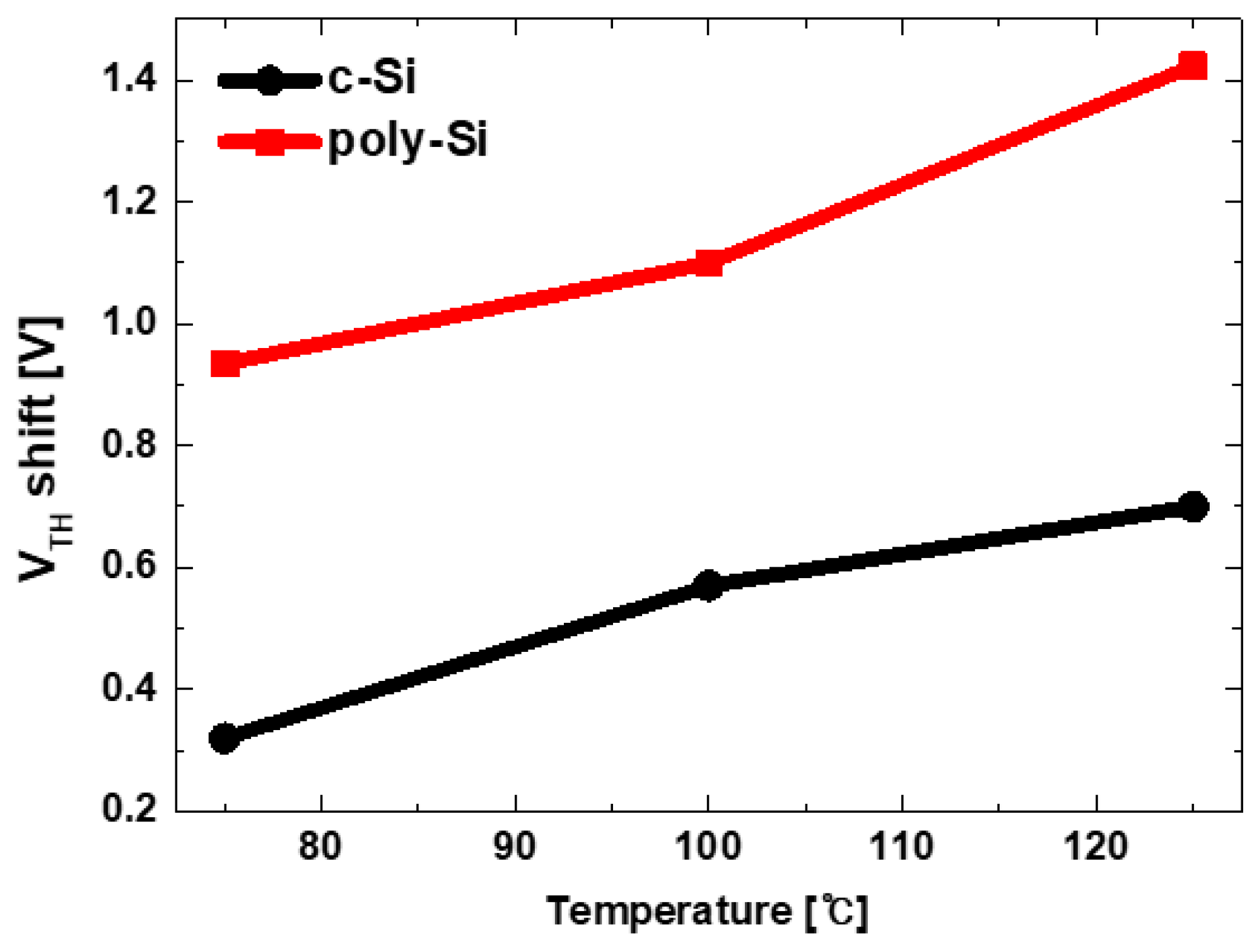

3.2. Electrical Characteristic Analysis

3.2.1. Data Retention Measurement

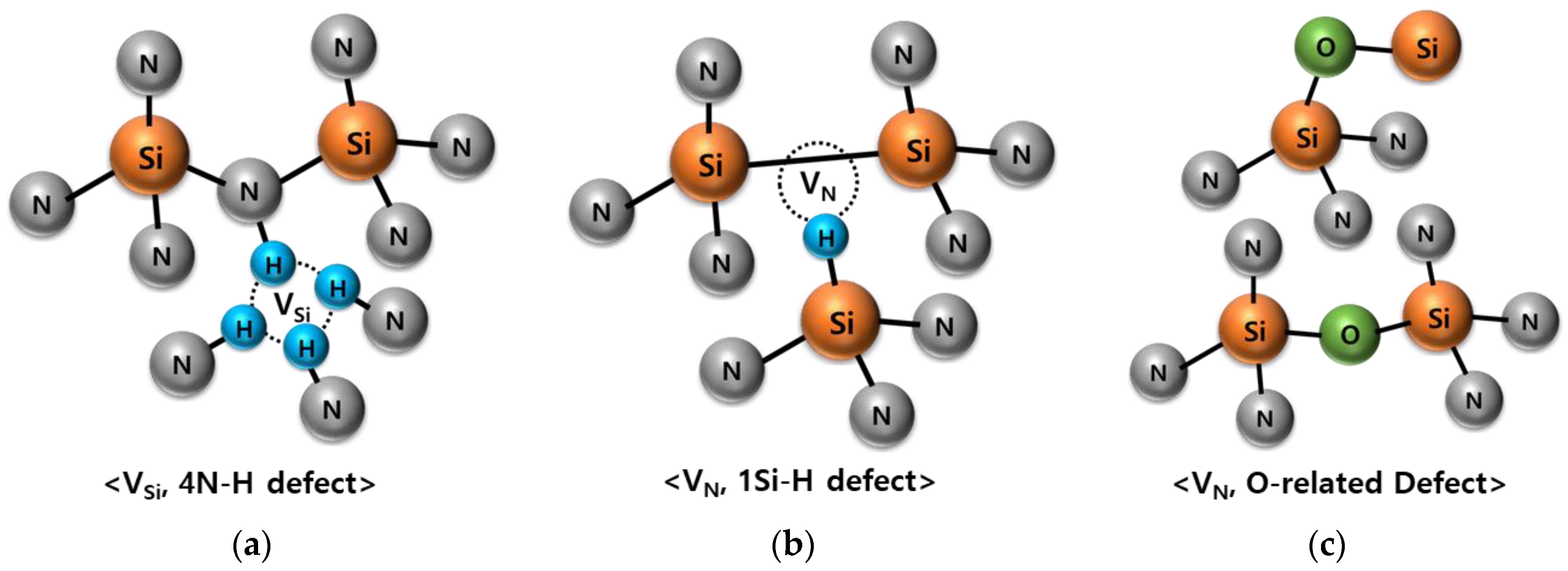

3.2.2. High Pressure D2 Annealing Effect

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Yang, S.D.; Oh, J.S.; Yun, H.J.; Jeong, K.S.; Kim, Y.M.; Lee, S.Y.; Lee, H.-D.; Lee, G.-W. The short channel effect immunity of silicon nanowire SONOS flash memory using TCAD simulation. Trans. Electr. Electron. Mater. 2013, 14, 139–142. [Google Scholar] [CrossRef]

- Xie, Q.; Lee, C.J.; Xu, J.; Wann, C.; Sun, J.Y.C.; Taur, Y. Comprehensive analysis of short-channel effects in ultrathin SOI MOSFETs. IEEE Trans. Electron. Devices 2013, 60, 1814–1819. [Google Scholar] [CrossRef]

- Bohara, P.; Vishvakarma, S.K. NAND flash memory device with ground plane in buried oxide for reduced short channel effects and improved data retention. J. Comput. Electron. 2019, 18, 500–508. [Google Scholar] [CrossRef]

- Endoh, T.; Kinoshita, K.; Tanigami, T.; Wada, Y.; Sato, K.; Yamada, K.; Yokoyama, T.; Takeuchi, N.; Tanaka, K.; Awaya, N.; et al. Novel ultrahigh-density flash memory with a stacked-surrounding gate transistor (S-SGT) structured cell. IEEE Trans. Electron. Devices 2003, 50, 945–951. [Google Scholar] [CrossRef]

- Kim, H.; Ahn, S.J.; Shin, Y.G.; Lee, K.; Jung, E. Evolution of NAND flash memory: From 2D to 3D as a storage market leader. In Proceedings of the 2017 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 14–17 May 2017; IEEE: Monterey, CA, USA, 2017; pp. 1–4. [Google Scholar]

- Seager, C.H. Grain boundaries in polycrystalline silicon. Ann. Rev. Mater. Sci. 1985, 15, 271–302. [Google Scholar] [CrossRef]

- Yamashita, Y.; Asano, A.; Nishioka, Y.; Kobayashi, H. Dependence of interface states in the Si band gap on oxide atomic density and interfacial roughness. Phys. Rev. B 1999, 59, 15872. [Google Scholar] [CrossRef]

- Hong, S.B.; Park, J.H.; Lee, T.H.; Lim, J.H.; Shin, C.; Park, Y.W.; Kim, T.G. Variation of poly-Si grain structures under thermal annealing and its effect on the performance of TiN/Al2O3/Si3N4/SiO2/poly-Si capacitors. Appl. Surf. Sci. 2019, 477, 104–110. [Google Scholar] [CrossRef]

- Aozasa, H.; Fujiwara, I.; Nomoto, K.; Komatsu, H.; Koyama, K.; Kobayashi, T.; Oda, T. Effects of nitridation on the electrical properties of MONOS nonvolatile memories. J. Electrochem. Soc. 2007, 154, H798. [Google Scholar] [CrossRef]

- Kizilyalli, I.C.; Lyding, J.W.; Hess, K. Deuterium post-metal annealing of MOSFET’s for improved hot carrier reliability. IEEE Electron. Device Lett. 1997, 18, 81–83. [Google Scholar] [CrossRef]

- Cheng, K.; Hess, K.; Lyding, J.W. A new technique to quantify deuterium passivation of interface traps in MOS devices. IEEE Electron. Device Lett. 2001, 22, 203–205. [Google Scholar] [CrossRef]

- Yang, Y.L.; Purwar, A.; White, M.H. Reliability considerations in scaled SONOS nonvolatile memory devices. Solid State Electron. 1999, 43, 2025–2032. [Google Scholar] [CrossRef]

- Li, W.; Li, D.Y. On the correlation between surface roughness and work function in copper. J. Chem. Phys. 2005, 122, 064708. [Google Scholar] [CrossRef] [PubMed]

- Choi, Y.W.; Xie, K.; Kim, H.M.; Wie, C.R. Interface trap and interface depletion in lattice-mismatched GaInAs/GaAs heterostructures. J. Electron. Mater. 1991, 20, 545–551. [Google Scholar] [CrossRef]

- Huang, Z.C.; Wie, C.R.; Johnstone, D.K.; Stutz, C.E.; Evans, K.R. Effects of lattice mismatch and thermal annealing on deep traps and interface states in Ga0. 92In0. 08As (n+)/GaAs (p) heterojunctions. J. Appl. Phys. 1993, 73, 4362–4366. [Google Scholar] [CrossRef]

- Lee, J.D.; Choi, J.H.; Park, D.; Kim, K. Effects of interface trap generation and annihilation on the data retention characteristics of flash memory cells. IEEE Trans. Device Mater. Reliab. 2004, 4, 110–117. [Google Scholar] [CrossRef]

- Yang, S.D.; Jung, J.K.; Lim, J.G.; Park, S.G.; Lee, H.D.; Lee, G.W. Investigation of Intra-Nitride Charge Migration Suppression in SONOS Flash Memory. Micromachines 2019, 10, 356. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Park, Y.B.; Rhee, S.W. Bulk and interface properties of low-temperature silicon nitride films deposited by remote plasma enhanced chemical vapor deposition. J. Mater. Sci. Mater. Electron. 2001, 12, 515–522. [Google Scholar] [CrossRef]

- Huang, J.J.; Liu, C.J.; Lin, H.C.; Tsai, C.J.; Chen, Y.P.; Hu, G.R.; Lee, C.C. Influences of low temperature silicon nitride films on the electrical performances of hydrogenated amorphous silicon thin film transistors. J. Phys. D Appl. Phys. 2008, 41, 245502. [Google Scholar] [CrossRef]

- Wong, H.; Gritsenko, V.A. Defects in silicon oxynitride gate dielectric films. Microelectron. Reliab. 2002, 42, 597–605. [Google Scholar] [CrossRef]

- Lusky, E.; Shacham-Diamand, Y.; Shappir, A.; Bloom, I.; Eitan, B. Traps spectroscopy of the Si3Ni4 layer using localized charge-trapping nonvolatile memory device. Appl. Phys. Lett. 2004, 85, 669–671. [Google Scholar] [CrossRef]

- Perera, R.; Ikeda, A.; Hattori, R.; Kuroki, Y. Effects of post annealing on removal of defect states in silicon oxynitride films grown by oxidation of silicon substrates nitrided in inductively coupled nitrogen plasma. Thin Solid Film 2003, 423, 212–217. [Google Scholar] [CrossRef]

- Vianello, E.; Driussi, F.; Blaise, P.; Palestri, P.; Esseni, D.; Perniola, L.; Molas, G.; De Salvo, B.; Selmi, L. Explanation of the charge trapping properties of silicon nitride storage layers for NVMs—Part II: Atomistic and electrical modeling. IEEE Trans. Electron. Devices 2011, 58, 2490–2499. [Google Scholar] [CrossRef] [Green Version]

- Gritsenko, V.A.; Perevalov, T.V.; Orlov, O.M.; Krasnikov, G.Y. Nature of traps responsible for the memory effect in silicon nitride. Appl. Phys. Lett. 2016, 109, 062904. [Google Scholar] [CrossRef]

- Sonoda, K.I.; Tsukuda, E.; Tanizawa, M.; Yamaguchi, Y. Electron trap level of hydrogen incorporated nitrogen vacancies in silicon nitride. J. Appl. Phys. 2015, 117, 104501. [Google Scholar] [CrossRef]

- Yamaguchi, K.; Otake, A.; Kobayashi, K.; Shiraishi, K. Atomistic guiding principles for MONOS-type memories with high program/erase cycle endurance. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; IEEE: Baltimore, MD, USA, 2009; pp. 1–4. [Google Scholar]

- Noguchi, M.; Isogai, T.; Yamashita, H.; Sawa, K.; Fujitsuka, R.; Yamanaka, T.; Okada, S.; Aoyama, T.; Aiso, F.; Abe, J.; et al. Formation of High Reliability Hydrogen-free MONOS Cells Using Deuterated Ammonia. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; IEEE: San Francisco, CA, USA, 2019; pp. 30–32. [Google Scholar]

- Tanaka, M.; Saida, S.; Mitani, Y.; Mizushima, I.; Tsunashima, Y. Highly reliable MONOS Devices with optimized silicon nitride film having deuterium terminated charge traps. In Proceedings of the 2002 Digest. International Electron Devices Meeting, Washington, DC, USA, 2–5 December 2001; IEEE: San Francisco, CA, USA, 2003; pp. 237–240. [Google Scholar]

- Choi, S.; Baek, S.; Jang, M.; Jeon, S.; Kim, J.; Kim, C.; Hwang, H. Effects of High-Pressure Deuterium annealing on nonvolatile memory device with silicon nanocrystals embedded in silicon nitride. J. Electrochem. Soc. 2005, 152, G345. [Google Scholar] [CrossRef]

| LPCVD | Temperature (°C) | Pressure (mTorr) | Composition Ratio |

|---|---|---|---|

| SiO2 | 800 | - | Si(OC2H5)4 |

| Si3N4 | 720 | 200 | SiH2Cl2:NH3 = 20:120 |

| Condition | Peak to Valley (nm) | Mean Height (nm) | RMS Roughness (nm) |

|---|---|---|---|

| c-Si channel | 1.2 | 0 | 0.157 |

| Poly-Si channel | 15.715 | 0.494 | 2.422 |

| Only poly-Si | 12.627 | 0.158 | 2.660 |

| c-Si | Si-Si | SixNy | Si3N4 | SiO2 | poly-Si | Si-Si | SixNy | Si3N4 | SiO2 |

|---|---|---|---|---|---|---|---|---|---|

| Peak (eV) | 99.84 | 101.17 | 102.03 | 103.49 | Peak (eV) | 100.02 | 101.39 | 102.14 | 103.36 |

| Ratio (%) | 2 | 25 | 40 | 33 | Ratio (%) | 7 | 54 | 11 | 28 |

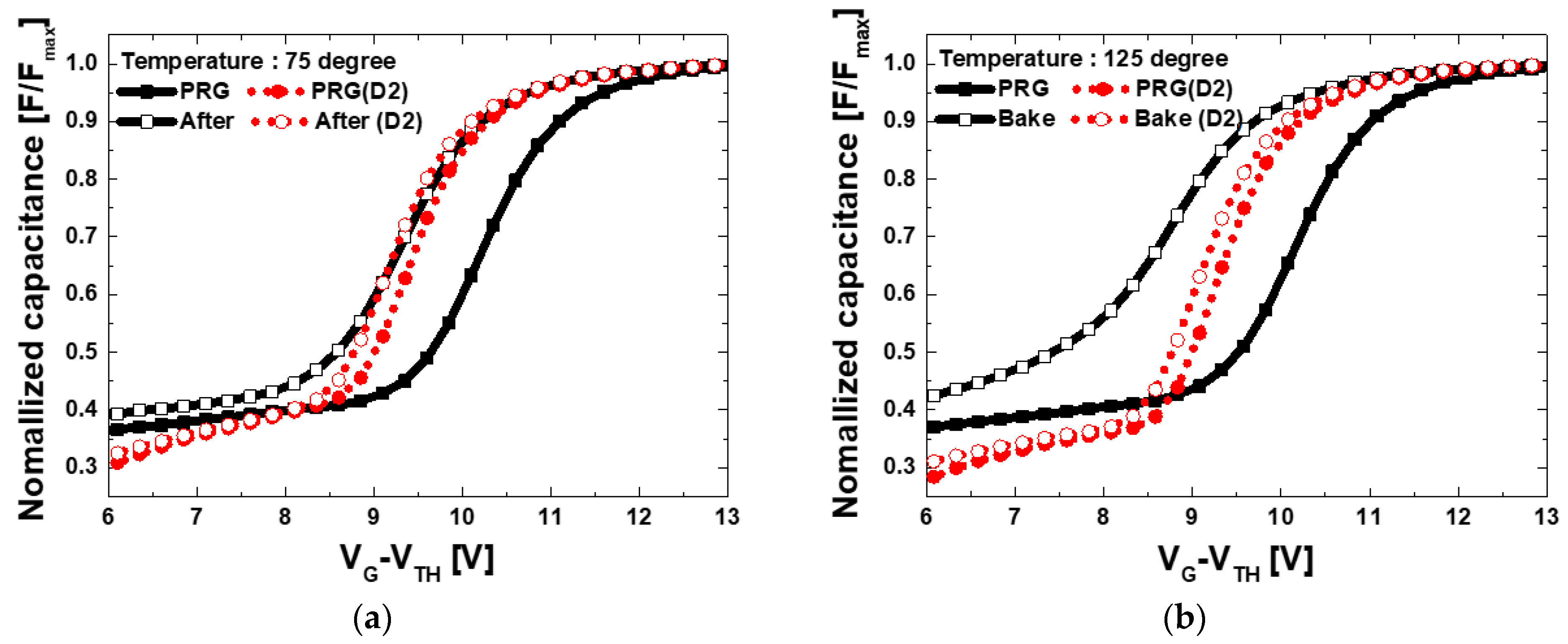

| Temperature (°C) | 75 | 125 | ||

|---|---|---|---|---|

| Condition | No Treatment | D2 Annealing | No Treatment | D2 Annealing |

| Program (V) | 10.75 | 9.86 | 10.58 | 9.74 |

| Bake (V) | 9.82 | 9.68 | 9.16 | 9.54 |

| ΔVTH (V) | 0.93 | 0.18 | 1.42 | 0.20 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jeong, J.-K.; Sung, J.-Y.; Ko, W.-S.; Nam, K.-R.; Lee, H.-D.; Lee, G.-W. Physical and Electrical Analysis of Poly-Si Channel Effect on SONOS Flash Memory. Micromachines 2021, 12, 1401. https://doi.org/10.3390/mi12111401

Jeong J-K, Sung J-Y, Ko W-S, Nam K-R, Lee H-D, Lee G-W. Physical and Electrical Analysis of Poly-Si Channel Effect on SONOS Flash Memory. Micromachines. 2021; 12(11):1401. https://doi.org/10.3390/mi12111401

Chicago/Turabian StyleJeong, Jun-Kyo, Jae-Young Sung, Woon-San Ko, Ki-Ryung Nam, Hi-Deok Lee, and Ga-Won Lee. 2021. "Physical and Electrical Analysis of Poly-Si Channel Effect on SONOS Flash Memory" Micromachines 12, no. 11: 1401. https://doi.org/10.3390/mi12111401

APA StyleJeong, J.-K., Sung, J.-Y., Ko, W.-S., Nam, K.-R., Lee, H.-D., & Lee, G.-W. (2021). Physical and Electrical Analysis of Poly-Si Channel Effect on SONOS Flash Memory. Micromachines, 12(11), 1401. https://doi.org/10.3390/mi12111401