Reliability Evaluation of Fan-Out Type 3D Packaging-On-Packaging

Abstract

1. Introduction

2. Materials and Methods

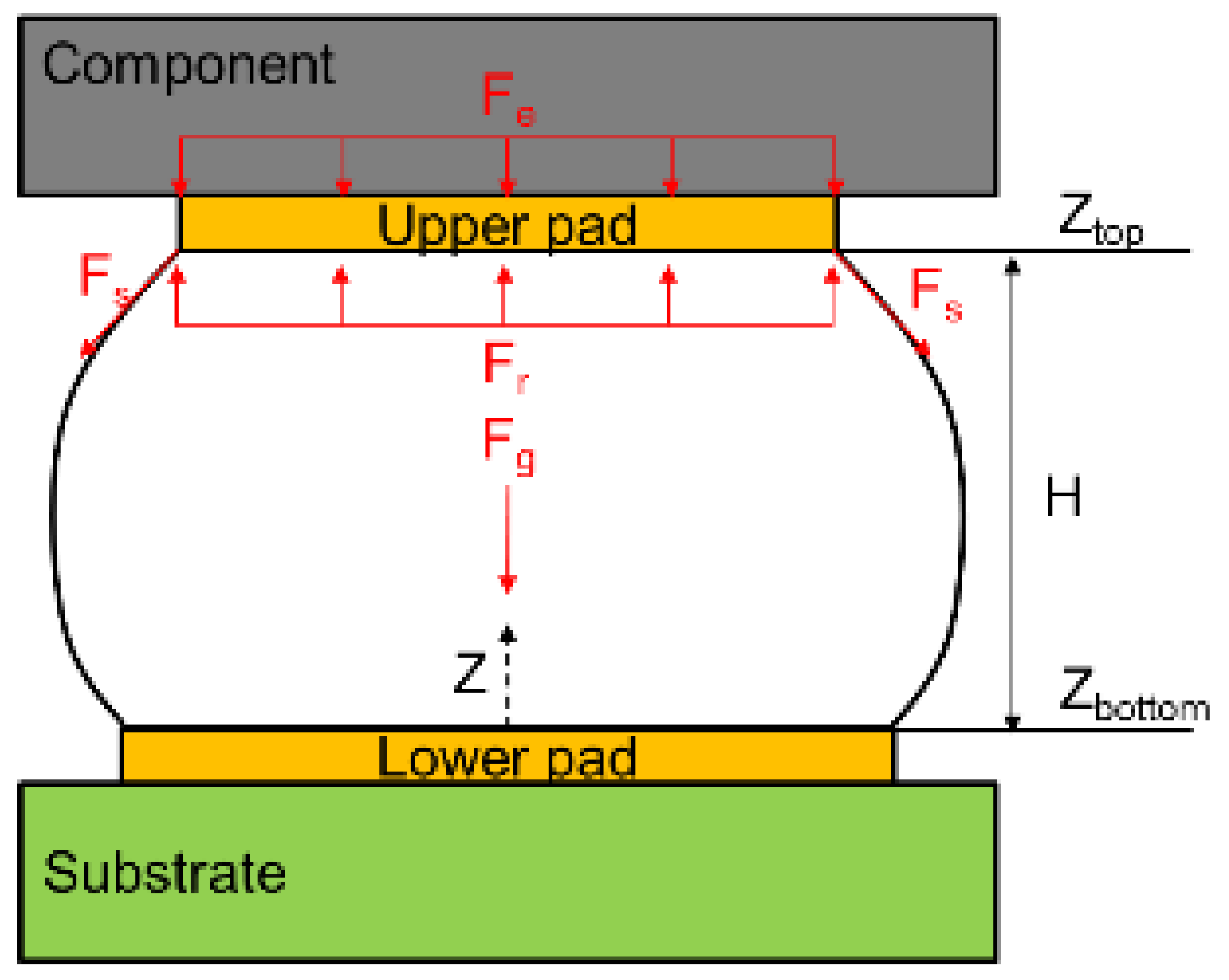

2.1. Shape Prediction of the Reflowed Solder Joint

2.2. Life Prediction of the Solder Joints

3. Test Vehicle Structure and Thermal Cycling

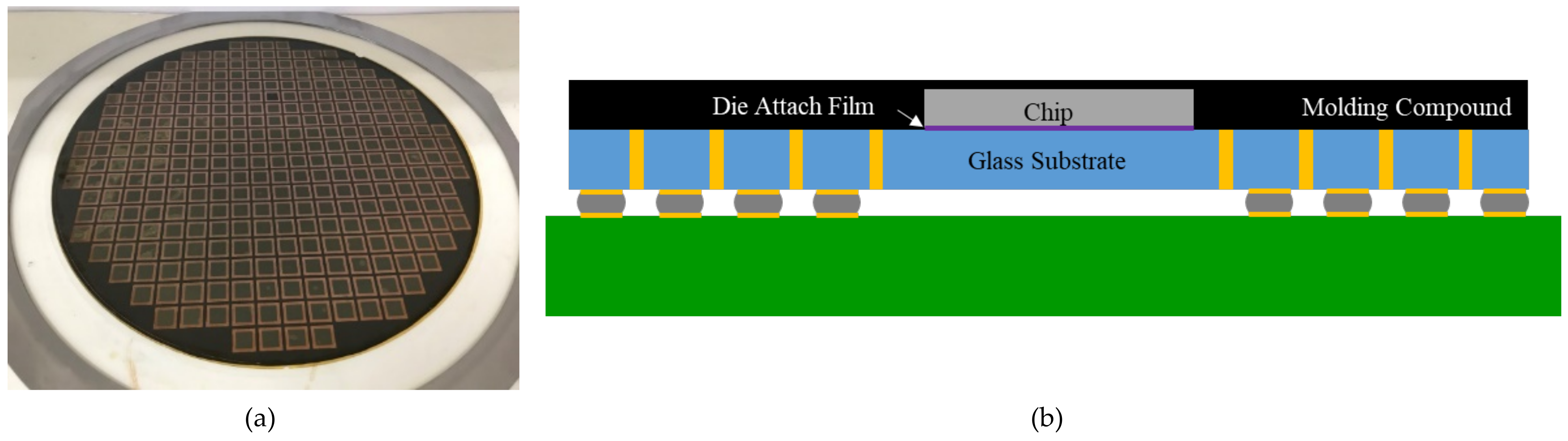

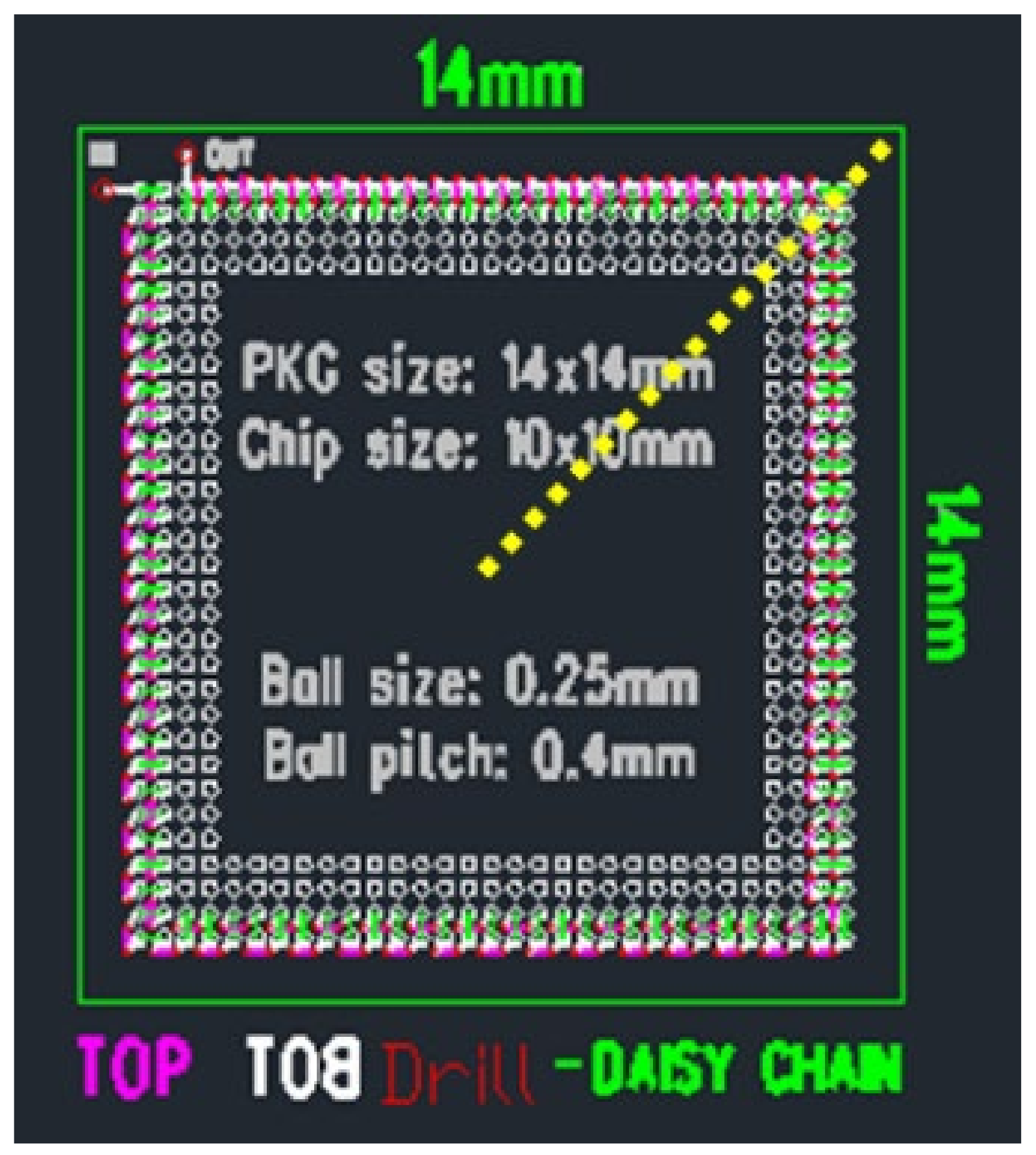

3.1. Structure of the Test Vehicle

3.2. Thermal Cycling and Weibull Distribution

4. Finite Element Analysis of FO-WLP

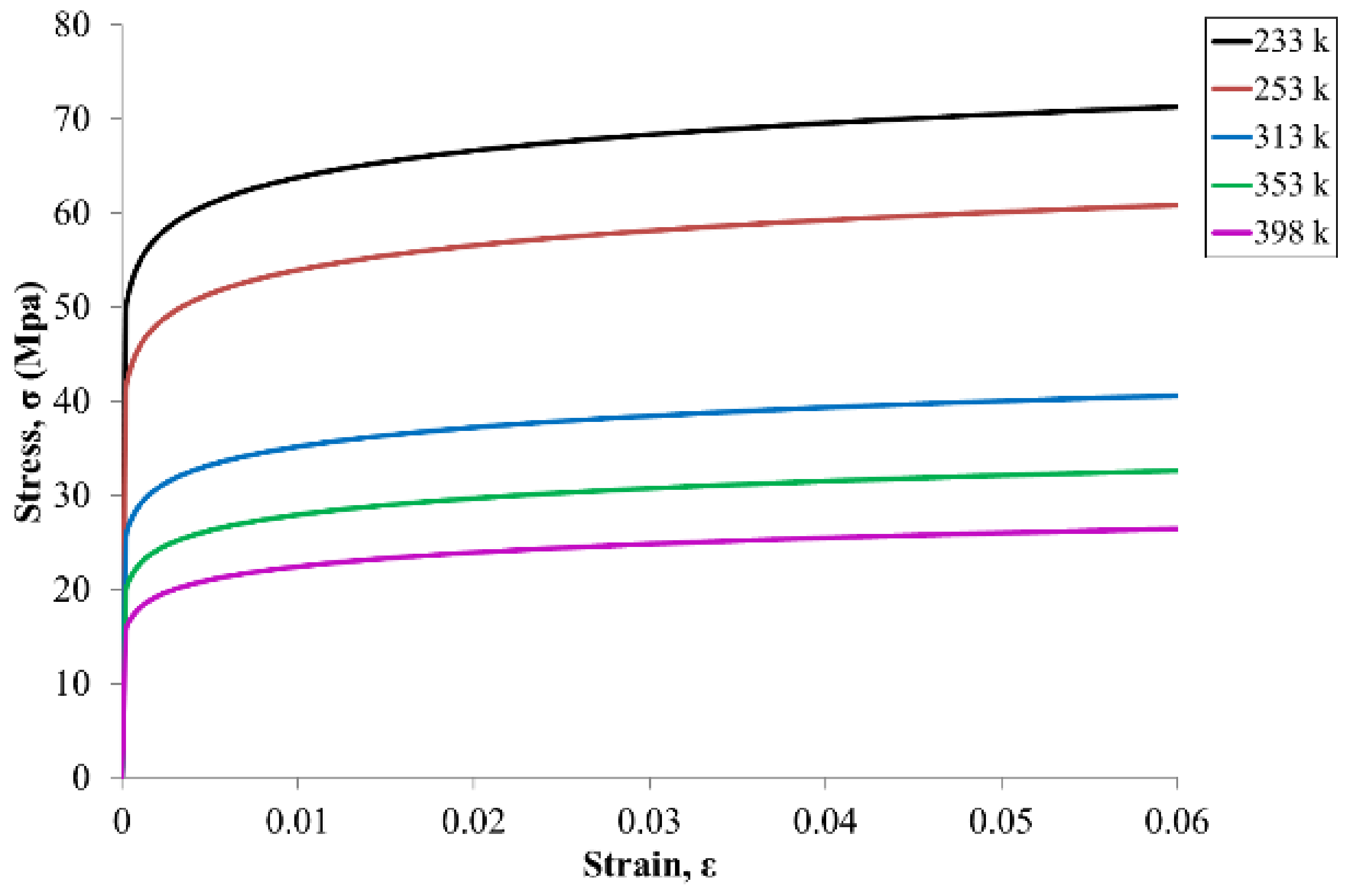

4.1. Material Parameters

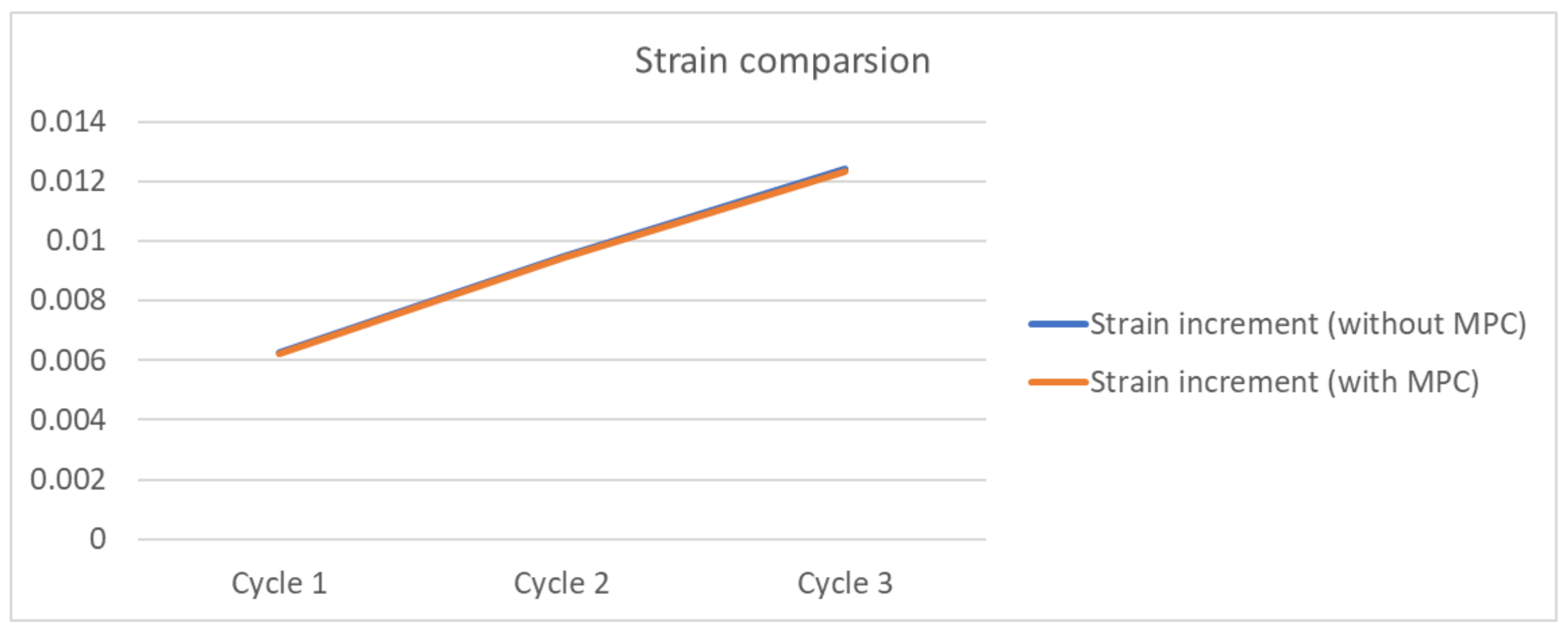

4.2. 2D Plane Strain Model

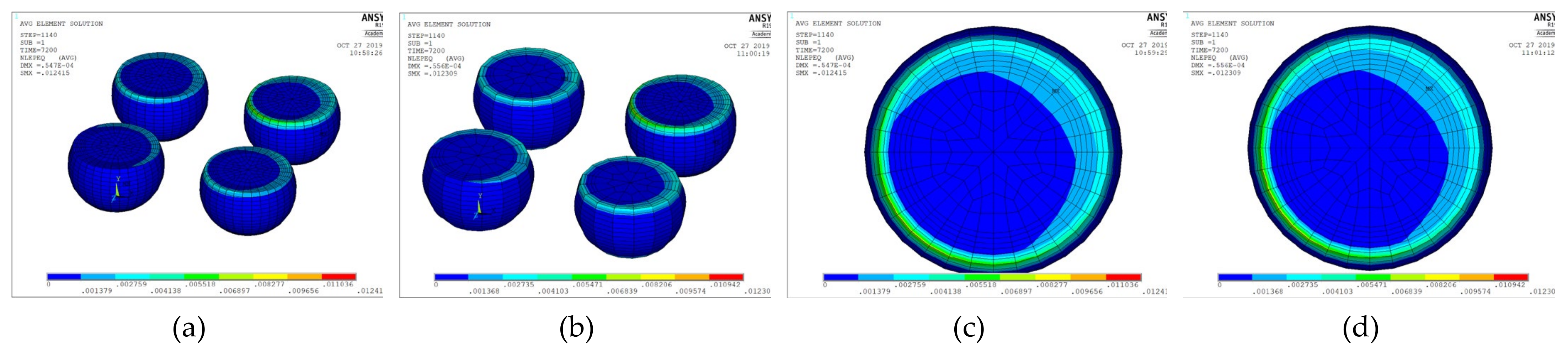

4.3. 3D Quarter Symmetry Model

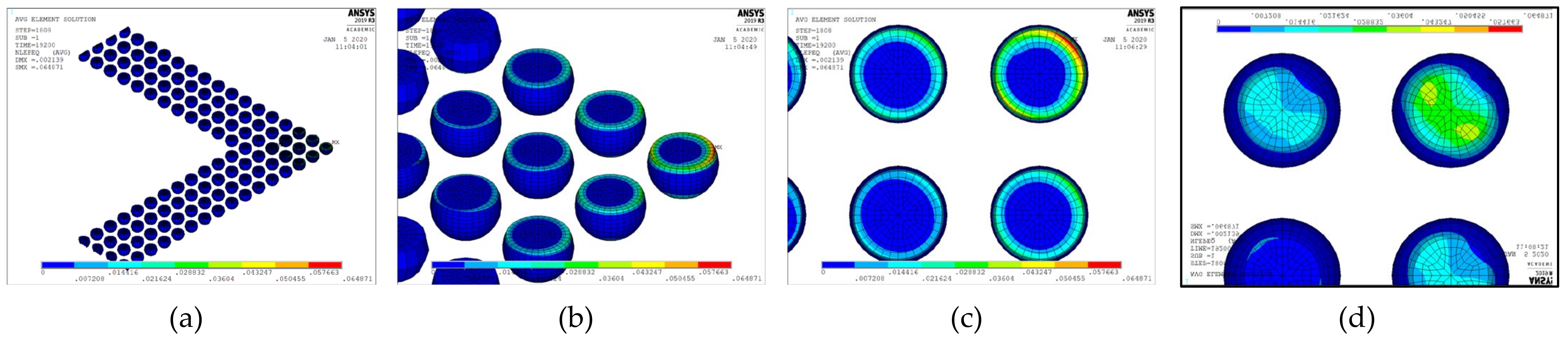

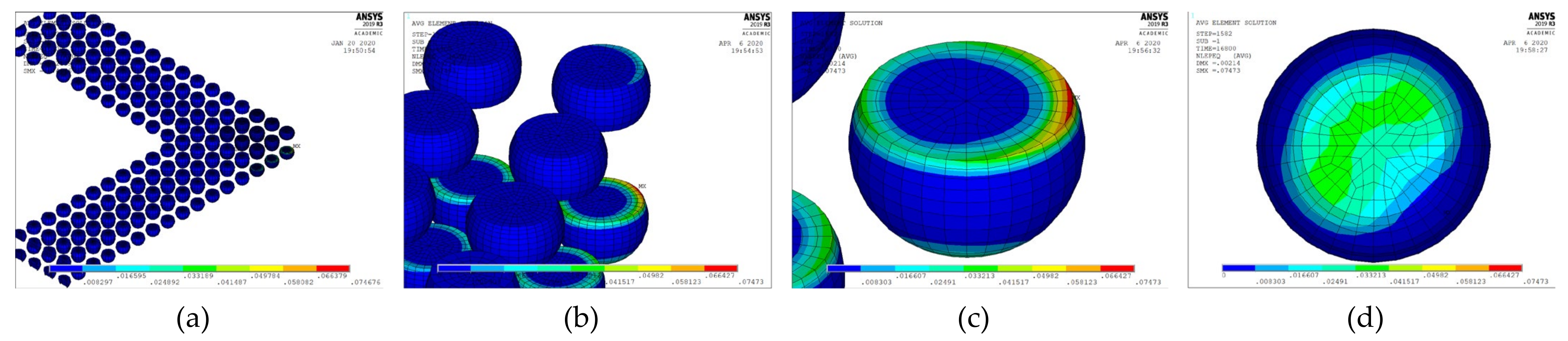

5. Results and Discussion

5.1. 2D Diagonal Plane Strain Model

5.2. 3D Quarter Symmetry Model

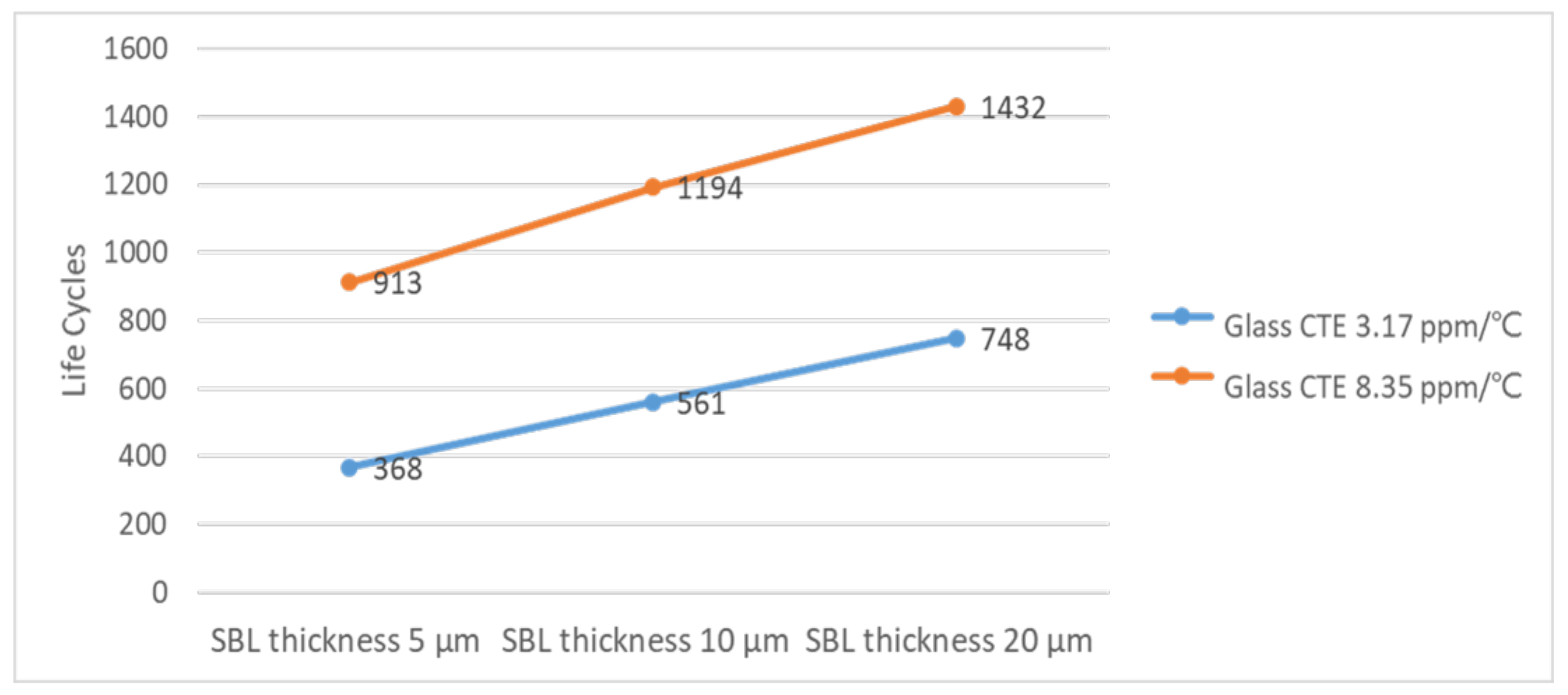

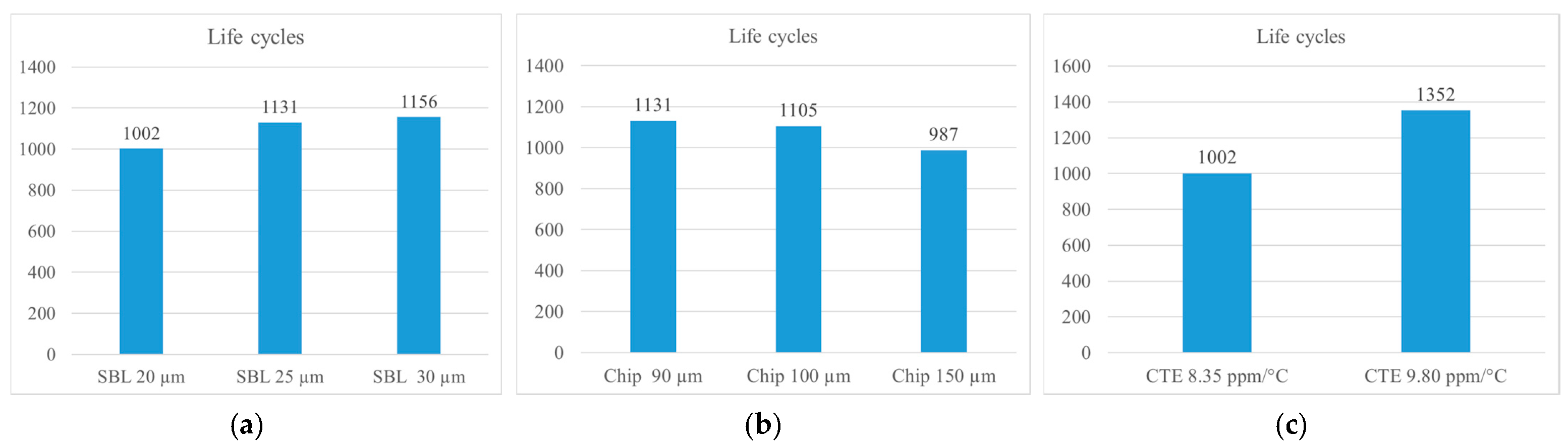

5.3. Parametric Analysis of FO-WLP PoP Structure Using the 2D Plane Strain Finite Element Model

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Lau, J.H.; Li, M.; Tian, D.; Fan, N.; Kuah, E.; Kai, W.; Yong, Q. Warpage and Thermal Characterization of Fan-out Wafer-Level Packaging. In Proceedings of the IEEE 67th Electronic Components and Technology Conference, Lake Buena Vista, FL, USA, 30 May–2 June 2017; pp. 595–602. [Google Scholar]

- Tseng, C.F.; Liu, C.S.; Wu, C.H.; Yu, D. InFO (Wafer Level Integrated Fan-Out) Technology. In Proceedings of the IEEE 66th Electronic Components and Technology Conference, Las Vegas, NV, USA, 31 May–3 June 2016; pp. 1–6. [Google Scholar]

- Tanaka, M.; Kuramochi, S.; Tai, T.; Sato, Y.; Kidera, N. High Frequency Characteristics of Glass Interposer. In Proceedings of the 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 26–29 May 2020; pp. 601–610. [Google Scholar] [CrossRef]

- Tsai, C.H.; Liu, S.W.; Chiang, K.N. Warpage Analysis of Fan-Out Panel-Level Packaging Using Equivalent CTE. IEEE Trans. Device Mater. Reliab. 2019, 20, 51–57. [Google Scholar] [CrossRef]

- Che, F.X.; Yamamoto, K.; Rao, V.S.; Sekhar, V.N. Panel Warpage of Fan-Out Panel-Level Packaging Using RDL-First Technology. IEEE Trans. Compon. Packag. Manuf. Technol. 2019, 10, 304–313. [Google Scholar] [CrossRef]

- Shah, U.; Liljeholm, J.; Campion, J.; Ebefors, T.; Oberhammer, J. Low-Loss, High-Linearity RF Interposers Enabled by Through Glass Vias. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 960–962. [Google Scholar] [CrossRef]

- Barbera, D.; Chen, H. On the Plastic Strain Accumulation in Notched Bars During High-Temperature Creep Dwell. J. Mech. 2020, 36, 167–176. [Google Scholar] [CrossRef]

- Cheng, H.C.; Wu, Z.D.; Liu, Y.C. Viscoelastic Warpage Modeling of Fan-Out Wafer-Level Packaging During Wafer-Level Mold Cure Process. IEEE Trans. Compon. Packag. Manuf. Technol. 2020, 10, 1240–1250. [Google Scholar] [CrossRef]

- Demir, K.; Armutlulu, A.; Sundaram, V.; Raj, P.M.; Tummala, R.R. Reliability of Copper Through-Package Vias in Bare Glass Interposers. IEEE Trans. Compon. Packag. Manuf. Technol. 2017, 7, 829–837. [Google Scholar] [CrossRef]

- Yang, C.C.; Su, Y.F.; Liang, S.Y.; Chiang, K.N. Simulation of Wire Bonding Process Using Explicit Fem with Ale Remeshing Technology. J. Mech. 2020, 36, 47–54. [Google Scholar] [CrossRef]

- Ramachandran, V.; Chiang, K.N. Feasibility Evaluation of Creep Model for Failure Assessment of Solder Joint Reliability of Wafer-Level Packaging. IEEE Trans. Device Mater. Reliab 2017, 17, 672–677. [Google Scholar] [CrossRef]

- Wu, P.L.; Wang, P.H.; Chiang, K.N. Empirical Solutions and Reliability Assessment of Thermal Induced Creep Failure for Wafer Level Packaging. IEEE Trans. Device Mater. Reliab. 2018, 19, 126–132. [Google Scholar] [CrossRef]

- Brakke, K.A. Surface Evolver Manual; Version 2.01; The Geometry Center: Minneapolis, MN, USA, 1996. [Google Scholar]

- Li, L.; Yeung, B. Wafer level and flip chip design through solder prediction models and validation. IEEE Trans. Compon. Packag. Technol. 2001, 24, 650–654. [Google Scholar] [CrossRef]

- Yeung, B.H.; Lee, T.-Y.T. Evaluation and optimization of package processing and design through solder joint profile prediction. IEEE Trans. Electron. Packag. Manuf. 2003, 26, 68–74. [Google Scholar] [CrossRef]

- Coffin, L.F. A study of the effects of cyclic thermal stress on a ductile metal. Transactions ASME 1954, 76, 931–950. [Google Scholar]

- Mason, S.S. Behavior of materials under conditions of thermal stress. Natl. Advis. Comm. Aeronaut. Tech. Note 1953, 2933, 317–350. [Google Scholar]

- Chou, P.H.; Chiang, K.; Liang, S.Y. Reliability Assessment of Wafer Level Package using Artificial Neural Network Regression Model. J. Mech. 2019, 35, 829–837. [Google Scholar] [CrossRef]

- Wang, P.H.; Lee, Y.; Lee, C.K.; Chang, H.H.; Chiang, K.N. Solder Joint Reliability Assessment and Pad Size Studies of FO-WLP with Glass Substrate. IEEE Trans. Device Mater. Reliab. 2021, 1, 96–101. [Google Scholar] [CrossRef]

- Lee, H.H.; Kwak, J.B. Realistic Creep Characterization for Sn3.0Ag0.5Cu Solder Joints in Flip Chip BGA Package. J. Electron. Mater. 2019, 48, 6857–6865. [Google Scholar] [CrossRef]

| Component | Size (mm) |

|---|---|

| Glass substrate | 14 × 14 × 0.10 |

| Chip | 10 × 10 × 0.10 |

| Molding compound | 0.19 |

| Die attach film | 10 × 10 × 0.01 |

| Printed circuit board | 77 × 132 × 1 |

| Lower pad | 0.24 × 0.02 |

| Upper pad | 0.25 × 0.002 |

| Stress buffer layer (SBL; polyimide) | 0.005 |

| Through glass via | 0.025 × 0.1 |

| Solder ball diameter | 0.25 |

| Solder ball pitch | 0.4 |

| Material | Young’s Modulus (GPa) | Poisson’s Ratio | CTE (ppm/°C) |

|---|---|---|---|

| Silicon | 150 | 0.28 | 2.62 |

| Stress buffer layer | 2 | 0.33 | 55 |

| Copper | 68.9 | 0.34 | 16.7 |

| SAC305 solder | Nonlinear/creep | 0.4 | 22.36 |

| Die attach film | 1.66 | 0.26 | 17 |

| Glass A | 73.6 | 0.23 | 3.17 |

| Glass B | 71.7 | 0.21 | 8.37 |

| Glass C | 74 | 0.23 | 9.8 |

| Printed circuit board | 18.2 | 0.19 | 16 |

| Molding compound | 8.96 | 0.35 | 15 |

| Material | A (1/s) | B (1/MPa) | n | Q (J/mol) |

|---|---|---|---|---|

| Value | 2631 | 0.0425 | 4.96 | 52,400 |

| Item | SBL Thickness (µm) | Chip Thickness (µm) | CTE (ppm/°C) | Life Prediction | |||||

|---|---|---|---|---|---|---|---|---|---|

| 20 | 25 | 30 | 90 | 100 | 150 | 8.35 | 9.8 | ||

| 1 | V | V | V | 1002 | |||||

| 2 | V | V | V | 1352 | |||||

| 3 | V | V | V | 976 | |||||

| 4 | V | V | V | 1337 | |||||

| 5 | V | V | V | 923 | |||||

| 6 | V | V | V | 1301 | |||||

| 7 | V | V | V | 1131 | |||||

| 8 | V | V | V | 1398 | |||||

| 9 | V | V | V | 1105 | |||||

| 10 | V | V | V | 1241 | |||||

| 11 | V | V | V | 987 | |||||

| 12 | V | V | V | 1156 | |||||

| 13 | V | V | V | 1427 | |||||

| 14 | V | V | V | 1129 | |||||

| 15 | V | V | V | 1410 | |||||

| 16 | V | V | V | 998 | |||||

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, P.-H.; Huang, Y.-W.; Chiang, K.-N. Reliability Evaluation of Fan-Out Type 3D Packaging-On-Packaging. Micromachines 2021, 12, 295. https://doi.org/10.3390/mi12030295

Wang P-H, Huang Y-W, Chiang K-N. Reliability Evaluation of Fan-Out Type 3D Packaging-On-Packaging. Micromachines. 2021; 12(3):295. https://doi.org/10.3390/mi12030295

Chicago/Turabian StyleWang, Pao-Hsiung, Yu-Wei Huang, and Kuo-Ning Chiang. 2021. "Reliability Evaluation of Fan-Out Type 3D Packaging-On-Packaging" Micromachines 12, no. 3: 295. https://doi.org/10.3390/mi12030295

APA StyleWang, P.-H., Huang, Y.-W., & Chiang, K.-N. (2021). Reliability Evaluation of Fan-Out Type 3D Packaging-On-Packaging. Micromachines, 12(3), 295. https://doi.org/10.3390/mi12030295