Fabrication and Characterization of Nanonet-Channel LTPS TFTs Using a Nanosphere-Assisted Patterning Technique

Abstract

:1. Introduction

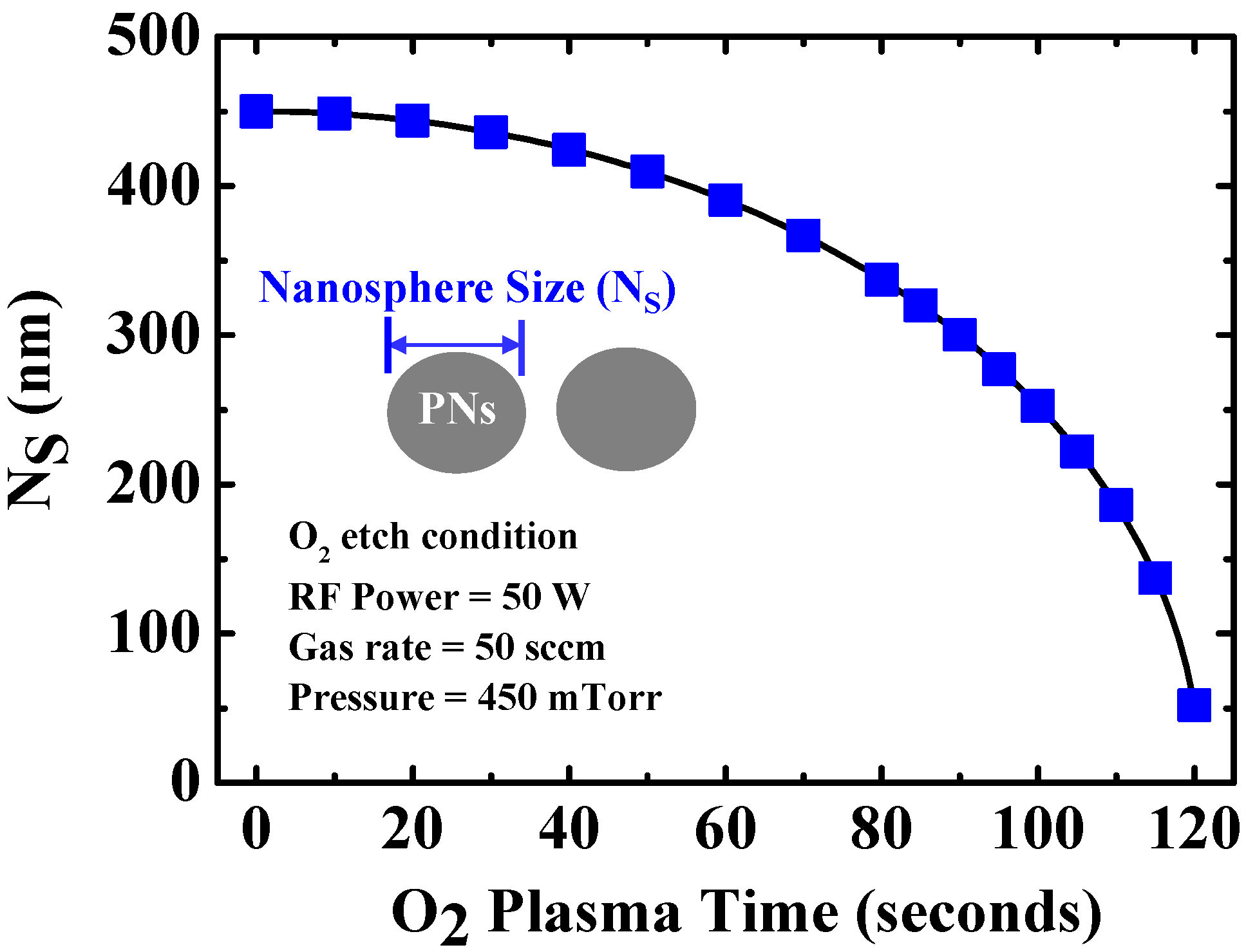

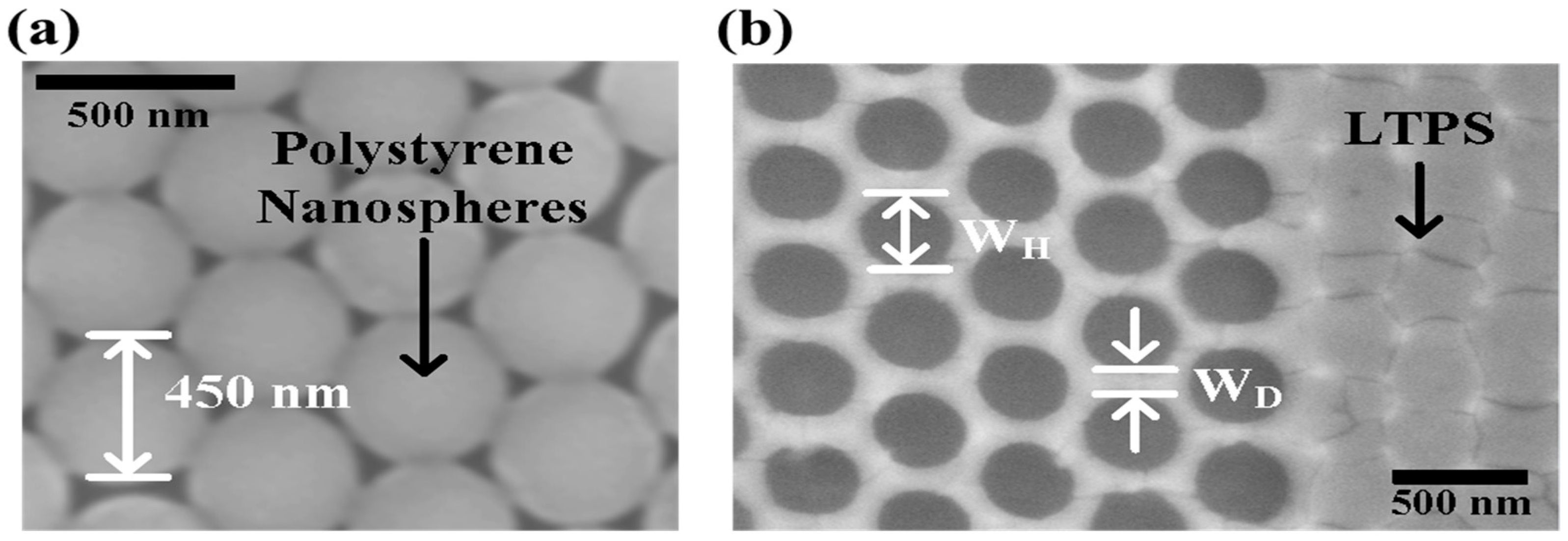

2. Experimental Details

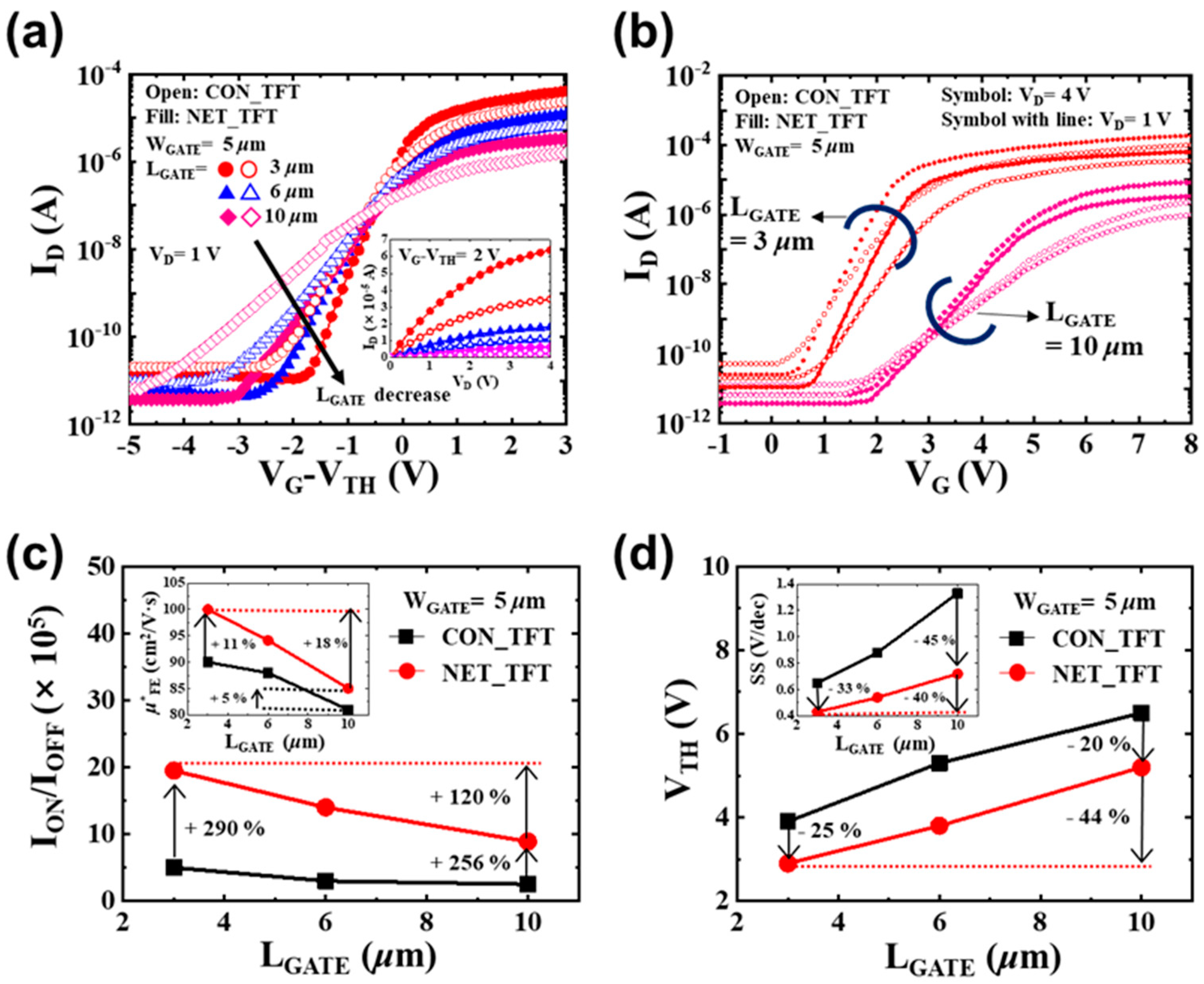

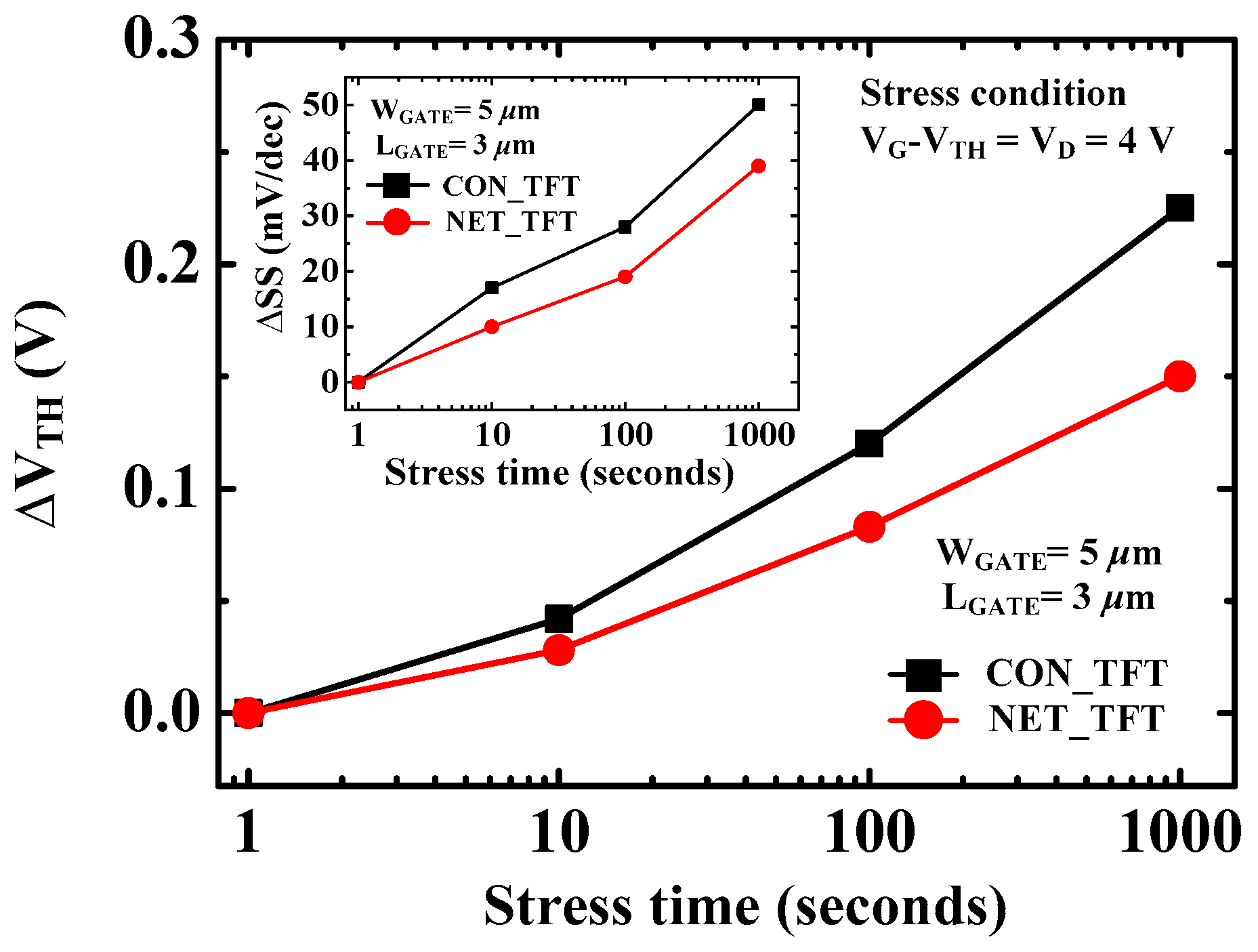

3. Results and Discussions

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Tai, Y.-H.; Kuo, Y.-F.; Lee, Y.-H. Photosensitivity Analysis of Low-Temperature Poly-Si Thin-Film Transistor Based on the Unit-Lux-Current. IEEE Trans. Electron. Devices 2009, 56, 50–56. [Google Scholar] [CrossRef]

- Shih-Ching, C.; Ting-Chang, C.; Po-Tsun, L.; Yung-Chun, W.; Po-Shun, L.; Bae-Heng, T.; Jang-Hung, S.; Sze, S.M.; Chun-Yen, C.; Chen-Hsin, L. A Novel Nanowire Channel Poly-Si TFT Functioning as Transistor and Nonvolatile SONOS Memory. IEEE Electron. Device Lett. 2007, 28, 809–811. [Google Scholar] [CrossRef]

- Goto, T.; Saito, K.; Imaizumi, F.; Hatanaka, M.; Takimoto, M.; Mizumura, M.; Gotoh, J.; Ikenoue, H.; Sugawa, S. LTPS Thin-Film Transistors Fabricated Using New Selective Laser Annealing System. IEEE Trans. Electron. Devices 2018, 65, 3250–3256. [Google Scholar] [CrossRef]

- Asano, A.; Kinoshita, T. 43.2: Low-Temperature Polycrystalline-Silicon TFT Color LCD Panel Made of Plastic Substrates. SID Symp. Dig. Tech. Pap. 2002, 33, 1196. [Google Scholar] [CrossRef]

- Farmakis, F.V.; Brini, J.; Kamarinos, G.; Angelis, C.T.; Dimitriadis, C.A.; Miyasaka, M. On-current modeling of large-grain polycrystalline silicon thin-film transistors. IEEE Trans. Electron. Devices 2001, 48, 701–706. [Google Scholar] [CrossRef]

- Tsai, C.-C.; Wei, K.-F.; Lee, Y.-J.; Chen, H.-H.; Wang, J.-L.; Lee, I.-C.; Cheng, H.-C. High-Performance Short-Channel Double-Gate Low-Temperature Polysilicon Thin-Film Transistors Using Excimer Laser Crystallization. IEEE Electron. Device Lett. 2007, 28, 1010–1013. [Google Scholar] [CrossRef]

- Nakajima, Y.; Kida, Y.; Murase, M.; Toyoshima, Y.; Maki, Y. 21.3: Invited Paper: Latest Development of “System-on-Glass” Display with Low Temperature Poly-Si TFT. SID Symp. Dig. Tech. Pap. 2004, 35, 864. [Google Scholar] [CrossRef]

- Stewart, M.; Howell, R.S.; Pires, L.; Hatalis, M.K. Polysilicon TFT technology for active matrix OLED displays. IEEE Trans. Electron. Devices 2001, 48, 845–851. [Google Scholar] [CrossRef]

- Son, S.W.; Byun, C.W.; Lee, Y.W.; Yun, S.J.; Takaloo, A.V.; Park, J.H.; Joo, S.K. Effect of Dopant Concentration in Lightly Doped Drain Region on the Electrical Properties of N-Type Metal Induced Lateral Crystallization Polycrystalline Silicon Thin Film Transistors. Jpn. J. Appl. Phys. 2013, 52, 10MC13. [Google Scholar] [CrossRef]

- Park, J.H.; Seok, K.H.; Kim, H.Y.; Chae, H.J.; Lee, S.K.; Joo, S.K. A Novel Design of Quasi-Lightly Doped Drain Poly-Si Thin-Film Transistors for Suppression of Kink and Gate-Induced Drain Leakage Current. IEEE Electron. Device Lett. 2015, 36, 351–353. [Google Scholar] [CrossRef]

- Yamauchi, N.; Hajjar, J.-J.J.; Reif, R. Polysilicon thin-film transistors with channel length and width comparable to or smaller than the grain size of the thin film. IEEE Trans. Electron. Devices 1991, 38, 55–60. [Google Scholar] [CrossRef]

- Watakabe, H.; Sameshima, T. Polycrystalline silicon thin-film transistors fabricated by defect reduction methods. IEEE Trans. Electron. Devices 2002, 49, 2217–2221. [Google Scholar] [CrossRef]

- Wang, A.W.; Saraswat, K.C. A strategy for modeling of variations due to grain size in polycrystalline thin-film transistors. IEEE Trans. Electron. Devices 2000, 47, 1035–1043. [Google Scholar] [CrossRef]

- Kouvatsos, D.N.; Voutsas, A.T.; Hatalis, M.K. High-performance thin-film transistors in large grain size polysilicon deposited by thermal decomposition of disilane. IEEE Trans. Electron. Devices 1996, 43, 1399–1406. [Google Scholar] [CrossRef]

- Wu, I.-W.; Huang, T.-Y.; Jackson, W.B.; Lewis, A.G.; Chiang, A. Passivation kinetics of two types of defects in polysilicon TFT by plasma hydrogenation. IEEE Electron. Device Lett. 1991, 12, 181–183. [Google Scholar] [CrossRef]

- Chang-Ho, O.; Matsumura, M. A proposed single grain-boundary thin-film transistor. IEEE Electron. Device Lett. 2001, 22, 20–22. [Google Scholar] [CrossRef]

- Yeh, M.-S.; Lee, Y.-J.; Hung, M.-F.; Liu, K.-C.; Wu, Y.-C. High-Performance Gate-All-Around Poly-Si Thin-Film Transistors by Microwave Annealing with NH3 Plasma Passivation. IEEE Trans. Nanotechnol. 2013, 12, 636–640. [Google Scholar] [CrossRef]

- Sposili, R.S.; Im, J.S. Sequential lateral solidification of thin silicon films on SiO2. Appl. Phys. Lett. 1996, 69, 2864–2866. [Google Scholar] [CrossRef]

- Wang, C.-L.; Lee, I.-C.; Wu, C.-Y.; Chou, C.-H.; Yang, P.-Y.; Cheng, Y.-T.; Cheng, H.-C. High-Performance Polycrystalline-Silicon Nanowire Thin-Film Transistors with Location-Controlled Grain Boundary via Excimer Laser Crystallization. IEEE Electron. Device Lett. 2012, 33, 1562–1564. [Google Scholar] [CrossRef]

- Fukuzumi, Y.; Katsumata, R.; Kito, M.; Kido, M.; Sato, M.; Tanaka, H.; Nagata, Y.; Matsuoka, Y.; Iwata, Y.; Aochi, H.; et al. Optimal Integration and Characteristics of Vertical Array Devices for Ultra-High Density, Bit-Cost Scalable Flash Memory. In Proceedings of the 2007 International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; pp. 449–452. [Google Scholar]

- Lee, H.; Lee, J.; Baek, S.; Jeong, W.H.; Lee, Y.; Yang, T.; Lee, J.-S. Highly Enhanced Performance of Network Channel Polysilicon Thin-Film Transistors. IEEE Electron. Device Lett. 2017, 38, 187–190. [Google Scholar] [CrossRef]

- Lee, J.; Lee, H.; Jin, B.; Oh, H.; Baek, S.; Yoon, G.; Lee, Y.; Baek, R.-H.; Lee, J.-S. Impact of geometrical parameters on the electrical performance of network-channel polycrystalline silicon thin-film transistors. Jpn. J. Appl. Phys. 2018, 57, 104001. [Google Scholar] [CrossRef]

- Liou, J.-K.; Chen, C.-C.; Chou, P.-C.; Tsai, Z.-J.; Chang, Y.-C.; Liu, W.-C. Implementation of a High-Performance GaN-Based Light-Emitting Diode Grown on a Nanocomb-Shaped Patterned Sapphire Substrate. IEEE J. Quantum Electron. 2014, 50, 973–980. [Google Scholar] [CrossRef]

- Sun, S.; Lu, P.; Xu, J.; Xu, L.; Chen, K.; Wang, Q.; Zuo, Y. Fabrication of Anti-reflecting Si Nano-structures with Low Aspect Ratio by Nano-sphere Lithography Technique. Nano-Micro Lett. 2013, 5, 18–25. [Google Scholar] [CrossRef] [Green Version]

- Zhang, Y.; Geng, H.; Zhou, Z.; Wu, J.; Wang, Z.; Zhang, Y.; Li, Z.; Zhang, L.; Yang, Z.; Hwang, H. Development of Inorganic Solar Cells by Nano-technology. Nano-Micro Lett. 2012, 4, 124–134. [Google Scholar] [CrossRef] [Green Version]

- Purwidyantri, A.; Kamajaya, L.; Chen, C.-H.; Luo, J.-D.; Chiou, C.-C.; Tian, Y.-C.; Lin, C.-Y.; Yang, C.-M.; Lai, C.-S. A Colloidal Nanopatterning and Downscaling of a Highly Periodic Au Nanoporous EGFET Biosensor. J. Electrochem. Soc. 2018, 165, H3170–H3177. [Google Scholar] [CrossRef]

- Liang, X.; Dong, R.; Ho, J.C. Self-Assembly of Colloidal Spheres toward Fabrication of Hierarchical and Periodic Nanostructures for Technological Applications. Adv. Mater. Technol. 2019, 4, 1800541. [Google Scholar] [CrossRef] [Green Version]

- Valsesia, A.; Meziani, T.; Bretagnol, F.; Colpo, P.; Ceccone, G.; Rossi, F. Plasma assisted production of chemical nano-patterns by nano-sphere lithography: Application to bio-interfaces. J. Phys. D Appl. Phys. 2007, 40, 2341–2347. [Google Scholar] [CrossRef]

- Purwidyantri, A.; Chen, C.-H.; Hwang, B.-J.; Luo, J.-D.; Chiou, C.-C.; Tian, Y.-C.; Lin, C.-Y.; Cheng, C.-H.; Lai, C.-S. Spin-coated Au-nanohole arrays engineered by nanosphere lithography for a Staphylococcus aureus 16S rRNA electrochemical sensor. Biosens. Bioelectron. 2016, 77, 1086–1094. [Google Scholar] [CrossRef]

- Doyle, B.S.; Datta, S.; Doczy, M.; Hareland, S.; Jin, B.; Kavalieros, J.; Linton, T.; Murthy, A.; Rios, R.; Chau, R. High Performance Fully-Depleted Tri-Gate CMOS Transistors. IEEE Electron. Device Lett. 2003, 24, 263–265. [Google Scholar] [CrossRef]

- Krutsick, T.J.; White, M.H.; Hon-Sum, W.; Booth, R.V.H. An improved method of MOSFET modeling and parameter extraction. IEEE Trans. Electron. Devices 1987, 34, 1676–1680. [Google Scholar] [CrossRef]

- Ma, W.C.-Y.; Chiang, T.-Y.; Lin, J.-W.; Chao, T.-S. Oxide Thinning and Structure Scaling Down Effect of Low-Temperature Poly-Si Thin-Film Transistors. J. Disp. Technol. 2012, 8, 12–17. [Google Scholar] [CrossRef]

- Levinson, J.; Shepherd, F.R.; Scanlon, P.J.; Westwood, W.D.; Este, G.; Rider, M. Conductivity behavior in polycrystalline semiconductor thin film transistors. J. Appl. Phys. 1982, 53, 1193–1202. [Google Scholar] [CrossRef]

- Proano, R.E.; Misage, R.S.; Ast, D.G. Development and electrical properties of undoped polycrystalline silicon thin-film transistors. IEEE Trans. Electron. Devices 1989, 36, 1915–1922. [Google Scholar] [CrossRef]

- Chen, C.-Y.; Lee, J.-W.; Wang, S.-D.; Shieh, M.-S.; Lee, P.-H.; Chen, W.-C.; Lin, H.-Y.; Yeh, K.-L.; Lei, T.-F. Negative Bias Temperature Instability in Low-Temperature Polycrystalline Silicon Thin-Film Transistors. IEEE Trans. Electron. Devices 2006, 53, 2993–3000. [Google Scholar] [CrossRef]

- Kow, M.C.; Yuan, H.C.; Gin, M.L.; Chi, G.D.; Jian, H.L. Enhanced degradation in polycrystalline silicon thin-film transistors under dynamic hot-carrier stress. IEEE Electron. Device Lett. 2001, 22, 475–477. [Google Scholar]

- Takeuchi, K.; Tatsumi, T.; Furukawa, A. Channel engineering for the reduction of random-dopant-placement-induced threshold voltage fluctuations. In Proceedings of the 1996 International Electron Devices Meeting, Washington, DC, USA, 10 December 1997; pp. 841–844. [Google Scholar]

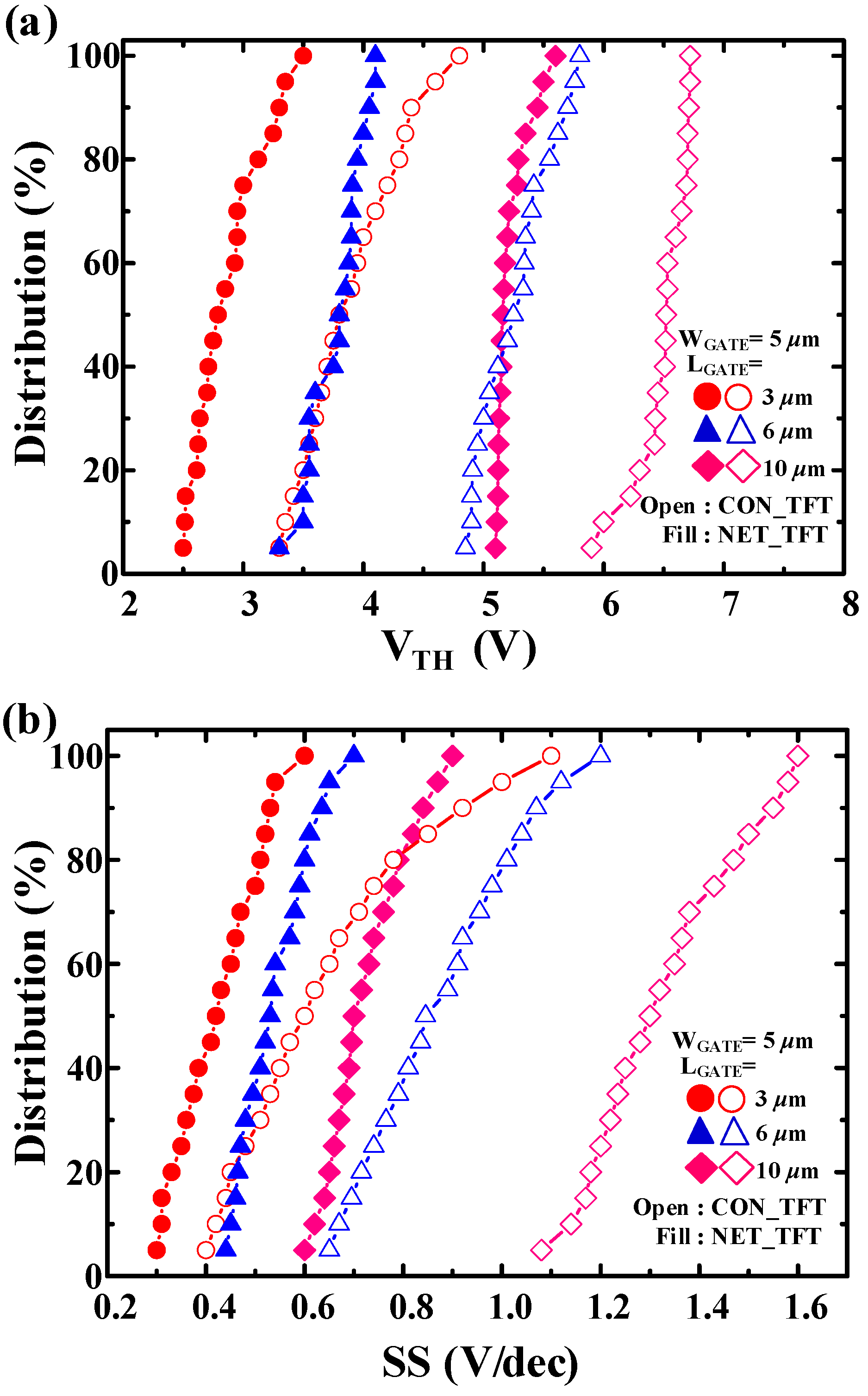

|

Channel Structure |

LGATE [μm] |

AVG. VTH [V] |

STD VTH [V] |

AVG. SS [V/dec] |

STD SS [V/dec] |

|---|---|---|---|---|---|

| conventional | 3 | 3.9 | 0.43 | 0.65 | 0.20 |

| 6 | 5.3 | 0.30 | 0.88 | 0.16 | |

| 10 | 6.5 | 0.23 | 1.33 | 0.15 | |

| nanonet | 3 | 2.9 | 0.29 | 0.43 | 0.09 |

| 6 | 3.8 | 0.20 | 0.54 | 0.08 | |

| 10 | 5.2 | 0.15 | 0.72 | 0.07 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yoon, G.; Kim, D.; Park, I.; Jin, B.; Lee, J.-S. Fabrication and Characterization of Nanonet-Channel LTPS TFTs Using a Nanosphere-Assisted Patterning Technique. Micromachines 2021, 12, 741. https://doi.org/10.3390/mi12070741

Yoon G, Kim D, Park I, Jin B, Lee J-S. Fabrication and Characterization of Nanonet-Channel LTPS TFTs Using a Nanosphere-Assisted Patterning Technique. Micromachines. 2021; 12(7):741. https://doi.org/10.3390/mi12070741

Chicago/Turabian StyleYoon, Gilsang, Donghoon Kim, Iksoo Park, Bo Jin, and Jeong-Soo Lee. 2021. "Fabrication and Characterization of Nanonet-Channel LTPS TFTs Using a Nanosphere-Assisted Patterning Technique" Micromachines 12, no. 7: 741. https://doi.org/10.3390/mi12070741

APA StyleYoon, G., Kim, D., Park, I., Jin, B., & Lee, J.-S. (2021). Fabrication and Characterization of Nanonet-Channel LTPS TFTs Using a Nanosphere-Assisted Patterning Technique. Micromachines, 12(7), 741. https://doi.org/10.3390/mi12070741