Investigation of a 4H-SiC Trench MOSFET with Back-Side Super Junction

Abstract

:1. Introduction

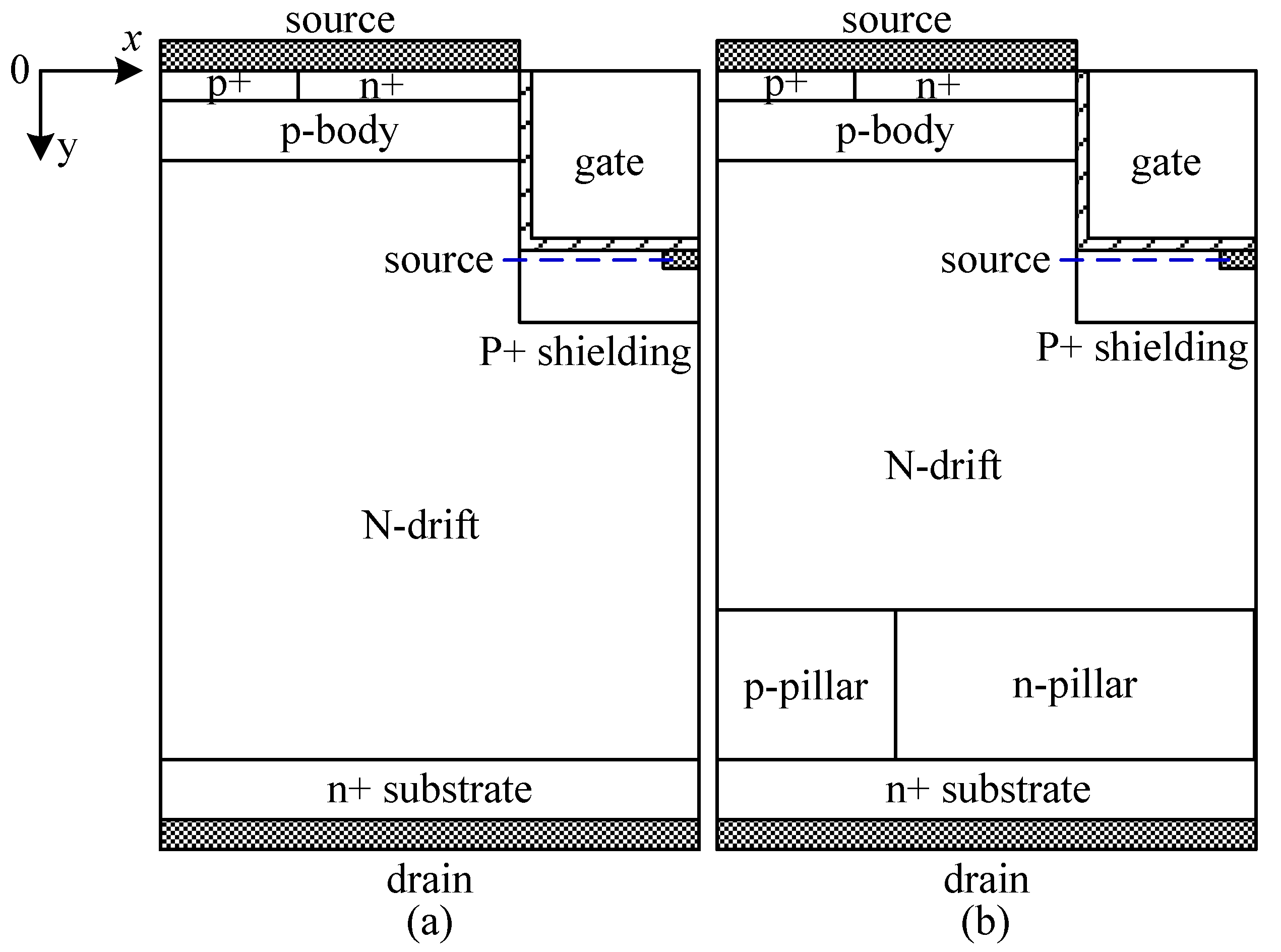

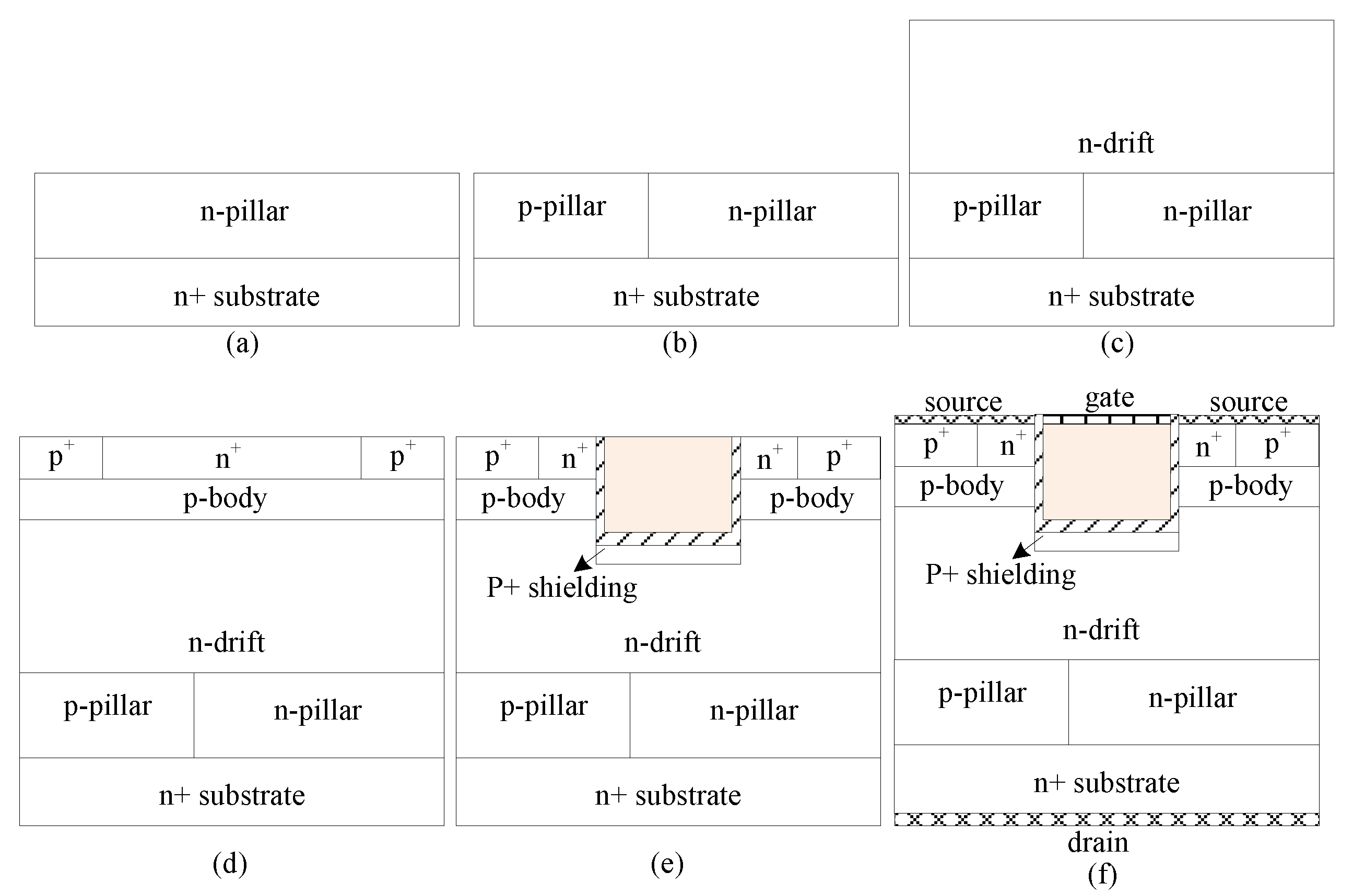

2. Device Structure and Simulation Setup

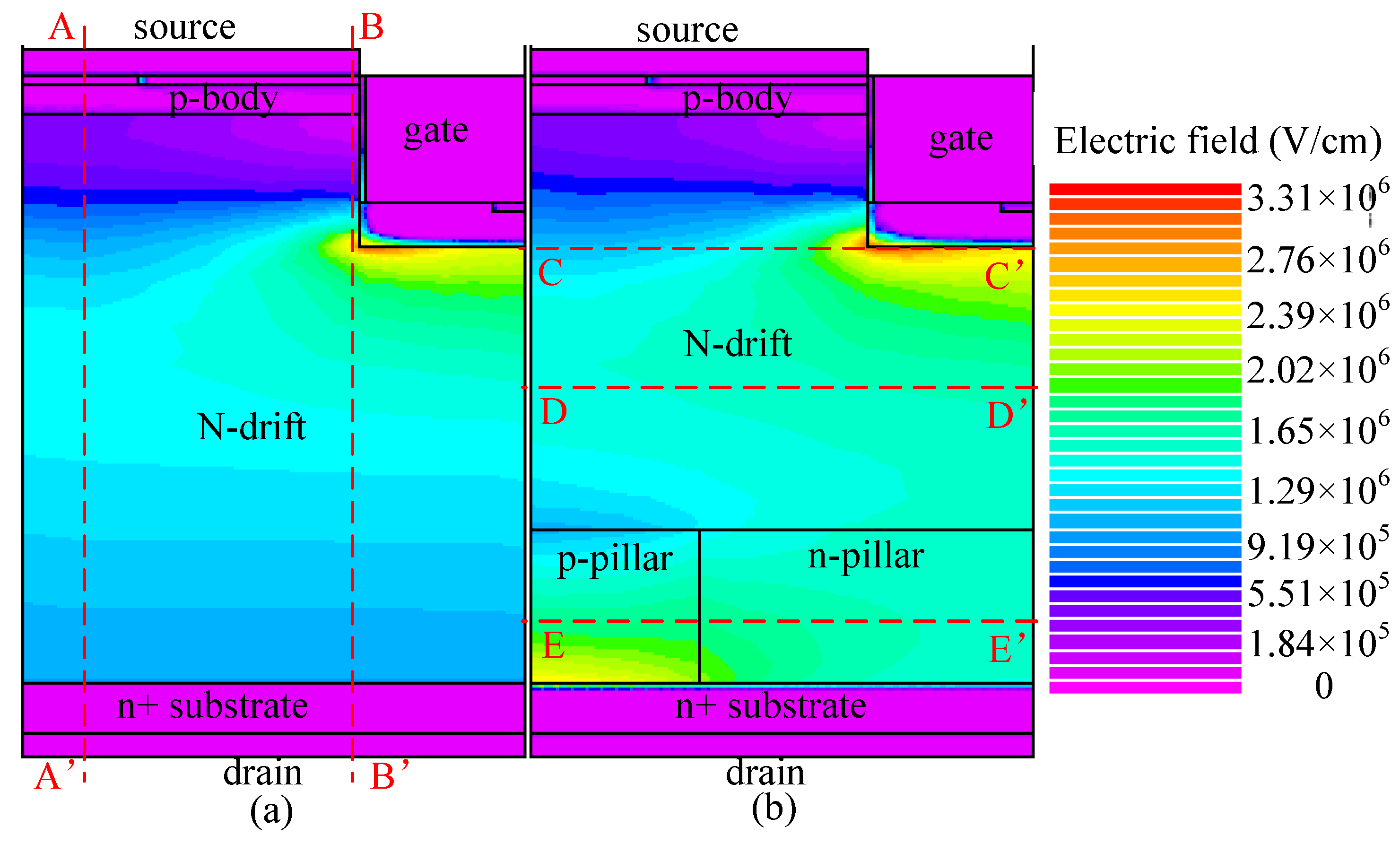

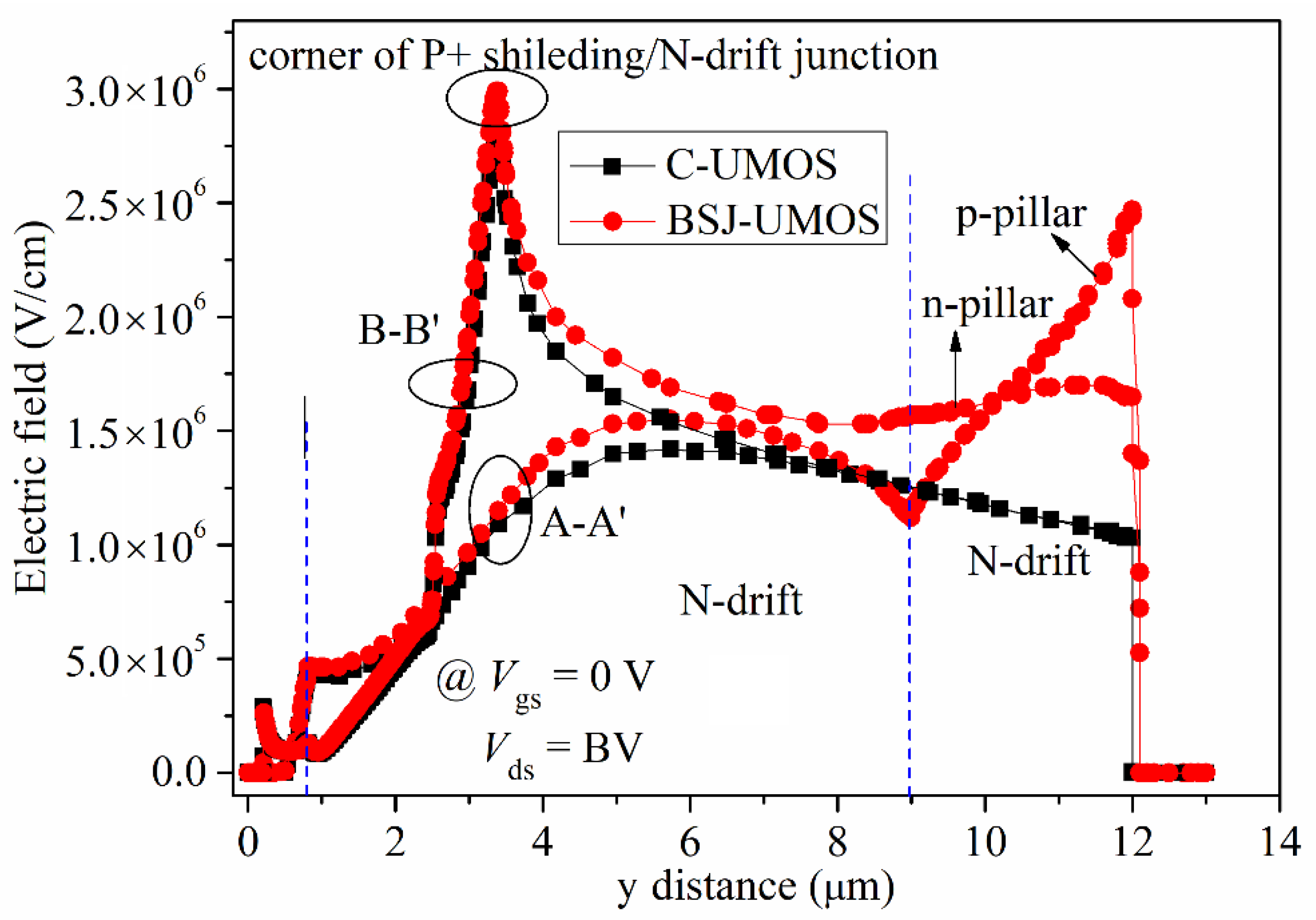

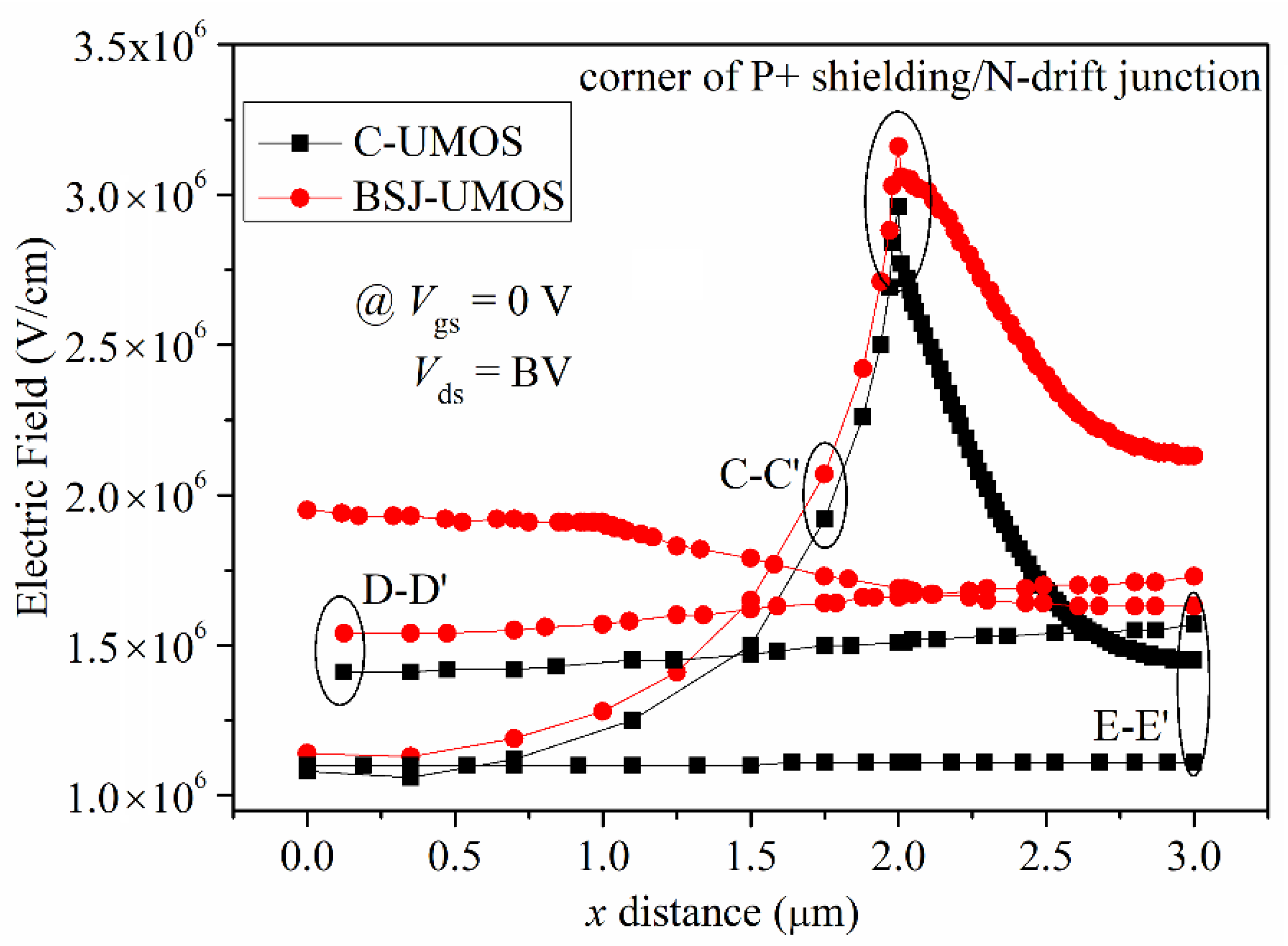

3. Analysis and Discussion of Simulation Results

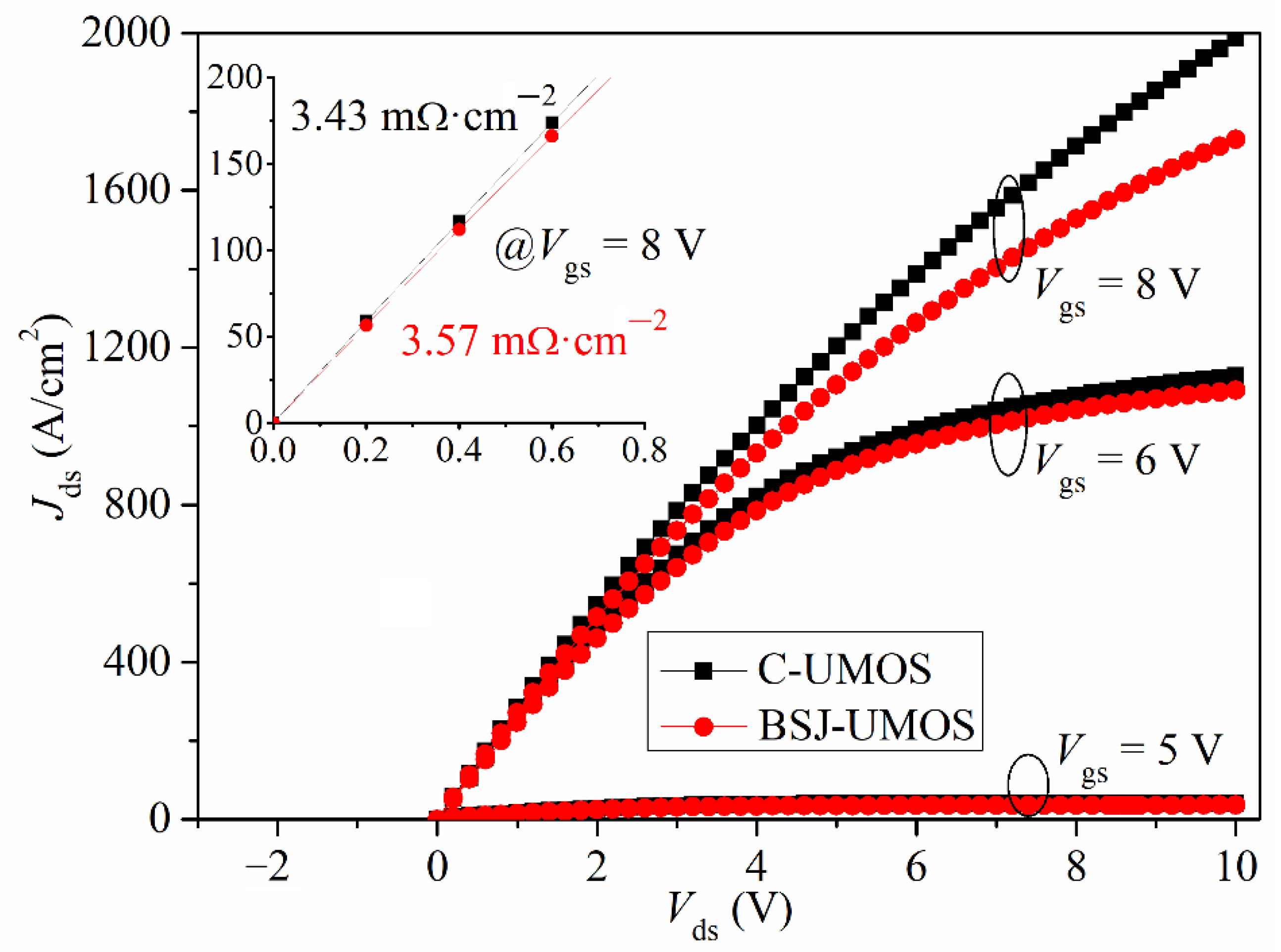

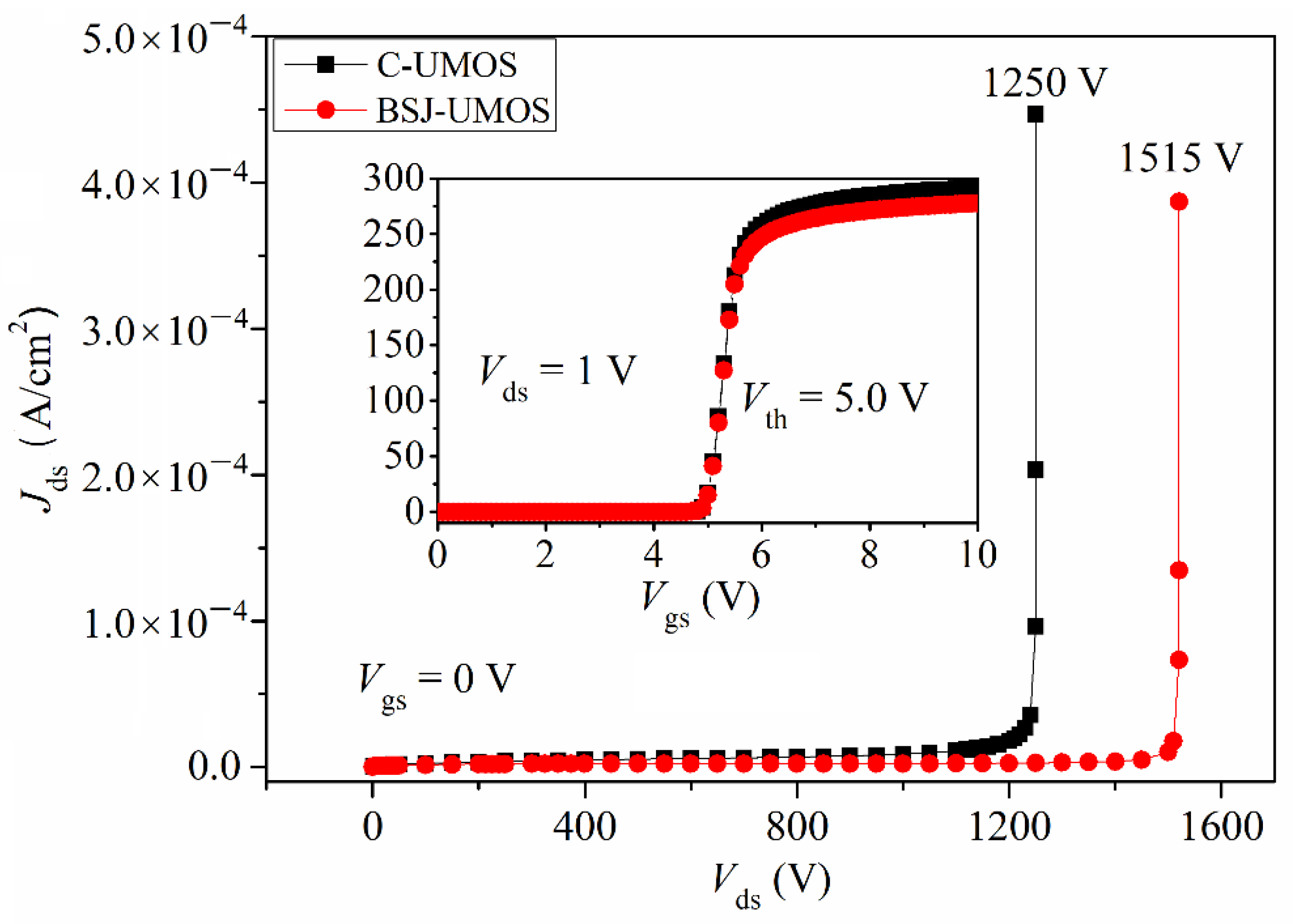

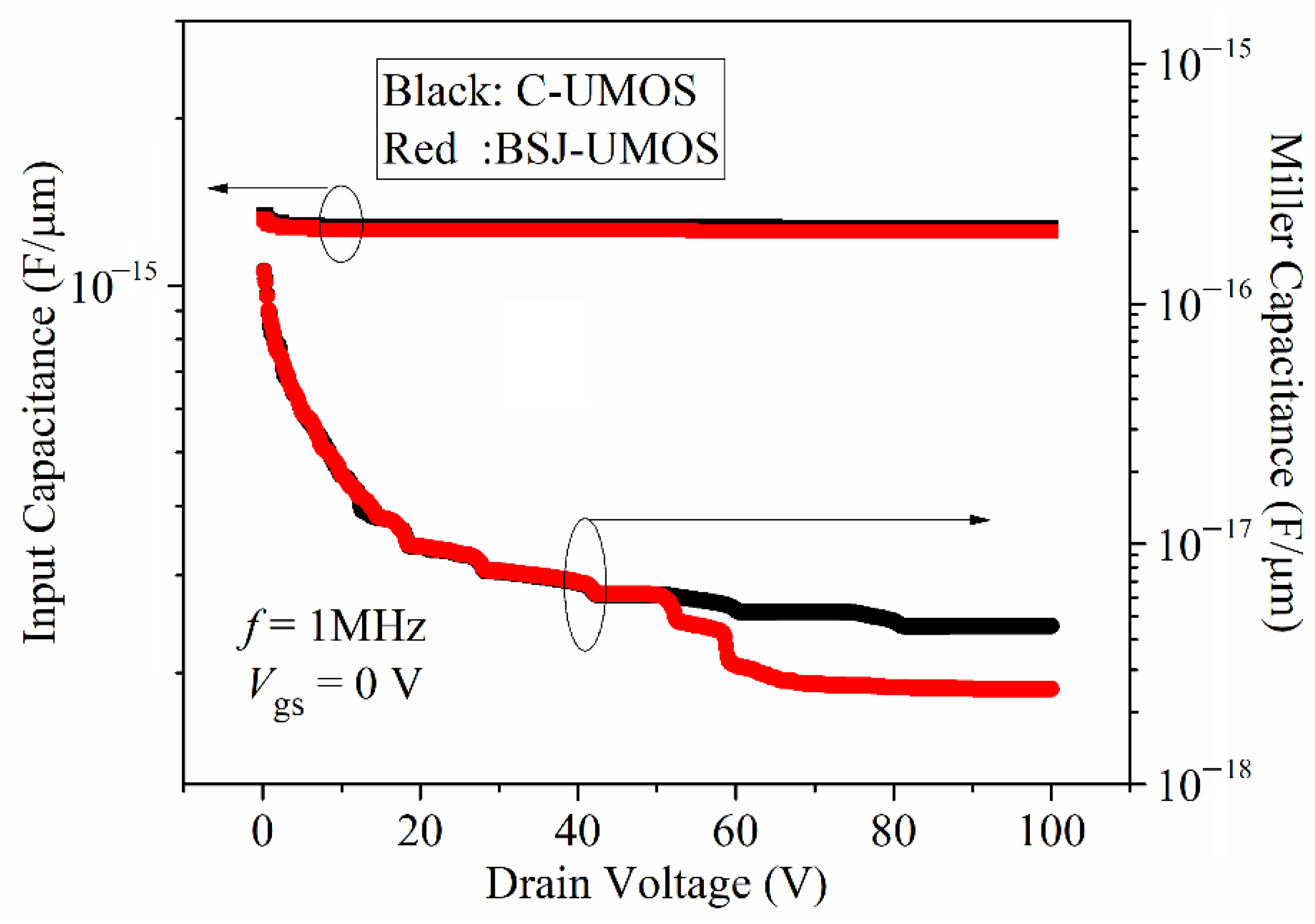

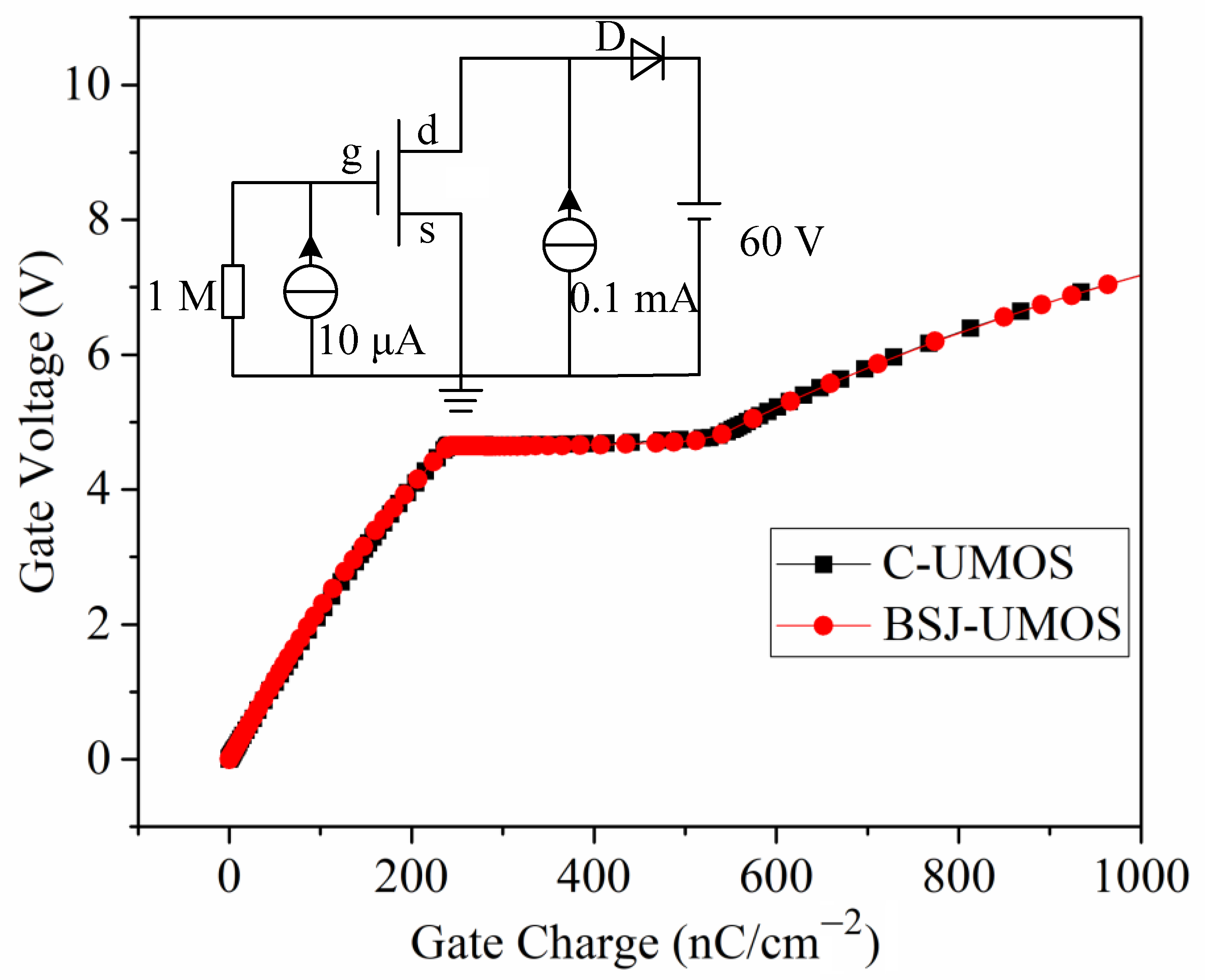

3.1. On and Off Characteristics

3.2. Other Performances

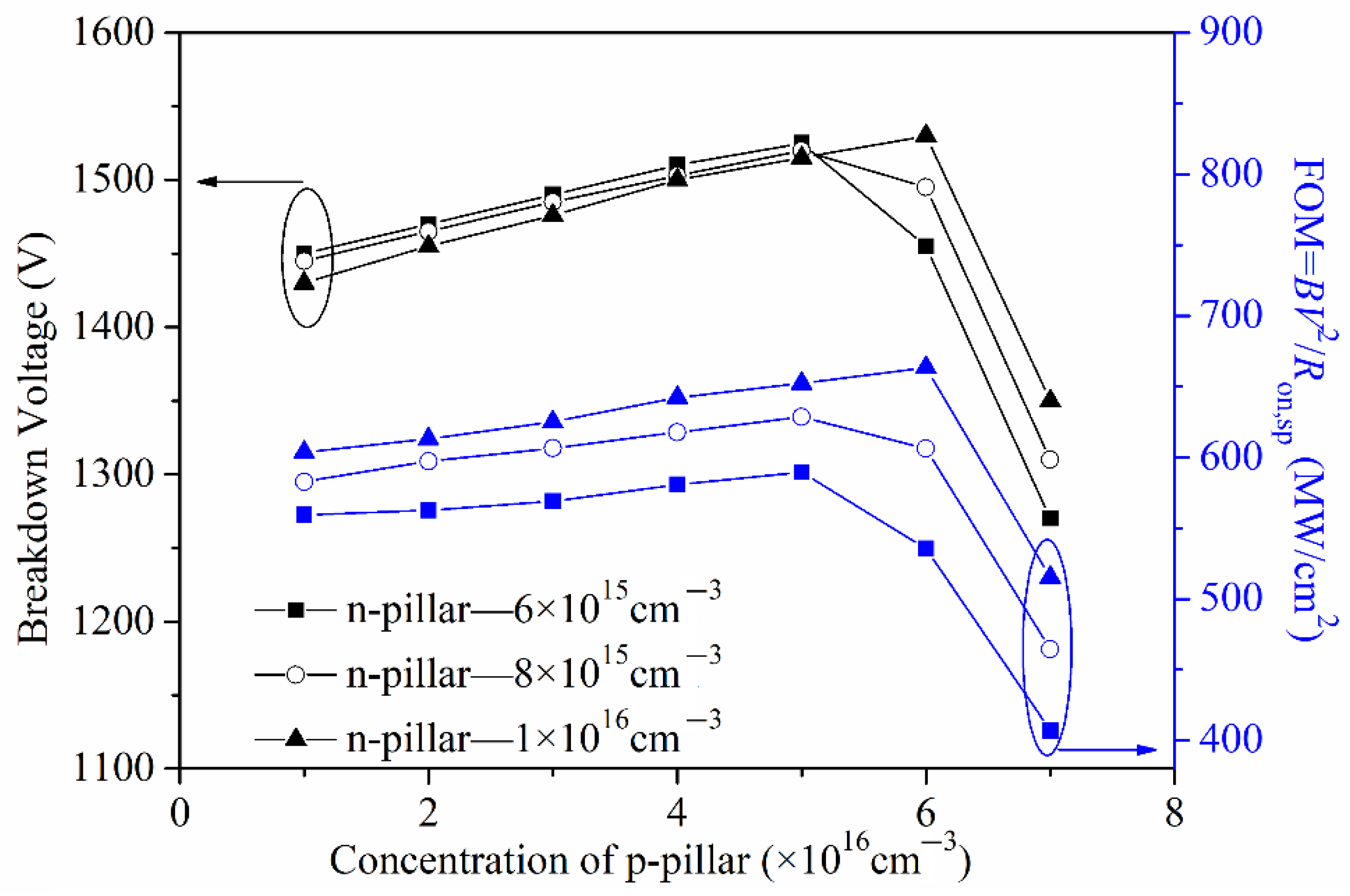

3.3. Parameter Influence

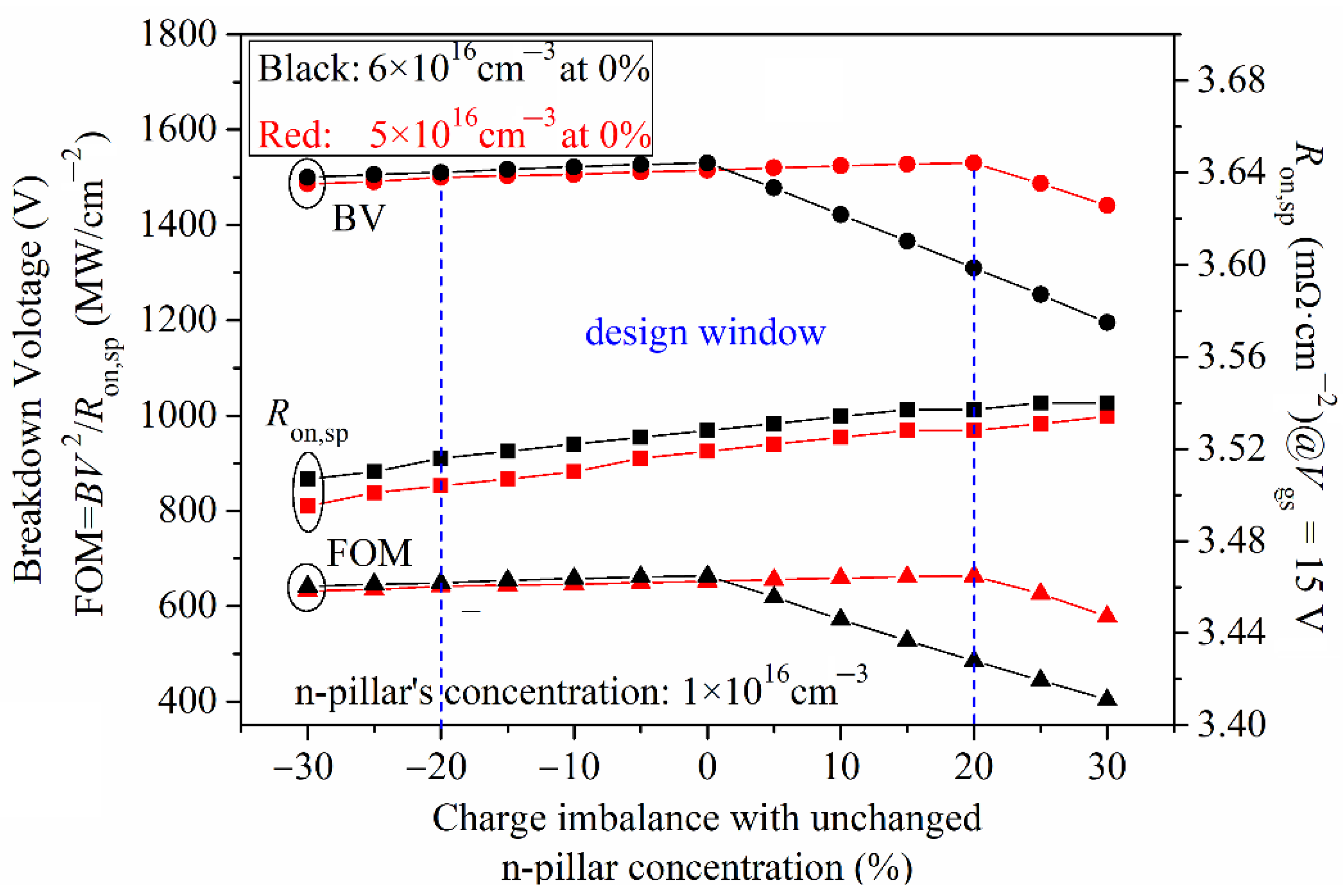

3.4. Charge Imbalance and Design Windows

3.5. Short-Circuit Capability

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Palmour, J.W.; Edmond, J.A.; Kong, H.; Charter, C. Vertical Power Devices in Silicon Carbide. In Silicon Carbide and Related Materials; Trans Tech Publications Ltd.: Zurich, Switzerland, 1994; pp. 499–502. [Google Scholar]

- Cooper, J.; Melloch, M.; Singh, R.; Agarwal, A.; Palmour, J. Status and Prospects for SiC Power MOSFETs. IEEE Trans. Electron. Devices 2004, 49, 658–664. [Google Scholar] [CrossRef]

- Östling, M.; Ghandi, R.; Zetterling, C. SiC Power Devices–Present Status, Applications and Future Perspective. In Proceedings of the 2011 IEEE 23rd International Symposium on Power Semiconductor Devices and ICs, San Diego, CA, USA, 23–26 May 2011; pp. 10–15. [Google Scholar]

- Friedrichs, P.; Burte, E.P.; Schorner, R. Dielectric Strength of Thermal Oxides on 6H-SiC and 4H-SiC. Appl. Phys. Lett. 1994, 65, 1665–1667. [Google Scholar] [CrossRef]

- Shenoy, J.N.; Das, M.K.; Cooper, J.A.; Melloch, M.R.; Palmour, J.W. Effort of Substrate Orientation and Crystal Anisotropy on the Thermally Oxidized SiO2/SiC Interface. J. Appl. Phys. 1996, 79, 3042–3045. [Google Scholar] [CrossRef]

- Baliga, B.J. Silicon Carbide Switching Device with Rectifying Gate. U.S. Patent 5 396 085, 7 March 1995. [Google Scholar]

- Zhang, Q.; Gomez, M.; Bui, C.; Hanna, E. 1600 V 4H-SiC UMOSFETs with Dual Buffer Layers. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs, Santa Barbara, CA, USA, 23–26 May 2005; pp. 211–214. [Google Scholar]

- Nakano, Y.; Nakamura, R.; Sakairi, H.; Mitani, S.; Nakamura, T. 690 V, 1.00 mΩ·cm2 4H-SiC Double-Trench MOSFETs. Mater. Sci. Forum 2012, 717–720, 1069–1072. [Google Scholar] [CrossRef]

- Orouji, A.A.; Jozi, M.; Fathipour, M. High-Voltage and Low Specific On-Resistance Power UMOSFET Using P and N Type Columns. Mater. Sci. Semicond. Process. 2015, 39, 711–720. [Google Scholar] [CrossRef]

- Saitoh, Y.; Hiyoshi, T.; Wada, K.; Masuda, T.; Tsuno, T. 4H-SiC V-Groove Trench MOSFETs with The Buried P+ Regions. Sei Tech. Rev. 2015, 80, 75–80. [Google Scholar]

- Peyvast, N.; Fathipour, M. A Novel 4H-SiC UMOSFET_ACCUFET with Large Blocking Voltage. In Proceedings of the 1st International Symposium on Quality Electronic Design, Barcelona, Spain, 14–18 June 2009; pp. 35–38. [Google Scholar]

- Wang, Y.; Tian, K.; Hao, Y.; Yu, C.H.; Liu, Y.J. 4H–SiC Step Trench Gate Power Metal–Oxide–Semiconductor Field-Effect Transistor. IEEE Electron. Device Lett. 2016, 37, 633–635. [Google Scholar] [CrossRef]

- Song, Q.; Yang, S.; Tang, G.N.; Han, C.; Zhang, Y.; Tang, X.; Zhang, Y. 4H-SiC Trench MOSFETs with L Shaped Gate. IEEE Electron. Device Lett. 2016, 37, 463–466. [Google Scholar] [CrossRef]

- Wei, J.; Zhang, M.; Jiang, H.; Cheng, C.-H.; Chen, K.J. Low ON-Resistance SiC Trench/Planar MOSFET With Reduced OFF-State Oxide Field and Low Gate Charges. IEEE Electron. Device Lett. 2016, 37, 1458–1461. [Google Scholar] [CrossRef]

- Zhang, M.; Wei, J.; Jiang, H.; Chen, K.J.; Cheng, C.H. A New SiC Trench MOSFET Structure With Protruded p-Base for Low Oxide Field and Enhanced Switching Performance. IEEE Trans. Device Mater. Reliab. 2017, 17, 432–437. [Google Scholar] [CrossRef]

- Zhou, X.T.; Yue, R.F.; Zhang, J.; Dai, G.; Li, J.; Wang, Y. 4H-SiC Trench MOSFET With Floating/Grounded Junction Barrier-controlled Gate Structure. IEEE Trans. Electron. Devices 2017, 64, 4568–4574. [Google Scholar] [CrossRef]

- Bharti, D.; Islam, A. Optimization of SiC UMOSFET Structure for Improvement of Breakdown Voltage and ON-Resistance. IEEE Trans. Electron. Devices 2018, 65, 615–621. [Google Scholar] [CrossRef]

- Yang, T.T.; Wang, Y.; Yue, R.F. SiC Trench MOSFET with Reduced Switching Loss and Increased Short-circuit Capability. IEEE Trans. Electron. Devices 2020, 67, 3685–3690. [Google Scholar] [CrossRef]

- Chung, G.Y.; Tin, C.C.; Williams, J.R.; McDonald, K.; Chanana, R.K.; Weller, R.A.; Palmour, J.W. Improved Inversion Channel Mobility for 4H-SiC MOSFETs Following High Temperature Anneals in Nitric Oxide. IEEE Electron. Device Lett. 2001, 22, 176–178. [Google Scholar] [CrossRef]

- Constant, A.; Camara, N.; Montserrat, J.; Pausas, E.; Camassel, J.; Godignon, P. Oxidation Process by RTP for 4H-SiC MOSFET Gate Fabrication. Mater. Sci. Forum 2011, 679–680, 500–503. [Google Scholar] [CrossRef]

- Chanthaphan, A.; Hosoi, T.; Shimura, T.; Watanabe, H. Study of SiO2/4H-SiC Interface Nitridation by Post-Oxidation Annealing in Pure Nitrogen Gas. Aip Adv. 2015, 111, 097134. [Google Scholar] [CrossRef]

- Dai, O.; Yano, H.; Hirata, K.; Hatayama, T.; Fuyuki, T. Improved Inversion Channel Mobility in 4H-SiC MOSFETs on Si Face Utilizing Phosphorus-Doped Gate Oxide. IEEE Electron. Device Lett. 2010, 31, 710–712. [Google Scholar]

- Sledziewski, T.; Weber, H.B.; Krieger, M. Passivation and Generation of States at P-Implanted Thermally Grown and Deposited N-Type 4H-SiC/SiO2 Interfaces. Mater. Sci. Forum 2016, 858, 697–700. [Google Scholar] [CrossRef]

- Dai, O.; Sometani, M.; Harada, S.; Kosugi, R.; Yonezawa, Y.; Yano, H. Improved Channel Mobility in 4H-SiC MOSFETs by Boron Passivation. IEEE Electron. Device Lett. 2014, 35, 1176–1178. [Google Scholar]

- Cabello, M.; Soler, V.; Montserrat, J.; Rebollo, J.; Rafí, J.M.; Godignon, P. Impact of Boron Diffusion on Oxynitrided Gate Oxides in 4H-SiC Metal-Oxide-Semiconductor Field-Effect Transistors. Appl. Phys. Lett. 2017, 111, 321–337. [Google Scholar] [CrossRef]

- Ryu, S.H.; Capell, C.; Cheng, L.; Jonas, C.; Gupta, A.; Donofrio, M.; Bhattacharya, S. High performance, ultra high voltage 4H-SiC IGBTs. In 2012 IEEE Energy Conversion Congress and Exposition (ECCE); IEEE: Raleigh, North Carolina, 2012; pp. 3603–3608. [Google Scholar]

- Usman, M.; Nawaz, M. Device design assessment of 4H–SiC n-IGBT—A simulation study. Solid-State Electron. 2014, 92, 5–11. [Google Scholar] [CrossRef]

- Muhammad, N.; Chimento, F. On the assessment of temperature dependence of 10–20 kV 4H-SiC IGBTs using TCAD. Mater. Sci. Forum 2013, 740–742, 1085–1088. [Google Scholar]

- Buono, B.; Ghandi, R.; Domeij, M.; Malm, B.G.; Zetterling, C.M.; Ostling, M. Modeling and characterization of current gain versus temperature in 4H-SiC power BJTs. IEEE Trans. Electron. Devices 2010, 57, 704–711. [Google Scholar] [CrossRef]

- Silvaco Int. Two-Dimensional Device Simulation Program; Silvaco Int.: Santa Clara, CA, USA, 2012. [Google Scholar]

- Namai, M.; An, J.; Yano, H.; Iwamuro, N. Experimental and Numerical Demonstration and Optimized Methods for SiC Trench MOSFET Short-Circuit Capability. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; Volume 3, pp. 7–10. [Google Scholar]

- Tanaka, R.; Kagawa, Y.; Fujiwara, N.; Sugawara, K.; Fukui, Y.; Miura, N.; Yamakawa, S. Impact of Grounding the Bottom Oxide Protection Layer on The Short-Circuit Ruggedness of 4H-SiC Trench MOSFETs. In Proceedings of the 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 75–78. [Google Scholar]

| Parameters | C-UMOS | BSJ-UMOS |

|---|---|---|

| Concentration of n+/p+ region (cm−3) | 1.0 × 10 19 | 1.0 × 10 19 |

| Concentration of p-body region (cm−3) | 1.0 × 10 17 | 1.0 × 10 17 |

| Thickness of p-body region (μm) | 0.6 | 0.6 |

| Width of trench gate (μm) | 1.0 | 1.0 |

| Depth of trench gate (μm) | 2.5 | 2.5 |

| Concentration of P+ shielding region (cm−3) | 1.0 × 10 18 | 1.0 × 10 18 |

| Concentration of N-drift region (cm−3) | 4.0 × 10 15 | 4.0 × 10 15 |

| Thickness of N-drift region (μm) | 11.2 | 8.2 |

| Concentration of p-pillar (cm−3) | - | 5 × 10 16 |

| Thickness of p-pillar region (μm) | - | 3 |

| Width of p-pillar region (μm) | - | 1 |

| Concentration of n-pillar region (cm−3) | - | 1 × 10 16 |

| Thickness of n-pillar region (μm) | - | 3 |

| Width of n-pillar region (μm) | - | 2 |

| Concentration of n+ substrate region (cm−3) | 1 × 10 19 | 1 × 10 19 |

| Width of a half cell (μm) | 3 | 3 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, L.; Liu, Y.; Fang, J.; Liu, Y. Investigation of a 4H-SiC Trench MOSFET with Back-Side Super Junction. Micromachines 2022, 13, 1770. https://doi.org/10.3390/mi13101770

Zhang L, Liu Y, Fang J, Liu Y. Investigation of a 4H-SiC Trench MOSFET with Back-Side Super Junction. Micromachines. 2022; 13(10):1770. https://doi.org/10.3390/mi13101770

Chicago/Turabian StyleZhang, Lili, Yuxuan Liu, Junpeng Fang, and Yanjuan Liu. 2022. "Investigation of a 4H-SiC Trench MOSFET with Back-Side Super Junction" Micromachines 13, no. 10: 1770. https://doi.org/10.3390/mi13101770

APA StyleZhang, L., Liu, Y., Fang, J., & Liu, Y. (2022). Investigation of a 4H-SiC Trench MOSFET with Back-Side Super Junction. Micromachines, 13(10), 1770. https://doi.org/10.3390/mi13101770