Buffer Traps Effect on GaN-on-Si High-Electron-Mobility Transistor at Different Substrate Voltages

Abstract

:1. Introduction

2. Materials and Methods

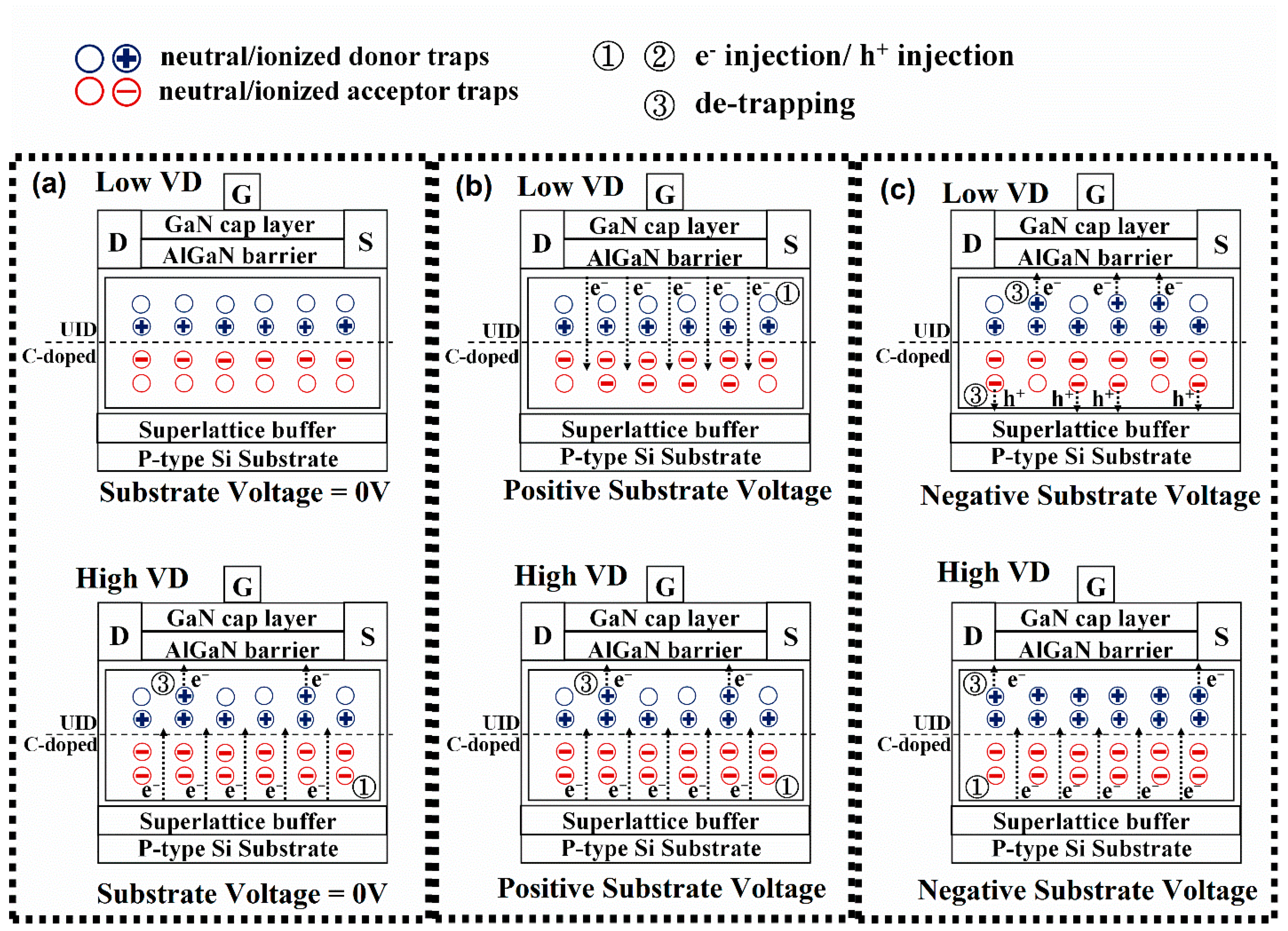

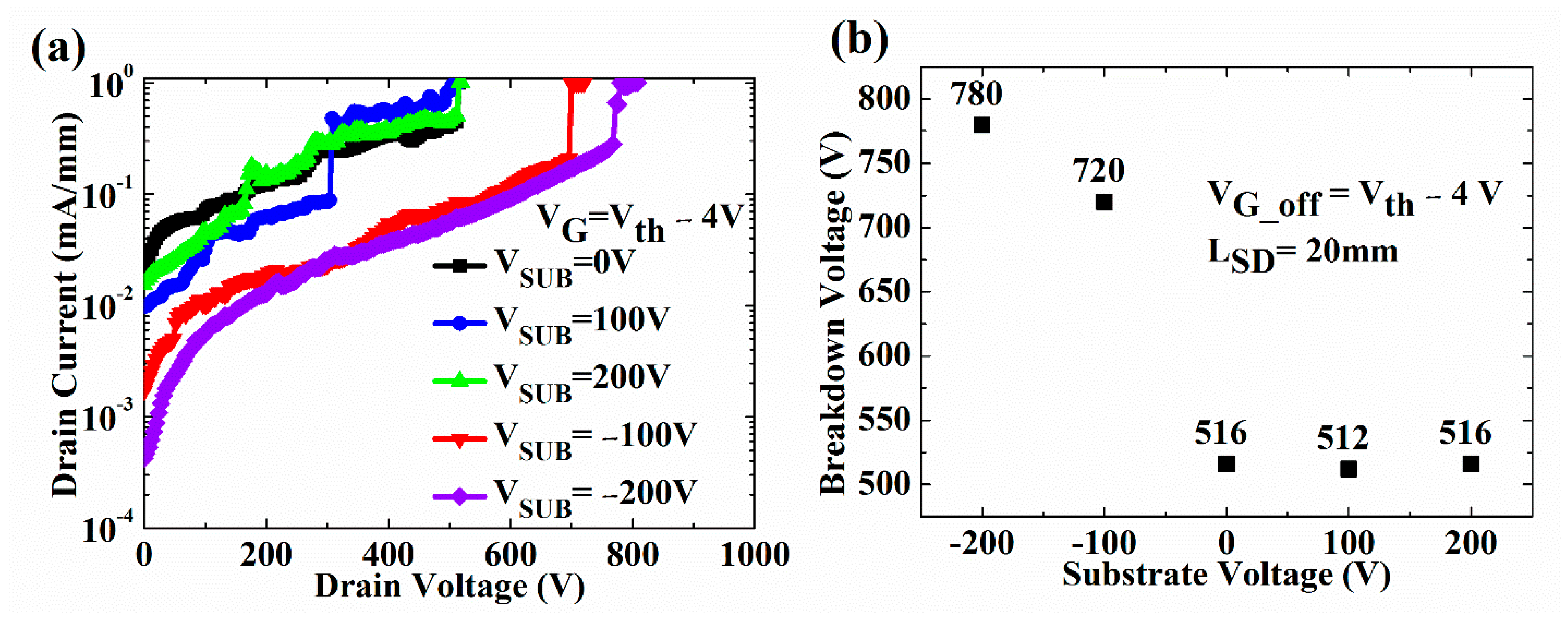

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Amano, H.; Baines, Y.; Beam, E.; Borga, M.; Bouchet, T.; Chalker, R.P.; Charles, M.; Chen, K.J.; Chowdhury, N.; Chu, R.; et al. The 2018 GaN power electronics roadmap. J. Phys. D 2018, 51, 163001. [Google Scholar] [CrossRef]

- Chen, J.K.; Häberlen, O.; Lidow, A.; Tsai, C.L.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si Power Technology: Devices and Applications. IEEE Trans. Electron Devices 2017, 64, 779–795. [Google Scholar] [CrossRef]

- Zhou, C.D.; Li, W.; Shen, J.; Chen, L.; Zhao, T.; Lin, K.; Zhang, M.; Chen, L.; Chiu, H.C.; Zhang, J.; et al. Reliability of 200 mm E-mode GaN-on-Si Power HEMTs. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020. [Google Scholar]

- Yang, S.; Han, S.; Wei, J.; Sheng, K.; Chen, K.J. Impact of substrate bias polarity on buffer-related current collapse in AlGaN/GaN-on-Si power devices. IEEE Trans. Electron Devices 2017, 64, 5048–5056. [Google Scholar] [CrossRef]

- Marchand, H.; Zhao, L.; Zhang, N.; Moran, B.; Coffie, R.; Mishra, U.K.; Speck, J.S.; DenBaars, S.P. Metal organic chemical vapor deposition of GaN on Si(111): Stress control and application to field-effect transistors. J. Appl. Phys. 2001, 89, 7846. [Google Scholar] [CrossRef]

- Yang, S.; Han, S.; Sheng, K.; Chen, K.J. Dynamic on-resistance in GaN power devices: Mechanisms, characterizations, and modeling. IEEE J. Emerg. Sel. Top. Power Electron 2019, 7, 1425–1439. [Google Scholar] [CrossRef]

- Yang, S.; Jiang, Q.; Li, B.; Tang, Z.; Chen, K.J. GaN-to-Si vertical conduction mechanisms in AlGaN/GaN-on-Si lateral heterojunction FET structures. Phys. Status Solidi C 2014, 11, 949–952. [Google Scholar] [CrossRef]

- Moens, P.; Banerjee, A.; Uren, M.J.; Meneghini, M.; Karboyan, S.; Chatterjee, I.; Vanmeerbeek, P.; Cäsar, M.; Liu, C.; Salih, A.; et al. Impact of buffer leakage on intrinsic reliability of 650v AlGaN/GaN HEMTs. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015. [Google Scholar]

- Miller, E.J.; Yu, E.T.; Waltereit, P.; Speck, J.S. Analysis of reverse-bias leakage current mechanisms in GaN grown by molecular beam epitaxy. Appl. Phys. Lett. 2004, 84, 535–537. [Google Scholar] [CrossRef] [Green Version]

- Zagni, N.; Chini, A.; Puglisi, F.M.; Pavan, P.; Verzellesi, G. On the modeling of the donor/acceptor compensation ratio in carbon-doped GaN to univocally reproduce breakdown voltage and current collapse in lateral GaN power HEMTs. Micromachines 2021, 12, 709. [Google Scholar] [CrossRef]

- Matsubara, M.; Bellotti, E. A first-principles study of carbon-related energy levels in GaN. I. Complexes formed by substitutional interstitial carbons and gallium nitrogen vacancies. J. Appl. Phys. 2017, 121, 195701. [Google Scholar] [CrossRef] [Green Version]

- Lyons, J.L.; Wickramaratne, D.; Walle, C.G.V.D. A first-principles understanding of point defects and impurities in GaN. J. Appl. Phys. 2021, 129, 111101. [Google Scholar] [CrossRef]

- Remesh, N.; Mohan, N.; Raghavan, S.; Muralidharan, R.; Nath, D.N. Optimum carbon concentration in GaN-on-Silicon for breakdown enhancement in AlGaN/GaN HEMTs. IEEE Trans. Electron Devices 2020, 67, 2311–2317. [Google Scholar] [CrossRef]

- Joshi, V.; Tiwari, S.P.; Shrivastava, M. Part I: Physical insight into carbon-doping-induced delayed avalanche action in GaN buffer in AlGaN/GaN HEMTs. IEEE Trans. Electron Devices 2019, 66, 561–569. [Google Scholar]

- Uren, J.M.; Karboyan, S.; Chatterjee, I.; Pooth, A.; Moens, P.; Banerjee, A.; Kuball, M. “Leaky Dielectric” Model for the Suppression of Dynamic RON in Carbon-Doped AlGaN/GaN HEMTs. IEEE Trans. Electron Devices 2017, 64, 2826–2834. [Google Scholar]

- Yang, W.; Yuan, J.S.; Krishnan, B.; Shea, P. Low-side GaN power device dynamic Ron characteristics under different substrate biases. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 31 March–4 April 2021. [Google Scholar]

- Chiu, H.-C.; Peng, L.Y.; Yang, C.W.; Wang, H.C.; Hsin, Y.M.; Chyi, J.I. Analysis of the back-gate effect in normally off p-GaN gate high-electron mobility transistor. IEEE Trans. Electron Devices 2015, 62, 507–511. [Google Scholar] [CrossRef]

- Mahaboob, I.; Yakimov, M.; Hogan, K.; Rocco, E.; Tozier, S.; Shahedipour-Sandvik, F. Dynamic control of AlGaN/GaN HEMT 18 characteristics by implementation of a p-GaN body-diode-based back-gate. IEEE J. Electron Devices Soc. 2019, 7, 581–588. [Google Scholar] [CrossRef]

- Moench, S.; Müller, S.; Reiner, R.; Waltereit, P.; Czap, H.; Basler, M.; Hückelheim, J.; Kirste, L.; Kallfass, I.; Quay, R.; et al. Monolithic integrated AlGaN/GaN power converter topologies on high-voltage AlN/GaN superlattice buffer. Phys. Status Solidi 2020, 218, 2000404. [Google Scholar] [CrossRef]

- He, X.; Feng, Y.; Yang, X.; Wu, S.; Cai, Z.; Wei, J.; Shen, J.; Huang, H.; Liu, D.; Chen, Z.; et al. Step-graded AlGaN vs superlattice: Role of strain relief layer in dynamic on-resistance degradation. Appl. Phys. Express 2020, 15, 011001. [Google Scholar] [CrossRef]

- Yang, W.; Yuan, J.S. Experimental investigation of buffer traps physical mechanisms on the gate charge of GaN-on-Si devices under various substrate biases. Appl. Phys. Lett. 2020, 116, 083501. [Google Scholar] [CrossRef]

- Zhuang, J.; Zulauf, G.; Rivas-Davila, J. Substrate bias effect on e-mode GaN-on-Si HEMT coss losses. In Proceedings of the IEEE 6th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Atlanta, GA, USA, 31 October–2 November 2018. [Google Scholar]

- Tang, G.; Wei, J.; Zhang, Z.; Tang, X.; Hua, M.; Wang, H.; Chen, K.J. Dynamic Ron of GaN-on-Si lateral power devices with a floating substrate termination. IEEE Electron Device Lett. 2017, 38, 937–940. [Google Scholar] [CrossRef]

- Zhou, C.; Jiang, Q.; Huang, S.; Chen, J.K. Vertical Leakage/Breakdown Mechanisms in AlGaN/GaN-on-Si Devices. IEEE Electron Device Lett. 2012, 33, 1132–1134. [Google Scholar] [CrossRef]

- Zhou, C.; Jiang, Q.; Huang, S.; Chen, K.J. Vertical Leakage/Breakdown Mechanisms in AlGaN/GaN-on-Si Structures. In Proceedings of the 24th International Symposium on Power Semiconductor Devices and ICs (24th ISPSD), Bruges, Belgium, 3–7 June 2012. [Google Scholar]

- Chatterjee, I.; Uren, J.M.; Karboyan, S.; Pooth, A.; Moens, P.; Banerjee, A.; Kuball, M. Lateral charge transport in the carbon-doped buffer in AlGaN/GaN-on-Si HEMTs. IEEE Trans. Electron Devices 2017, 64, 977–983. [Google Scholar] [CrossRef] [Green Version]

- Zhang, H.; Kang, X.; Jin, Z.; Zheng, Y.; Wu, H.; Wei, K.; Liu, X.; Ye, T. Investigation on Dynamic Characteristics of AlGaN/GaN Lateral Schottky Barrier Diode. Micromachines 2021, 12, 1296. [Google Scholar] [CrossRef] [PubMed]

- Joh, J.; Alamo, J.A.D. A Current-Transient Methodology for Trap Analysis for GaN High Electron Mobility Transistors. IEEE Trans. Electron Devices 2011, 58, 132–140. [Google Scholar] [CrossRef]

| Substrate Voltage (V) | On/Off ID Ratio | S.S (mV/dec) | Vth (V) | Ron (Ω•mm) | gm (mS/mm) | ID,max (mA/mm) | Off-State ID (mA/mm) |

|---|---|---|---|---|---|---|---|

| −200 | 1.16 × 106 | 155 | −9.59 | 9.45 | 87.5 | 608 | 5.24 × 10−4 |

| −100 | 4.79 × 105 | 180 | −10.59 | 9.39 | 82 | 644 | 1.34 × 10−3 |

| 0 | 2.16 × 105 | 202 | −11.76 | 9.28 | 80.4 | 696 | 3.22 × 10−3 |

| 100 | 2.91 × 105 | 203 | −11.8 | 9.21 | 81.5 | 702 | 2.41 × 10−3 |

| 200 | 3.05 × 105 | 201 | −11.78 | 9.16 | 81.7 | 701 | 2.3 × 10−3 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lin, Y.; Kao, M.-L.; Weng, Y.-C.; Dee, C.-F.; Chen, S.-C.; Kuo, H.-C.; Lin, C.-H.; Chang, E.-Y. Buffer Traps Effect on GaN-on-Si High-Electron-Mobility Transistor at Different Substrate Voltages. Micromachines 2022, 13, 2140. https://doi.org/10.3390/mi13122140

Lin Y, Kao M-L, Weng Y-C, Dee C-F, Chen S-C, Kuo H-C, Lin C-H, Chang E-Y. Buffer Traps Effect on GaN-on-Si High-Electron-Mobility Transistor at Different Substrate Voltages. Micromachines. 2022; 13(12):2140. https://doi.org/10.3390/mi13122140

Chicago/Turabian StyleLin, Yuan, Min-Lu Kao, You-Chen Weng, Chang-Fu Dee, Shih-Chen Chen, Hao-Chung Kuo, Chun-Hsiung Lin, and Edward-Yi Chang. 2022. "Buffer Traps Effect on GaN-on-Si High-Electron-Mobility Transistor at Different Substrate Voltages" Micromachines 13, no. 12: 2140. https://doi.org/10.3390/mi13122140

APA StyleLin, Y., Kao, M.-L., Weng, Y.-C., Dee, C.-F., Chen, S.-C., Kuo, H.-C., Lin, C.-H., & Chang, E.-Y. (2022). Buffer Traps Effect on GaN-on-Si High-Electron-Mobility Transistor at Different Substrate Voltages. Micromachines, 13(12), 2140. https://doi.org/10.3390/mi13122140