Optimization of Feedback FET with Asymmetric Source Drain Doping Profile

Abstract

:1. Introduction

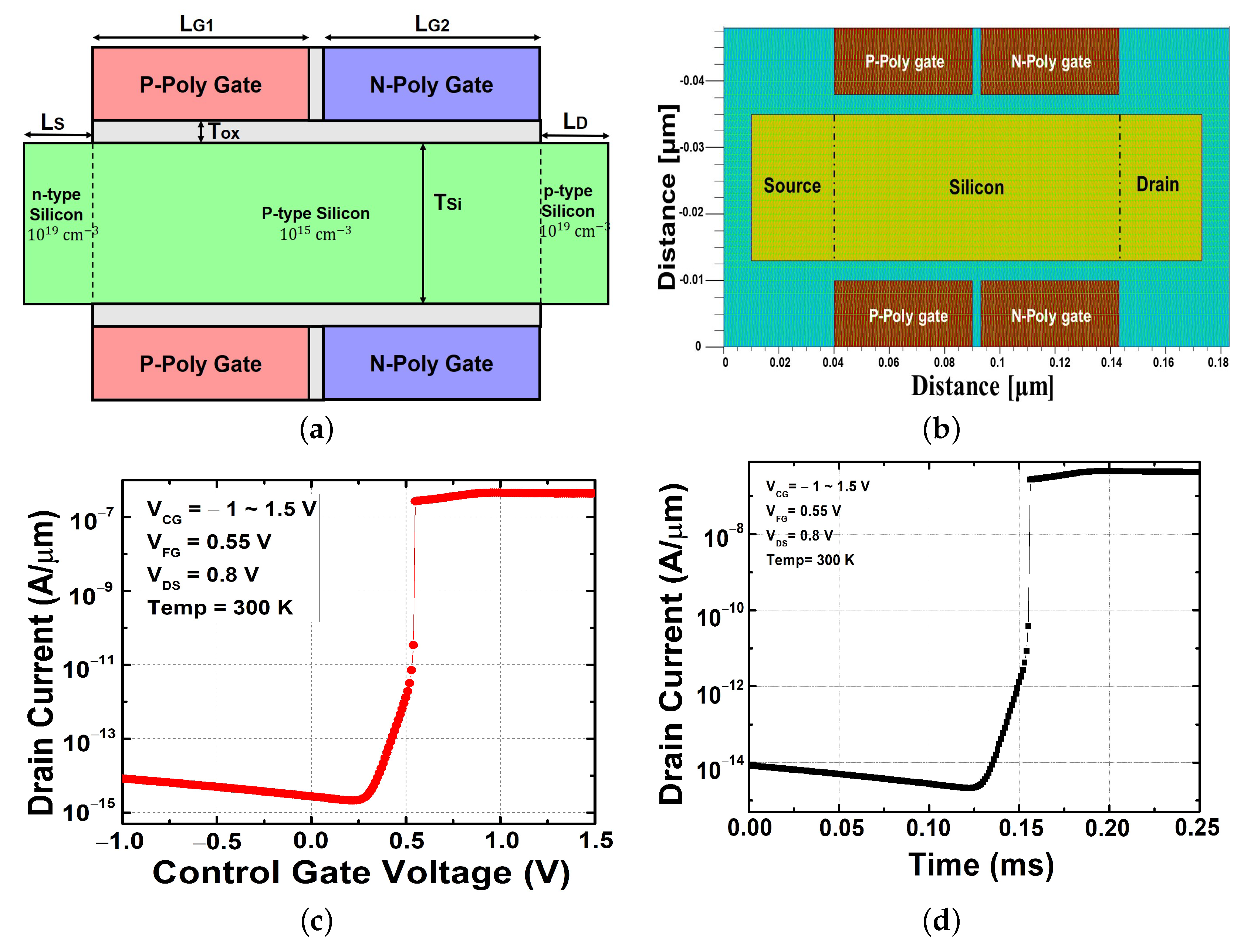

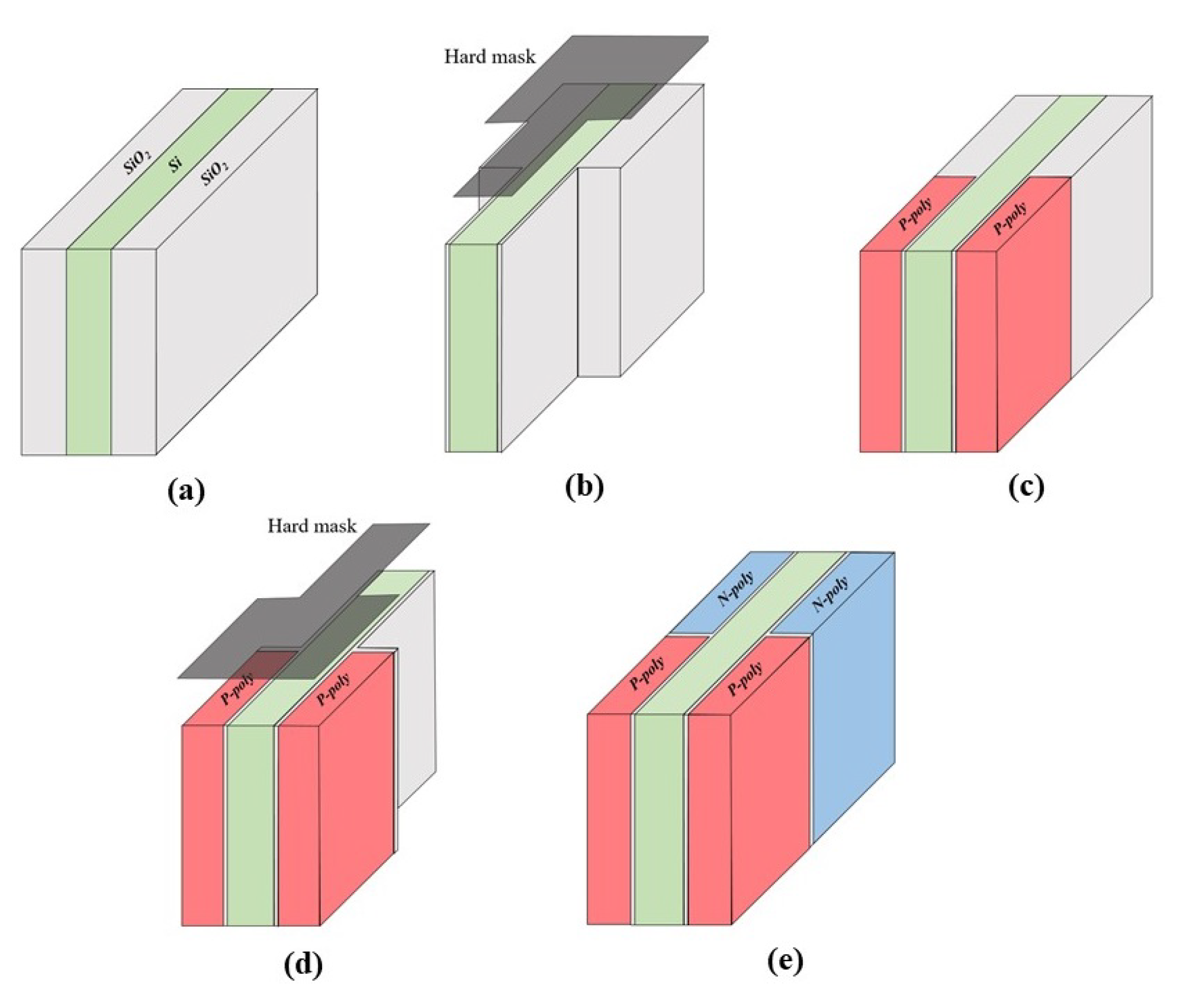

2. Device Structure and Methods

3. Results and Discussion

3.1. Simulation Conditions

3.2. Doping Variation

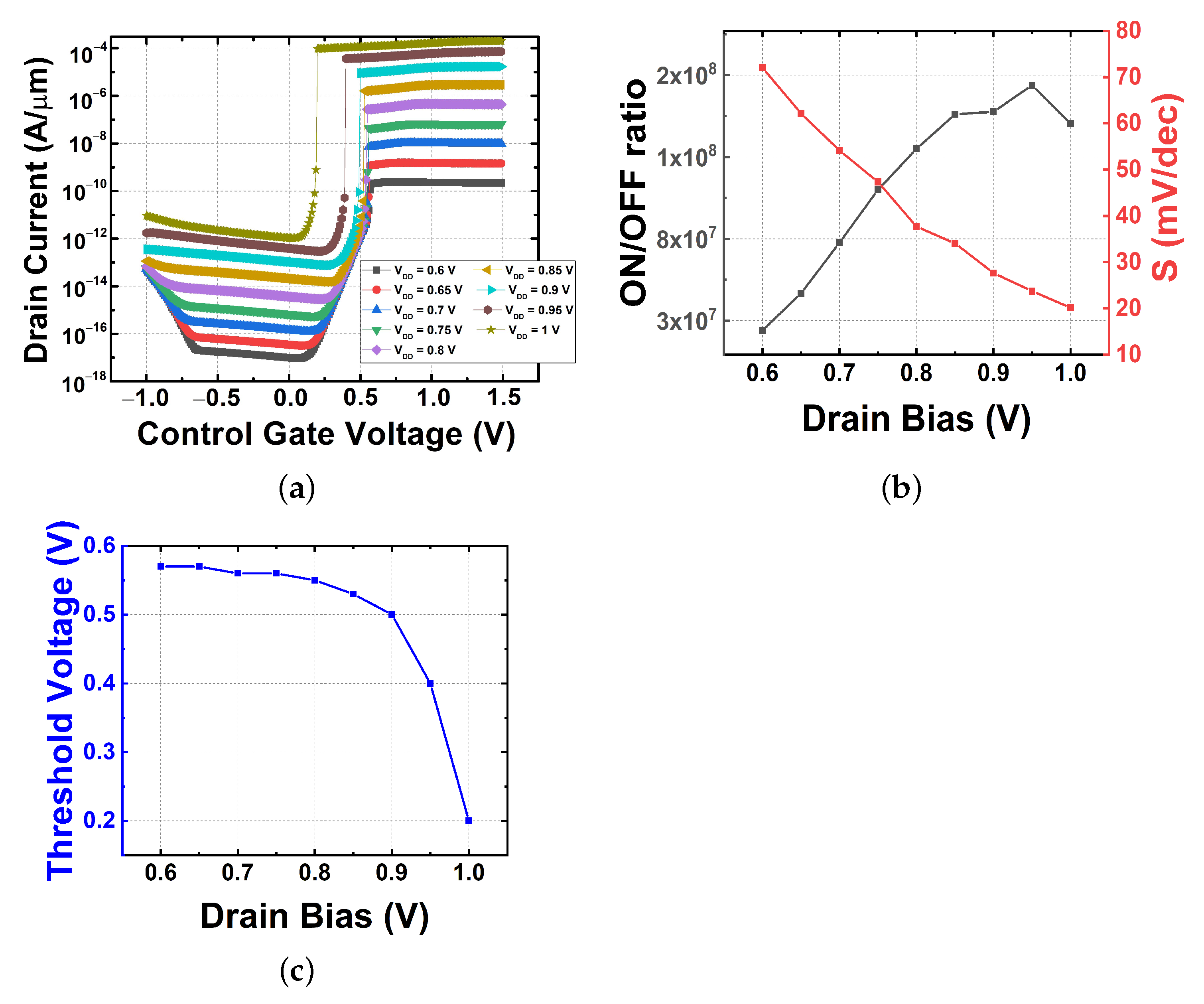

3.2.1. Source and Drain Doping Variation

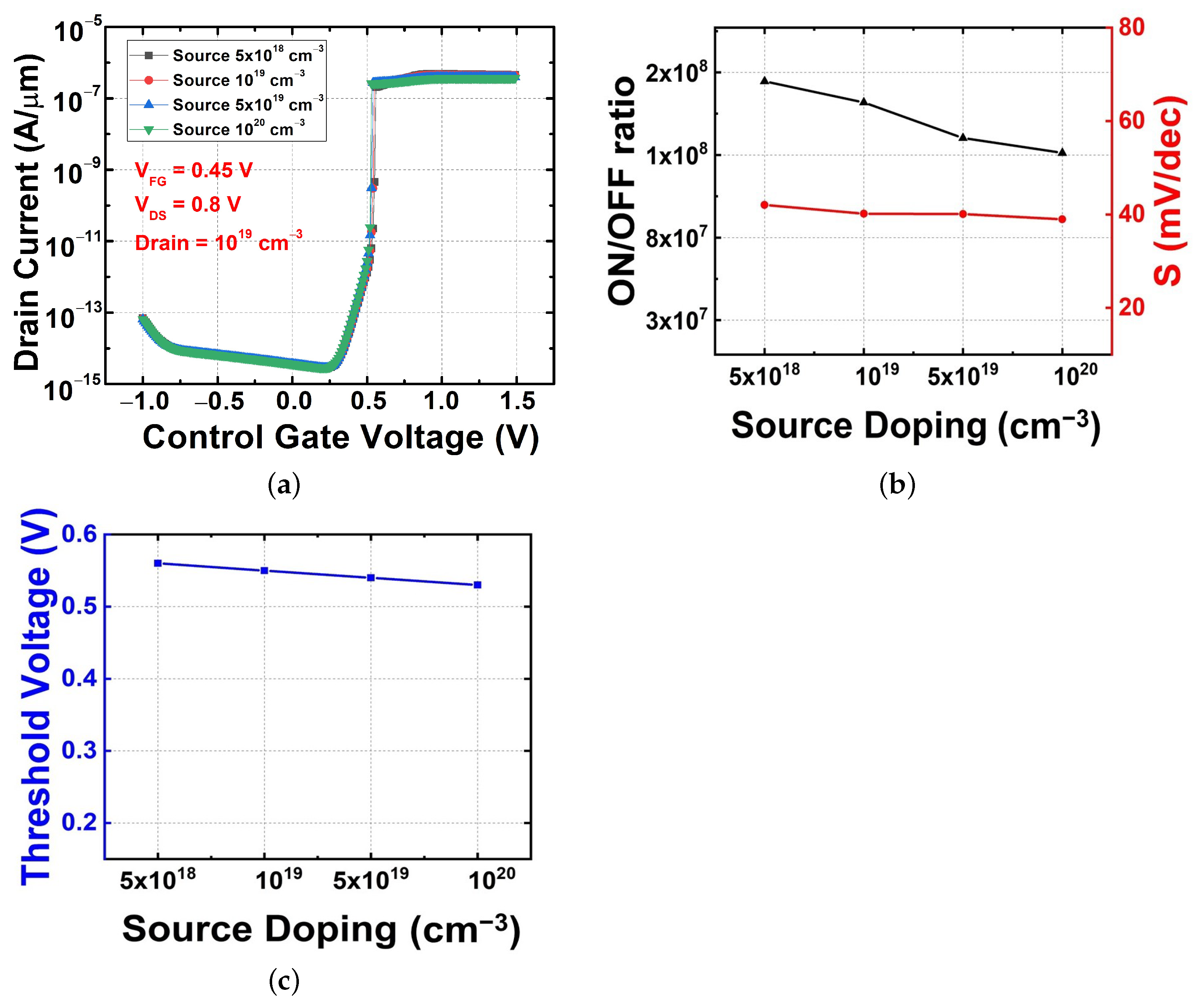

3.2.2. Source Doping Variation with Fixed Drain Doping

3.2.3. Drain Doping Variation with Fixed Source Doping

3.3. Dimensional Feature Variation

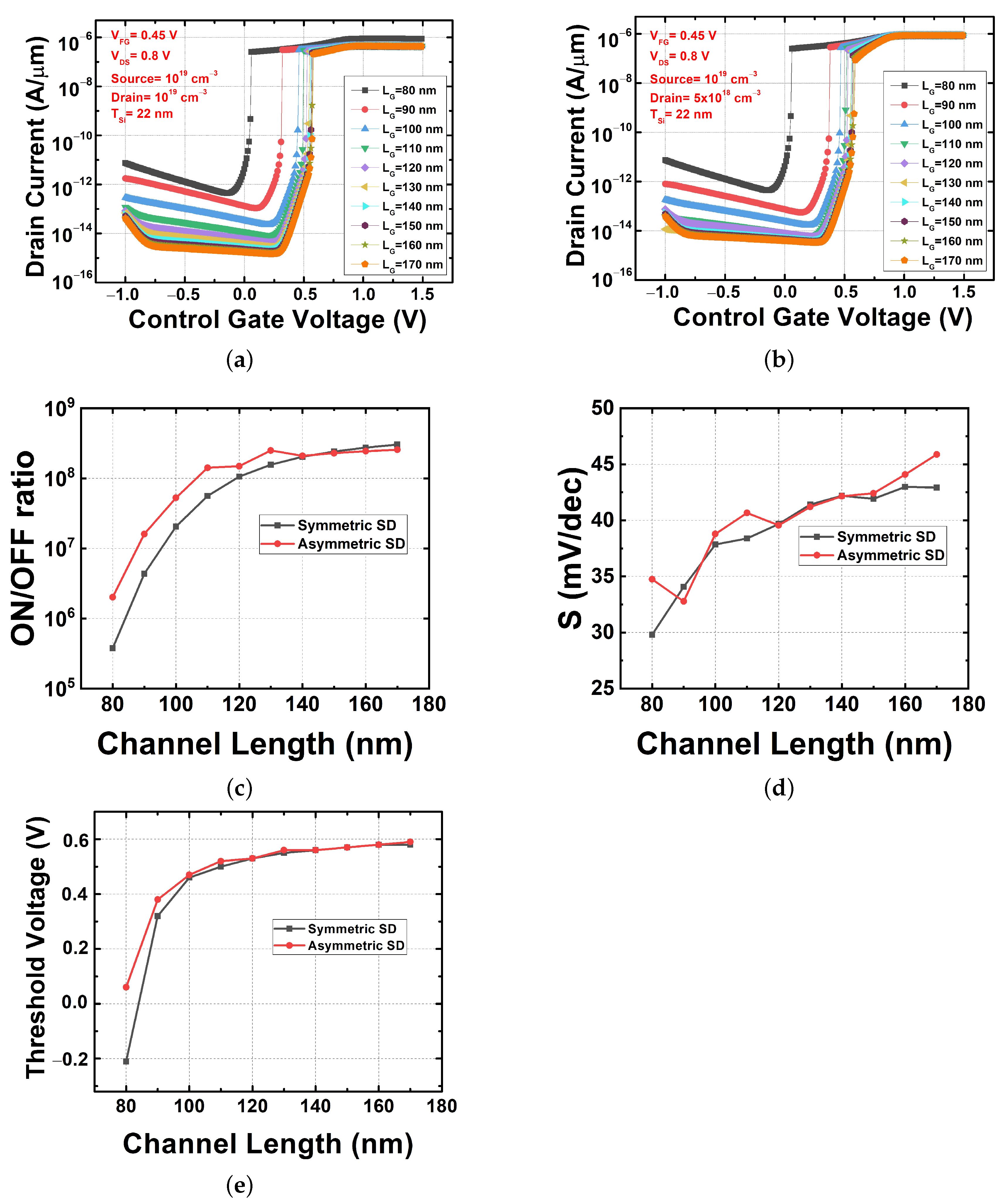

3.3.1. Channel Length Variation

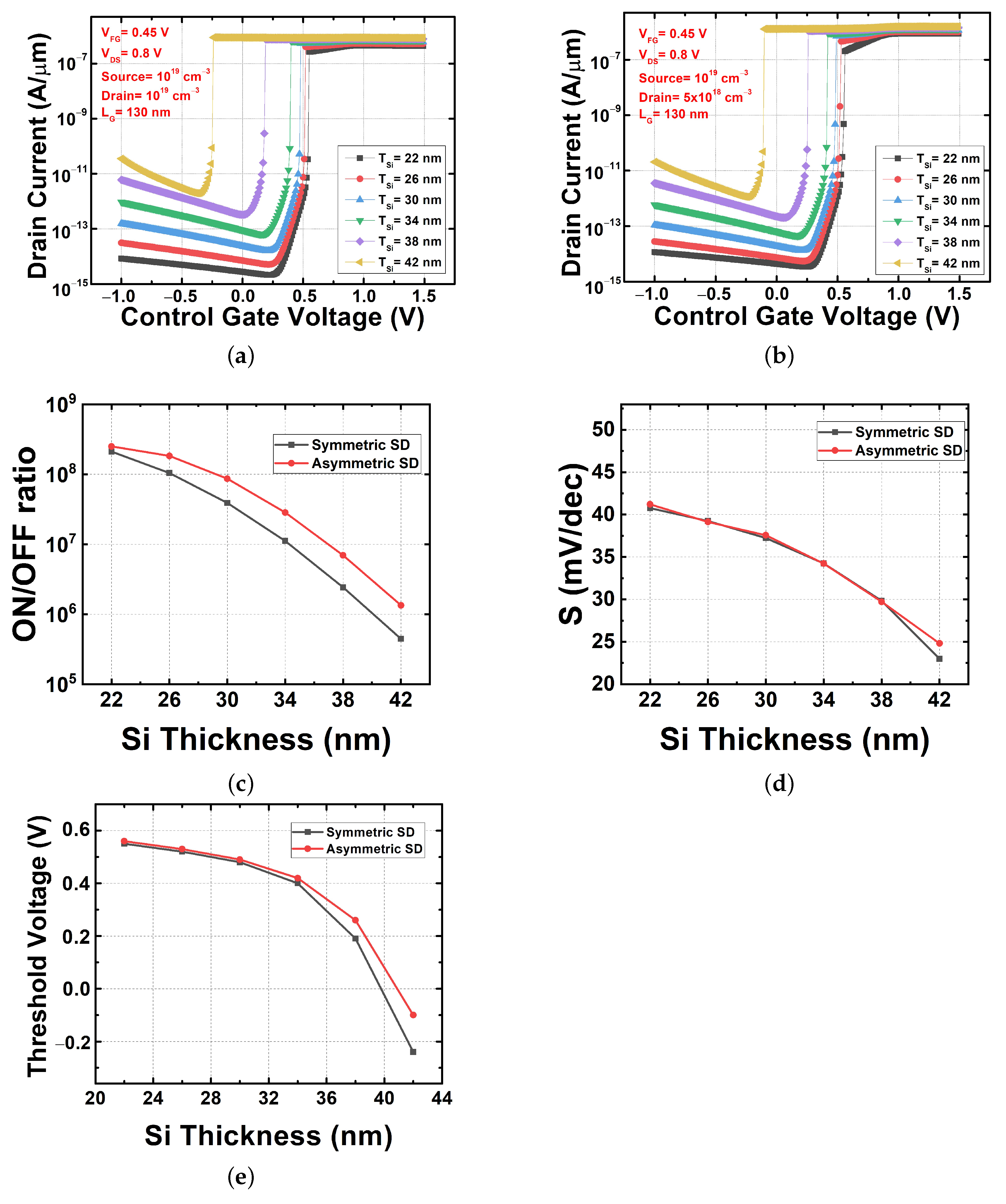

3.3.2. Channel Thickness Variation

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Thompson, S.; Parthasarathy, S. Moore’s law: The future of Si microelectronics. Mater. Today 2006, 9, 20–25. [Google Scholar] [CrossRef]

- Takayasu, S.; Shin, C. Perspectives of low-power VLSI’s. IEICE Trans. Electron. 2004, 87, 429–436. [Google Scholar]

- Jo, J. Study of Temperature Effects on Negative Capacitance Field-Effect Transistor. IEEK 2014, 37, 70–72. [Google Scholar]

- Jo, J. Fifty Years of Moore’s Law. IEEE Trans. Semicond. Manuf. 2011, 24, 202–207. [Google Scholar]

- Palestri, P.; Eminente, S.; Esseni, D.; Fiegna, C.; Sangiorgi, E.; Selmi, L. An improved semi-classical Monte-Carlo approach fornano-scale MOSFET simulation. IEEE Trans. Solid-State Electron. 2005, 49, 727–732. [Google Scholar] [CrossRef]

- Borkar, S. Design perspectives on 22 nm cmos and beyond. In Proceedings of the 46th Annual Design Automation Conference, San Francisco, CA, USA, 26 July 2009; pp. 93–94. [Google Scholar]

- Borkar, S. Electronics beyond nano-scale CMOS. In Proceedings of the 46rd Annual Design Automation Conference, San Francisco, CA, USA, 24 July 2006; pp. 807–808. [Google Scholar]

- Cristoloveanu, S.; Wan, J.; Zaslavsky, A. A review of sharp-switching devices for ultra-low power applications. IEEE J. Electron. Devices Soc. 2016, 4, 215–226. [Google Scholar] [CrossRef]

- Cristoloveanu, S.; Wan, J.; le Royer, C.; Zaslavsky, A. (Invited) Innovative Sharp Switching Devices. IEEE Trans. Semicond. Manuf. 2013, 54, 65–75. [Google Scholar] [CrossRef]

- El Dirani, H.; Fonteneau, P.; Solaro, Y.; Legrand, C.A.; Marin-Cudraz, D.; Ferrari, P.; Cristoloveanu, S. Sharp-switchingband-modulation back-gated devices in advanced FDSOI technology. Solid-State Electron. 2017, 128, 180–186. [Google Scholar] [CrossRef]

- Wan, J.; Le Royer, C.; Zaslavsky, A.; Cristoloveanu, S. A systematic study of the sharp-switching Z2-FET device: From mechanismto modeling and compact memory applica-tions. Solid-State Electron. 2013, 90, 2–11. [Google Scholar] [CrossRef]

- Ko, E.; Shin, J.; Shin, C. Steep switching devices for low power applications: Negative differential capacitance/resistance field effect transistors. Nano Converg. 2018, 5, 1–9. [Google Scholar] [CrossRef] [Green Version]

- Nayfeh, O.M.; Chleirigh, C.N.; Hennessy, J.; Gomez, L.; Hoyt, J.L.; Antoniadis, D.A. Design of tunneling field-effect transistors using strained-silicon/strained-germanium type-II staggered heterojunctions. IEEE Electron Device Lett. 2008, 29, 1074–1077. [Google Scholar] [CrossRef]

- Choi, W.Y.; Park, B.-G.; Lee, J.D.; Liu, T.-J.K. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 2007, 28, 743–745. [Google Scholar] [CrossRef]

- Björk, M.T.; Hayden, O.; Schmid, H.; Riel, H.; Riess, W. Vertical surround-gated silicon nanowire impact ionization field-effect transistors. Appl. Phys. Lett. 2007, 90, 142110. [Google Scholar] [CrossRef]

- Gopalakrishnan, K.; Griffin, P.B.; Plummer, J.D. Impact ionization MOS (I-MOS)-Part I: Device and circuit simulations. IEEE Trans. Electron. Devices 2004, 52, 69–76. [Google Scholar] [CrossRef] [Green Version]

- Gopalakrishnan, K.; Griffin, P.B.; Plummer, J.D. I-MOS: A novel semiconductor device with a subthreshold slope lower than kT/q. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 8–11 December 2002; pp. 289–292. [Google Scholar]

- Jo, J.; Choi, W.Y.; Park, J.D.; Shim, J.W.; Yu, H.Y.; Shin, C. Negative capacitance in organic/ferroelectric capacitor to implement steep switching MOS devices. Nano Lett. 2015, 15, 4553–4556. [Google Scholar] [CrossRef]

- Khan, A.I.; Chatterjee, K.; Wang, B.; Drapcho, S.; You, L.; Serrao, C.; Bakaul, S.R.; Ramesh, R.; Salahuddin, S. Negative capacitance in a ferroelectric capacitor. Nat. Mater. 2015, 14, 182–186. [Google Scholar] [CrossRef]

- Ko, E.; Lee, J.W.; Shin, C. Negative Capacitance FinFET with Sub-20-mV/decade Subthreshold Slope and Minimal Hysteresis of 0.48 V. IEEE Electron Device Lett. 2017, 38, 418–421. [Google Scholar] [CrossRef]

- Kim, M.; Lee, K.; Kim, S. A review of feedback field-effect transistors: Operation mechanism and their applications. IKEEE 2018, 22, 499–505. [Google Scholar]

- Kim, M.; Kim, Y.; Lim, D.; Woo, S.; Cho, K.; Kim, S. Steep switching characteristics of single-gated feedback field-effect transistors. Nat. Nanotechnol. 2016, 28, 055205. [Google Scholar] [CrossRef]

- Lee, C.; Shin, C. Study on Various Device Structures for Steep-Switching Silicon-on-Insulator Feedback Field-Effect Transistors. IEEE Trans. Electron Devices 2020, 67, 1852–1858. [Google Scholar] [CrossRef]

- Hwang, S.; Kim, H.; Kwon, D.W.; Lee, J.H.; Park, B.G. Si1–xGex Positive Feedback Field-effect Transistor with Steep Subthreshold Swing for Low-voltage Operation. JSTS 2017, 17, 216–222. [Google Scholar]

- Wan, J.; Cristoloveanu, S.; Le Royer, C.; Zaslavsky, A. A feedback silicon-on-insulator steep switching device with gate-controlled carrier injection. Solid-State Electron. 2012, 76, 109–111. [Google Scholar] [CrossRef]

- Woo, S.Y.; Kang, W.M.; Choi, K.B.; Kim, J.; Kim, C.H.; Bae, J.H.; Park, B.G.; Lee, J.H. Analyzation of Positive Feed-back device with Steep Subthreshold Swing Characteristics in 14 nm FinFET Technology. In Proceedings of the Electron Devices Technology and Manufacturing Conference (EDTM), Singapore, 12–15 March 2019; pp. 404–406. [Google Scholar]

- Lee, C.; Ko, E.; Shin, C. Steep slope silicon-on-insulator feedback field-effect transistor: Design and performance analysis. IEEE Trans. Electron Devices 2018, 66, 286–291. [Google Scholar] [CrossRef]

- Wu, C.; Huang, Q.; Zhao, Y.; Wang, J.; Wang, Y.; Huang, R. A Novel Tunnel FET Design With Stacked Source Configuration for Average Subthreshold Swing Reduction. IEEE Trans. Electron Devices 2016, 63, 5072–5076. [Google Scholar] [CrossRef]

- Kam, H.; Liu, T.K.; Alon, E. Design Requirements for Steeply Switching Logic Devices. IEEE Trans. Electron Devices 2012, 59, 326–334. [Google Scholar] [CrossRef]

| Parameter | Value [unit] |

|---|---|

| Channel length (L) | 130 [nm] |

| Silicon channel thickness (T) | 22 [nm] |

| Poly-silicon gate thickness (T) | 130 [nm] |

| Control gate/fixed gate length (L/L) | 63.5 [nm] |

| Gate dielectric thickness (T) | 3 [nm] |

| Source/drain length (L/L) | 10 [nm] |

| Source/drain doping concentration | 1 × 10 [cm] |

| Channel doping concentration | 1 × 10 [cm] |

| Control gate/fixed gate doping concentration | 1 × 10 [cm] |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, I.; Park, H.; Nguyen, Q.T.; Kim, G.; Cho, S.; Cho, I. Optimization of Feedback FET with Asymmetric Source Drain Doping Profile. Micromachines 2022, 13, 508. https://doi.org/10.3390/mi13040508

Lee I, Park H, Nguyen QT, Kim G, Cho S, Cho I. Optimization of Feedback FET with Asymmetric Source Drain Doping Profile. Micromachines. 2022; 13(4):508. https://doi.org/10.3390/mi13040508

Chicago/Turabian StyleLee, Inyoung, Hyojin Park, Quan The Nguyen, Garam Kim, Seongjae Cho, and Ilhwan Cho. 2022. "Optimization of Feedback FET with Asymmetric Source Drain Doping Profile" Micromachines 13, no. 4: 508. https://doi.org/10.3390/mi13040508

APA StyleLee, I., Park, H., Nguyen, Q. T., Kim, G., Cho, S., & Cho, I. (2022). Optimization of Feedback FET with Asymmetric Source Drain Doping Profile. Micromachines, 13(4), 508. https://doi.org/10.3390/mi13040508