On-State Current Degradation Owing to Displacement Defect by Terrestrial Cosmic Rays in Nanosheet FET

Abstract

:1. Introduction

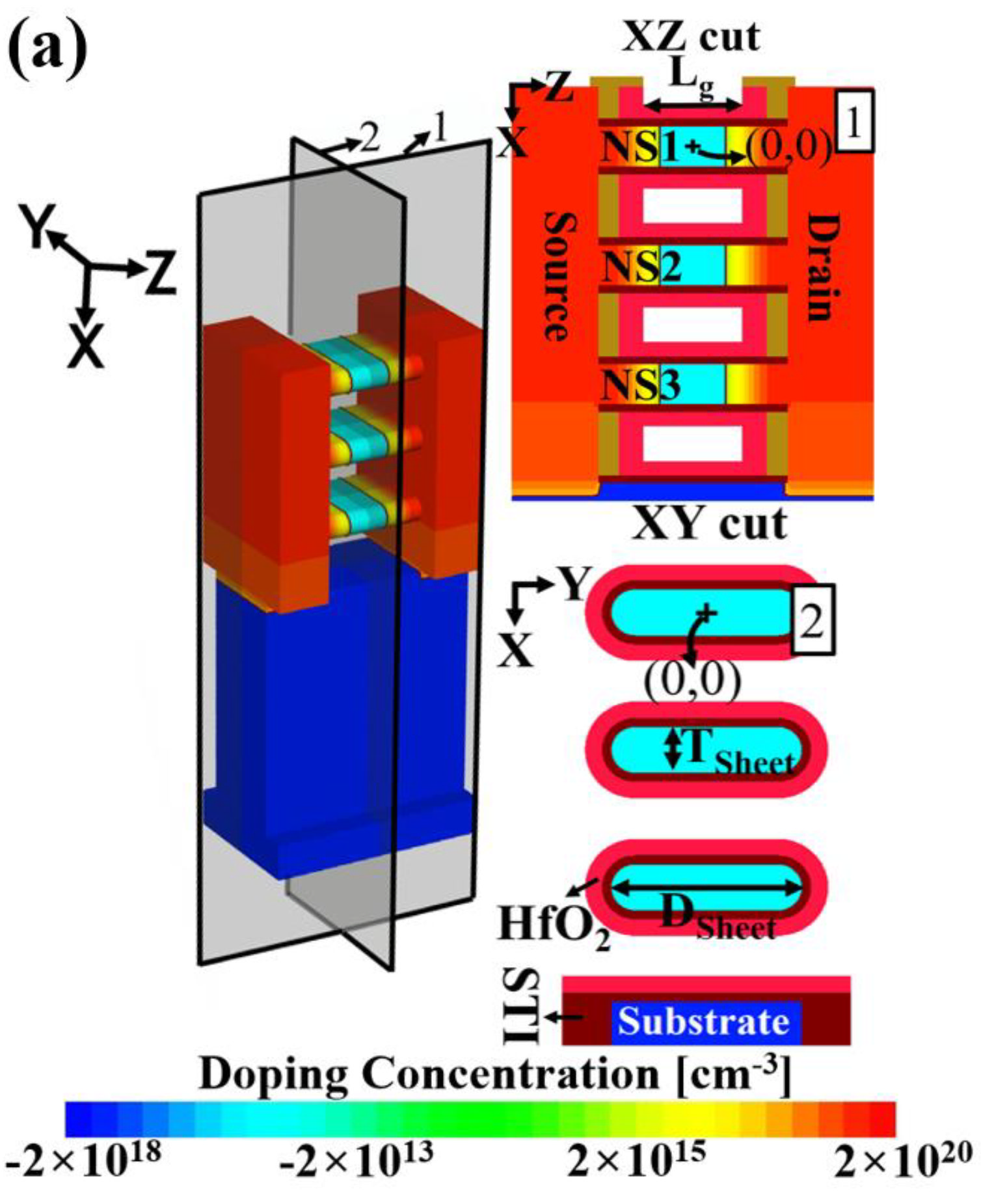

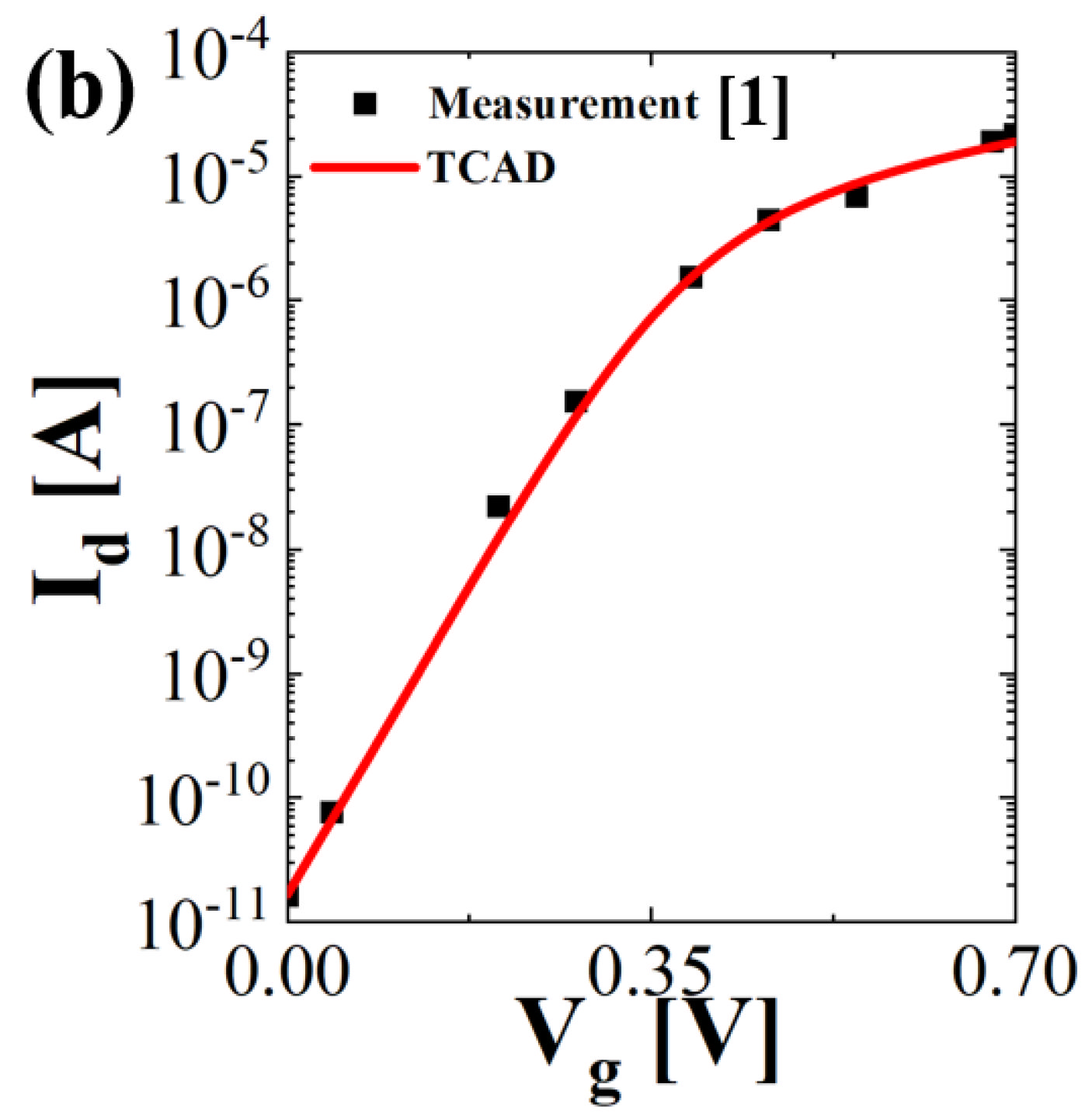

2. Materials and Methods

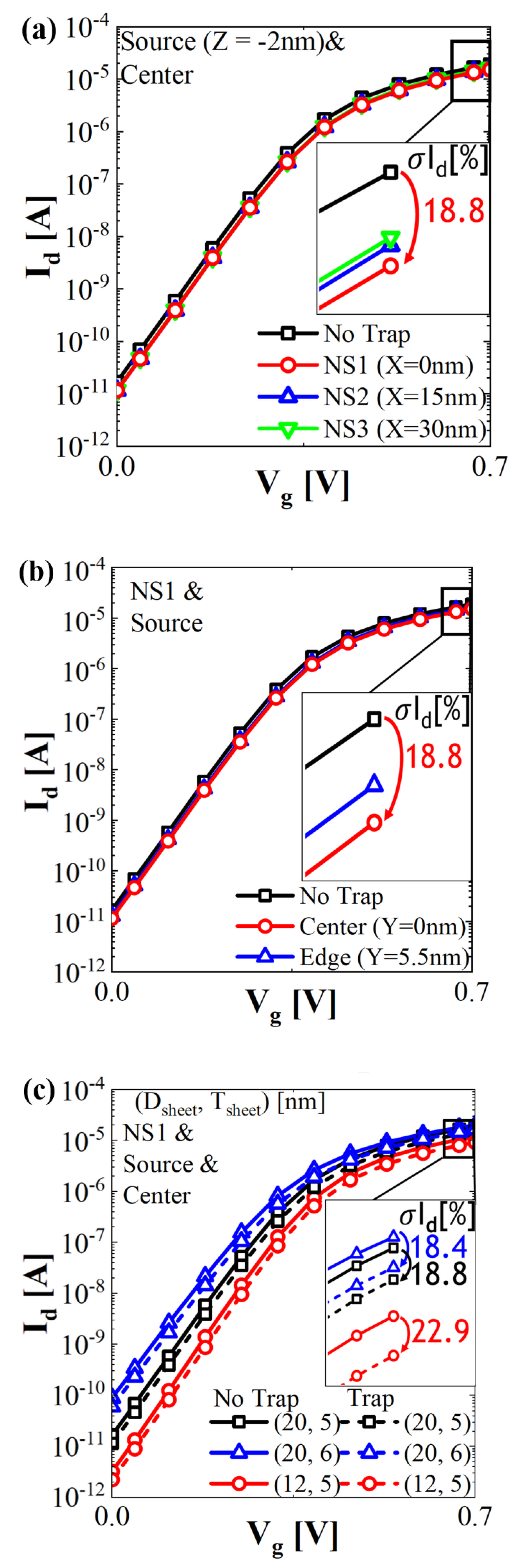

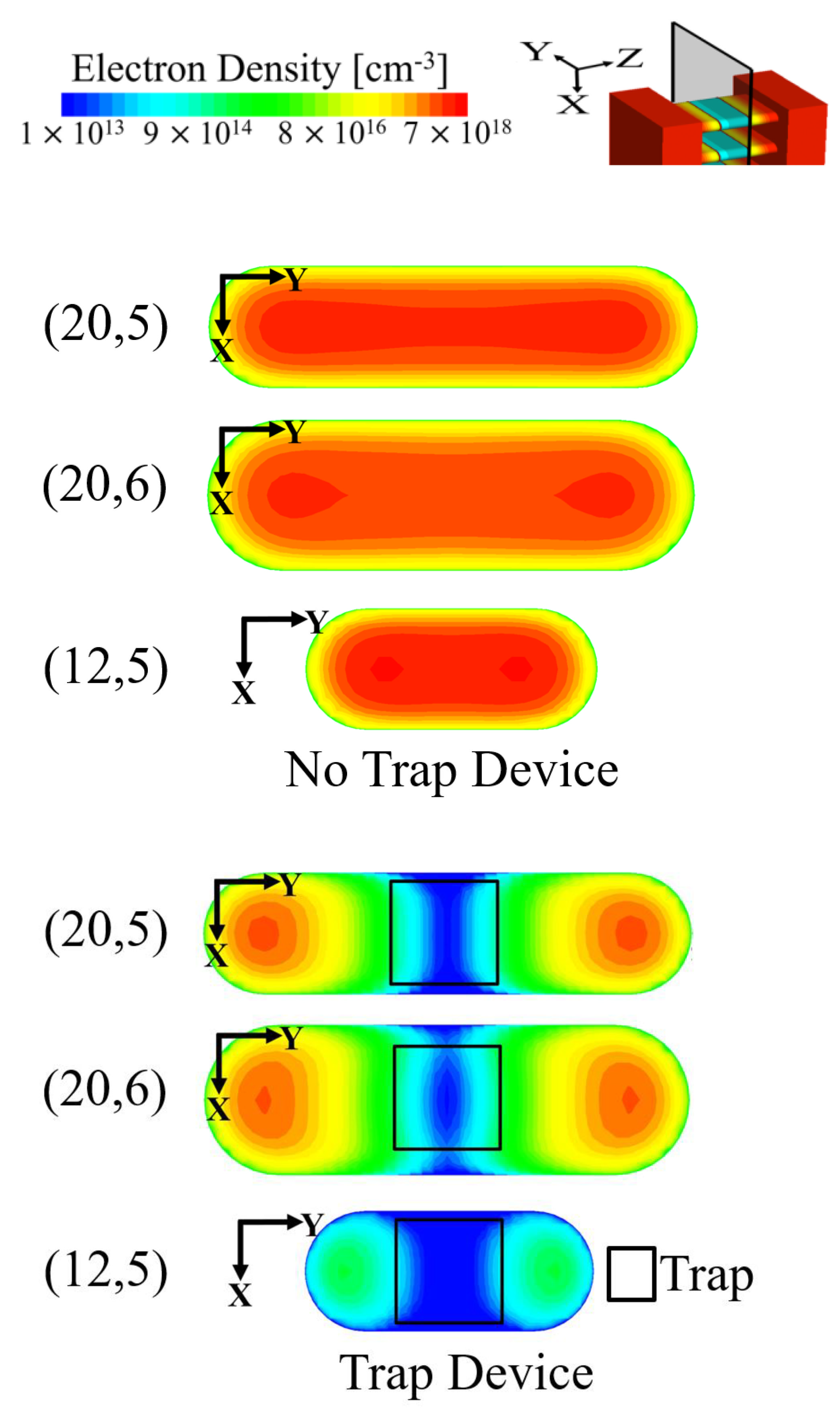

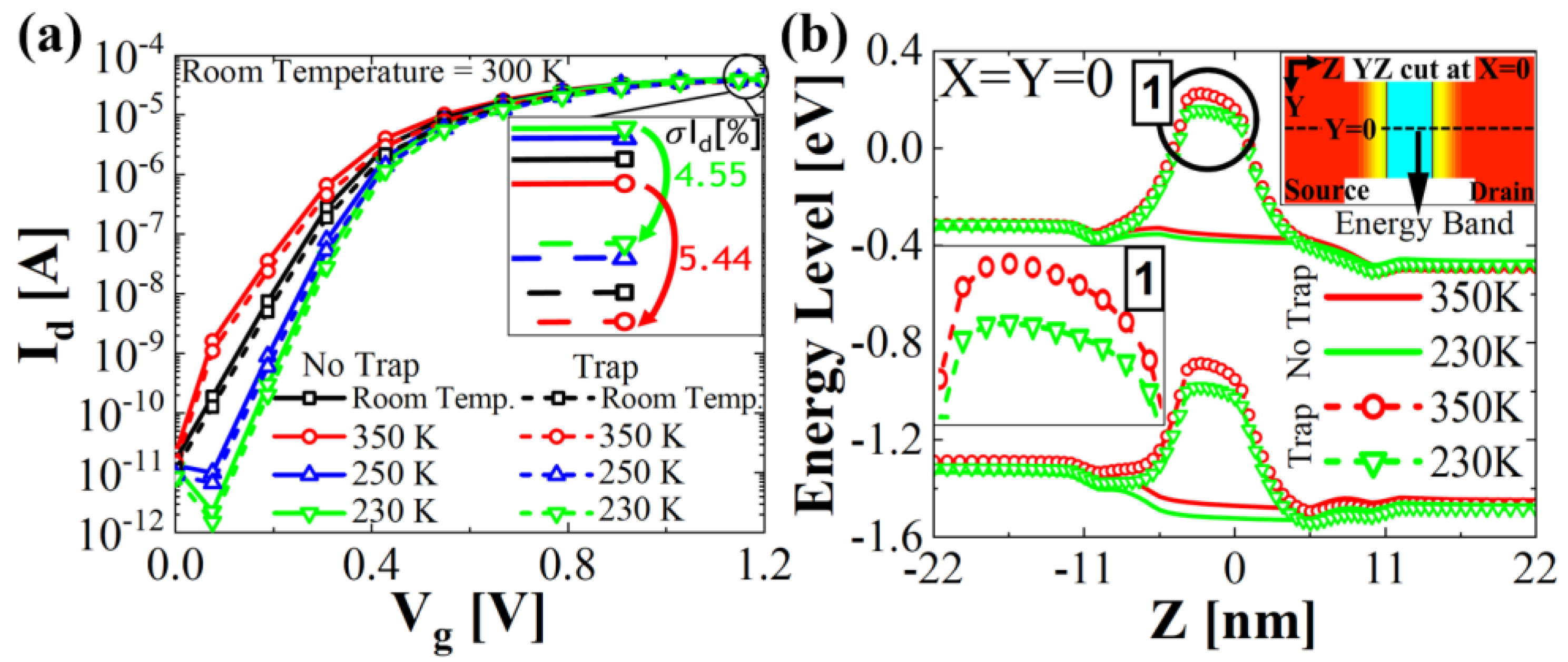

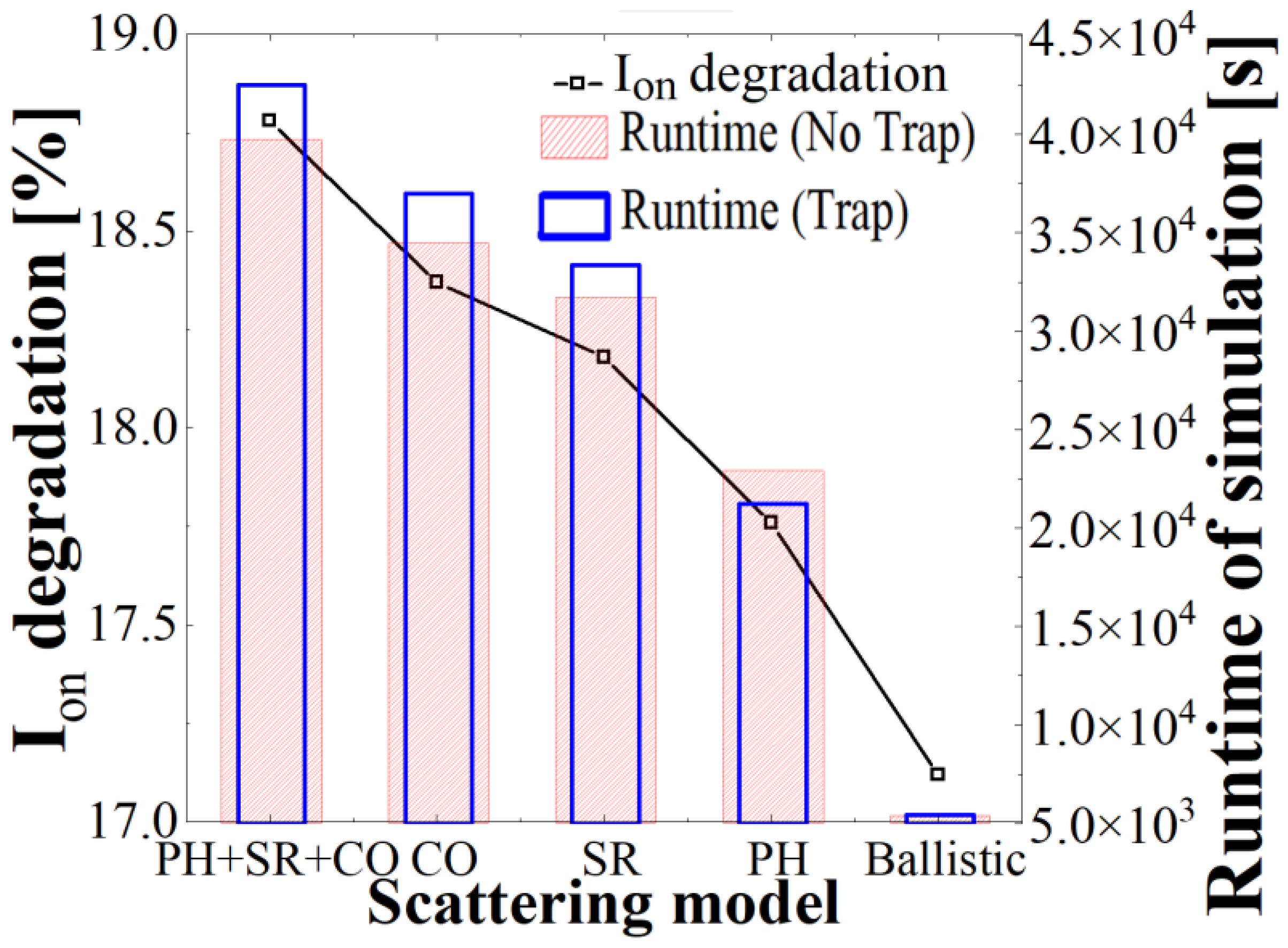

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T230–T231. [Google Scholar] [CrossRef]

- Kim, S.D.; Guillorn, M.; Lauer, I.; Oldiges, P.; Hook, T.; Na, M.H. Performance trade-offs in FinFET and gate-all-around device architectures for 7nm-node and beyond. In Proceedings of the IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Rohnert Park, CA, USA, 5–8 October 2015; pp. 1–3. [Google Scholar] [CrossRef]

- Gossmann, H.J.L.; Agarwal, A.; Parrill, T.; Rubin, L.M.; Poate, J.M. On the FinFET extension implant energy. IEEE Trans. Nanotech. 2003, 2, 285–290. [Google Scholar] [CrossRef]

- Hook, T.B.; Brown, J.; Cottrell, P.; Adler, E.; Hoyniak, D.; Johnson, J.; Mann, R. Lateral ion implant straggle and mask proximity effect. IEEE Trans. Electron Devices 2003, 50, 1946–1951. [Google Scholar] [CrossRef]

- Nylandsted Larsen, A. Epitaxial growth of Ge and SiGe on Si substrates. Mater. Sci. Semicond. Process. 2006, 9, 454–459. [Google Scholar] [CrossRef]

- David, T.; Aqua, J.-N.; Liu, K.; Favre, L.; Ronda, A.; Abbarchi, M.; Claude, J.-B.; Berbezier, I. New strategies for producing defect free SiGe strained nanolayers. Sci. Rep. 2018, 8, 2891. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Kim, J.; Lee, J.-S.; Han, J.-W.; Meyyappan, M. Caution: Abnormal Variability Due to Terrestrial Cosmic Rays in Scaled-Down FinFETs. IEEE Trans. Electron Devices 2019, 66, 1887–1891. [Google Scholar] [CrossRef]

- Esposito, M.G.; Manuel, J.E.; Bielejec, E.; Vizkelethy, G.; Dickerson, J.; Kerber, P.; King, M.P.; Talin, A.A.; Ashby, D.; McLain, M.; et al. Heavy Ion Displacement Damage Effects in 14 nm-Process FinFETs. United States. 2020. Available online: https://www.osti.gov/servlets/purl/1765528 (accessed on 1 February 2020).

- Burger, R.; MacCallum, J.M., Jr.; Lagnado, I.; Killiany, J.M.; Goodman, A.M.; Gwyn, C.; Benz, H.; Werner, R.M.; Reitmeyer, R.; Palkuti, L. DoD Silicon Investment Strategy; Report of DoD Advisory Group on Election Devices Working Group; Office of the Under Secretary of Defense for Acquisition: Arlington, VA, USA, 1992. [Google Scholar]

- Ziegler, J.; Lanford, W. The effect of sea level cosmic rays on electronic devices. In Proceedings of the 1980 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, San Francisco, CA, USA, 13–15 February 1980; Volume XXIII, pp. 70–71. [Google Scholar] [CrossRef]

- Ginet, G.P.; O’Brien, T.P.; Huston, S.L.; Johnston, W.R.; Guild, T.B.; Friedel, R.; Lindstrom, C.D.; Roth, C.J.; Whelan, P.; Quinn, R.A.; et al. AE9, AP9 and SPM: New Models for Specifying the Trapped Energetic Particle and Space Plasma Environment. Space Sci. Rev. 2013, 179, 579–615. [Google Scholar] [CrossRef] [Green Version]

- Sentaurus Device User Guide; Version N-2017.09; Synopsys: San Jose, CA, USA, 2017.

- Han, J.-W.; Wong, H.Y.; Moon, D.I.; Braga, N.; Meyyappan, M. Stringer Gate FinFET on Bulk Substrate. IEEE Trans. Electron Devices 2016, 63, 3432–3438. [Google Scholar] [CrossRef]

- Kim, J.; Han, J.-W.; Meyyappan, M. Reduction of Variability in Junctionless and Inversion-Mode FinFETs by Stringer Gate Structure. IEEE Trans. Electron Devices 2018, 65, 470–475. [Google Scholar] [CrossRef]

- Hurkx, G.A.M.; Klaassen, D.B.M.; Knuvers, M.P.G. A new recombination model for device simulation including tunneling. IEEE Trans. Electron Devices 1992, 39, 331–338. [Google Scholar] [CrossRef]

- Moroz, V.; Huang, J.; Arghavani, R. Transistor design for 5 nm and beyond: Slowing down electrons to speed up transistors. In Proceedings of the 2016 17th International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 15–16 March 2016; pp. 278–283. [Google Scholar] [CrossRef]

- Smith, L.; Choi, M.; Frey, M.; Moroz, V.; Ziegler, A.; Luisier, M. FinFET to nanowire transition at 5nm design rules. In Proceedings of the 2015 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Washington, DC, USA, 9–11 September 2015; pp. 254–257. [Google Scholar] [CrossRef]

- Choi, M.; Moroz, V.; Smith, L.; Huang, J. Extending drift-diffusion paradigm into the era of FinFETs and nanowires. In Proceedings of the 2015 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Washington, DC, USA, 9–11 September 2015; pp. 242–245. [Google Scholar] [CrossRef]

- SentaurusTM Device QTX User Guide; VersionO-2018.06; Synopsys, Inc.: Mountain View, CA, USA, 2018.

- Kim, J. The Impact of Displacement Defect in Nanosheet Field Effect Transistor. J. Electr. Eng. Technol. 2021, 16, 525–529. [Google Scholar] [CrossRef]

- Song, J.; Yuan, Y.; Yu, B.; Xiong, W.; Taur, Y. Compact Modeling of Experimental n- and p-Channel FinFETs. IEEE Trans. Electron Devices 2010, 57, 1369–1374. [Google Scholar] [CrossRef] [Green Version]

- Poli, S.; Pala, M.G.; Poiroux, T. Full Quantum Treatment of Remote Coulomb Scattering in Silicon Nanowire FETs. IEEE Trans. Electron Devices 2009, 56, 1191–1198. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ha, J.; Lee, G.; Bae, H.; Kim, K.; Han, J.-W.; Kim, J. On-State Current Degradation Owing to Displacement Defect by Terrestrial Cosmic Rays in Nanosheet FET. Micromachines 2022, 13, 1276. https://doi.org/10.3390/mi13081276

Ha J, Lee G, Bae H, Kim K, Han J-W, Kim J. On-State Current Degradation Owing to Displacement Defect by Terrestrial Cosmic Rays in Nanosheet FET. Micromachines. 2022; 13(8):1276. https://doi.org/10.3390/mi13081276

Chicago/Turabian StyleHa, Jonghyeon, Gyeongyeop Lee, Hagyoul Bae, Kihyun Kim, Jin-Woo Han, and Jungsik Kim. 2022. "On-State Current Degradation Owing to Displacement Defect by Terrestrial Cosmic Rays in Nanosheet FET" Micromachines 13, no. 8: 1276. https://doi.org/10.3390/mi13081276