Abstract

For electronic products, printed circuit boards are employed to fix integrated circuits (ICs) and connect all ICs and electronic components. This allows for the smooth transmission of electronic signals among electronic components. Machine learning (ML) techniques are popular and employed in various fields. To capture the nonlinear data patterns and input–output electrical relationships of analog circuits, this study aims to employ ML techniques to improve operations from modeling to testing in the analog IC packaging and testing industry. The simulation calculation of the resistance, inductance, and capacitance of the pin count corresponding to the target electrical specification is a complex process. Tasks include converting a two-dimensional circuit into a three-dimensional one in simulation and modeling-buried structure operations. In this study, circuit datasets are employed for training the ML model to predict resistance (R), inductance (L), and capacitance (C). The least squares support vector regression (LSSVR) with Genetic Algorithms (GA) (LSSVR-GA) serves as an ML model for forecasting RLC values. Genetic algorithms are used to select parameters of LSSVR models. To demonstrate the performance of LSSVR models in forecasting RLC values, three other ML models with genetic algorithms, including backpropagation neural networks (BPNN-GA), random forest (RF-GA), and eXtreme gradient boosting (XGBoost-GA), were employed to cope with the same data. Numerical results illustrated that the LSSVR-GA outperformed the three other forecasting models by around 14.84% averagely in terms of mean absolute percentage error (MAPE), weighted absolute percent error measure (WAPE), and normalized mean absolute error (NMAE). This study collected data from an IC packaging and testing firm in Taiwan. The innovation and advantage of the proposed method is using a machine approach to forecast RLC values instead of through simulation ways, which generates accurate results. Numerical results revealed that the developed ML model is effective and efficient in RLC circuit forecasting for the analog IC packaging and testing industry.

1. Introduction

Circuit simulation work in the integrated circuit (IC) packaging process depends on model complexity in geometry and electromagnetic materials. Properly simulating IC packaging plays a vital role in catching potential EMC, power, and signal integrity issues early in the design process and overcoming major pitfalls. The elimination of manual processing is required to reduce the time and effort from customer requirement specifications to IC packaging design, testing, manufacturing, and to determine the tools and process options for application design. Implementation takes prediction, evaluation, and decision making with machine learning-centric databases, tools, and design models. Learning-based tools and process models must continuously improve through additional design experience [1,2].

Machine learning (ML) solved many problems that were originally difficult to solve in data science. Many studies have shown that machine learning and optimization algorithms are suitable for solving different problems in the IC packaging and design processes, reducing design errors and design cycle time [3]. Table 1 shows the latest research on the IC packaging process using machine learning.

The signal passes through the substrate of the printed circuit board. Simulation provides the designer with a pre-optimized design concept. Ren et al. [4] introduced a graph neural network to predict network parasitics and device parameters by converting circuit schematics into graphs and utilizing key GNN-based modeling techniques. The results showed that the average simulation error was reduced from over 100% and estimated by designers to be less than 10%. Shook et al. [5] proposed a new machine learning-based parasitic estimation method for pre-layout custom circuit designs. For various analog circuits, the results show a reduction in the average error between pre-layout and post-layout circuit simulations from 37% to 8%.

For optimization and evaluation of package structural characteristics, Wu and Chu [6] proposed and verified an analog-driven design method for chip package integration structure design optimization. The study’s results suggest that the random forest algorithm can predict stress for chip package-integrated design. Hsiao and Chiang [7] proposed applying the RF model to predict the reliability of wafer-level packaging. The designers can easily optimize the WLP structure and shorten the design cycle. Lee et al. [8] developed a chip-to-package interactive risk assessment platform using finite element analysis, meta-modeling, and genetic algorithm optimization methods.

Heat transfer analysis of package structures is important in package functional testing. Acharya et al. [9] used three ML algorithms, random forest, support vector regression, and a neural network to model thermal behavior through hotspot temperature simulation data evaluation. They proposed an ML-based thermal design method and provided a reference frame for future packaging materials. Durgam et al. [10] used several machine learning methods to predict the temperature of the heat source on the substrate. The results showed that the temperature agreement between the prediction and the simulation was less than 10%. Jing et al. [11] proposed using the genetic algorithm to optimize the temperature curve prediction model in the reflow soldering process. The results show that the predicted value meets the error accuracy requirements. The results also prove that the established mathematical model can effectively predict temperature curves.

The power delivery network (PDN) must reliably supply power to functional blocks in an integrated circuit (IC). A robust PDN design has always been a critical challenge. Cecchetti et al. [12] developed a Genetic Algorithm (GA) and Artificial Neural Network (ANN) model for iterative optimization of the placement of decoupling capacitors in a PDN. They concluded that the GA-ANN model is consistent with the results of commercial simulator optimization. Sourav et al. [13] presented an ML architecture that combined neural networks and regression trees to predict printed circuit board (PCB) inductance and resistance. They employed an LSTM model to predict voltage drop as a function of time. The average prediction accuracy of the proposed method is 94%.

There have been many models utilizing machine learning and optimization to solve issues in IC packaging. Mao et al. [14] proposed a machine learning (ML) model based on the backpropagation (BP) method for predicting three-dimensional board-level drop responses for ball grid array (BGA) encapsulation structures. Jin et al. [15] constructed several machine learning methods to accurately predict the radiated electric field of wire-bonded ball grid array packages. They optimized model parameters to minimize the prediction error of each model. Their conclusion shows that DNN is an effective and feasible prediction model. Wang et al. [16] proposed a reverse design method based on convolutional neural networks for the fast optimization and design of encapsulation structures. Schierholz et al. [2] provided a database that allows for the study of machine learning tools and techniques in signal integrity, power integrity, and electromagnetic compatibility. It contains printed circuit board (PCB)-based interconnects and physics (PB). The corresponding frequency domain data of the tool can be used for different types of structural simulations.

Table 1.

Summary of ML-based IC packaging process applications.

Table 1.

Summary of ML-based IC packaging process applications.

| Literature | Years | Application | Method(s) |

|---|---|---|---|

| Ren et al. [4] | 2021 | Predict net parasitics and device parameters | GNN |

| Shook et al. [5] | 2020 | Parasitic estimation | Random forest |

| Wu and Chu [6] | 2021 | The structural design optimization of chip package integration | Random forest |

| Hsiao and Chiang [7] | 2020 | Packaging reliability analysis and prediction | Random forest |

| Lee et al. [8] | 2021 | Interactive risk assessment of chip packaging | FEA, MOGA |

| Acharya et al. [9] | 2021 | Predict the thermal behavior of a power electronics package | Random forest, SVR, ANN |

| Durgam et al. [10] | 2022 | The optimization of temperature on printed circuit board | XG Boost, ANN, SVR, RFR |

| Jing et al. [11] | 2021 | Predicting the temperature curve of SMT reflow soldering | Genetic Algorithm |

| Cecchetti et al. [12] | 2020 | Power delivery network (PDN) | ANN, Genetic Algorithm |

| Sourav et al. [13] | 2020 | Power delivery network (PDN) | Regressor trees, LSTM |

| Mao et al. [14] | 2022 | Predicting three-dimensional board-level drop responses for ball grid array (BGA) encapsulation structures | BPNN |

| Jin et al. [15] | 2022 | Predicting the radiated electric field of a wire-bonded ball grid array package | DNN, SVR, K-nearest neighbors, LR |

| Wang et al. [16] | 2021 | Full wave radiation simulation of package design process | CNN |

| Schierholz et al. [2] | 2021 | Signal integrity (SI) and power integrity (PI) database based on PCB interconnection | ANN, Genetic Algorithm |

This study attempted to use least squares support vector regression with genetic algorithms to predict the RLC (resistance, inductance, and capacitance) values currently generated by simulation methods. The genetic algorithms were employed to determine LSSVR parameters to improve forecasting accuracy. The designed method employs a machine learning approach to forecast RLC values instead of through simulation ways and generates more accurate results than the three other machine learning models. The rest of this study is organized as follows. Section 2 provides the substrate and interface electrical transfer properties based on IC packages. Section 3 briefs the LSSVR model and genetic algorithms. The flowchart of the LSSVR-GA model for predicting RLC values is also addressed and presented. Numerical results are illustrated in Section 4. Conclusions are indicated in Section 5.

2. The Substrate and Interface of the IC Package Transmit Electrical Properties

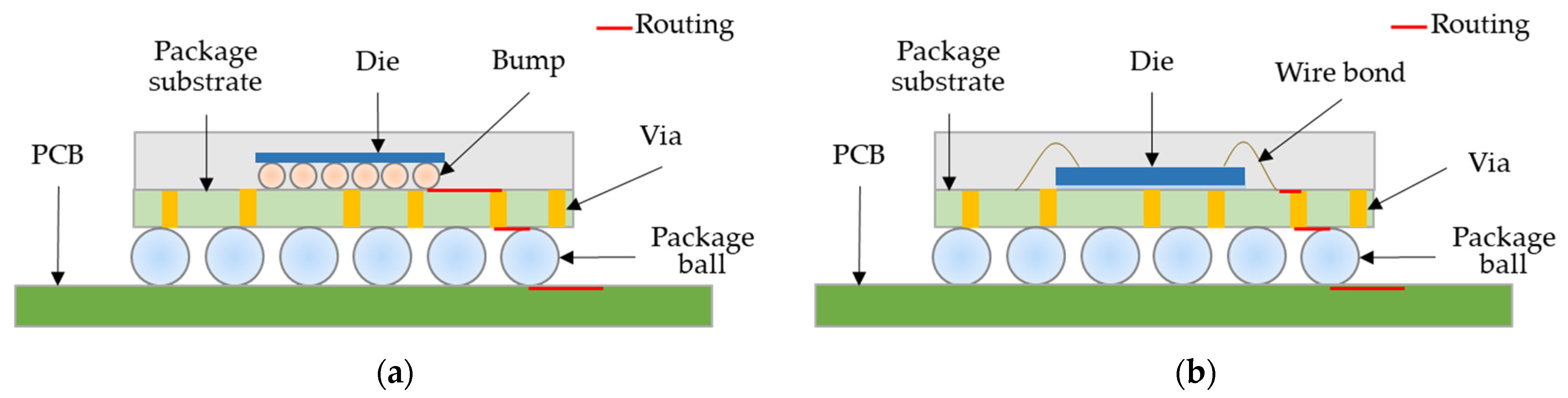

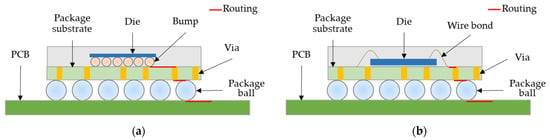

In IC packaging design, the substrate is used as a carrier. The functions of the substrate are to protect and carry the IC chip and serve as a medium for circuit signal transmission. Integrated circuit packaging is the final stage of semiconductor component manufacturing. As a method for connecting the die to the external circuit, the chip’s packaging considers the pin configuration, electrical performance, heat dissipation, and the chip’s physical size. There are many typical packaging forms in the semiconductor industry [17,18]. Currently, the most common internal packaging methods of integrated circuits are wire bonding (WB) and flip chip (FC) packages. Flip chip packaging connects the chip to the bump and then turns the IC chip over to directly connect the bump and substrate. The wire bonding package places the chip on the substrate (chip pad) and then uses the wire bonding technology to connect the chip to the connection point on the substrate. The IC substrate acts as a buffer interface for electrical connection and transmission between the IC die and the PCB through the conductive routing and vias (VIA) network, as shown in Figure 1.

Figure 1.

IC Package connections with substrate [19]. (a) Flip chip; (b) wire bonding.

The RLC circuit is essential to evaluate the overall interface transmission capability in the IC packaging design process. It is a circuit structure composed of resistors, capacitors, and inductors. Parasitic effects associated with ICs and printed circuit board (PCB) conductors and their paths are essential parameters of the electrical transport model. The parasitic effects of RLC lines in the IC package process can cause signal integrity problems due to signal attenuation and delay [20,21].

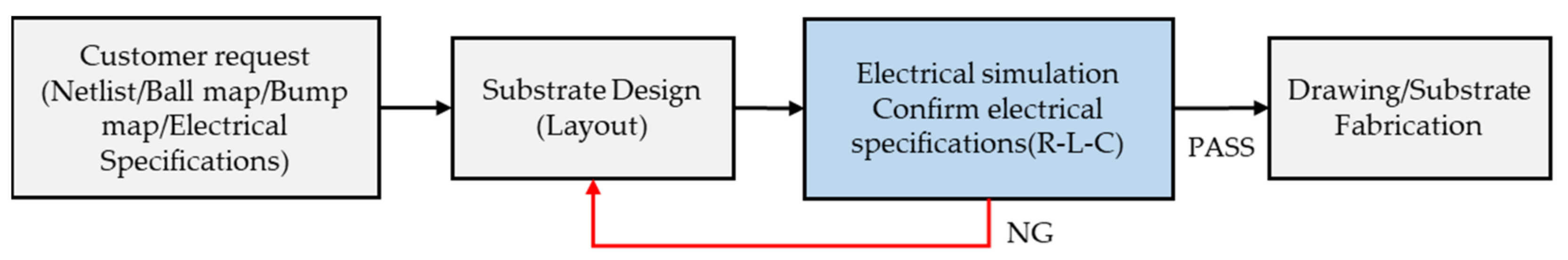

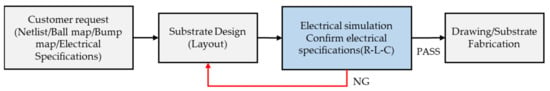

In the process of IC substrate generation, the substrate design is first performed according to the target circuit specification. The netlist of the corresponding circuit is associated with performing a post-layout simulation to verify the corresponding layout performance. If the post-layout simulation results are violated, the designer will adjust his layout and re-simulate. Figure 2 shows that this process is repeated until the simulated substrate design conforms to the RLC electrical specifications for interface transmission. The current process requires multiple simulation runs to meet the desired target circuit specification. Therefore, any inaccuracies in the design or components can produce misleading post-layout simulation results. Such misleading results can reduce yield and increase circuit design waste time.

Figure 2.

IC substrate generation process.

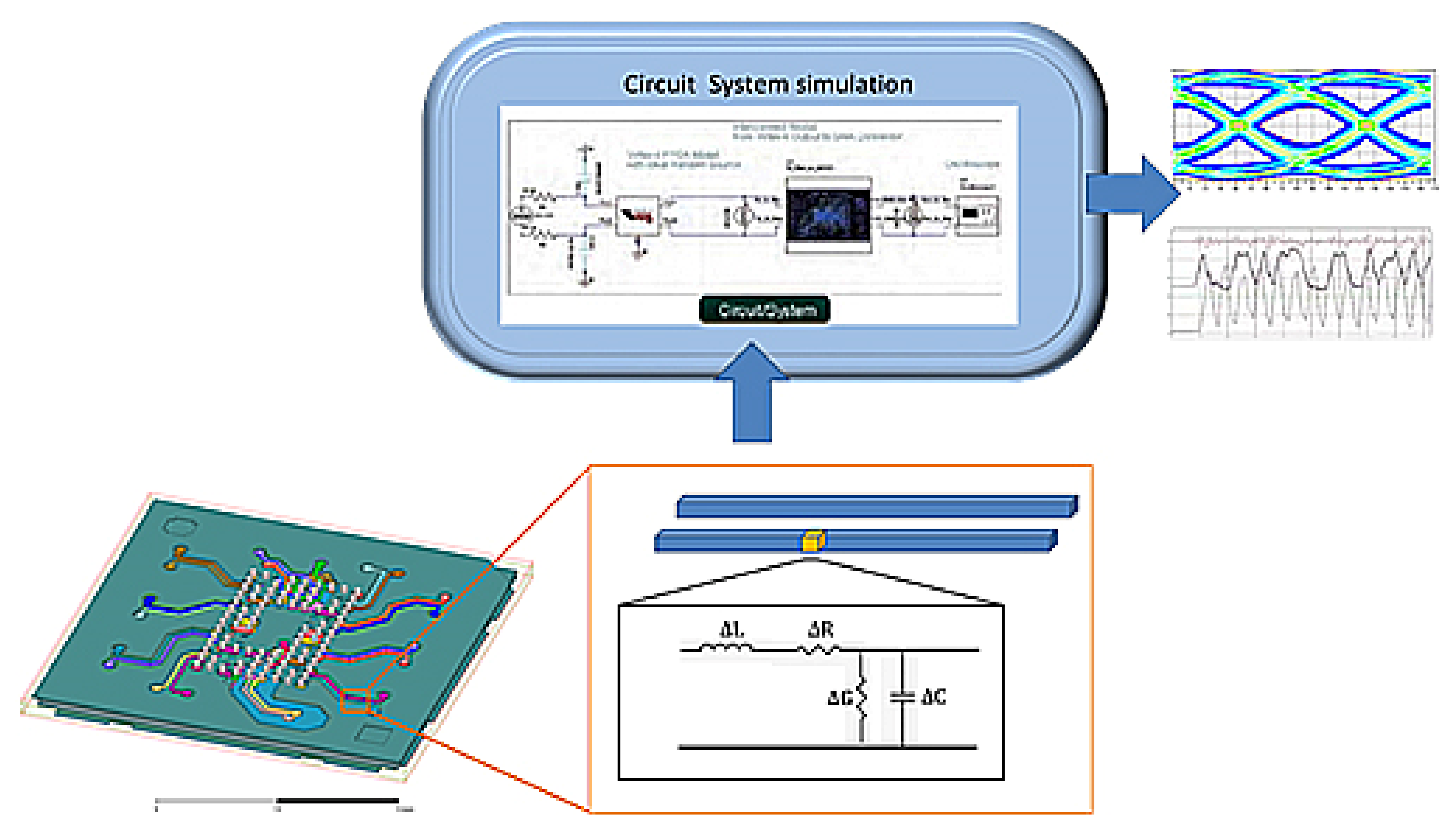

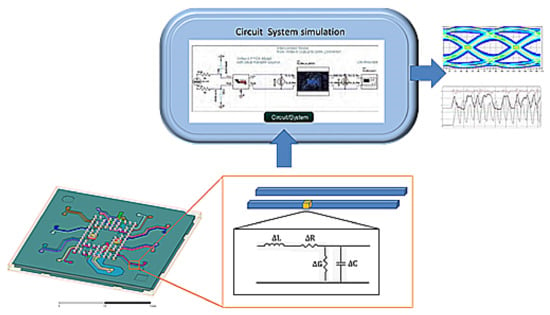

Signal transmission relies on the interconnected line group. According to the transmission line theory, the transmission line calibration model can replace the electrical characteristics of the signal and use an equivalent model. When the system simulation is based on the transmission line calibration model, the substrate RLC model, IC input/output buffer information specification (IBIS) model, and PCB electrical properties model are applied to the system simulations for system verification. The process is shown in Figure 3.

Figure 3.

The illustration of RLC model system simulation and verification provided by SPIL (Siliconware Precision Industries Co., Ltd., Taichung City, Taiwan).

3. Forecasting RLC Values of Integrated Circuits by LSSVR-GA Models

3.1. LSSVR Models with Genetic Algorithms

The LSSVR method can be traced back to the SVM (Support Vector Machine) proposed by Cortes and Vapnik [22]. The SVM can handle classification and regression problems and performs better on small samples. Suykens and Vandewalle [23] proposed LSSVM. It solves the high computational burden problem of the SVM. The problem used to solve regression is called LSSVR [24].

Consider a given data set {, | i = 1,2,3, …, n}, where is the ith input data including d features, and is the ith output data. Establishing the model for the LSSVR is as follows in Equation (1):

where is the transposed form of the weight matrix, represents a nonlinear function that maps from the original dimensional feature space to a higher dimensional feature space, and is a bias value.

The optimization problem to be solved by the model is presented as Equation (2):

where is lose function, is the regularization parameter, and means the random error.

Because of the constraints, the optimal solution to the computational problem is very complicated. The Lagrange function is optimized and presented in Equation (3) to solve this problem:

where is the Lagrange function and is the Lagrange multiplier. After optimization using the KKT condition (Karush–Kuhn–Tucker condition), the formula is described in Equation (4)

The kernel function is considered as follows in Equation (5):

Finally, the model estimation formula by LSSVR can be obtained with Equation (6):

There are common kernel functions such as the string kernel [25], the radial basis function kernel (RBF) [26], and the polynomial kernel [27]. This study used the RBF kernel function in Equation (7), and the RBF kernel utilizes high-dimensional nonlinear mapping to resolve the nonlinear relationship between dependent and independent variables. The RBF kernel learned more complex decision boundaries:

where is the parameter of the RBF kernel function. The decision of these two parameters— and —would affect the accuracy of the LSSVR model, so GA was performed to optimize these two parameters. The complete concept of GA was advocated by John Holland [28,29]. GA simulates the natural evolution law of natural ecology, imitates the survival of the fittest in the natural group, eliminates the inferior, and converges into a balanced mechanism under repeated iterations. GA is a search method used to solve optimization problems. Genes can select, crossover, and mutate. Better genes are passed to the new generation, and the inferior genes will be eliminated gradually. GA has been widely applied in solving optimization problems, data searches, artificial intelligence, and machine learning.

3.2. LSSVR-GA Architecture for RLC Prediction

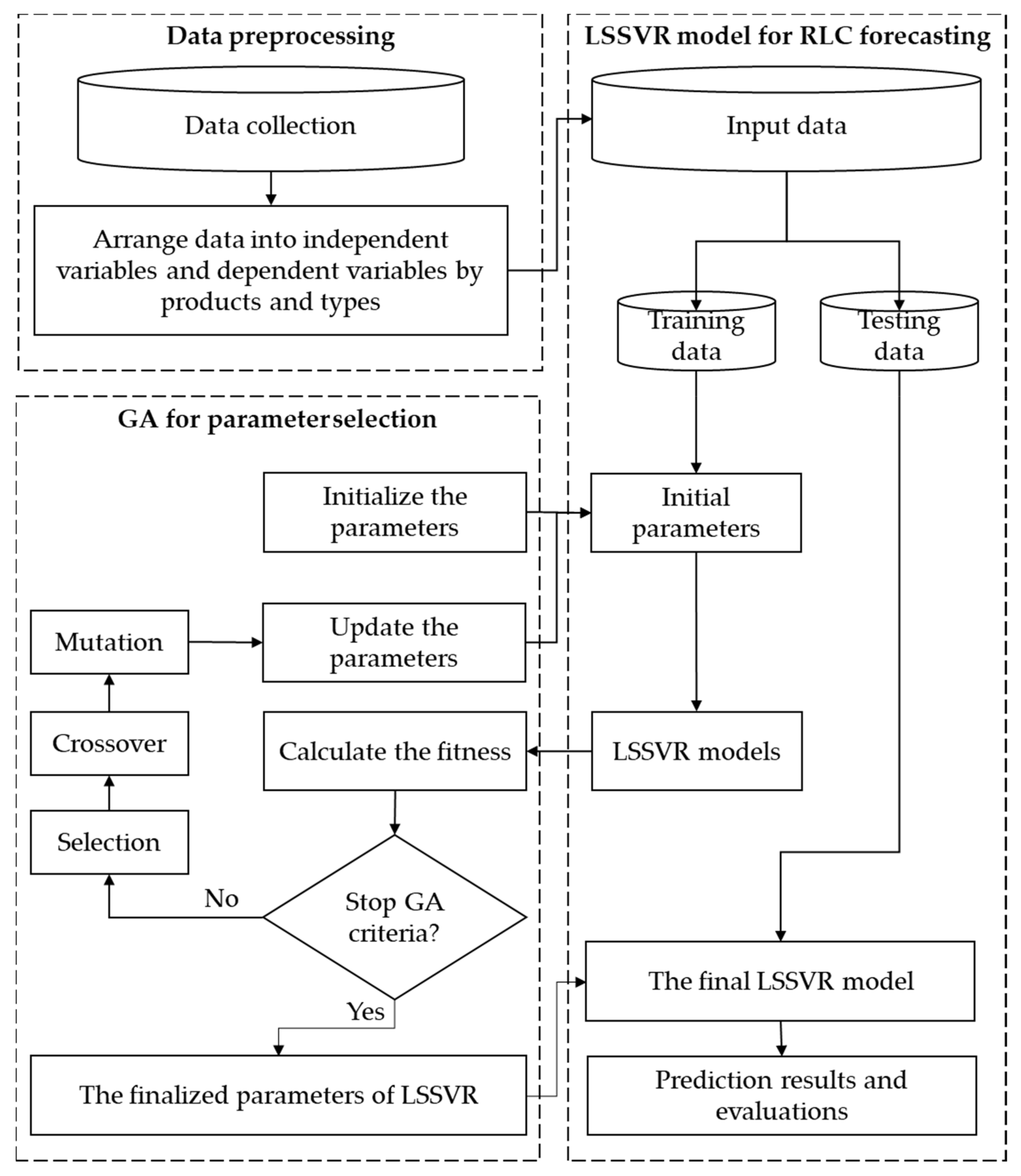

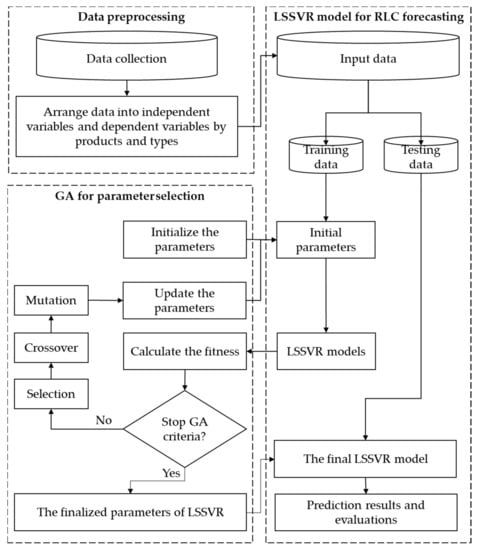

Figure 4 illustrates the framework of the LSSVR-GA model in RLC (resistance, inductance, and capacitance) forecasting. It consists of 3 modules: data preprocessing, GA for parameter selection, and the LSSVR model for RLC forecasting. To solve the time-consuming problem of calculating the parameters for complex simulation software while verifying substrate designs, this study proposed a machine learning method to predict the RLC values for different product types.

Figure 4.

The framework of LSSVR-GA model for RLC values prediction.

The experimental data were semi-structured historical data provided by SPIL (Siliconware Precision Industries Co., Ltd.), including two different IC package process products, FC and WB. The historical data of different products of two-layer, four-layer, and six-layer PCB were selected based on these two processes. The three dependent variables for each product are resistance (R), inductance (L), and capacitance (C). The independent variables (X1~Xn) include ball, bump, base, L1, L2, L3, L4, L5, via, and wire. In the data preprocessing stage, this study integrated these scattered semi-structured data into one-to-one corresponding structured data between dependent and independent variables according to product types. It filled the missing values with 0. Table 2 describes the features and samples in predicting RLC for different data sets of substrate products.

Table 2.

The features and samples in predicting RLC for different substrate products.

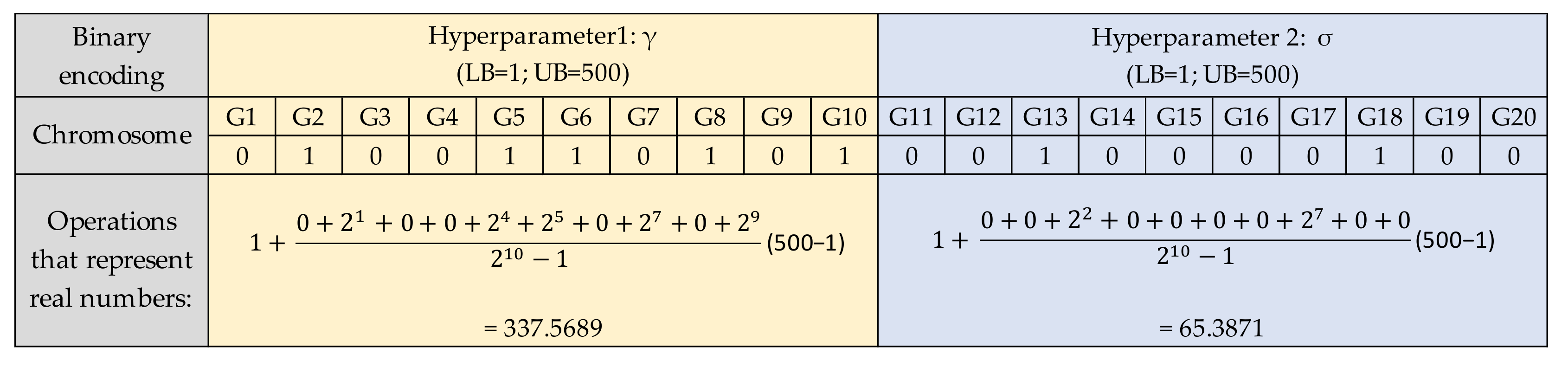

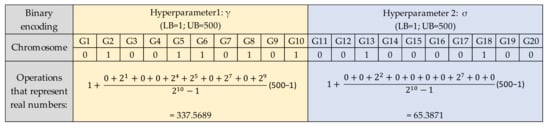

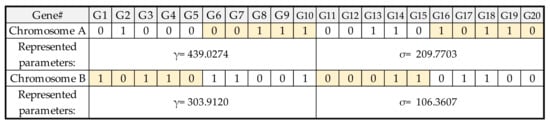

The preprocessed data sets were divided into 80% training data and 20% testing data. The training data were used to build the LSSVR model with the parameters optimized by GA. Before applying GA, it is necessary to encode the parameters to be optimized into a group of chromosomes. The common encoding methods include binary, real, multi-objective, parallel, chaotic, and hybrid GA [30]. Considering the simplicity of implementation for factory operators, this study used the binary-coded GA to optimize the parameters of LSSVR, and each digital bit represented a gene. The length of the chromosome was defined according to the spatial range of the actual problem to be solved. The real number represented by the binary encoded was calculated as Equation (8).

where is the real number represented by the binary encoded, is the lower bound of the spatial range, is the upper bound of the spatial range, is the encoded bit length, and is the bit value of the ith bit.

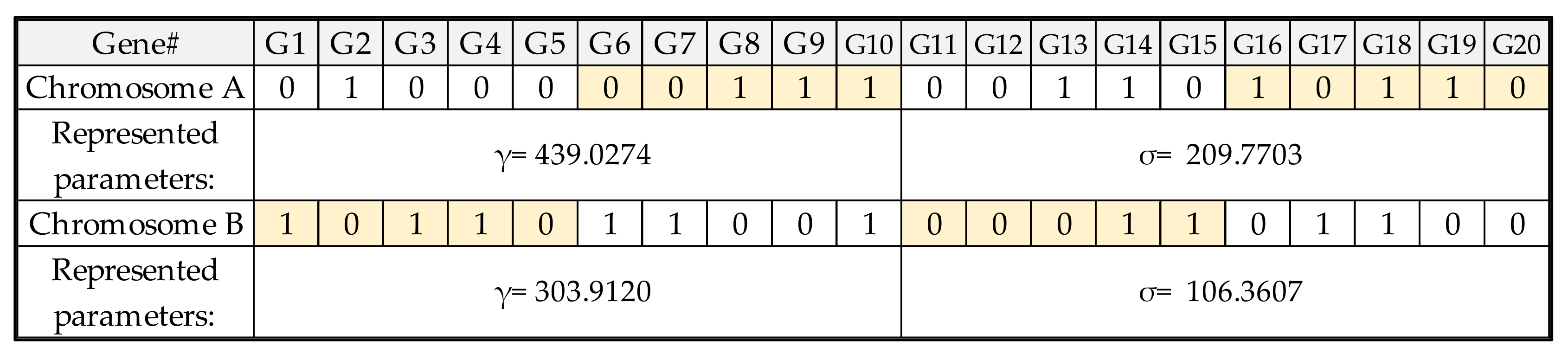

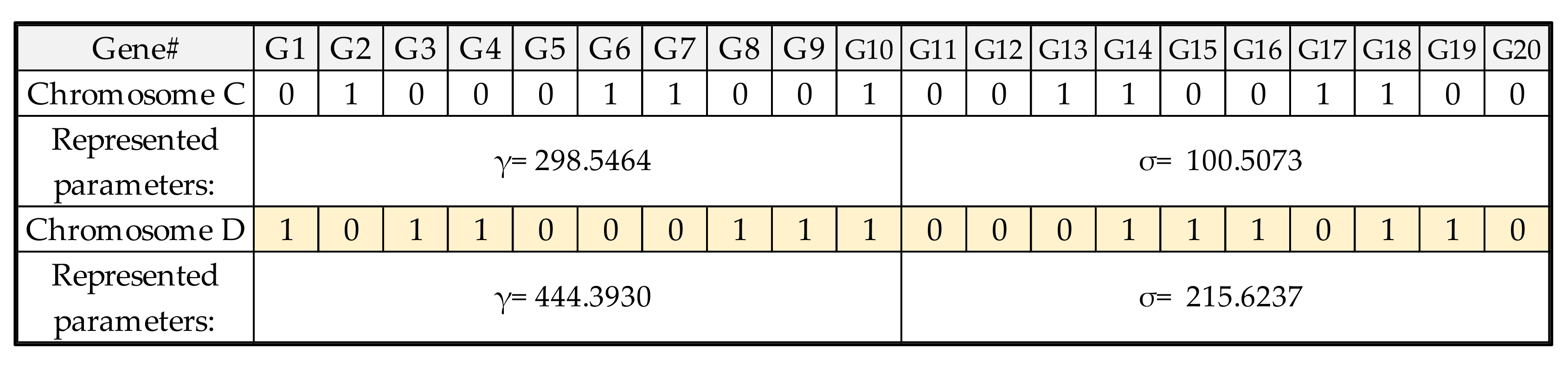

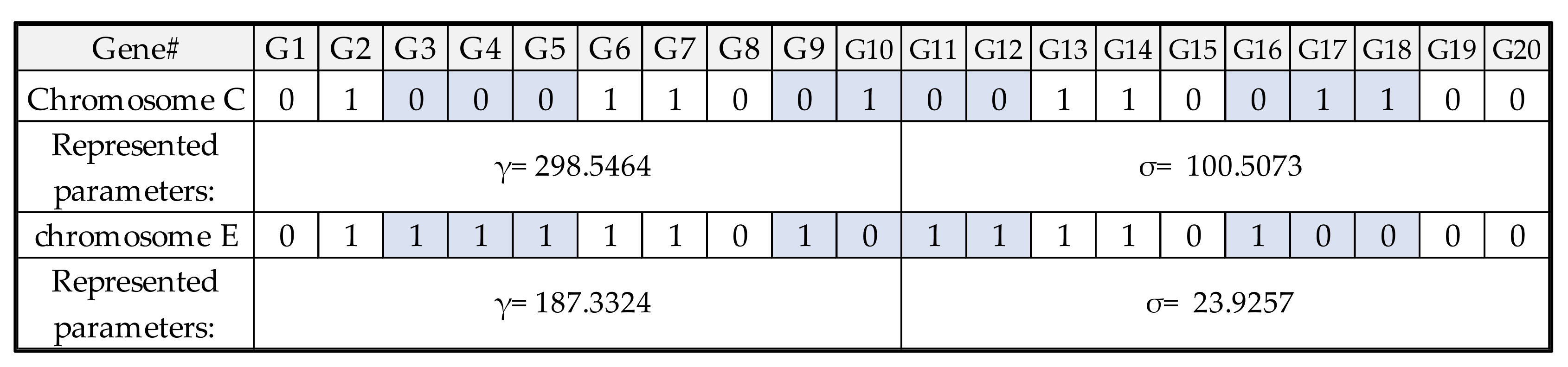

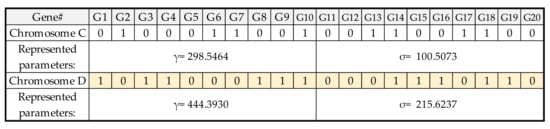

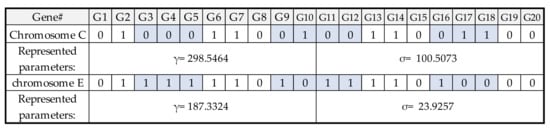

Figure 5 shows the LSSVR model’s encoded parameters—γ and —and the operation of real numbers. Each parameter consists of 10 genes, and the LSSVR model has two parameters. These two parameters represent 20 genes as a chromosome. The lower and upper bounds of the two parameters are both 1 and 500, and the real numbers represented are calculated accordingly. It is also necessary to define the optimized procedure settings of LSSVR-GA. The population size, iteration, crossover rate, and mutation rate were arranged at 40, 20, 0.8, and 0.1, respectively. When starting GA, the parameters must first be initialized as the input parameter of the LSSVR model. The training result of the LSSVR model is calculated by the fitness function. This is to evaluate the stopping conditions for GA. If conditions are not met, it will go through the process as in Figure 6, Figure 7 and Figure 8, and the GA selection-crossover-mutation process will have a new generation. Good chromosomes have more opportunities to be selected. Unfit and less fit chromosomes are gradually eliminated. Therefore, the updated parameters are used as input parameters of the LSSVR model. To find the best-fit parameters of LSSVR, repeat the fitness function to compute the evaluation until the GA stop condition. Then, set the best-fit parameters of LSSVR in the final LSSVR model and perform RLC predictions.

Figure 5.

The LSSVR parameter encoding and operation of representing real numbers.

Figure 6.

The binary encoding for parameters of LSSVR at the stage of initial population.

Figure 7.

The binary encoding for parameters of LSSVR after multi-point crossover.

Figure 8.

The binary encoding for parameters of LSSVR after mutation from chromosome C to E.

4. Numerical Results

Predicted results are evaluated and analyzed with the testing data to examine the effectiveness and interpretability of the proposed method. The evaluation is measured by mean absolute percentage error (MAPE (%)), weighted absolute percent error measure (WAPE (%)), and normalized mean absolute error (NMAE), as shown in Equations (9)–(11).

where is the ith predict value, is the ith actual value, and = 1~n.

Three other forecasting models with genetic algorithms, namely backpropagation neural networks (BPNN-GA), random forest (RF-GA), and eXtreme gradient boosting (XGBoost-GA), were employed to deal with the same data. Table 3 illustrates parameters determined by genetic algorithms to predict LCR values of different forecasting models. Lewis [31] reported that forecasting performance measured by MAPE values could be depicted in Table 4. Table 5 lists the MAPE, WAPE, and NMAE values of the four forecasting models.

Table 3.

Parameters of forecasting models provided by genetic algorithms in LCR values prediction.

Table 4.

Levels of forecasting accuracy measured by MAPE [31].

Table 5.

Forecasting results of different models in terms of MAPE, WAPE, and NMAE.

The average performance of these six products is at the levels of good or highly accurate in predicting RLC using LSSVR-GA models. Furthermore, the LSSVR-GA models can generate average more accurate results than the other three forecasting models in terms of MAPE, WAPE, and NMAE.

5. Conclusions

This study outlines an efficient method for predicting RLC circuit simulation in the IC package process using LSSVR-GA hybrid models. This method can be used to predict the integrity of RLC circuits. The ability to accurately predict analog circuits is essential to the IC package industry due to the timesaving in substrate design and process optimization. The numerical results revealed that the designed LSSVR-GA method is a feasible, effective, and efficient alternative for forecasting RLC values. For future research, one potential direction is to employ deep learning approaches to cope with the same data sets used in this study to improve forecasting accuracy. The other possible direction is to apply the presented LSSVR-GA framework to more complex circuit cases to examine performance.

Author Contributions

Conceptualization, Y.-P.W. and P.-F.P.; methodology, J.-P.L. and Y.-L.L.; software, J.-P.L. and Y.-L.L.; validation, H.-C.L. and C.-Y.S.; formal analysis, J.-P.L. and Y.-L.L.; data curation, H.-C.L. and C.-Y.S.; writing—original draft preparation, J.-P.L. and Y.-L.L.; writing—review and editing, P.-F.P.; visualization, J.-P.L. and Y.-L.L.; supervision, Y.-P.W. and P.-F.P.; funding acquisition, Y.-P.W. and P.-F.P. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by Siliconware Precision Industries Co., Ltd., grant number 110A052.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Not applicable.

Acknowledgments

The raw data of this work were supported by Huei-Chi Yang of Siliconware Precision Industries Co., Ltd.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Swaminathan, M.; Torun, H.M.; Yu, H.; Hejase, J.A.; Becker, W.D. Demystifying machine learning for signal and power integrity problems in packaging. IEEE Trans. Compon. Packag. Technol. 2020, 10, 1276–1295. [Google Scholar] [CrossRef]

- Schierholz, M.; Sánchez-Masís, A.; Carmona-Cruz, A.; Duan, X.; Roy, K.; Yang, C.; Rimolo-Donadio, R.; Schuster, C. Si/pi-database of pcb-based interconnects for machine learning applications. IEEE Access 2021, 9, 34423–34432. [Google Scholar] [CrossRef]

- Abdolrasol, M.G.; Hussain, S.S.; Ustun, T.S.; Sarker, M.R.; Hannan, M.A.; Mohamed, R.; Ali, J.A.; Mekhilef, S.; Milad, A. Artificial neural networks based optimization techniques: A review. Electronics 2021, 10, 2689. [Google Scholar] [CrossRef]

- Ren, H.; Kokai, G.F.; Turner, W.J.; Ku, T.-S. Paragraph: Layout parasitics and device parameter prediction using graph neural networks. In Proceedings of the 2020 57th ACM/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 20–24 July 2020; pp. 1–6. [Google Scholar]

- Shook, B.; Bhansali, P.; Kashyap, C.; Amin, C.; Joshi, S. Mlparest: Machine learning based parasitic estimation for custom circuit design. In Proceedings of the 2020 57th ACM/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 20–24 July 2020; pp. 1–6. [Google Scholar]

- Wu, H.; Chu, W. Machine learning assisted structural design optimization for flip chip packages. In Proceedings of the 2021 6th International Conference on Integrated Circuits and Microsystems (ICICM), Nanjing, China, 22–24 October 2021; pp. 132–136. [Google Scholar]

- Hsiao, H.; Chiang, K. Ai-assisted reliability life prediction model for wafer-level packaging using the random forest method. J. Mech. 2021, 37, 28–36. [Google Scholar] [CrossRef]

- Lee, M.S.; Baick, I.; Kim, M.; Kwon, S.H.; Yeo, M.S.; Rhee, H.; Lee, E. Chip to package interaction risk assessment of fcbga devices using fea simulation, meta-modeling and multi-objective genetic algorithm optimization technique. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021; pp. 1–6. [Google Scholar]

- Acharya, P.V.; Lokanathan, M.; Ouroua, A.; Hebner, R.; Strank, S.; Bahadur, V. Machine learning-based predictions of benefits of high thermal conductivity encapsulation materials for power electronics packaging. J. Electron. Packag. 2021, 143, 041109. [Google Scholar] [CrossRef]

- Durgam, S.; Bhosale, A.; Bhosale, V.; Deshpande, R.; Sutar, P.; Kamble, S. Effective computational approach for optimization of temperature on printed circuit board. J. Inst. Eng. Ser. C 2022, 103, 763–776. [Google Scholar] [CrossRef]

- Jing, S.; Li, M.; Li, X.; Yin, P. Optimization of reflow soldering temperature curve based on genetic algorithm. Energy Rep. 2021, 7, 772–782. [Google Scholar] [CrossRef]

- Cecchetti, R.; de Paulis, F.; Olivieri, C.; Orlandi, A.; Buecker, M. Effective pcb decoupling optimization by combining an iterative genetic algorithm and machine learning. Electronics 2020, 9, 1243. [Google Scholar] [CrossRef]

- Sourav, S.; Roy, A.; Cao, Y.; Pandey, S. Machine learning framework for power delivery network modelling. In Proceedings of the 2020 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMCSI), Reno, NV, USA, 28 July–28 August 2020; pp. 10–15. [Google Scholar]

- Mao, M.; Wang, W.; Lu, C.; Jia, F.; Long, X. Machine learning for board-level drop response of bga packaging structure. Microelectron. Reliab. 2022, 134, 114553. [Google Scholar] [CrossRef]

- Jin, H.; Gu, Z.-M.; Tao, T.-M.; Li, E. Hierarchical attention-based machine learning model for radiation prediction of wb-bga package. IEEE Trans. Electromagn. Compat. 2021, 63, 1972–1980. [Google Scholar] [CrossRef]

- Wang, D.; Deng, L.; Zhang, L.; Zhang, F.; Qi, X.; Jin, H. Inverse design for wb-bga package structure by deep learning. In Proceedings of the 2021 13th Global Symposium on Millimeter-Waves & Terahertz (GSMM), Nanjing, China, 23–25 May 2021; pp. 1–3. [Google Scholar]

- Kuo, C.-H.; Hu, A.H.; Hung, L.H.; Yang, K.-T.; Wu, C.-H. Life cycle impact assessment of semiconductor packaging technologies with emphasis on ball grid array. J. Clean. Prod. 2020, 276, 124301. [Google Scholar] [CrossRef]

- Su, D.; Zhao, D.; Zhang, L.; Yang, H.; Wang, C.; Jiang, W. Reliability assessment of flip chip interconnect electronic packaging under thermal shocks. In Proceedings of the 2020 21st International Conference on Electronic Packaging Technology (ICEPT), Guangzhou, China, 12–15 August 2020; pp. 1–4. [Google Scholar]

- Wang, D.; Zhao, Y.; Yao, Q.; Cao, Y.; Lian, B.; Zhang, H. Study on electrical performance of fc and wb in ic ceramic package. In Proceedings of the 2016 3rd International Conference on Materials Engineering, Manufacturing Technology and Control, Taiyuan, China, 27–28 February 2016; pp. 1670–1675. [Google Scholar]

- Venkataiah, C.; Prasad, K.S.; Prasad, T.J.C. Effect of interconnect parasitic variations on circuit performance parameters. In Proceedings of the 2016 International Conference on Communication and Electronics Systems (ICCES), Coimbatore, India, 21–22 October 2016; pp. 1–4. [Google Scholar]

- Khan, R.A.; Muhaisin, M.M.; Roberts, G.W. Extracting rlc parasitics from a flexible electronic hybrid assembly using on-chip esd protection circuits. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 4025–4037. [Google Scholar] [CrossRef]

- Cortes, C.; Vapnik, V. Support-vector networks. Mach. Learn. 1995, 20, 273–297. [Google Scholar] [CrossRef]

- Suykens, J.A.; Vandewalle, J. Least squares support vector machine classifiers. Neural Processing Lett. 1999, 9, 293–300. [Google Scholar] [CrossRef]

- Suykens, J.A.; De Brabanter, J.; Lukas, L.; Vandewalle, J. Weighted least squares support vector machines: Robustness and sparse approximation. Neurocomputing 2002, 48, 85–105. [Google Scholar] [CrossRef]

- Lodhi, H.; Saunders, C.; Shawe-Taylor, J.; Cristianini, N.; Watkins, C. Text classification using string kernels. J. Mach. Learn. Res. 2002, 2, 419–444. [Google Scholar]

- Vert, J.-P.; Tsuda, K.; Schölkopf, B. A primer on kernel methods. Kernel Methods Comput. Biol. 2004, 47, 35–70. [Google Scholar]

- Goldberg, Y.; Elhadad, M. Splitsvm: Fast, space-efficient, non-heuristic, polynomial kernel computation for nlp applications. In Proceedings of the 46th Annual Meeting of the Association for Computational Linguistics on Human Language Technologies: Short Papers, Columbus, OH, USA, 15–20 June 2008; pp. 237–240. [Google Scholar]

- Holland, J.H. Adaptation in Natural and Artificial Systems; The University of Michigan Press: Ann Arbor, MI, USA, 1975. [Google Scholar]

- Holland, J.H. Genetic algorithms. Sci. Am. 1992, 267, 66–73. [Google Scholar] [CrossRef]

- Katoch, S.; Chauhan, S.S.; Kumar, V. A review on genetic algorithm: Past, present, and future. Multimed. Tools 2021, 80, 8091–8126. [Google Scholar] [CrossRef] [PubMed]

- Lewis, C.D. Industrial and Business forecasting METHODS: A Practical Guide to Exponential Smoothing and Curve Fitting; Butterworth-Heinemann: Oxford, UK, 1982. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).