The Effects of Different Anode Positions on the Electrical Properties of Square-Silicon Drift Detector

Abstract

:1. Introduction

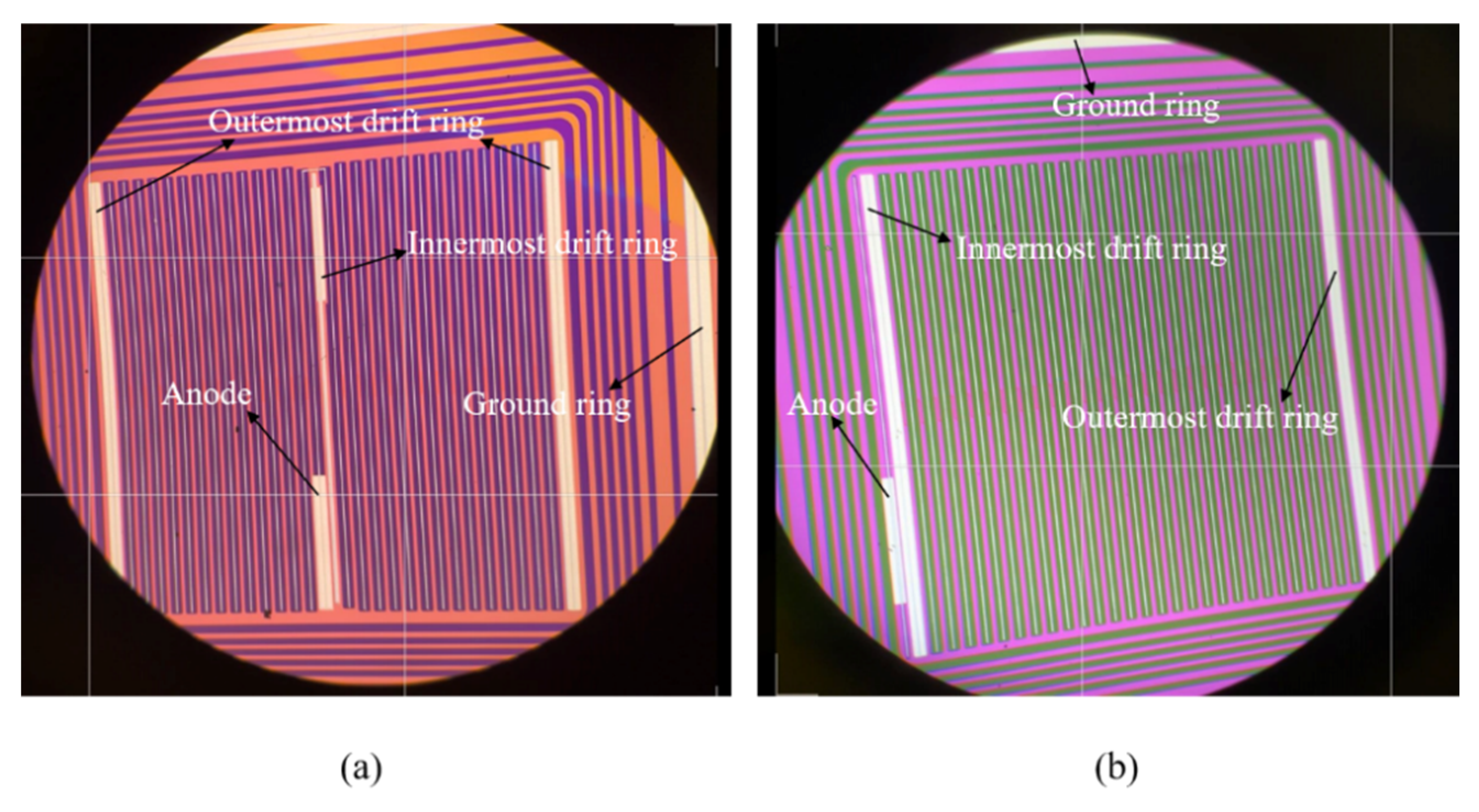

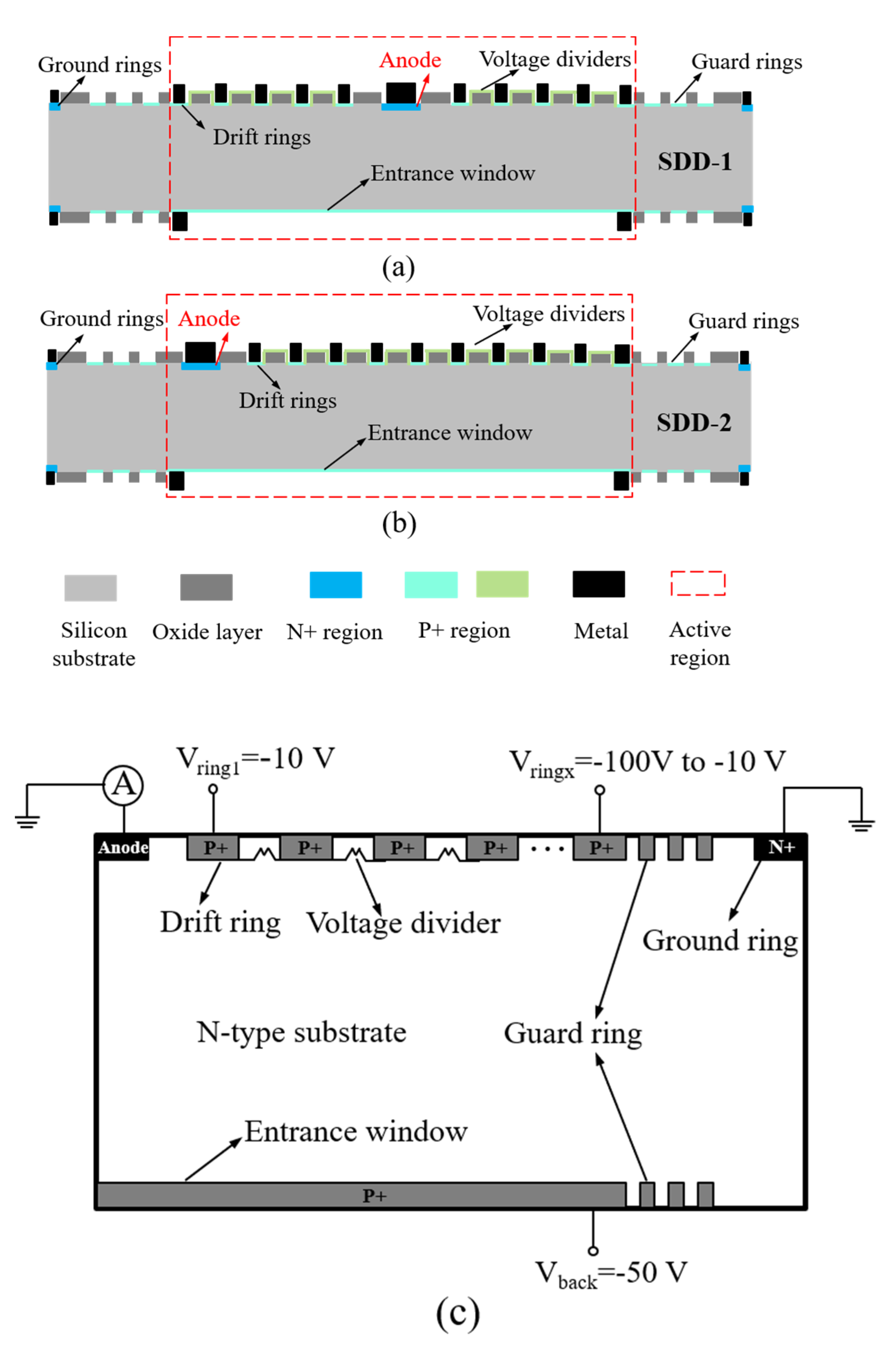

2. Experiment

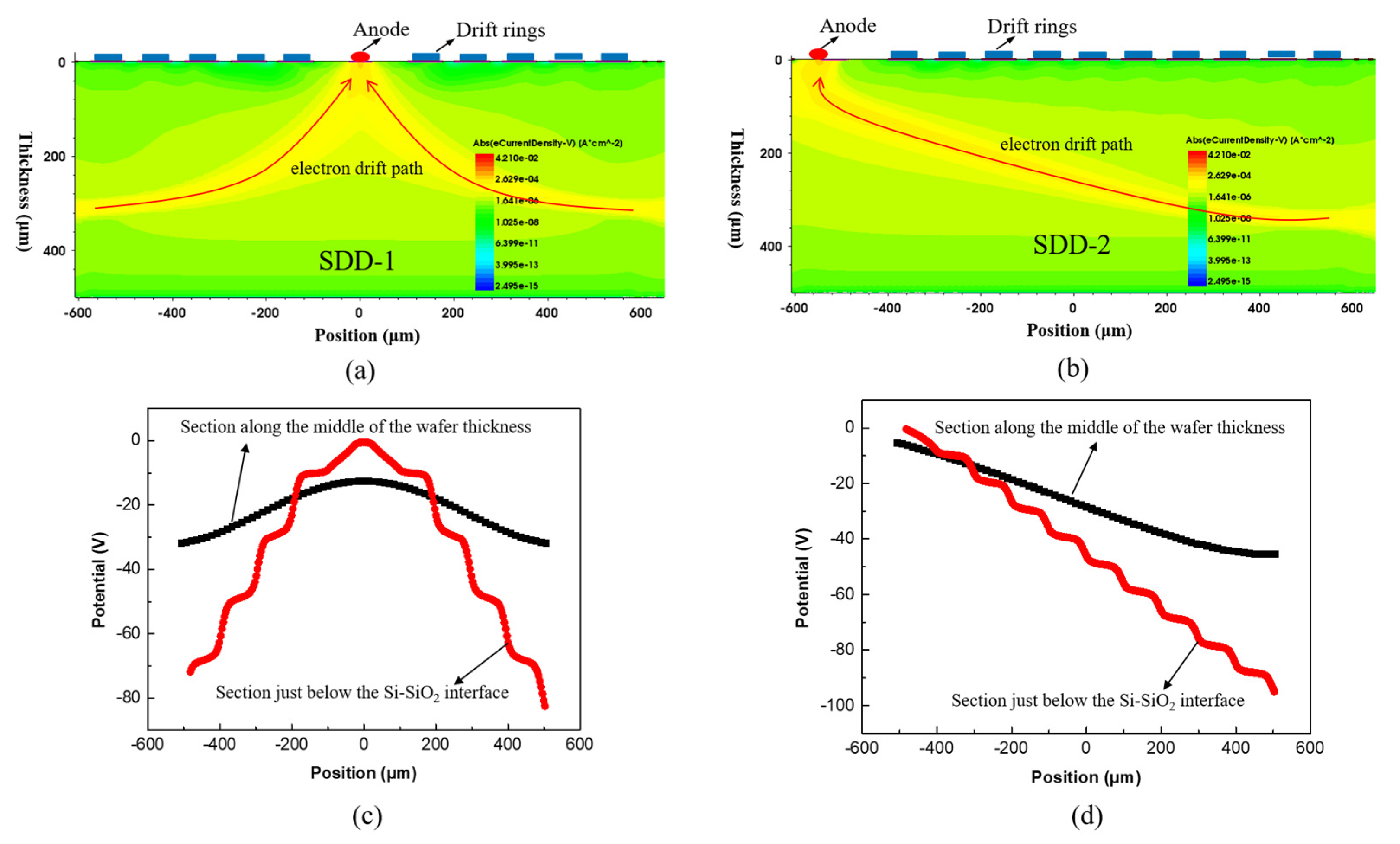

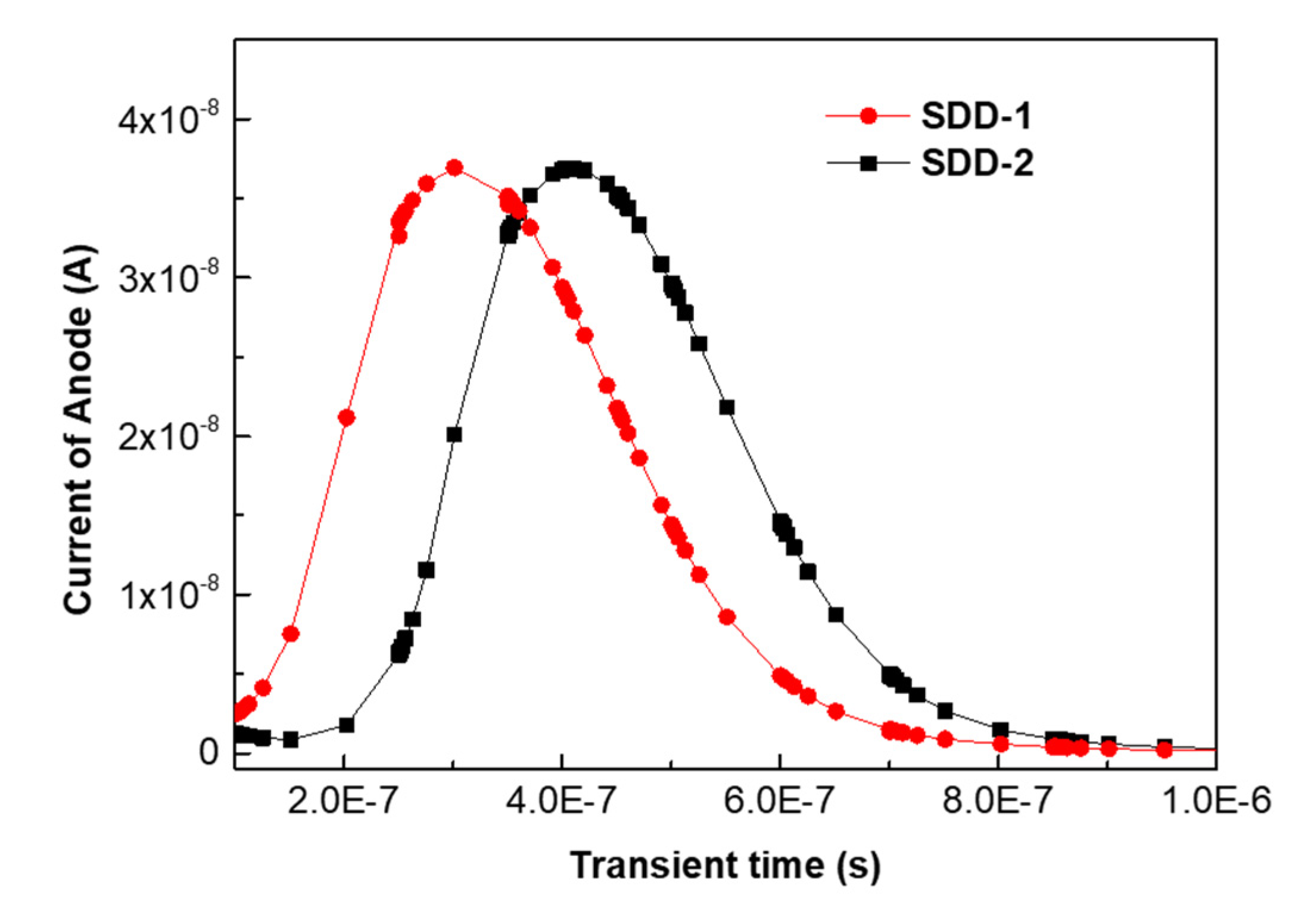

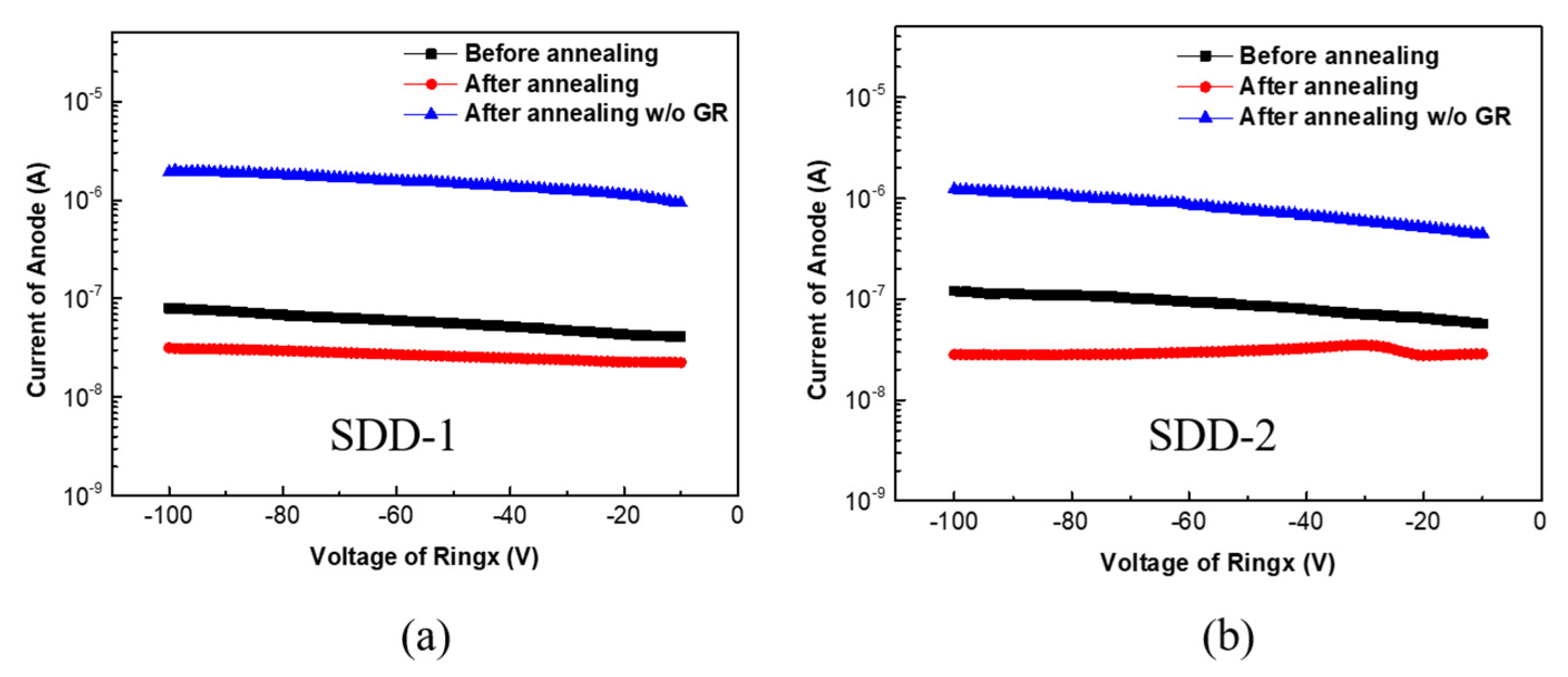

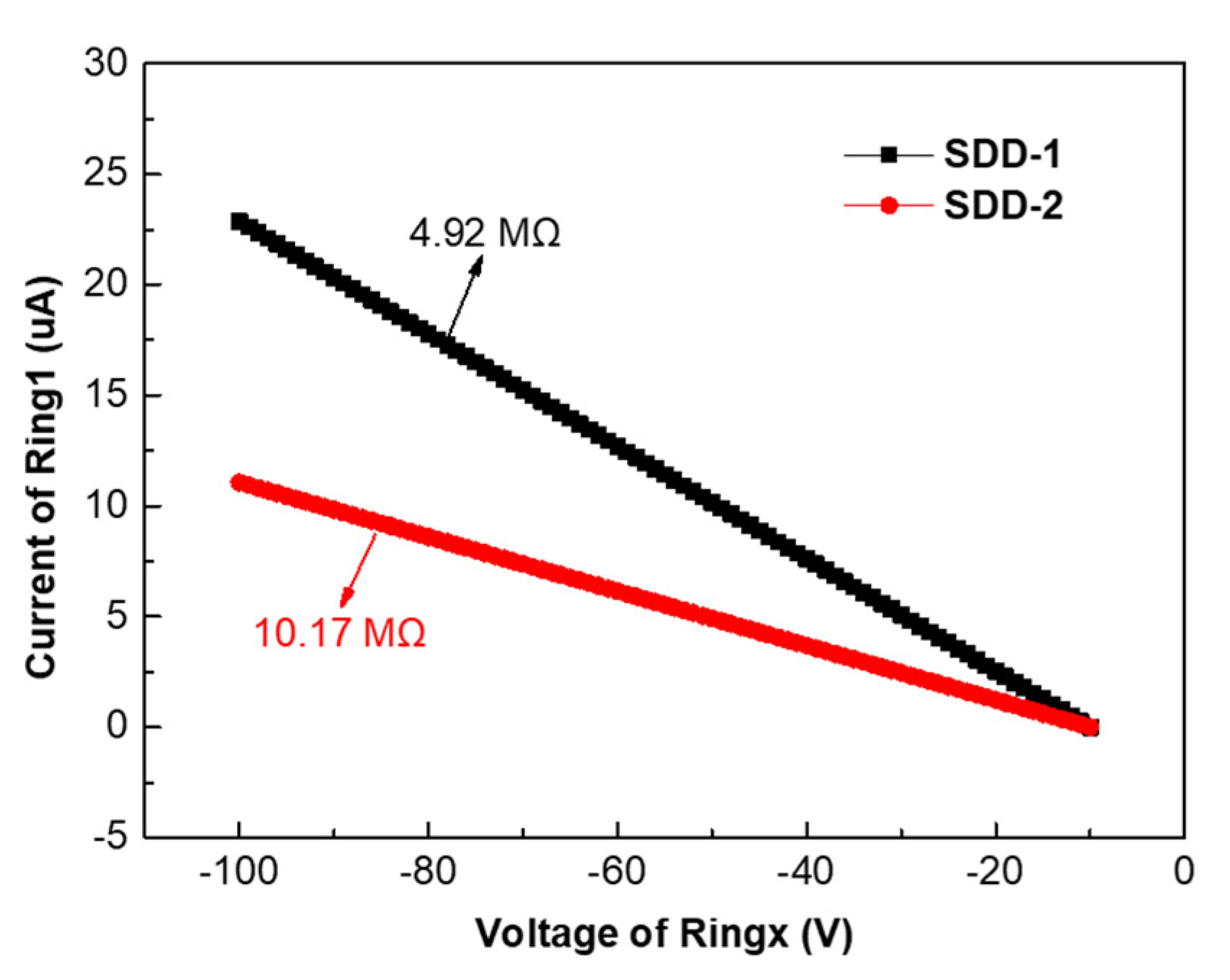

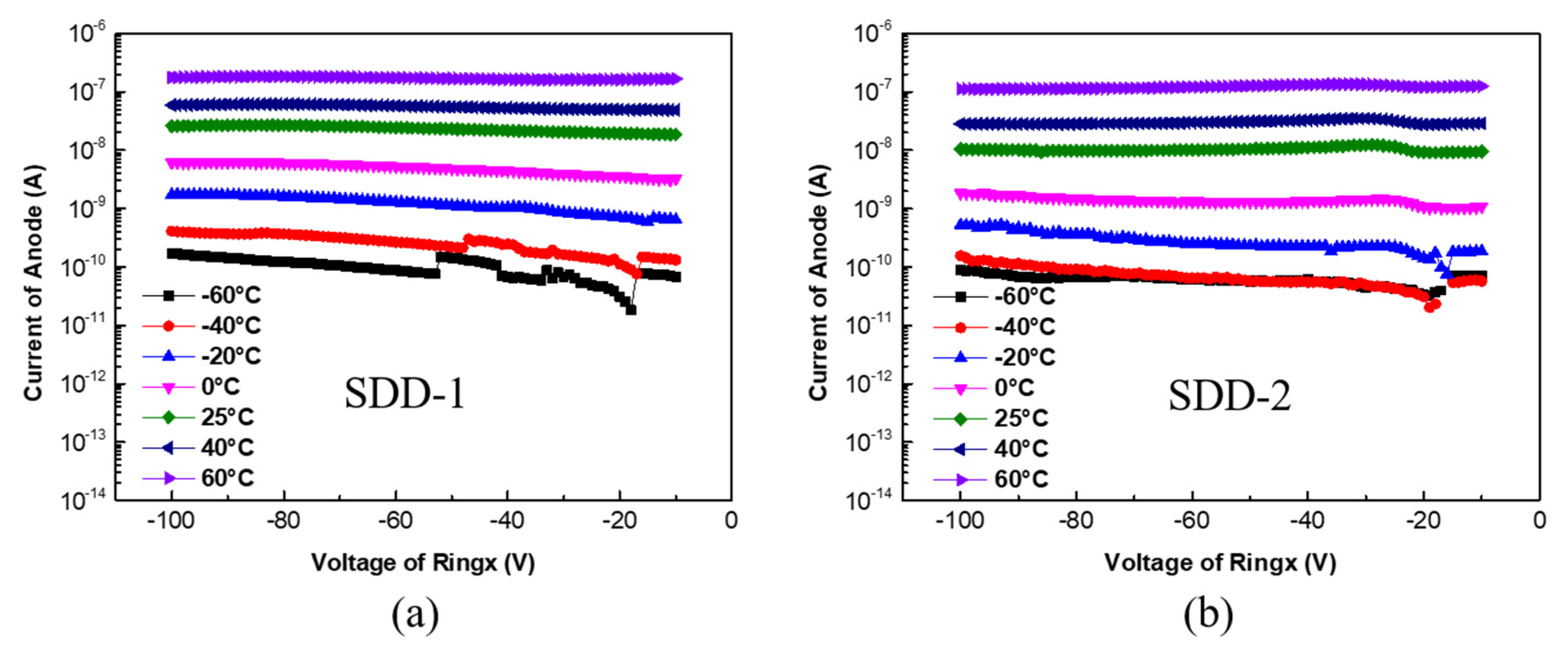

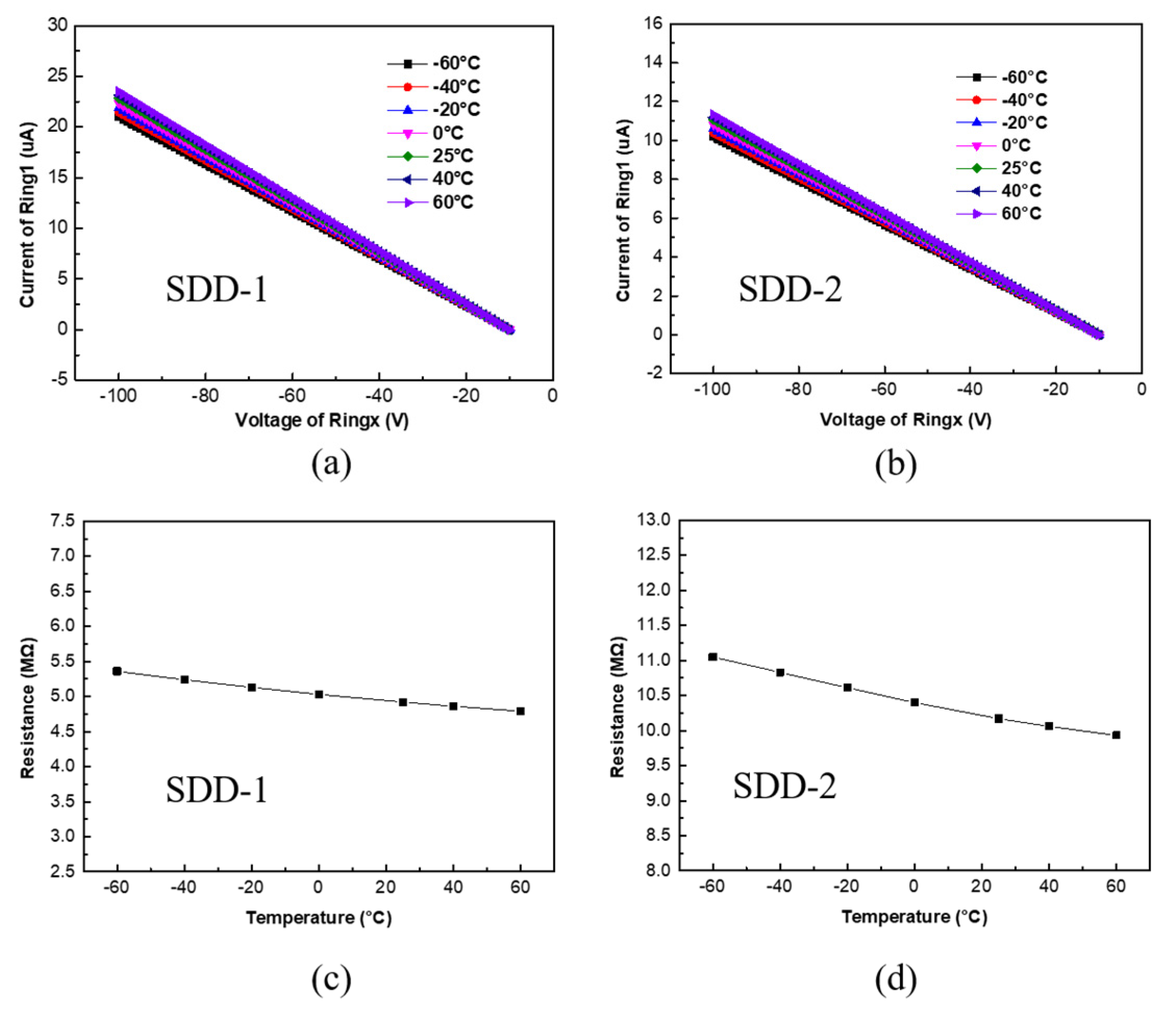

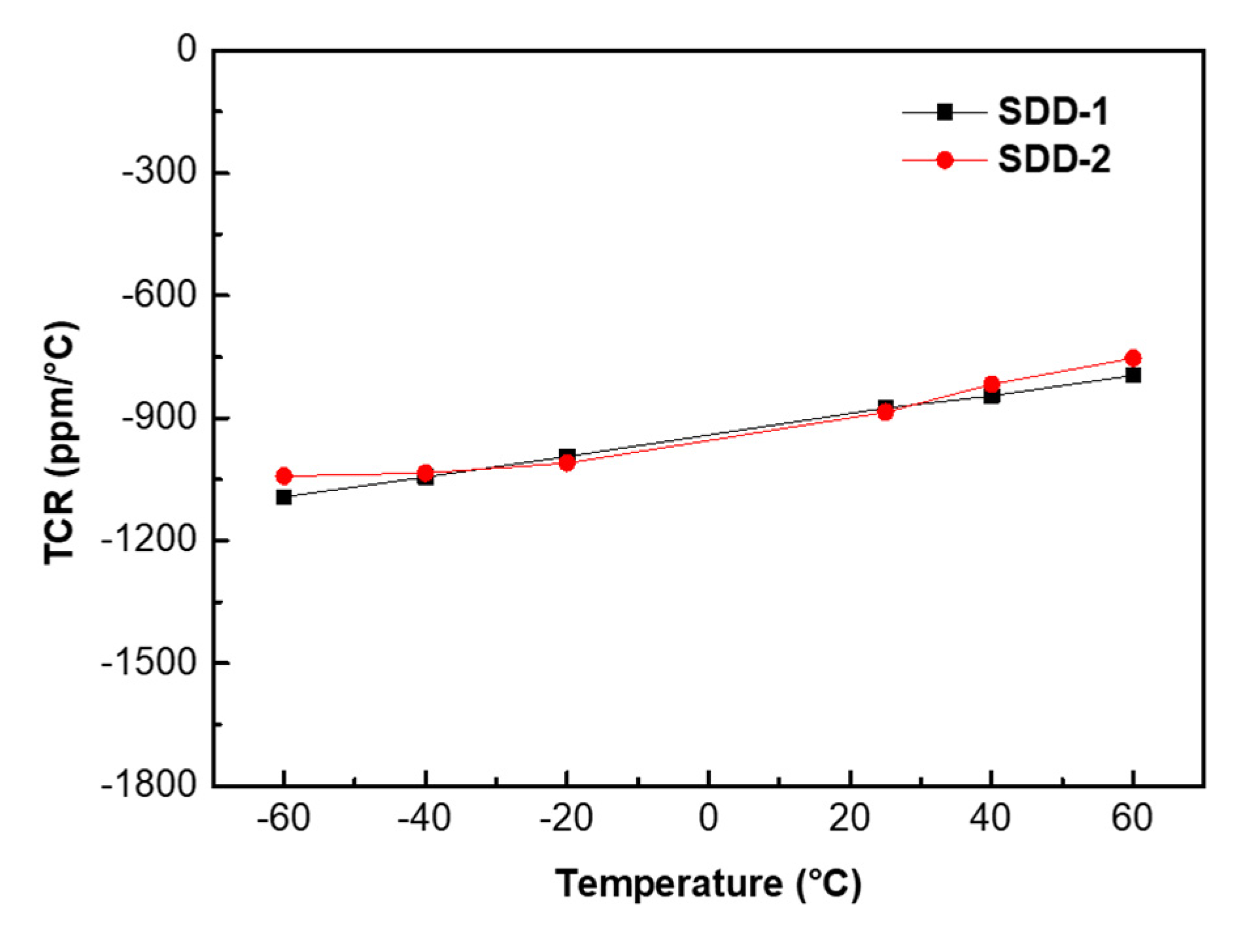

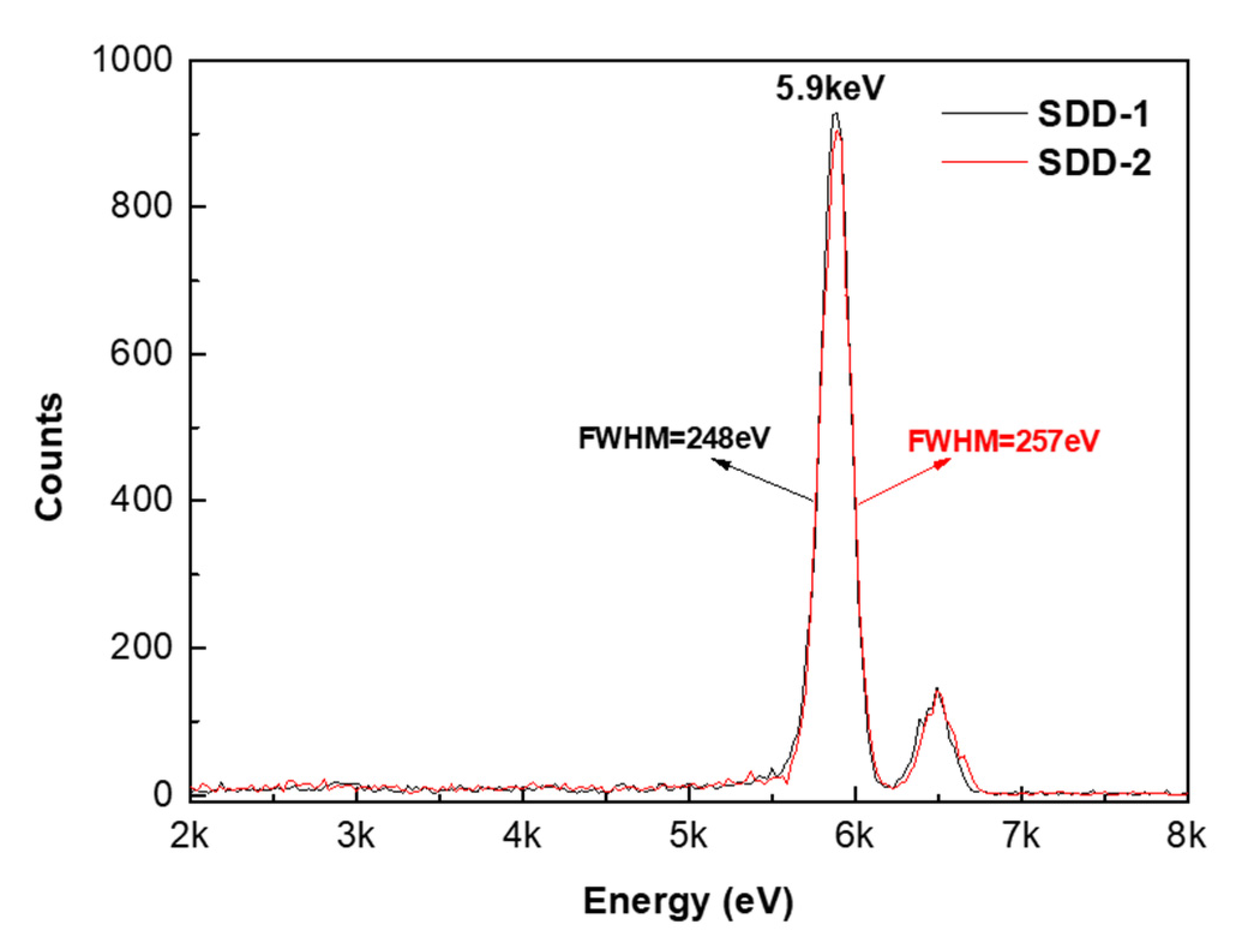

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Gatti, E.; Rehak, P. Semiconductor drift chamber-An application of a novel charge transport scheme. Nucl. Instrum. Methods Phys. Res. 1984, 225, 608–614. [Google Scholar] [CrossRef]

- Vacchi, A.; Castoldi, A.; Chinnici, E.S. Performance of the UA6 large-area silicon drift chamber prototype. Nucl. Instrum. Methods Phys. Res. 1991, 306, 187–193. [Google Scholar] [CrossRef]

- Castoldi, A.; Fiorini, C.; Guazzoni, C.; Longoni, A.; Strüder, L. Semiconductor drift detectors: Applications and new devices. X-ray Spectrom. 1999, 28, 312–316. [Google Scholar] [CrossRef]

- Lechner, P.; Pahlke, A.; Soltau, H. Novel high-resolution silicon drift detectors. X-ray Spectrom. 2004, 33, 256–261. [Google Scholar] [CrossRef]

- Keister, J.W. Silicon photodiodes for absolute soft X-ray radiometry—Art. no. 66890U. Proc. SPIE Int. Soc. Opt. Eng. 2007, 6689. [Google Scholar]

- Soffitta, P.; Arnaud, M.; Murray, S.S.; Costa, E.; Muleri, F.; Takahashi, T.; Campana, R.; Monte, E.D.; Cosimo, S.D.; Evangelista, Y. A set of X-ray polarimeters for the New Hard X-ray Imaging and Polarimetric Mission. Proc. Spie 2010, 7732, 38. [Google Scholar]

- Curceanu, C.; Bartalucci, S.; Bertolucci, S.; Bragadireanu, M.; Cargnelli, M. New Experimental Limit on the Pauli Exclusion Principle Violation by Electrons—The VIP Experiment. Found. Phys. 2011, 1232. [Google Scholar] [CrossRef]

- Watanabe, M.; Egerton, R.F. Evolution in X-ray analysis from micro to atomic scales in aberration-corrected scanning transmission electron microscopes. Microscopy 2022, 71, i132–i147. [Google Scholar] [CrossRef]

- Sareen, R. Further measurements on light pulses using a Silicon Drift Detector R A Sareen. In Using a Semiconductor X-ray Detector to Measure Light Pulses R A Sareen; CRC Press: Boca Raton, FL, USA, 2021. [Google Scholar]

- Quarta, G.; Caricato, A.P.; Provenzano, C.; Marra, M.; Albanese, E.; Vasco, G.; Martino, M.; Maruccio, L.; Calcagnile, L. The newly Installed IBIL (Ion Beam Induced Luminescence) Set-Up at CEDAD-University of Salento: Design and First Applications on Perovskite; IOP Publishing Ltd.: Bristol, UK, 2022. [Google Scholar]

- Strüder, L.; Niculae, A.; Holl, P.; Soltau, H. Development of the Silicon Drift Detector for Electron Microscopy Applications. Microsc. Today 2020, 28, 46–53. [Google Scholar] [CrossRef]

- Samber, B.D.; Bensellam, M.; Malderen, S.; Seiboth, F.; Brückner, D.; Garrevoet, J.; Falkenberg, G.; Jonas, J.C.; Vincze, L. Proof-of-concept for 2D/CT element analysis of entire cryofrozen islets of Langerhans using a cryoloop synchrotron X-ray fluorescence setup. J. Anal. At. Spectrom. 2020, 35, 1368–1379. [Google Scholar] [CrossRef]

- Lechner, P.; Buttler, W.; Fiorini, C.; Hartmann, R.; Weber, U. 8-Multichannel silicon drift detectors for X-ray spectroscopy. Proc. SPIE Int. Soc. Opt. Eng. 2000, 4012, 592–599. [Google Scholar]

- Strueder, L.; Hartmann, R.; Kemmer, S.; Krause, N.; Sampietro, M. 9-Room-temperature x- and gamma-ray spectroscopy with silicon drift detectors. Proc. Spie Int. Soc. Opt. Eng. 2000, 4141, 29–47. [Google Scholar]

- Ramsey, B.D.; Gaskin, J.A.; Elsner, R.F.; Chen, W.; Carini, G.A.; Geronimo, G.D.; Keister, J.; Li, S.; Li, Z.; Siddons, D.P. 10-A low-power, radiation-resistant, Silicon-Drift-Detector array for extraterrestrial element mapping. J. Instrum. 2012, 7, 1313–1318. [Google Scholar] [CrossRef]

- Gaskin, J.; Carini, G.; Chen, W.; Geronimo, G.D.; Siddons, D.P. 11-The Development of a Silicon-Drift-Detector-Based X-ray Spectrometer for Remote Surface Analysis. In Earth and Space 2010: Engineering, Science, Construction, and Operations in Challenging Environments; ASCE Library: Alexander Bell Drive Reston, VA, USA, 2010. [Google Scholar]

- Jiang, S.; Tao, K.; Wang, L.; Luo, W.; Wang, B.; Song, H.; Li, X. Fabrication of ultra-shallow junction by in situ doped amorphous silicon films and its application in silicon drift detectors. J. Phys. D: Appl. Phys. 2022, 55, 025102. [Google Scholar] [CrossRef]

- Jiang, S.; Jia, R.; Tao, K.; Wu, Y.; Liu, S. High-resistance voltage dividers fabricated by thin polysilicon films in silicon drift detectors. J. Mater. Sci. 2019, 30, 6617–6627. [Google Scholar] [CrossRef]

- Liu, S.; Xue, Y.; Jia, R.; Tao, K.; Jiang, S.; Wu, Y.; Sun, H.; Guo, Q.; Zhang, L.; Feng, S. Design and preparation of integrated voltage divider for silicon drift detector by ion implantation. J. Mater. Sci. Mater. Electron. 2019, 30, 10152–10161. [Google Scholar] [CrossRef]

- Wu, Y.; Tao, K.; Jiang, S.; Rui, J.; Huang, Y. The investigation of surface passivation in N-type silicon and its application on Silicon Drift Detector. Chin. Phys. B 2020, 29, 037702. [Google Scholar] [CrossRef]

- Liu, W.; Zhao, X.; Deng, Z.; Li, F.; Qi, H. WASA: A low power front-end ASIC for time projection chambers in 65 nm CMOS. J. Instrum. 2020, 15, P05005. [Google Scholar] [CrossRef]

- Deng, Z.; He, L.; Liu, F.; Liu, Y.; Li, Y.; Yue, Q. An ultra-low noise cryogenic CMOS charge sensitive preamplifier for large volume point-contact HPGe detectors. J. Instrum. 2018, 13, P08019. [Google Scholar] [CrossRef]

- He, L.; Hao, J.; Deng, Z.; Liu, F.; Liu, Y.; Li, Y.; Yue, Q.; Cai, J. Comparison of JFET/MOS/HEMT Based Low Noise Charge Sensitive Preamplifiers for HPGe Detectors in Cryogenic Temperature. J. Phys. Conf. 2019, 1182, 012001. [Google Scholar] [CrossRef]

- Wu, Y.C.; Jhan, Y.R. 3D TCAD Simulation for CMOS Nanoeletronic Devices. In 3D TCAD Simulation for CMOS Nanoeletronic Devices; Springer: Berlin/Heidelberg, Germany, 2018. [Google Scholar]

- Deal, B.; Mckenna, E.; Castro, P. Characteristics of Fast Surface States Associated with SiO[sub 2]-Si and Si[sub 3]N[sub 4]-SiO[sub 2]-Si Structures. J. Electrochem. Soc. 1969, 116, 997. [Google Scholar] [CrossRef]

- Wei, C.; Zheng, L.; Kraner, H.W. Application of the rapid thermal process: Sintering the sputtered aluminum/silicon contact in silicon detector fabrication. In Proceedings of the Nuclear Science Symposium & Medical Imaging Conference, Orlando, FL, USA, 26–31 October 1992; Volume 39, pp. 558–562. [Google Scholar]

- Alok, D.; Baliga, B. SiC device edge termination using finite area argon implantation. IEEE Trans. Electron Devices 1997, 44, 1013–1017. [Google Scholar] [CrossRef]

- Kovalevskii, A.A.; Borisenko, V.E.; Borisevich, V.M.; Dolbik, A.V. Doping Effect on the Structure of Polycrystalline Silicon Films Grown via Silane Pyrolysis. Inorg. Mater. 2005, 41, 1260–1265. [Google Scholar] [CrossRef]

- Sproul, A.B.; Green, M.A. Intrinsic carrier concentration and minority-carrier mobility of silicon from 77 to 300 K. J. Appl. Phys. 1993, 73, 1214–1225. [Google Scholar] [CrossRef]

- Rehak, G.P. Review of semiconductor drift detectors. In Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment; Elsevier: Amsterdam, The Netherlands, 2005. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Luo, W.; Wang, L.; Jia, R.; Tao, K.; Wang, B.; Ouyang, X.; Li, X. The Effects of Different Anode Positions on the Electrical Properties of Square-Silicon Drift Detector. Micromachines 2022, 13, 1496. https://doi.org/10.3390/mi13091496

Luo W, Wang L, Jia R, Tao K, Wang B, Ouyang X, Li X. The Effects of Different Anode Positions on the Electrical Properties of Square-Silicon Drift Detector. Micromachines. 2022; 13(9):1496. https://doi.org/10.3390/mi13091496

Chicago/Turabian StyleLuo, Wei, Longjie Wang, Rui Jia, Ke Tao, Bolong Wang, Xiaoping Ouyang, and Xing Li. 2022. "The Effects of Different Anode Positions on the Electrical Properties of Square-Silicon Drift Detector" Micromachines 13, no. 9: 1496. https://doi.org/10.3390/mi13091496

APA StyleLuo, W., Wang, L., Jia, R., Tao, K., Wang, B., Ouyang, X., & Li, X. (2022). The Effects of Different Anode Positions on the Electrical Properties of Square-Silicon Drift Detector. Micromachines, 13(9), 1496. https://doi.org/10.3390/mi13091496