1. SBD Theory

The GaN-based Schottky barrier diode (SBD) is commonly constructed in three different structures, vertical, quasi-vertical, and lateral, as illustrated in

Figure 1. The latter has both contacts, namely the cathode and anode, on the same surface level [

1]. Although lateral SBDs are easier to fabricate and test, they suffer from larger barrier height in comparison with vertical ones [

2]. However, lateral diodes tend to have a smaller on-resistance and turn-on voltage since current only flows in the drift region, and no substrate loading effects are observed in comparison to vertical diodes. Besides the low on-resistance, lateral SBDs also have a smaller junction capacitance which allow them to be an excellent candidate for high frequency applications.

In this project, the ohmic and Schottky contacts are fabricated laterally on the same surface using the wafer demonstrated in

Figure 2 to form the AlGaN/GaN heterostructure Schottky diode. The wafer consists of GaN epi-layers placed on a foreign substrate such as Si, sapphire, or SiC. The diode fabrication process starts by forming the isolation, either by mesa or ion implantation using Argon, to remove or damage the active layers between devices in order to self-isolate them for accurate measurements purposes. After that, the ohmic metallic stack-up is deposited and annealed to diffuse the metal into the semiconductor to eliminate the barrier between them and to lower the contact resistance. Next, a passivation layer (SiN) is deposited, then selectively etched for anode and bond-pads’ metal deposition. Finally, a second passivation layer is deposited and selectively etched to expose the measurement pads.

Unlike the p-n junction diode, where the current transport is conveyed through the minority carriers, the Schottky diode is a majority-carrier device, which as a result offers a faster switching capability and does not suffer from a charge storage delay resulting in a lower transition time with an instantaneous voltage change across its terminals [

3,

4]. The Schottky diode is based on a metal-semiconductor contact that forms its anode and ohmic, respectively. The latter (ohmic contacts), such as gallium arsenide, Silicon, or gallium nitride, emits a linear current-voltage (

I-

V) relation, where the current is a non-rectified one with a constant conductance value. Schottky (metal such as aluminum, titanium, copper, or gold), on the other hand, is a rectifying-contact formed when the metal (anode) is placed on a semiconductor (cathode) with a different work function, which as a result, creates a barrier height between them producing a nonlinear

I-

V curve. Ideally, the Schottky barrier should pass current only under forward bias conditions and block the current flow otherwise (reversed bias). Generally, due to higher mobility, the Schottky diode utilizes an n-type semiconductor (electrons’ majority-carriers) rather than a p-type (holes’ majority-carriers), which results in a higher cutoff frequency and lower series resistance.

Figure 3 illustrates the characteristic energy band diagram of a Schottky diode formed between a metal and semiconductor before and after the point of contact, where

Φm and

Φs are the energy differences (known as the work function) between the free-space level and fermi levels of the metal and the semiconductor, respectively. When a Schottky contact is generated between the metal and semiconductor, carriers will begin to flow from the semiconductor to the metal to reach a thermodynamic equilibrium condition at which both fermi levels are coincident, and a barrier height is situated between the metal and the semiconductor. This resultant junction potential is called the built-in potential across the diode junction, and it is expressed as:

The formed depletion region between the metal and the semiconductor is positively charged neutralizing the negatively charged metal, and it imitates the behavior of a capacitor’s dielectric. Assuming that electrons are completely ionized,

ns, which is the sheet density in the active channel, can be considered as the electron concentration, and the width of the depletion region is obtained using Equation (2).

where

=

GaN dielectric permittivity (GaN ≈ 7.88 × 10

−11 F/m).

= junction built-in potential

= applied voltage

= sheet density

= charge of electron (≈1.6 × 10−19 )

The charge per unit area

is given by:

By taking the derivative of charge with respect to the junction voltage, the capacitance of the depletion layer per unit area

can be obtained as shown:

Knowing the junction capacitance at zero bias

and the barrier height

, from measurements, Equation (4) can become:

where

m = a grading coefficient used as a reflect of the abruptness of the diode junction [

5], and its value is usually 0.5 <

m < 1, depending on the type of device [

6].

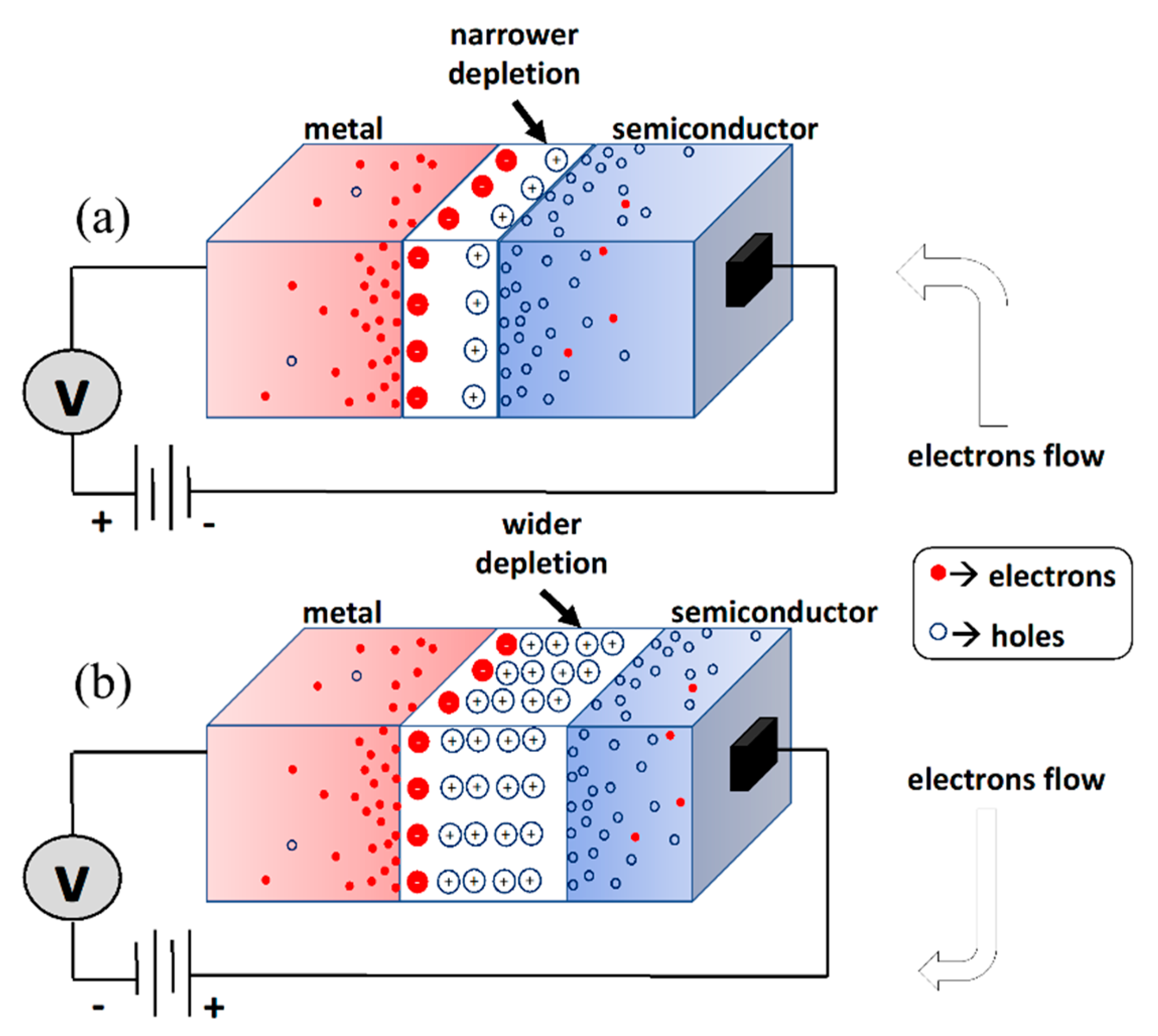

In general, the Schottky diode, under biasing, operates in two modes forward and reverse depending on the applied voltage, and its current is calculated using Equation (6). The applied voltage is utilized to alter the potential barrier magnitude with regard to the desired applications. If a forward operation is required, the potential barrier (

) is decreased and vice versa for a reverse-operational mode as depicted in

Figure 4. On the other hand, at zero-bias, the majority carriers in the Schottky diode require thermal activation to overcome the barrier that resulted from the unequal work function between the metal and semiconductor materials. This type of current transport is known as the thermionic emission, in which the currents flowing from metal to the semiconductor and vice versa are equal in magnitude, and as a result they cancel each other.

Figure 4.

Schottky diode mode of operation as a function of the applied potential, (a) forward (varistor) and (b) reverse (varactor).

Figure 4.

Schottky diode mode of operation as a function of the applied potential, (a) forward (varistor) and (b) reverse (varactor).

where

and

= area of the junction

= Richardson’s constant (GaN ≈ 26 A·cm2·K−2)

= absolute temperature

= Boltzmann’s constant (≈1.38 × 10−23 J·K−1)

= barrier height, which is defined as the difference between the metal work function and the electron affinity (EA = the energy required to move an electron from the conduction band to vacuum) of the semiconductor

= ideality factor; this is a mathematical correction factor added to rectify the diode current nonidealities that arise from practical defects, such as imperfections in the active layer caused by crystal structure damage during the growth process or a contamination within the various fabrication steps affecting the Schottky behavior of the anode. Ideally, its value should be a unity; however, for GaN material, the ideality factor ranges between 1.5 and 2.5 and higher in some cases [

7,

8,

9,

10].

2. Nonlinearities and Harmonics in SBD

As aforementioned, Schottky diodes are majority-carriers-based devices, which in consequence translates into a negligible delay in their switching-time due to a minimal charge storage or lack thereof. Therefore, the DC transfer function, in Equation (6), of the Schottky diode is also applicable for its AC transfer characteristics. Now, in order to identify the origin of harmonics in diodes, rewriting Equation (6) after an RF signal with a DC component (

) is inserted to the diode equation

. The RF signal has an amplitude

and an angular frequency of

; the diode current expression becomes:

where

25mV at room temperature

By applying Taylor’s series expansion followed by trigonometric double-angle identities [

11,

12] only to the exponential term that contains the AC component (RF signal) up to the fifth-order term to observe the mathematical basis by which the harmonics are generated, the diode current expression (7) can be rearranged as:

From the expression (8), it is apparent that the even-terms nonlinearities in the diode produce an additional rectified dc component beside the preceding even harmonics. The odd terms of nonlinearities, on the other hand, only generate odd harmonics. Furthermore, the dc component is usually utilized in power detection circuitry, and the generated harmonics are exploited in electronic circuits such as mixers and frequency multipliers.

3. Series Resistance and Capacitance

To enhance the diode’s performance, it is crucial to have a low series resistance.

Figure 5 illustrates the physical origin of the various components that contribute to the total series resistance of the diode. The diode current expression, which includes the series resistance effect, is given as:

In general, diode series resistance is comprised of four components: the ohmic contact resistance (

), the resistance of the metallic anode (

), the anode-cathode gap resistance (

), and the spreading resistance beneath the anode (

) that includes the aforementioned components that can be expressed as:

where

= anode resistance =

= ohmic contact resistance =

= resistance under the anode-cathode gap =

= spreading resistance below the anode =

= number of anode fingers

= conductivity of anode metal

= contact conductivity

= conductivity of gap between anode and cathode

= thickness of anode metal

,

, and

are the anode width, anode length, and anode-cathode distance, respectively. The factor 2 is used due to ohmic contact being on both sides of the Schottky. Furthermore, the other factor, 3, is added to make up for the anode metal and the spreading resistances being effective and distrusted by three metal contacts (two ohmic and the anode itself) [

13].

However, due to the depletion region being so thin, the Schottky/2DEG diode series resistance, which can be calculated using Equation (11), is largely composed of ohmic contact resistance (

) and the sheet resistance of the semiconductor (

) [

14]. The latter is inversely proportional to the electron mobility (

) and the electron concentration (

) in the 2DEG. Since the contact resistance arises from the ohmic cathodes on both sides of the anode, a factor of 2 is added to

[

14].

Knowing the contact specific resistivity from TLM and the sheet resistance value of the semiconductor from wafer characterization using Hall measurements, Equation (11) can be rewritten and further simplified to:

The total SBD junction capacitance may be calculated using the expression:

Furthermore, in order to predict the diode capacitance accurately, the capacitance per anode finger maybe calculated using this expression [

13]:

However, to consider the effect of the distance between the cathode and anode,

, and the Schottky metallic thickness,

, the capacitance per anode can be given as:

It is manifested from Equation (15) that the zero-bias junction capacitance of the diode is directly and linearly proportional to the width of the anode. On the other hand, the series resistance is decreasing exponentially with the anode width increase. Therefore, a trade-off is evident between the anode width on one side and the junction capacitance and series resistance on the other side. However, since the anode width and the series resistance have an exponential relation, 10–25 µm is a good trade-off range between the junction capacitance and the series resistance. Although lowering both components has a positive effect on the cutoff frequency of the diode, series resistance is more important to be lowered as it is responsible for the power dissipation in circuits such as frequency multipliers.

4. SBD Characterization

The most used figure of merit (FOM) to characterize the varactor diode is the dynamic cutoff frequency, which is a detriment of the maximum operational frequency before the diode is unusable. Practically, the diode actual operational frequency range is usually less than the cutoff frequency, and it can be obtained using the given equation:

where

maximum elastance near breakdown voltage

minimum elastance at zero-bias

Another FOM to characterize the varactor diode (which is simply a diode in a reverse-bias mode) is by analyzing its dynamics (

) at the desired operational frequency (output frequency in case of a multiplier), and it is computed using the expression:

where

= the frequency at which the varactor’s dynamic value is assessed. High

translates into higher efficiency when designing the frequency multiplier as to be shown in a later section.

Additionally, an important FOM is the capacitance or elastance modulation ratio between the maximum and minimum capacitance, or elastance, at zero and near-breakdown voltages, respectively. In order for the diode to exhibit a high cutoff frequency, the

Cmr FOM must be relatively large (>10), which can be calculated using the expression [

15]:

This can be achieved by increasing the number of anodes, which would result in a wider gap between the minimum and maximum capacitance and lower the series resistance. Nevertheless, increasing the number of anodes may have a negative impact on the breakdown voltage and the saturation current.

6. Varactors in Frequency Convertors

A diode-based frequency multiplier is dependent on the nonlinearities of the device. The nonlinearities can be either resistive current-voltage (

I-

V) or reactive charge-voltage (

Q-

V) relations, varistor and varactor, respectively. In this project, the

Q-

V nonlinearities are opted to maximize the efficiency at the expense of operable bandwidth. Theoretically, the available efficiency for the varactor-based multiplier is 100%, whereas the varistor multipliers are limited by a factor of 1/n

2 where n is the multiplication factor of the frequency multiplier (25% maximum efficiency for a double, for example) [

18]. Since a varactor diode topology is chosen, recalling Equation (5), the elastance (

S) which is the reciprocal of the capacitance can be expressed as [

19]:

where

and

, known as the elastance modulation factors, =0.502 and 0.166, respectively, and

= the elastance at the bias.

Equation (20) assumes that the frequency doubler is ideal, and only the fundamental and the second harmonic are present in the system. The relation between

and the bias voltage can be displayed as:

Now, the power in the system that is generated by such capacitance nonlinearities which satisfies the aforementioned assumptions can be written as:

As a result, the input power at the fundamental (

), the output power at the second harmonic (

), and the conversion efficiency (

) can be obtained from Equation (23).

8. Novel Trenched-Anode SBDs

GaN-based SBDs with low onset voltage (V

ON), high reverse-breakdown (V

BV) voltage, and low reverse-current leakage (I

R), high-switching speed (R

ON), and high cutoff frequency (ƒ

c) are essentially required to compete with current III-V technologies. Conventional GaN based SBD DC and RF performance is still limited to their large V

ON, switching loss, and RF leakage when utilizing LR Si substrates. Several researchers recently proposed low V

ON along with low I

R and high V

BV technologies, including a recessed anode, dual-field plates, regrowth cathodes, and a dual-channel field-effect rectifier. However, these approaches require accurate control of anode etching to the 2DEG and a complicated fabrication process, which incorporates reliability issues and extra processing cost. Nevertheless, a 3-D SBDs integrated with a tri-gate MOS structure has shown outstanding DC characteristics at the expense of RF performance owing to the inherently large junction capacitance (

Cj) and series resistance (

RS) [

20]. Therefore, these techniques are only limited to low-frequency applications. To date, most of the research effort into GaN-based SBDs on silicon is predominantly focused on power electronics, with limited literature targeting RF operation. However, achieving high fc while maintaining low IR and superior V

BV remains a challenge. In this work, an optimized multi-channel RF AlGaN/GaN SBDs on LR Si structure is demonstrated using a cost-effective (GaN on LR Si) design which is fully compatible with III-V THz monolithic integrated circuit (THz-MIC) technology. In contrast to conventional SBDs, the newly developed devices significantly enhanced the turn-on characteristics, switching loss, ideality factor (

ηn), and ƒ

c, where V

ON = 0.84 V, R

ON = 0.97 Ω⋅mm, V

BV > 30 V,

ηn = 1.69, and ƒ

c = 0.6 THz were achieved. This is attributed to the direct contact of the Schottky anode to 2DEG at the sidewalls of the multi-mesa trenches along with proper design geometries to suppress substrate coupling effects.

Figure 8 indicates a cross-section of the fabricated AlGaN/GaN SBDs on LR Si using a multi-channel structure, which was simultaneously fabricated with conventional SBDs on the same substrate to allow a precise comparison. A combination of multi-mesa and T-shaped structures was adopted to form the anode to reduce the Schottky barrier height and anode resistivity, respectively. The height (H

F), width (W

F), spacing (S

F), and length (L

F) of the nanowires were ∼50, 41, 89 nm, and 2 μm, respectively. The Anode length (L

A) and anode head length (L

AH) were 0.550 μm and 1.1 μm, respectively, whereas the junction length (L

j) was 4.28 μm. The total physical anode width was 2 × 10 μm, while the effective anode width for the fin-like anode structure was 2 × 5.83 μm.

The epitaxy material used in this work was grown on LR Si (111) (ρ < 40 Ω·cm) provided by Nexperia. The epilayer consists of a 4.65 μm buffer, 20 nm Al0.2Ga0.8N barrier, and 3 nm GaN cap layer. A sheet carrier density of 5.9 × 1012 cm−2 and electron mobility of 1713 cm2/Vs are determined by using Hall measurements.

The device fabrication started with defining the Ti/Pt markers, followed by the deposition of Ti/Al/Ni/Au ohmic contacts and rapid thermal annealing at 790 °C in a N

2 environment to form the cathode. Next, a ∼150 nm depth mesa isolation was performed through Cl

2/Ar-based inductively coupled plasma (ICP). Then, multi-mesa trenches were defined by e-beam lithography and subsequently etched using Cl

2/Ar-based ICP with an etch depth of ∼50 nm. A 100 nm Si

3N

4 passivation layer was then deposited using a low-stress inductively coupled plasma chemical vapor deposition (ICP-CVD) at room temperature. To form the T-shaped anode, E-beam lithography was used to define anode foot trenches through the Si

3N

4 passivation layer using a low damage SF

6/N

2 gas mixture reactive-ion etching (RIE), which was followed by Ni/Au metal stack evaporation to finish the T-shaped anode. Windows in the Si

3N

4 at the cathode areas were etched prior to the deposition of Ti/Au bond pads and a 160 nm Si

3N

4 layer as a final passivation layer. Device fabrication was finalized by Si

3N

4 etching in the measurement pad regions. The dimensions of the fabricated devices are outlined in

Table 1.

8.1. DC Characteristics

Figure 9 indicates the typical

I-

V characteristics of the fabricated conventional and multi-channel structures at room temperature using a linear scale. The diode current (A/mm) and resistance (Ω⋅mm) of conventional and multi-channel structures are normalized by the total physical anode width (2 × 10 μm) and effective anode width (2 × 5.83 μm), respectively.

Figure 9 reveals that incorporating a multi-channel anode structure reduced V

ON from 1.246 to 0.84 V together with improved R

ON from 1.52 to 0.97 to Ω⋅mm. This is attributed to the direct anode contact to the 2DEG, where the anode is wrapped around the narrow AlGaN/GaN bodies.

To analyze these findings further, the semilog

I-

V plot (shown in

Figure 10) is used, which allows the extraction of

ηn and

Φbh. Based on the analytical equations indicated in [

8], both device structures exhibited

ηn between 1 and 2, indicating the presence of conduction mechanism besides a thermionic emission mechanism. An improvement of 14.28% in

ηn (from 1.97 to 1.69) was obtained by the developed multi-channel structure as compared to conventional SBDs. Furthermore, the observed reduction in V

ON when using the new structure corresponds to a reduction of 17.5% in n (from 0.78 to 0.64 eV). However, I

R was slightly increased with the multi-channel structure, where I

R < 38 μA/mm was performed at a reverse voltage of up to 30 V. This is attributed to the additional anode length where the anode is in direct contact to the GaN buffer in the multi-mesa floor regions. The achieved results are comparable to that of SBDs on semi-insulating (SI) SiC with recessed anode and regrowth cathode technologies, with better V

BV and I

R [

2]. This enhancement is mainly attributed to the scale of anode-to-cathode spacing and the use of a T-shaped anode, owing to the reduction in the peak electric field of the Schottky junction.

The following set of equations are used to extract the DC parameters:

rearrangement of the above equation,

then,

where

= 2.718.

= the change of voltage which corresponds to the change in current per decade.

Now, the ideality factor is calculated as:

In addition, the barrier height is deduced using the expression:

where

= the extracted current value from the

I-

V semilog plot at the zero-voltage point;

is the Boltzmann constant;

is the diode temperature; and

is the Richardson constant.

Finally, the series resistance is obtained using equation:

where

= the first higher current at the point where the voltage, due to the slope decrease caused by the voltage drop across the series resistance, is deviated from the straight fit line of the semilog curve.

The extracted values of

Cj as a function of the applied voltage of the fabricated devices are shown in

Figure 11a.

Cj was inversely proportional to the applied reverse voltage, where a sharp drop in

Cj was obtained when changing the voltage form 0 to −2 V. Furthermore, owing to the direct anode contact to 2DEG for multi-channel SBDs,

Cj was significantly reduced at reverse biases beyond −2 V, as compared to conventional SBDs. This reflected a dramatic enhancement in ƒ

c which can be calculated from

RS and

Cj. Therefore, ƒ

c was improved by 32.7% (from 457 to 607 GHz), as shown in

Figure 11b. However, the achieved ƒ

c of the fabricated lateral SBDs on LR Si is still limited to their larger

RS, which mainly depends on material growth quality and cathode contact resistivity, as compared to SBDs realized on GaN on semi-insulating SiC substrates.

8.2. RF Behavior and Small Signal Model

On-wafer small-signal S-parameters’ measurements were performed in the frequency range 0.1 to 110 GHz using an Agilent PNA network analyzer (E8361A) and frequency extenders (N5260A). The system was calibrated with an off-wafer calibration impedance standard substrate (ISS), using a Short-Open-Load-Thru (SOLT) calibration technique.

Figure 12 shows the extracted small-signal circuit model of the devices, which was validated by the good agreement between modeled and measured S-parameters up to 110 GHz, as shown in

Figure 13. This allows the extraction of SBD intrinsic elements, junction resistance (R

j),

Cj, and

Rs, which were used to determine fc of the fabricated devices. As indicated in

Figure 12, unlike SI-substrates, substrate parasitic elements (S

sub and R

sub) are incorporated into the standard SBD circuit model when considering lossy Si as a substrate. Furthermore, C

p and L

P represent pad parasitic components. However, the external parasitic elements have a significant influence on the model at frequencies beyond 20 GHz.

Table 2 shows the extracted circuit element values of conventional and multi-channel structures at no bias (0 V). In contrast to conventional SBDs, an increase in

RS by 15.6% (44.9 to 51.9) and a slight reduction in

Cj by 5.5% (from 49.1 to 46.4 fF) were observed for the newly developed fin-type technology. This is attributed to the additional anode length in the multi-mesa trenches and reduction in n, respectively. In addition, the low capacitance value of C

sub and high resistance value of R

sub (3.1 fF and 10 kΩ, respectively) indicate that the substrate coupling effect could be neglected in both design structures. This was a result of the proper design geometries where the anode-to-cathode separation (2.42 μm) is less than the buffer thickness (4.65 μm).

The developed multi-channel RF lateral AlGaN/GaN SBD on LR Si technology was realized in this work. A V

ON of 0.84 V along with R

ON of 0.97 Ω⋅mm and a

ηn of 1.69 were achieved because of the direct Schottky anode contact to the 2DEG resulting in a

Φbh of 0.64 eV. The fabricated devices exhibited a V

BV of greater than 30 V along with an I

R of less than 38 μm/mm. In addition, a newly proposed small-signal circuit model was introduced up to 110 GHz. The models are exhibiting similar

I-

V characteristics, as shown in

Figure 14, which are comparable to the measured results of the devices. A ƒ

c of 0.6 THz at a reverse bias of −10 V was achieved because of the optimized SBD design structure and geometries. These findings enable an effective methodology for the realization of high-performance sub-THz-MIC topologies.