Investigation of Erase Cycling Induced Joint Dummy Cell Disturbance in Dual-Deck 3D NAND Flash Memory

Abstract

:1. Introduction

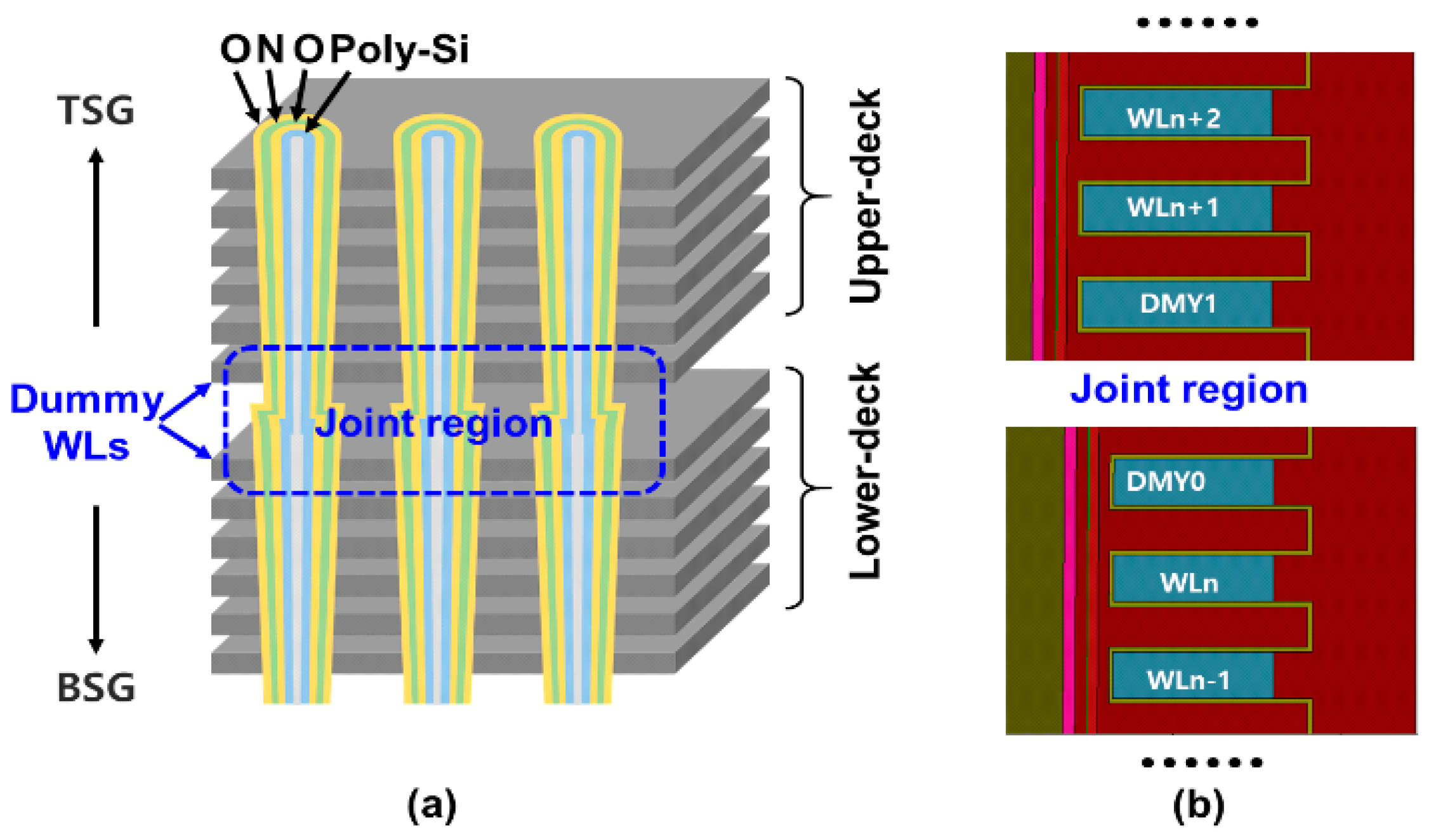

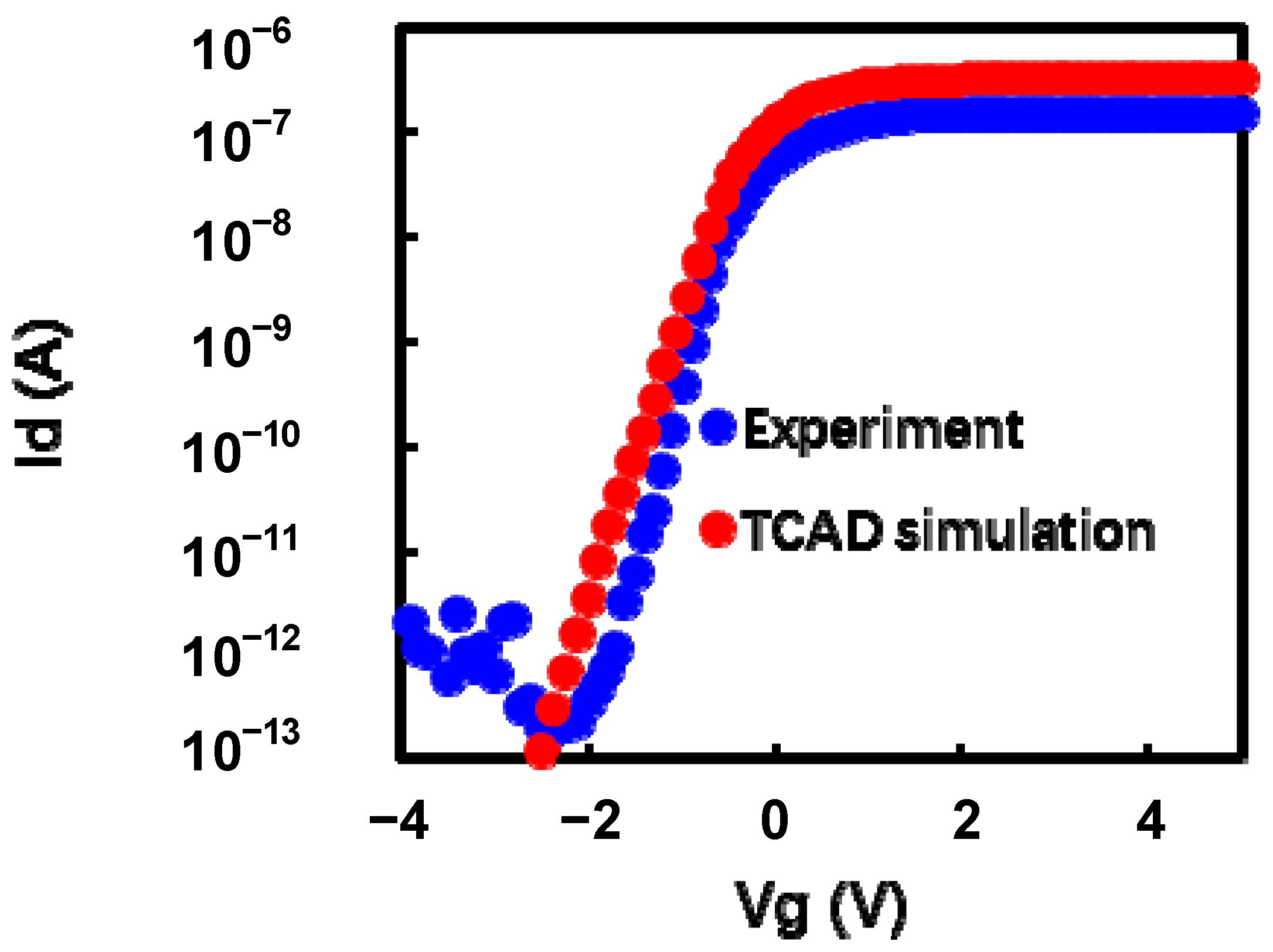

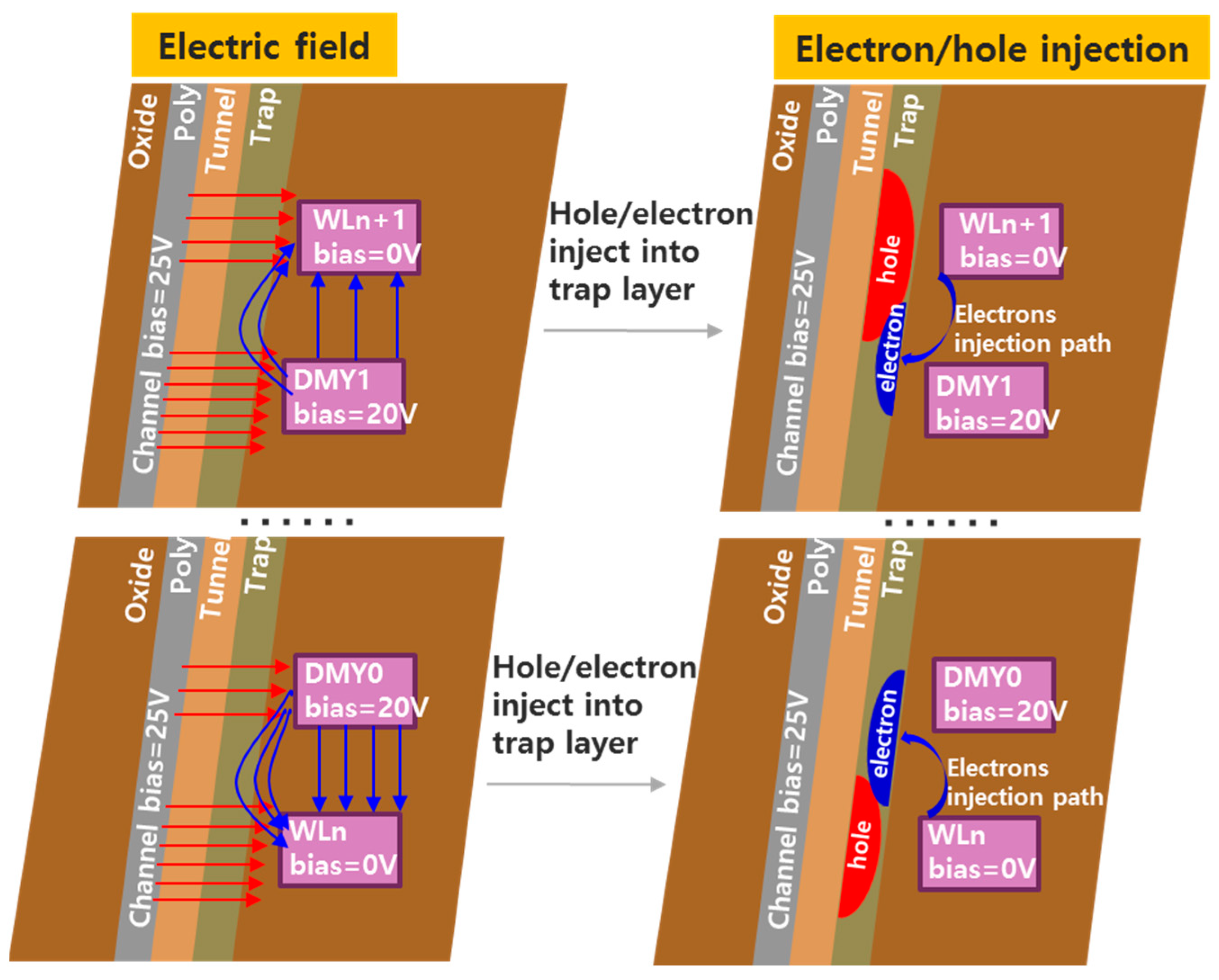

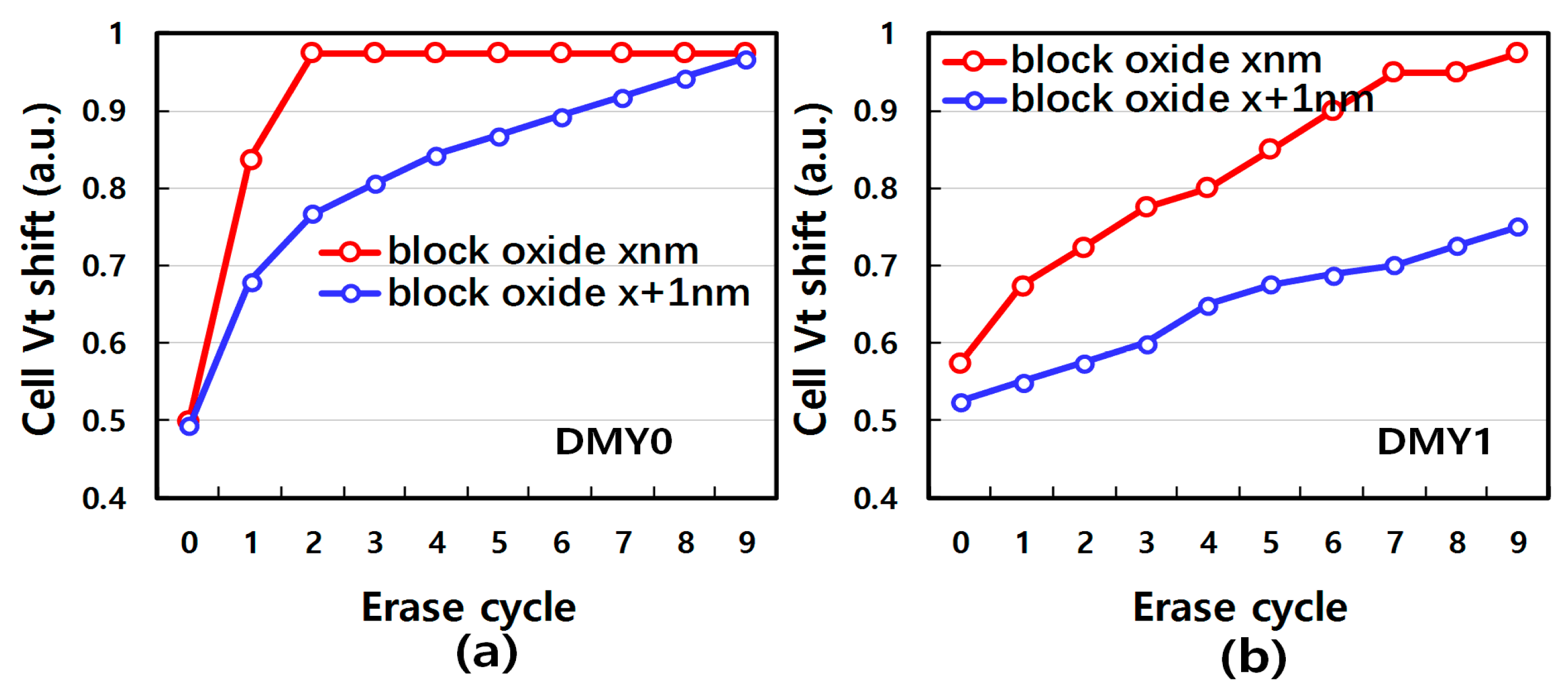

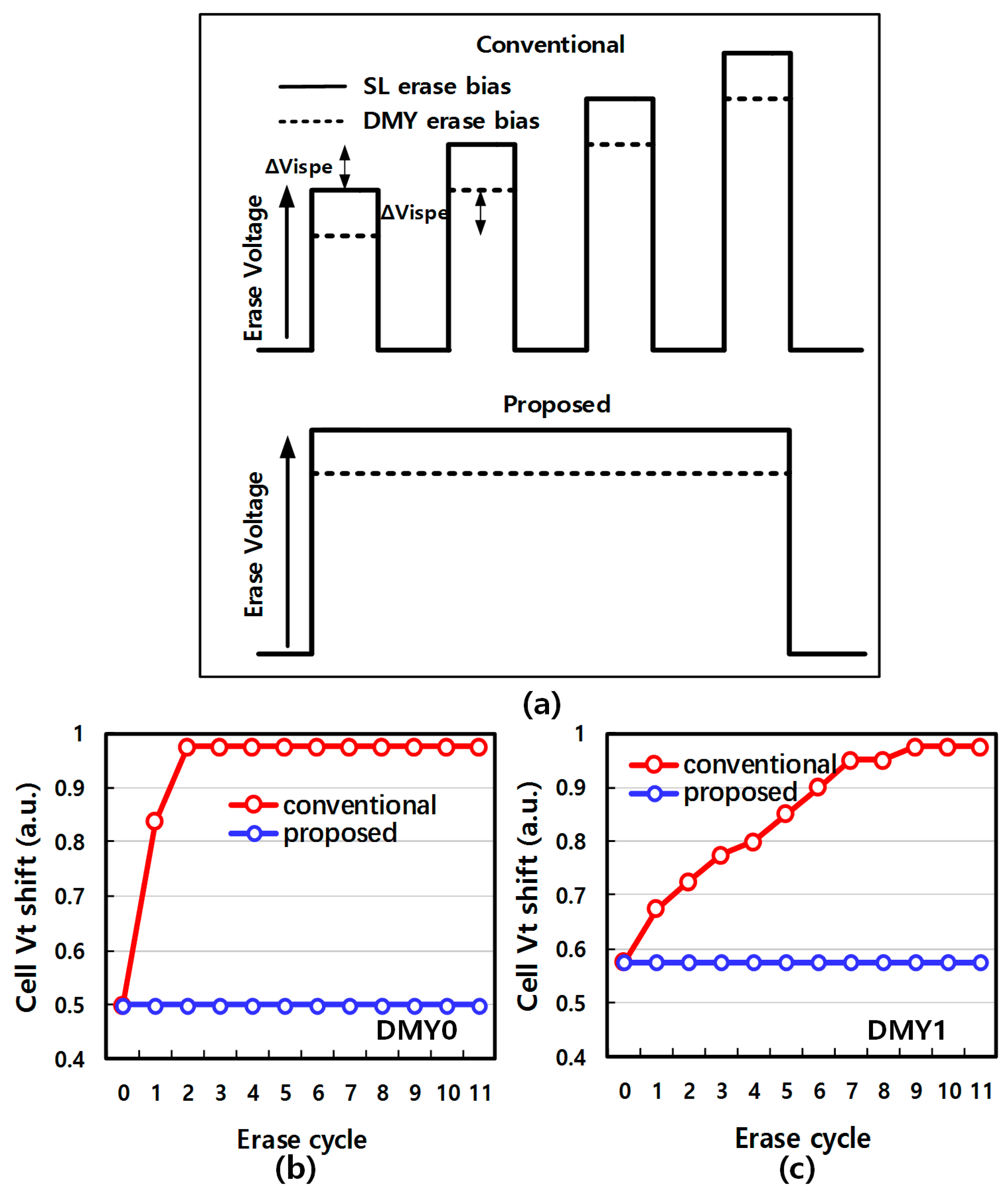

2. Materials and Methods

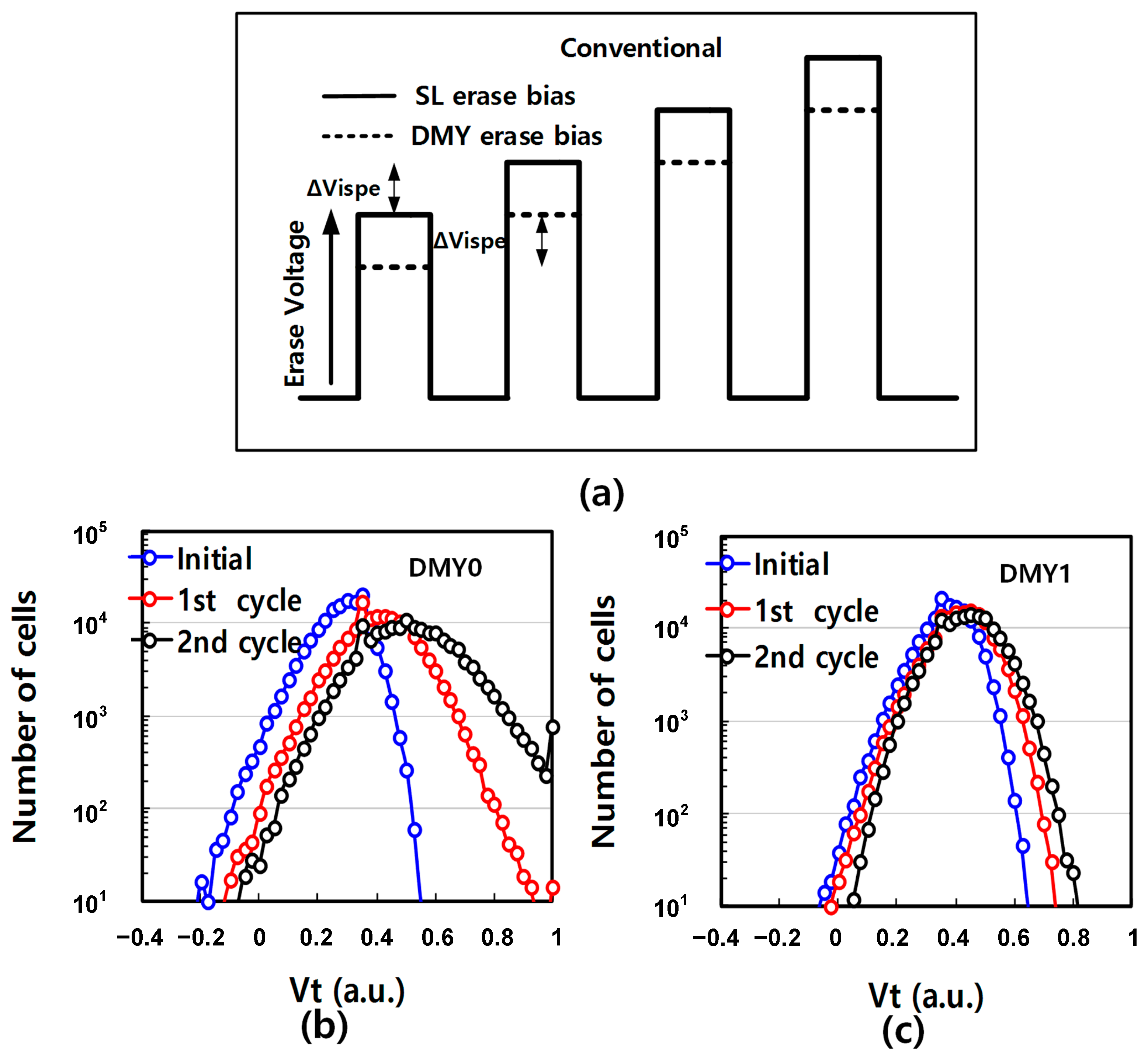

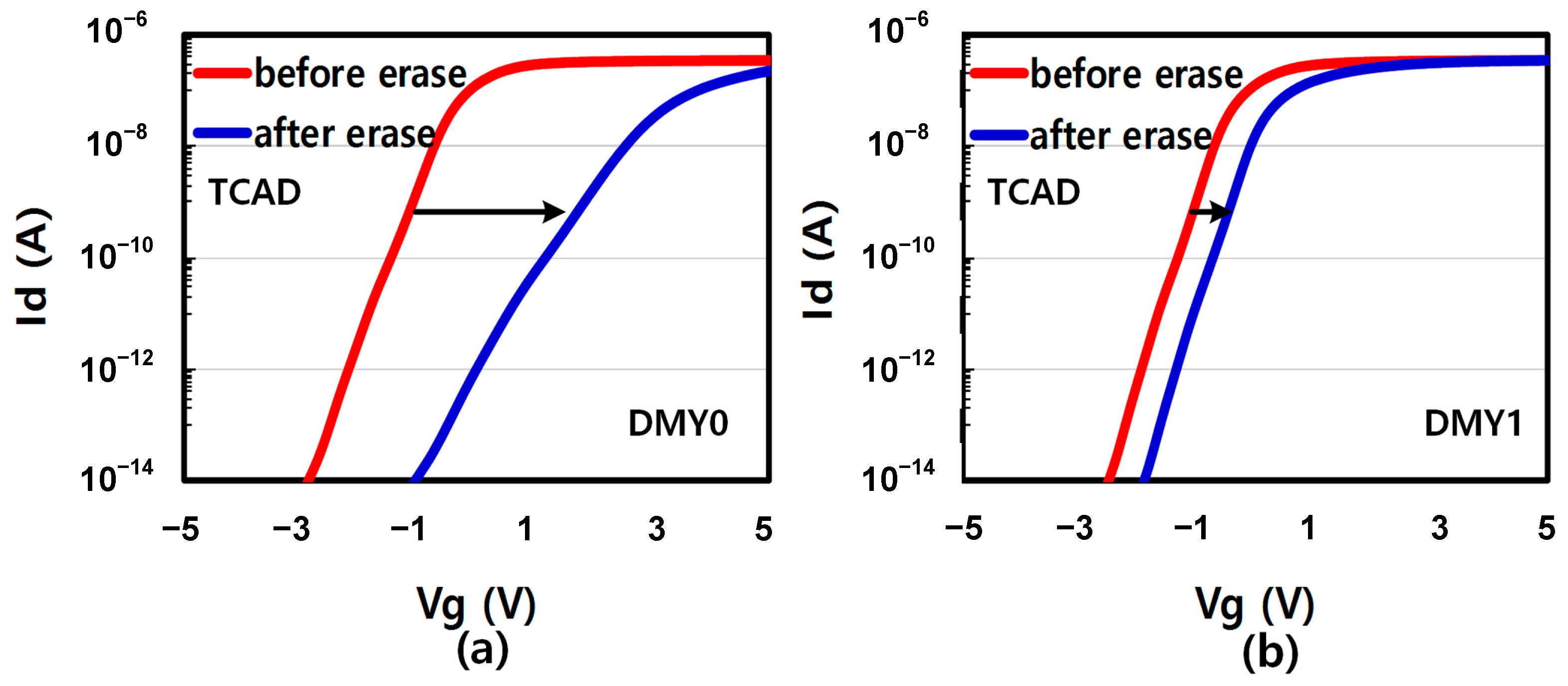

3. Experiments and Simulations

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kim, J.H.; Yim, Y.; Lim, J.; Kim, H.S.; Cho, E.S.; Yeo, C.; Lee, W.; You, B.; Lee, B.; Kang, M.; et al. Highly Manufacturable 7th Generation 3D NAND Flash Memory with COP structure and Double Stack Process. In Proceedings of the 2021 Symposium on VLSI Technology, Kyoto, Japan, 13–19 June 2021. [Google Scholar]

- Park, S.; Lee, J.; Jang, J.; Lim, J.K.; Kim, H.; Shim, J.J.; Yu, M.; Kang, J.; Ahn, S.J.; Song, J. Highly-Reliable Cell Characteristics with 128-Layer Single-Stack 3D-NAND Flash Memory. In Proceedings of the 2021 Symposium on VLSI Technology, Kyoto, Japan, 13–19 June 2021. [Google Scholar]

- Ishimaru, K. Future of Non-Volatile Memory—From Storage to Computing. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 1.3.1–1.3.6. [Google Scholar] [CrossRef]

- Khakifirooz, A.; Balasubrahmanyam, S.; Fastow, R.; Gaewsky, K.; Ha, C.; Haque, R.; Jungroth, O.; Law, S.; Madraswala, A.; Ngo, B.; et al. 30.2 A 1Tb 4b/Cell 144-Tier Floating-Gate 3D-NAND Flash Memory with 40MB/s Program Throughput and 13.8Gb/mm2 Bit Density. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 424–426. [Google Scholar] [CrossRef]

- Ishimaru, K. Challenges of Flash Memory for Next Decade. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Cho, B.; Lee, C.; Seol, K.; Hur, S.; Choi, J.; Chung, C. A New Cell-to-Cell Interference Induced by Conduction Band Distortion near S/D Region in Scaled NAND Flash Memories. In Proceedings of the 2011 3rd IEEE International Memory Workshop (IMW), Monterey, CA, USA, 22–25 May 2011; pp. 1–4. [Google Scholar] [CrossRef]

- Yeh, T.-H.E.; Chen, W.-C.; Hsu, T.-H.B.; Du, P.-Y.P.; Hsieh, C.-C.; Lue, H.-T.; Shih, Y.-H.; King, Y.-C.; Lu, C.-Y. Z-Interference and Z-Disturbance in Vertical Gate-Type 3-D NAND. IEEE Trans. Electron Devices 2016, 63, 1047–1053. [Google Scholar] [CrossRef]

- Chen, W.-C.; Lue, H.-T.; Hsieh, C.-C.; Lee, Y.-C.; Du, P.-Y.; Hsu, T.-H.; Chang, K.-P.; Wang, K.-C.; Lu, C.-Y. A physics-based Quasi-2D model to understand the wordline (WL) interference effects of junction-free structure of 3D NAND and experimental study in a 3D NAND flash test chip. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 4.6.1–4.6.4. [Google Scholar] [CrossRef]

- Yan, L.; Jin, L.; Zou, X.; Ai, D.; Li, D.; Zhang, A.; Wei, H.; Chen, Y.; Huo, Z. Investigation of Erase Cycling Induced TSG Vt Shift in 3D NAND Flash Memory. IEEE Electron Device Lett. 2019, 40, 21–23. [Google Scholar] [CrossRef]

- Jia, X.; Jin, L.; Jia, J.; You, J.; Li, K.; Li, S.; Song, Y.; Min, Y.; Cui, Y.; Wei, W.; et al. A Novel Program Scheme to Optimize Program Disturbance in Dual-Deck 3D NAND Flash Memory. IEEE Electron Device Lett. 2022, 43, 1033–1036. [Google Scholar] [CrossRef]

- Zou, X.; Yan, L.; Jin, L.; Li, D.; Xu, F.; Ai, D.; Zhang, A.; Liu, H.; Wang, M.; Li, W.; et al. Cycling Induced Trap Generation and Recovery Near the Top Select Gate Transistor in 3D NAND. In Proceedings of the 2019 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 31 March–4 April 2019; pp. 1–5. [Google Scholar] [CrossRef]

- Zou, X.; Jin, L.; Jiang, D.; Zhang, Y.; Chen, G.; Huo, Z. Investigation of Cycling-Induced Dummy Cell Disturbance in 3D NAND Flash Memory. IEEE Electron Device Lett. 2018, 39, 188–191. [Google Scholar] [CrossRef]

- Zhang, Y.; Jin, L.; Zou, X.; Liu, H.; Zhang, A.; Huo, Z. A Novel Program Scheme for Program Disturbance Optimization in 3-D NAND Flash Memory. IEEE Electron Device Lett. 2018, 39, 959–962. [Google Scholar] [CrossRef]

- Cheng, T.; Jia, J.; Jin, L.; Jia, X.; Xia, S.; Lu, J.; Li, K.; Luo, Z.; Li, D.; Liu, H.; et al. Investigation of Re-Program Scheme in Charge Trap-Based 3D NAND Flash Memory. IEEE J. Electron Devices Soc. 2021, 9, 640–644. [Google Scholar] [CrossRef]

- Li, D.; Jin, L.; Yan, L.; Jia, X.; Jia, J.; Song, Y.; Zhang, A.; Xu, F.; Hou, W.; Huo, Z.; et al. Impact of low temperature on the TSG Vt shift during erase cycling of 3-D NAND Flash memory. In Proceedings of the 2019 IEEE 26th International Symposium on Physical and Failure Analysis of Integrated Circuits (IPFA), Hangzhou, China, 2–5 July 2019; pp. 1–3. [Google Scholar] [CrossRef]

- Lee, J.G.; Jung, W.J.; Park, J.H.; Yoo, K.-H.; Kim, T.W. Effect of the Blocking Oxide Layer With Asymmetric Taper Angles in 3-D NAND Flash Memories. IEEE J. Electron Devices Soc. 2021, 9, 774–777. [Google Scholar] [CrossRef]

- Jo, H.; Ahn, S.; Shin, H. Investigation and Modeling of Z-Interference in Poly-Si Channel-Based 3-D NAND Flash Memories. IEEE Trans. Electron Devices 2022, 69, 543–548. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| SiO2 relative dielectric constant | 3.9 |

| SiO2 electron affinity | 0.9 eV |

| SiO2 band gap | 8.9 eV |

| SiO2 electron effective mass | 0.39 mo |

| SiO2 electron effective mass | 0.47 mo |

| Si3N4 relative dielectric constant | 7.5 |

| Si3N4 electron affinity | 1.9 eV |

| Si3N4 band gap | 5 eV |

| Si3N4 electron trap energy (from mid band gap) | 1.2 eV |

| Si3N4 electron cross section | 1 × 10−20 cm2 |

| Si3N4 electron trap density | 3 × 1019 cm−3 |

| Si3N4 electron trap volume | 1 × 10−10 um−3 |

| Si3N4 relative dielectric constant | 1 × 10−10 um−3 |

| Si3N4 hole trap energy (from mid band gap) | −1.35 eV |

| Si3N4 hole cross section | 1 × 10−17 cm2 |

| Si3N4 electron trap density | 1.35 × 1017 cm−3 |

| Si3N4 electron trap volume | 1 × 10−10 um−3 |

| Poly-Si/SiO2 interface donor/accepter trap density (peak at valance band) | 5 × 1013 cm2 |

| Poly-Si/SiO2 interface donor/accepter trap Gaussian distribution sigma | 0.05 eV |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

You, K.; Jin, L.; Jia, J.; Huo, Z. Investigation of Erase Cycling Induced Joint Dummy Cell Disturbance in Dual-Deck 3D NAND Flash Memory. Micromachines 2023, 14, 1916. https://doi.org/10.3390/mi14101916

You K, Jin L, Jia J, Huo Z. Investigation of Erase Cycling Induced Joint Dummy Cell Disturbance in Dual-Deck 3D NAND Flash Memory. Micromachines. 2023; 14(10):1916. https://doi.org/10.3390/mi14101916

Chicago/Turabian StyleYou, Kaikai, Lei Jin, Jianquan Jia, and Zongliang Huo. 2023. "Investigation of Erase Cycling Induced Joint Dummy Cell Disturbance in Dual-Deck 3D NAND Flash Memory" Micromachines 14, no. 10: 1916. https://doi.org/10.3390/mi14101916

APA StyleYou, K., Jin, L., Jia, J., & Huo, Z. (2023). Investigation of Erase Cycling Induced Joint Dummy Cell Disturbance in Dual-Deck 3D NAND Flash Memory. Micromachines, 14(10), 1916. https://doi.org/10.3390/mi14101916