Mechanical Reliability Assessment of a Flexible Package Fabricated Using Laser-Assisted Bonding

Abstract

1. Introduction

2. Experimental Procedure

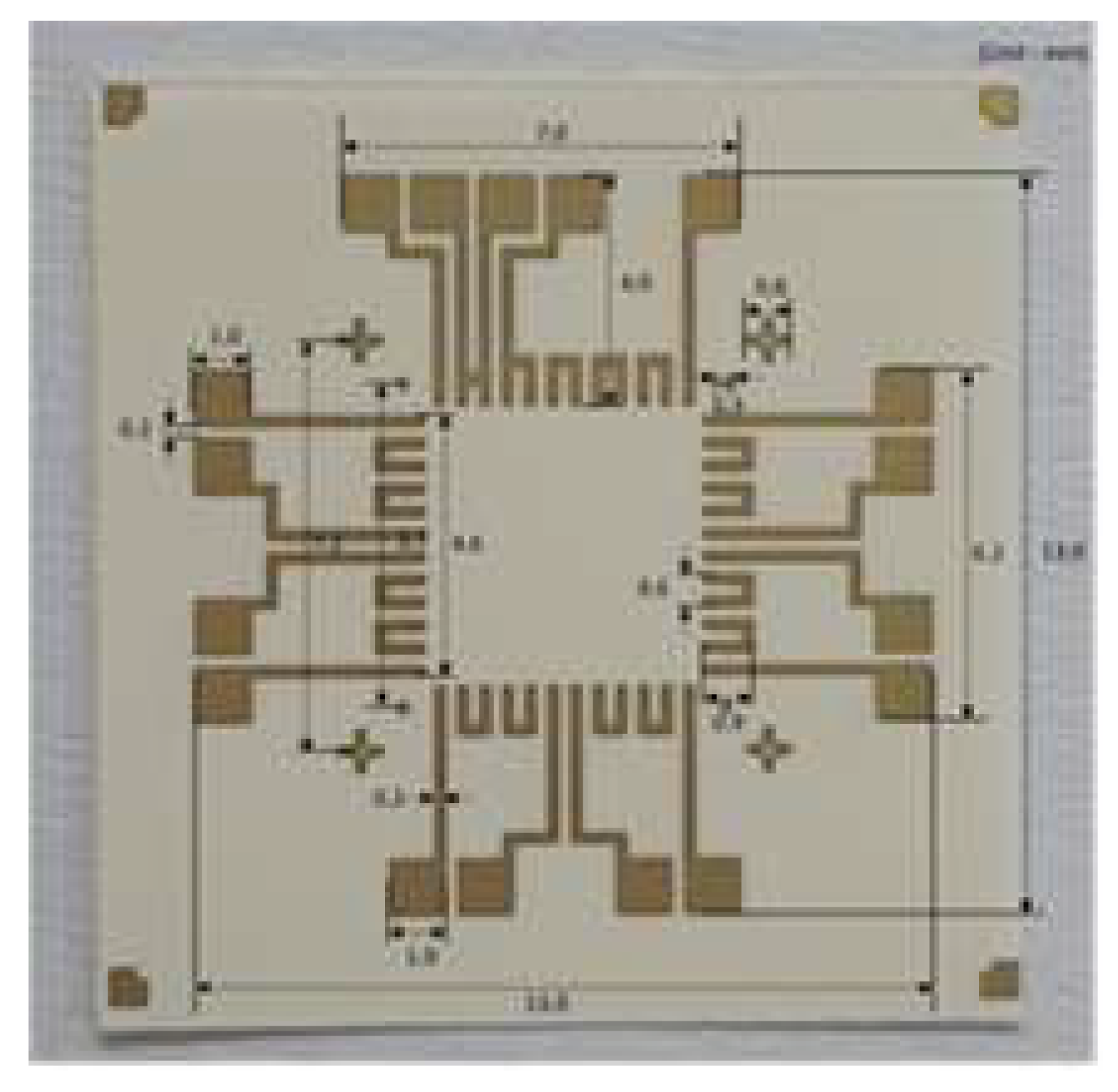

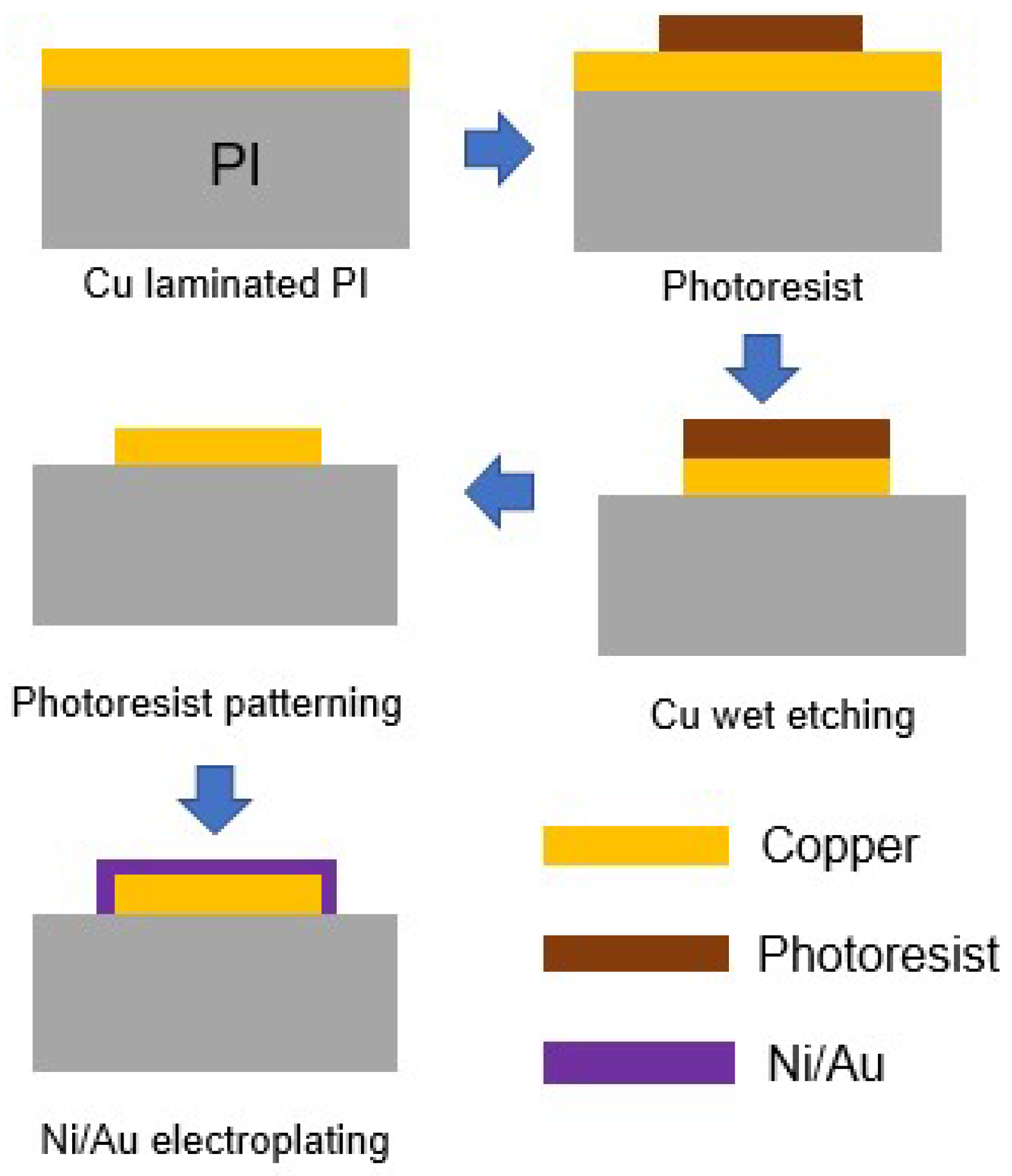

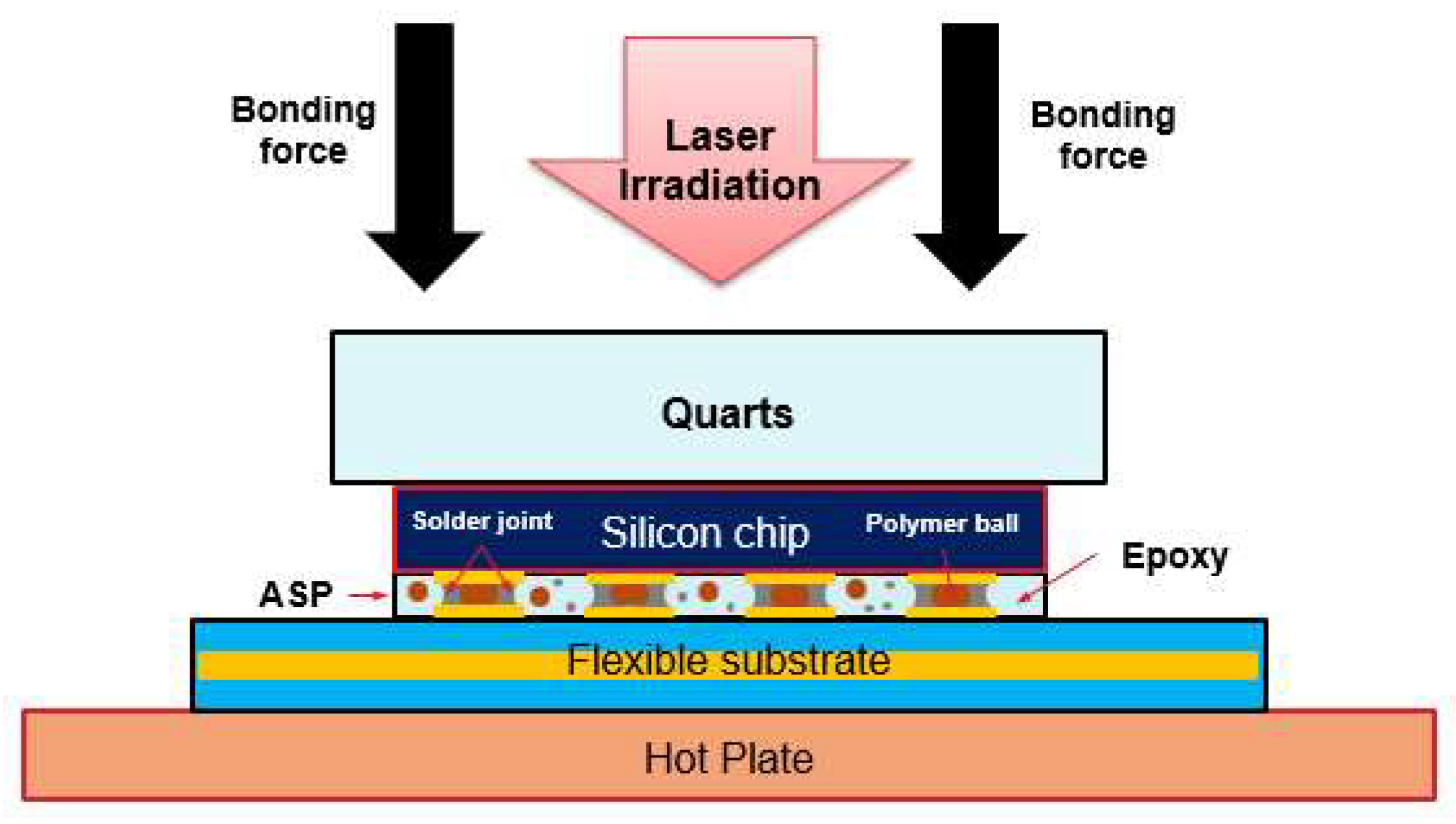

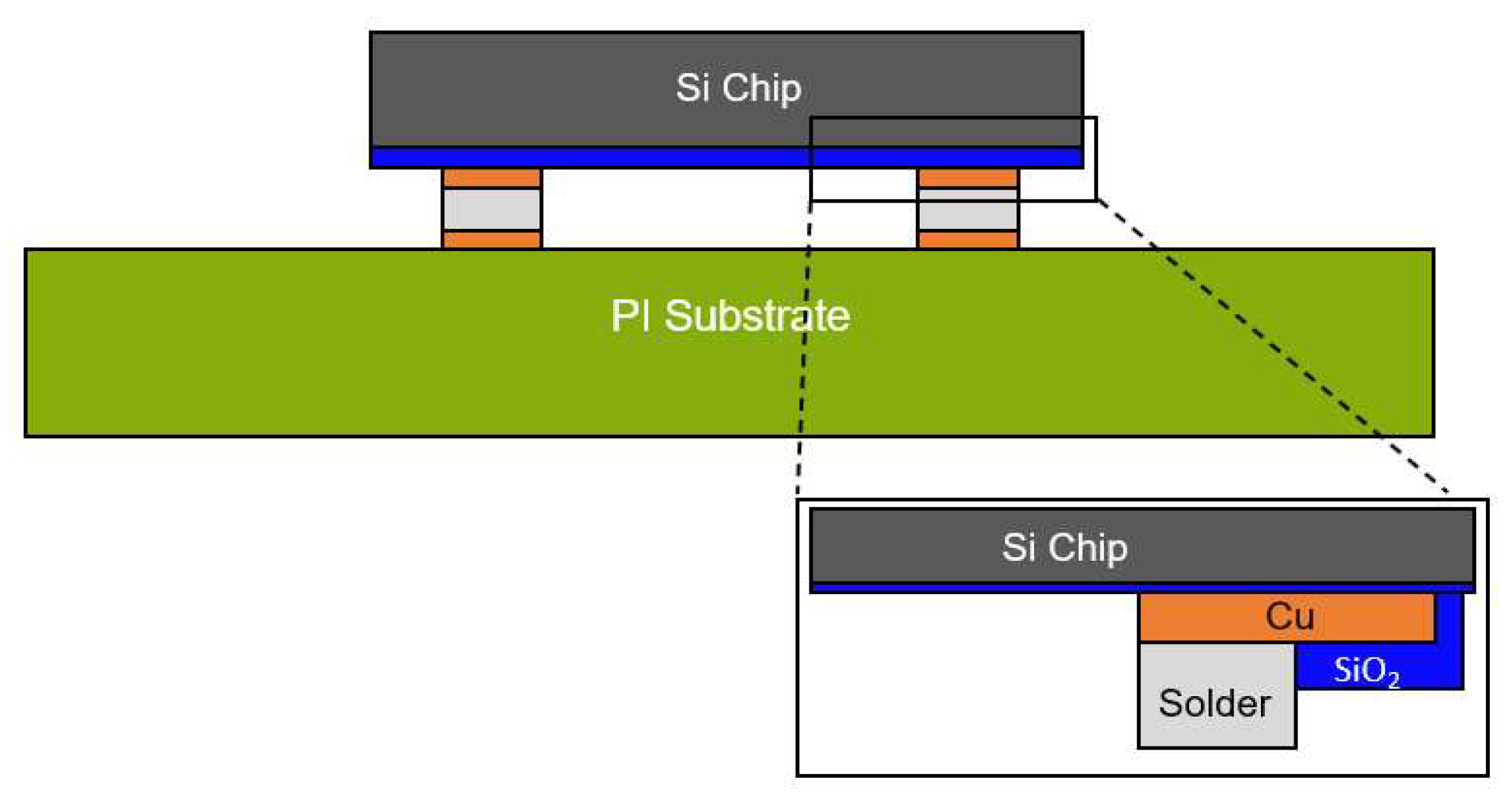

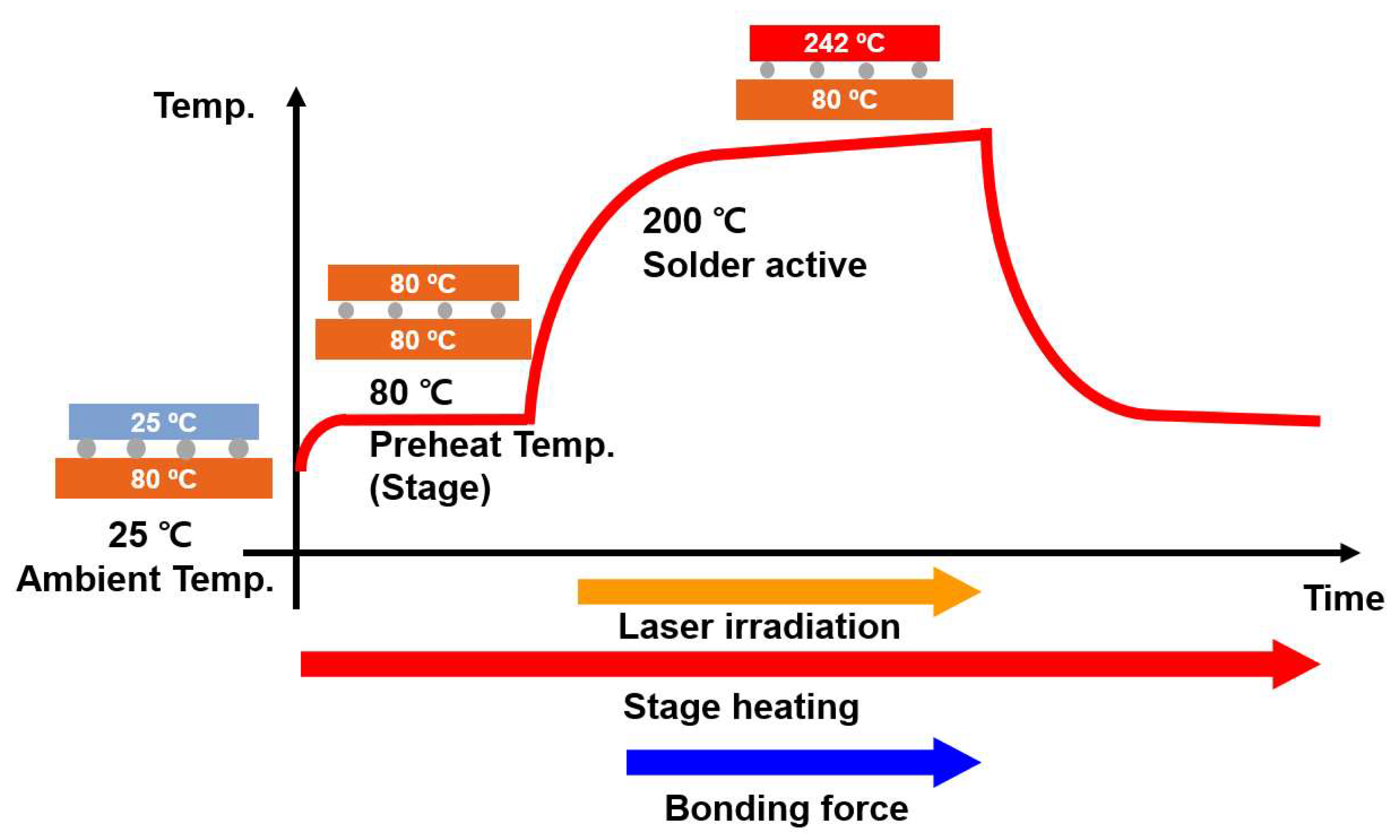

2.1. Fabrication of the Flexible Package

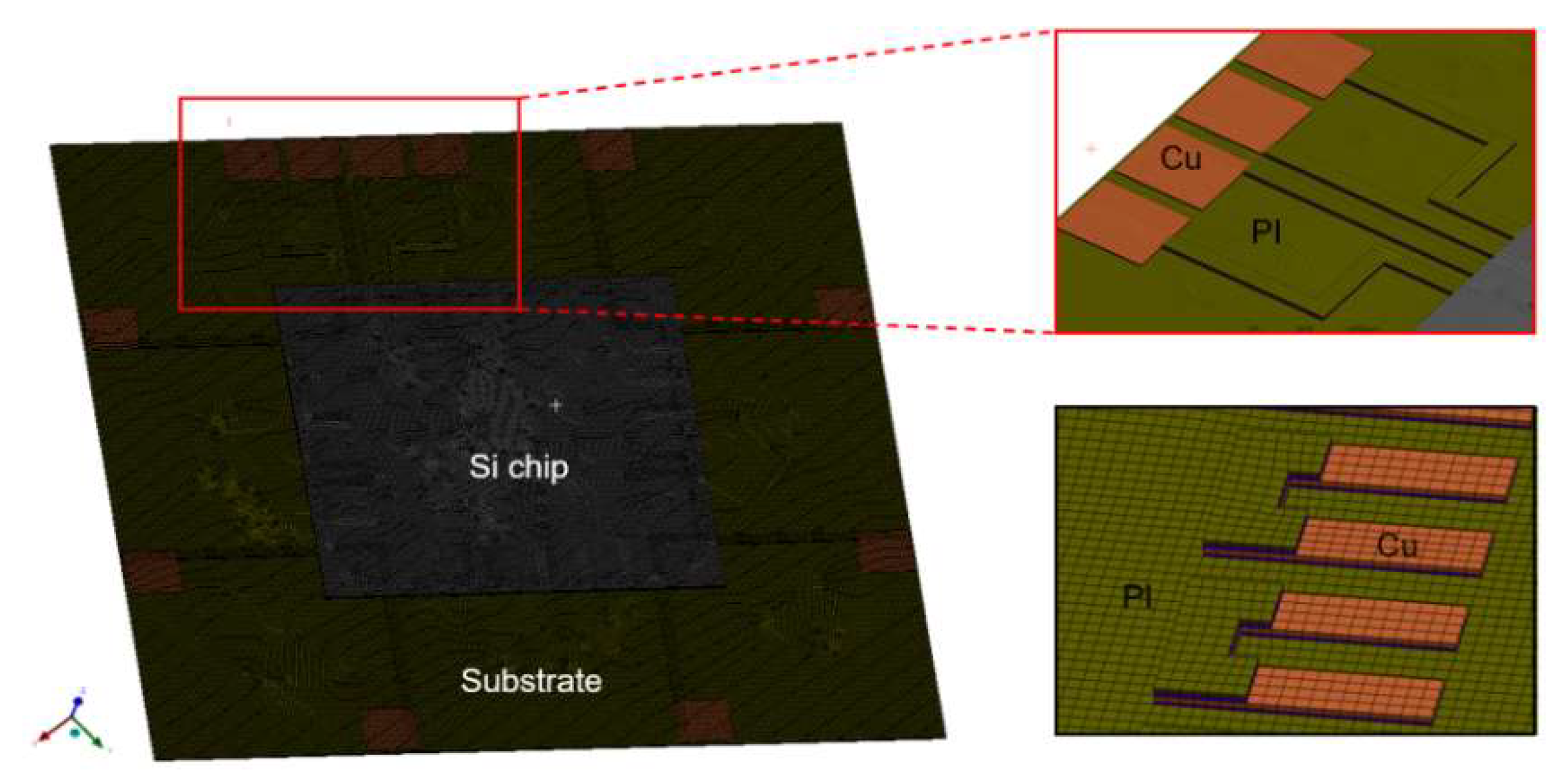

2.2. Numerical Modeling

3. Results and Discussion

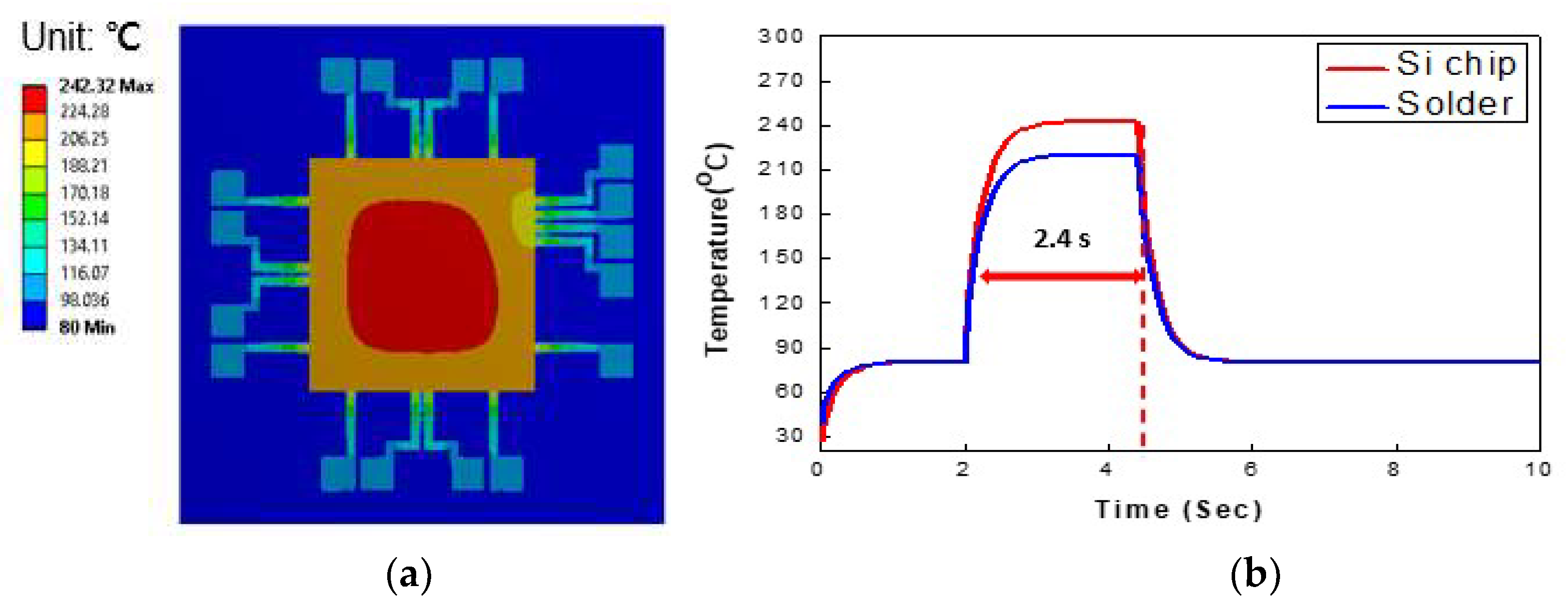

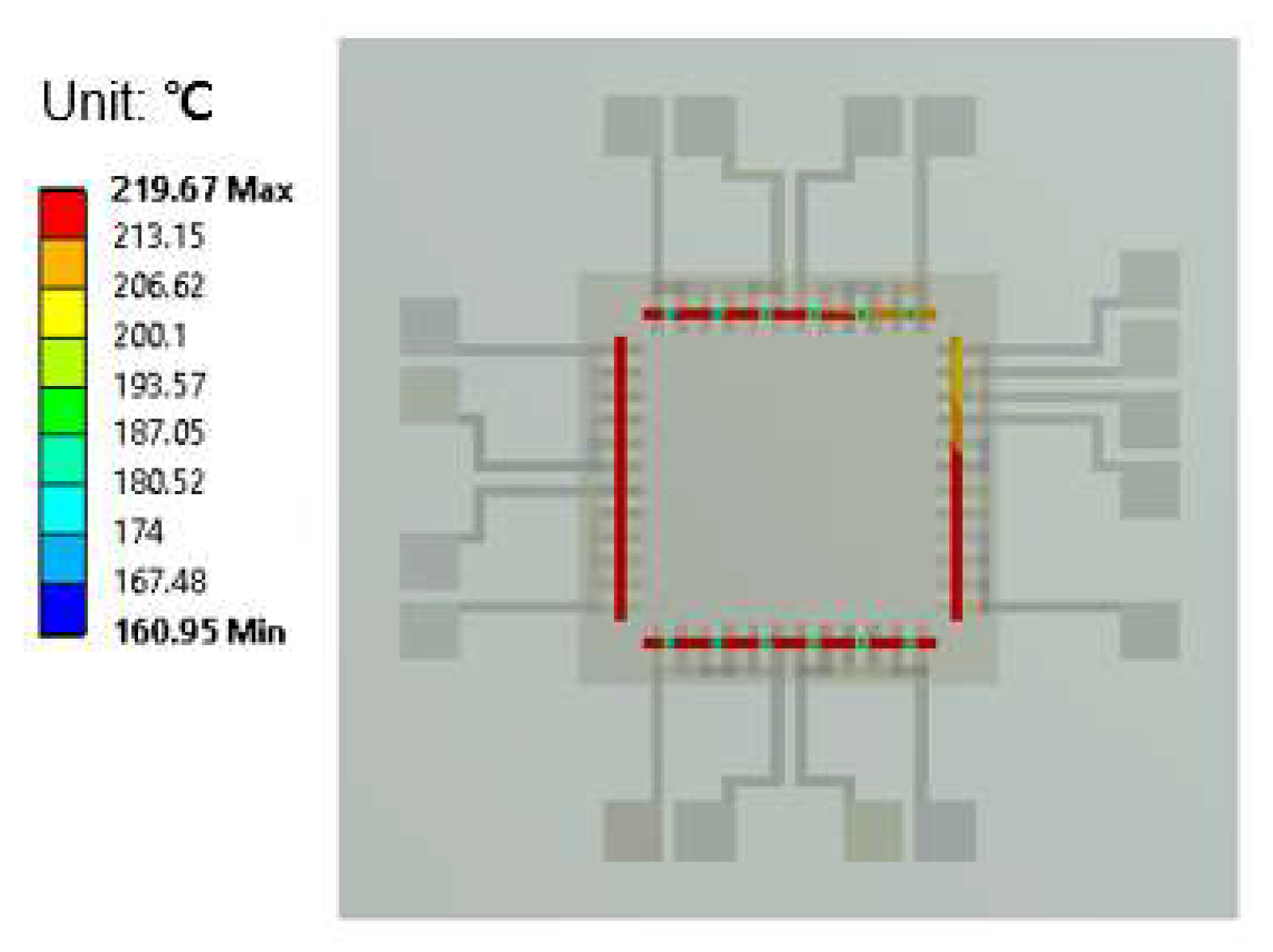

3.1. Heat Transfer Analysis

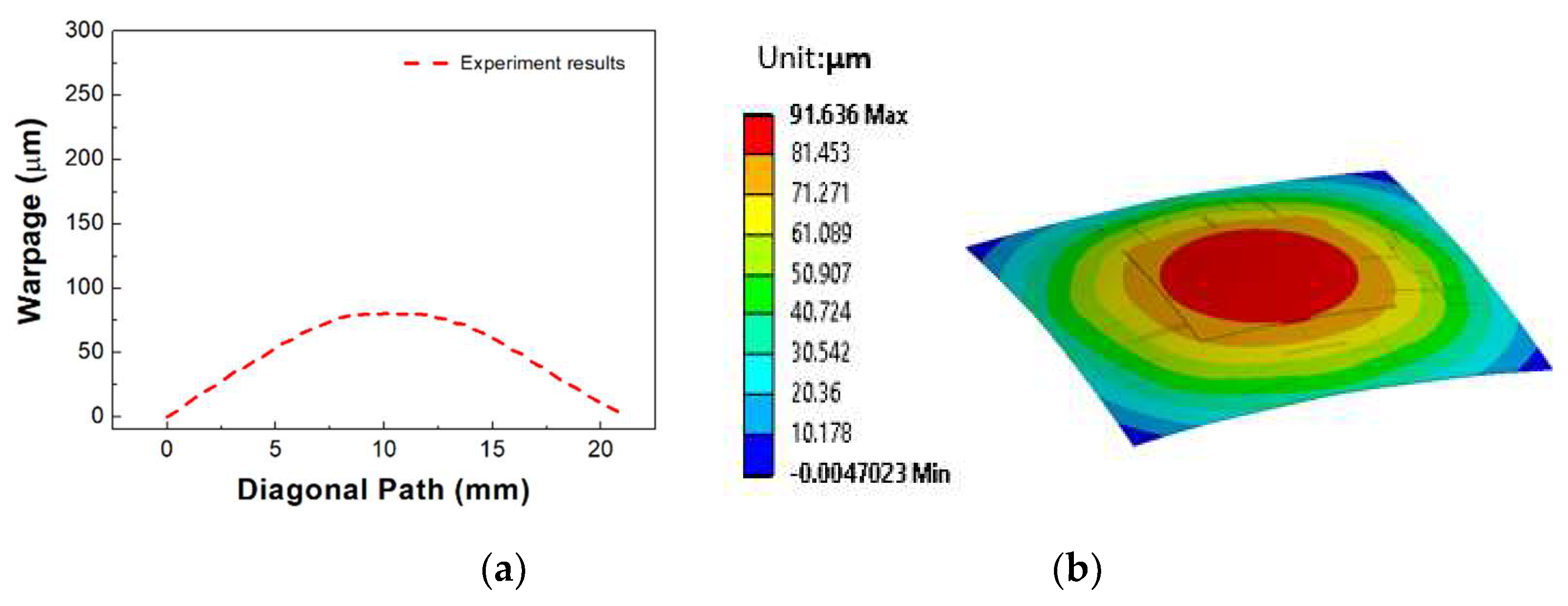

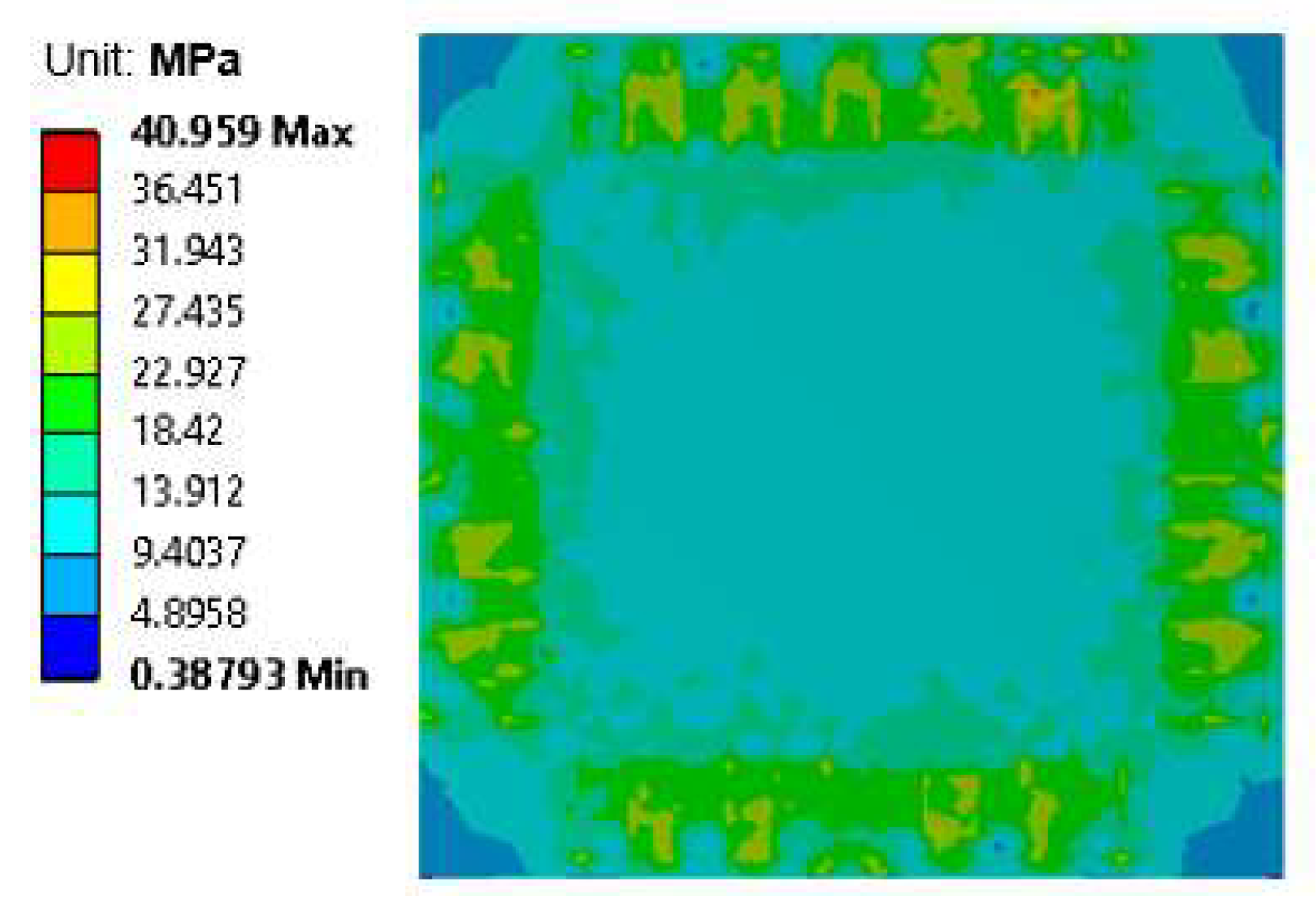

3.2. Warpage and Thermo-Mechanical Analysis

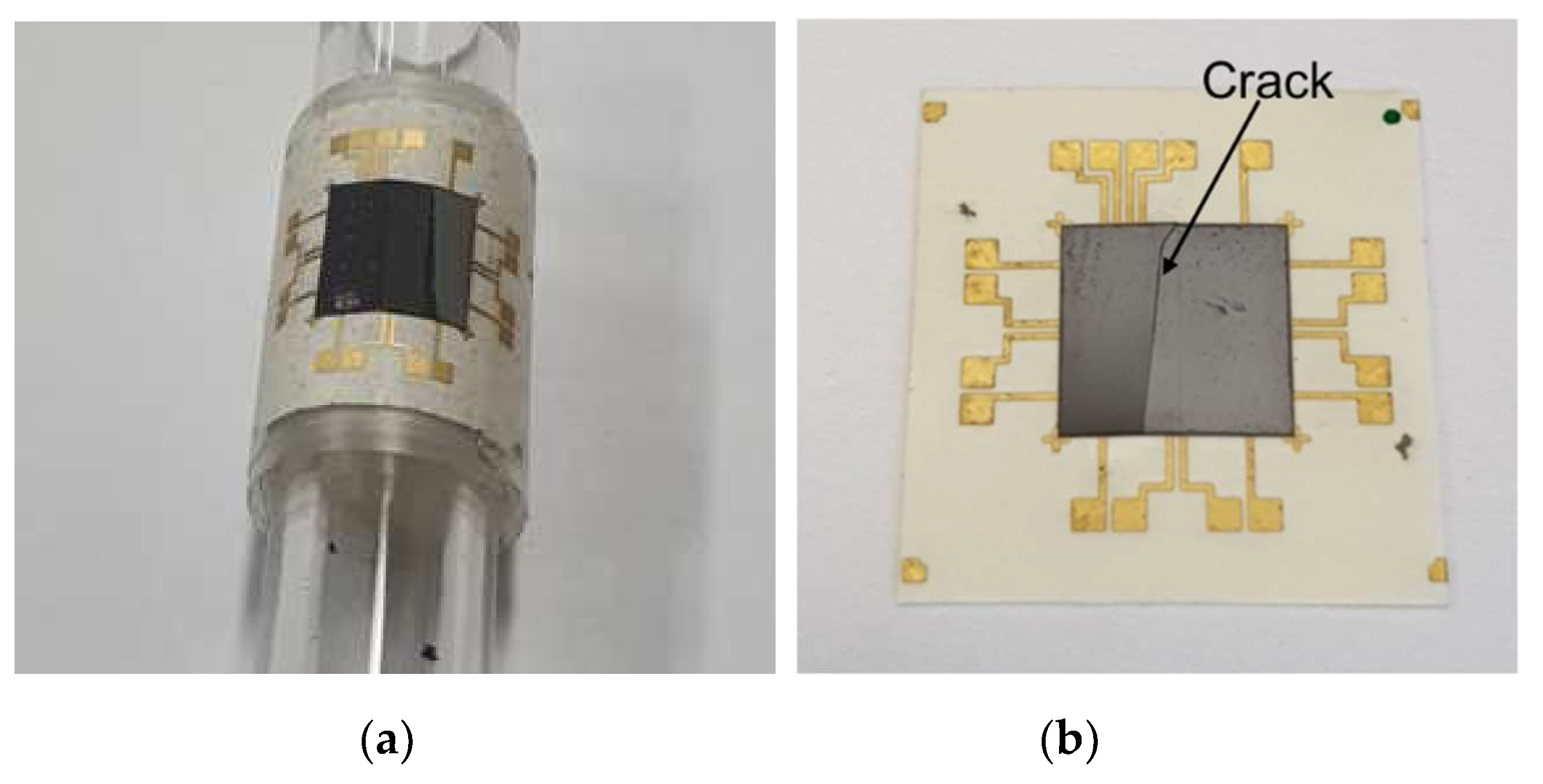

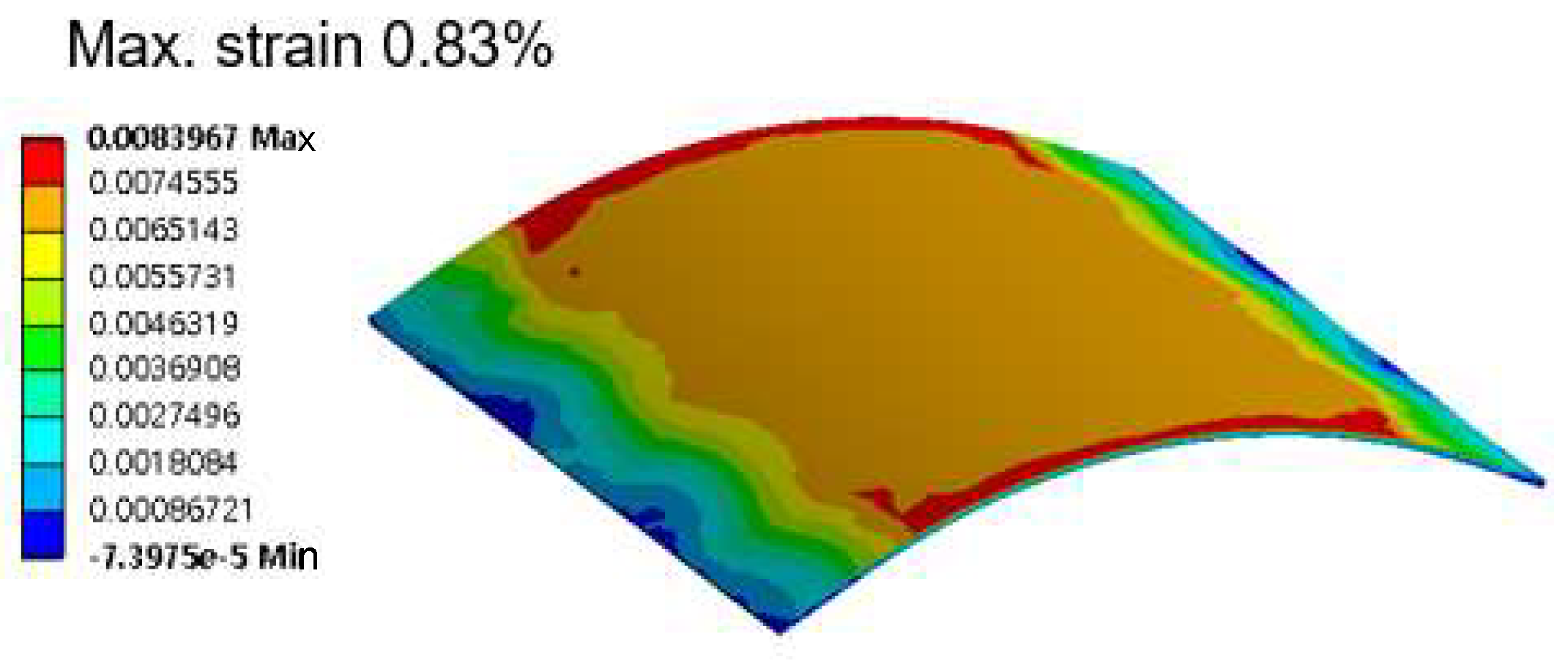

3.3. Bending Test and Simulation

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Gao, W.; Ota, H.; Kiriya, D.; Takei, K.; Javey, A. Flexible Electronics toward Wearable Sensing. Acc. Chem. Res. 2019, 52, 523–533. [Google Scholar] [CrossRef] [PubMed]

- Shen, G. Recent advances of flexible sensors for biomedical applications. Prog. Nat. Sci. 2021, 31, 872–882. [Google Scholar] [CrossRef]

- Zhang, H.; Chang, T.-H.; Min, S.; Ma, Z. Flexible semiconductor device technologies. In Proceeding of 5th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Chengdu, China, 8-11 April 2021; pp. 1–3. [Google Scholar]

- Dahiya, R.S.; Adami, A.; Collini, C.; Lorenzelli, L. Bendable ultra-thin silicon chips on foil. In Proceeding of 2012 IEEE Sensors, Taipei, Taiwan, 28–31 October 2012; pp. 1–4. [Google Scholar]

- Zhou, Z.; Zhang, H.; Liu, J.; Huang, W. Flexible electronics from intrinsically soft materials. Giant 2021, 6, 100051. [Google Scholar] [CrossRef]

- Gupta, S.; Navaraj, W.T.; Lorenzelli, L.; Dahiya, R. Ultra-thin chips for high-performance flexible electronics. NPJ Flex. Electron. 2018, 2, 8. [Google Scholar] [CrossRef]

- Angelopoulos, E.A.; Zimmermann, M. Ultra-thin chip technology for system-in-foil applications. In Proceeding of 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 251–254. [Google Scholar]

- Zhu, C.; Chalmers, E.; Chen, L.; Wang, Y.; Xu, B.B.; Li, Y.; Liu, X. Flexible devices: A nature-inspired, flexible substrate strategy for future wearable electronics. Small 2019, 15, 1970189. [Google Scholar] [CrossRef]

- Cordill, M.J.; Kreiml, P.; Mitterer, C. Materials Engineering for Flexible Metallic Thin Film Applications. Materials 2022, 15, 926. [Google Scholar] [CrossRef]

- de Mulatier, S.; Ramuz, M.; Coulon, D.; Blayac, S.; Delattre, R. Mechanical characterization of soft substrates for wearable and washable electronic systems. APL Mater. 2019, 7, 031505. [Google Scholar] [CrossRef]

- Chae, Y.; Chae, G.S.; Youn, Y.O.; Woo, S.; Shin, S.H.; Lee, J. Optimal design of thickness and young’s modulus of multi-layered foldable structure considering bending stress, neutral plane and delamination under 2.5 mm radius of curvature. Int. J. Precis. Eng. Manuf. 2018, 19, 1143–1154. [Google Scholar] [CrossRef]

- Malik, M.H.; Tsiamis, A.; Zangl, H.; Binder, A.; Mitra, S.; Roshanghias, A. Die-level thinning for flip-chip tntegration on flexible substrates. Electronics 2022, 11, 849. [Google Scholar] [CrossRef]

- Kumano, Y.; Tomura, Y.; Itagaki, M.; Bessho, Y. Development of chip-on-flex using SBB flip-chip technology. Microelectron. Reliab. 2001, 41, 525–530. [Google Scholar] [CrossRef]

- Malik, A.; Kandasubramanian, B. Flexible polymeric substrates for electronic applications. Polym. Rev. 2018, 58, 630–667. [Google Scholar] [CrossRef]

- Chan, Y.C.; Tan, S.C.; Lui, N.S.M.; Tan, C.W. Electrical Characterization of NCP- and NCF-Bonded Fine-Pitch Flip-Chip-on-Flexible Packages. IEEE Trans. Adv. Packag. 2007, 30, 142–147. [Google Scholar] [CrossRef]

- Kim, D.H.; Yoo, H.G.; Joe, D.J.; Lee, K.J. ACF-packaged ultrathin Si-based flexible NAND flash memory. In Proceeding of 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 1931–1934. [Google Scholar]

- Yoon, D.-J.; Malik, M.-H.; Yan, P.; Paik, K.-W.; Roshanghias, A. ACF bonding technology for paper- and PET-based disposable flexible hybrid electronics. J. Mater. Sci. Mater. Electron. 2021, 32, 2283–2292. [Google Scholar] [CrossRef]

- Malik, M.H.; Grosso, G.; Zangl, H.; Binder, A.; Roshanghias, A. Flip Chip integration of ultra-thinned dies in low-cost flexible printed electronics; the effects of die thickness, encapsulation and conductive adhesives. Microelectron. Reliab. 2021, 123, 114204. [Google Scholar] [CrossRef]

- Bo, G.; Yu, H.; Ren, L.; Cheng, N.; Feng, H.; Xu, X.; Dou, S.X.; Wang, H.; Du, Y. Gallium–Indium–Tin Liquid Metal Nanodroplet-Based Anisotropic Conductive Adhesives for Flexible Integrated Electronics. ACS Appl. Nano Mater. 2021, 4, 550–557. [Google Scholar] [CrossRef]

- Maeda, K.; Nitani, M.; Uno, M. Thermocompression bonding of conductive polymers for electrical connections in organic electronics. Polym. J. 2019, 52, 405–412. [Google Scholar] [CrossRef]

- Lee, S.-H.; Suk, K.-L.; Lee, K.; Paik, K.-W. Study on Fine Pitch Flex-on-Flex Assembly Using Nanofiber/Solder Anisotropic Conductive Film and Ultrasonic Bonding Method. IEEE Trans. Compon. Packag. Manuf. Technol. 2012, 2, 2108–2114. [Google Scholar] [CrossRef]

- Choi, K.-S.; Junior, W.A.B.; Jeong, L.; Jang, K.-S.; Moon, S.H.; Bae, H.-C.; Eom, Y.-S. Interconnection process using laser and hybrid underfill for LED array module on PET substrate. In Proceeding of 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 29 May–1 June 2018; pp. 1567–1573. [Google Scholar]

- Joo, J.; Eom, Y.-S.; Jang, K.-S.; Choi, G.-M.; Choi, K.-S. Development of bonding process for flexible devices with fine-pitch interconnection using Anisotropic Solder Paste and Laser-Assisted Bonding Technology. In Proceeding of 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 3–30 June 2020; pp. 1309–1314. [Google Scholar]

- Braganca, W.A.; Eom, Y.; Jang, K.; Moon, S.H.; Bae, H.; Choi, K.; Junior, W.A.B. Collective laser-assisted bonding process for 3D TSV integration with NCP. ETRI J. 2019, 41, 396–407. [Google Scholar] [CrossRef]

- Na, S.; Gim, M.; Kim, C.; Park, D.; Ryu, D.; Park, D.; Khim, J. Next Gen Laser Assisted Bonding (LAB) Technology. In Proceeding of 2022 IEEE 72nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 31 May–3 June 2022; pp. 1991–1995. [Google Scholar]

- Anwar, A.R.; Sajjad, M.T.; Johar, M.A.; Hernández-Gutiérrez, C.A.; Usman, M.; Łepkowski, S.P. Recent Progress in Micro-LED-Based Display Technologies. Laser Photonics Rev. 2022, 16, 2100427. [Google Scholar] [CrossRef]

- Park S-IAhn, J.-H.; Feng, X.; Wang, S.; Huang, Y.; Rogers, J.A. Theoretical and experimental studies of bending of inorganic electronic materials on plastic substrates. Adv. Funct. Mater. 2008, 18, 2673–2684. [Google Scholar] [CrossRef]

| Component | Material | Density (kg/m3) | E (GPa) | ν | α (ppm/°C) | Thermal Conductivity (W/m × K) | Specific Heat (J/kg × K) |

|---|---|---|---|---|---|---|---|

| Die | Silicon | 2300 | 131 | 0.28 | 2.8 | 124 | 794 |

| Die mask | Silicon oxide | 2170 | 66.3 | 0.15 | 0.55 | 1.3 | 680 |

| Electrode | Copper | 8960 | 128 | 0.34 | 16.5 | 398 | 390 |

| Substrate | Adhesive | 1150 | 0.69 | 0.4 | 50 | 0.17 | 1100 |

| PI | 1420 | 4 | 0.35 | 20 | 0.12 | 1090 | |

| Ni | 8908 | 200 | 0.31 | 13.4 | 90.9 | 440 | |

| Solder | ASP solder | 7360 | 1.36 | 0.4 | 62.5 | 1.045 | 167 |

| Epoxy | 1150 | 2.5 | 0.3 | 50 | 0.17 | 1100 |

| Bending Radius (mm) | Electrical Resistance (mW) |

|---|---|

| Before bending (Flat state) | 2.3 |

| 10 | 2.3 |

| 9 | 2.4 |

| 8 | 2.7 |

| 7 | 3.4 |

| 6 | 4.5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Le, X.-L.; Le, X.-B.; Hwangbo, Y.; Joo, J.; Choi, G.-M.; Eom, Y.-S.; Choi, K.-S.; Choa, S.-H. Mechanical Reliability Assessment of a Flexible Package Fabricated Using Laser-Assisted Bonding. Micromachines 2023, 14, 601. https://doi.org/10.3390/mi14030601

Le X-L, Le X-B, Hwangbo Y, Joo J, Choi G-M, Eom Y-S, Choi K-S, Choa S-H. Mechanical Reliability Assessment of a Flexible Package Fabricated Using Laser-Assisted Bonding. Micromachines. 2023; 14(3):601. https://doi.org/10.3390/mi14030601

Chicago/Turabian StyleLe, Xuan-Luc, Xuan-Bach Le, Yuhwan Hwangbo, Jiho Joo, Gwang-Mun Choi, Yong-Sung Eom, Kwang-Seong Choi, and Sung-Hoon Choa. 2023. "Mechanical Reliability Assessment of a Flexible Package Fabricated Using Laser-Assisted Bonding" Micromachines 14, no. 3: 601. https://doi.org/10.3390/mi14030601

APA StyleLe, X.-L., Le, X.-B., Hwangbo, Y., Joo, J., Choi, G.-M., Eom, Y.-S., Choi, K.-S., & Choa, S.-H. (2023). Mechanical Reliability Assessment of a Flexible Package Fabricated Using Laser-Assisted Bonding. Micromachines, 14(3), 601. https://doi.org/10.3390/mi14030601