Disturbance Characteristics of 1T DRAM Arrays Consisting of Feedback Field-Effect Transistors

Abstract

:1. Introduction

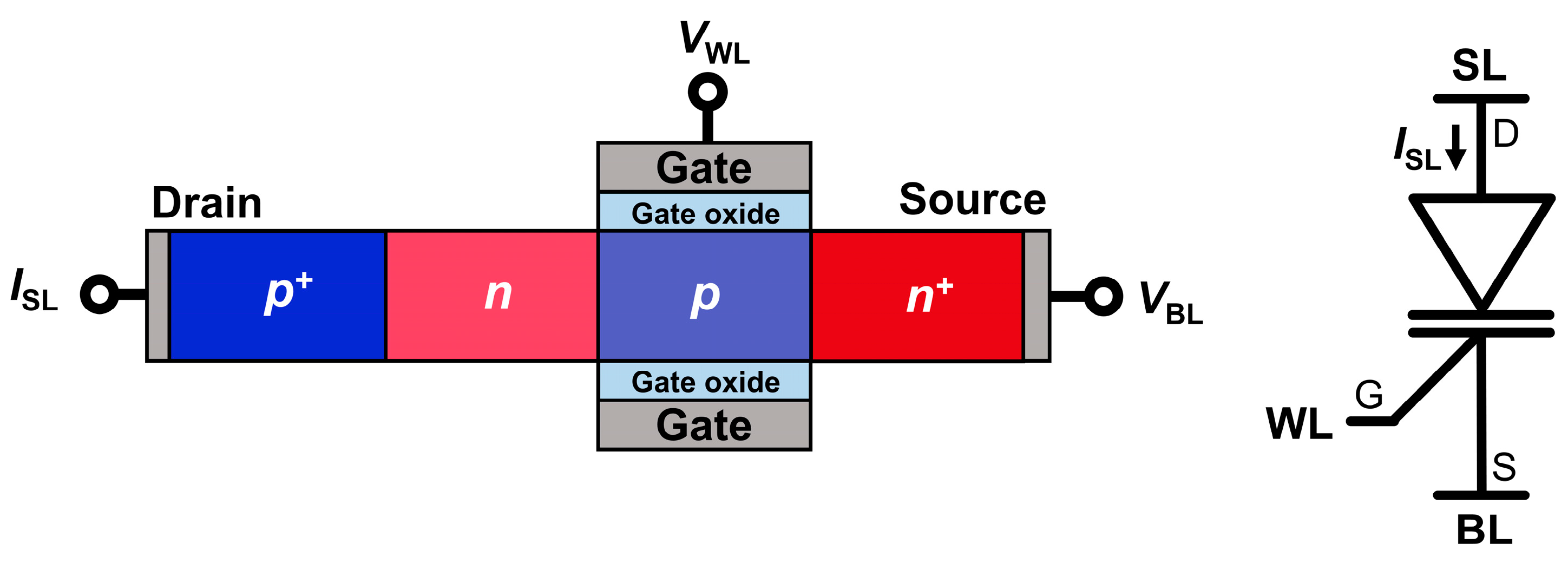

2. Device Structure and Simulation Method

3. Results

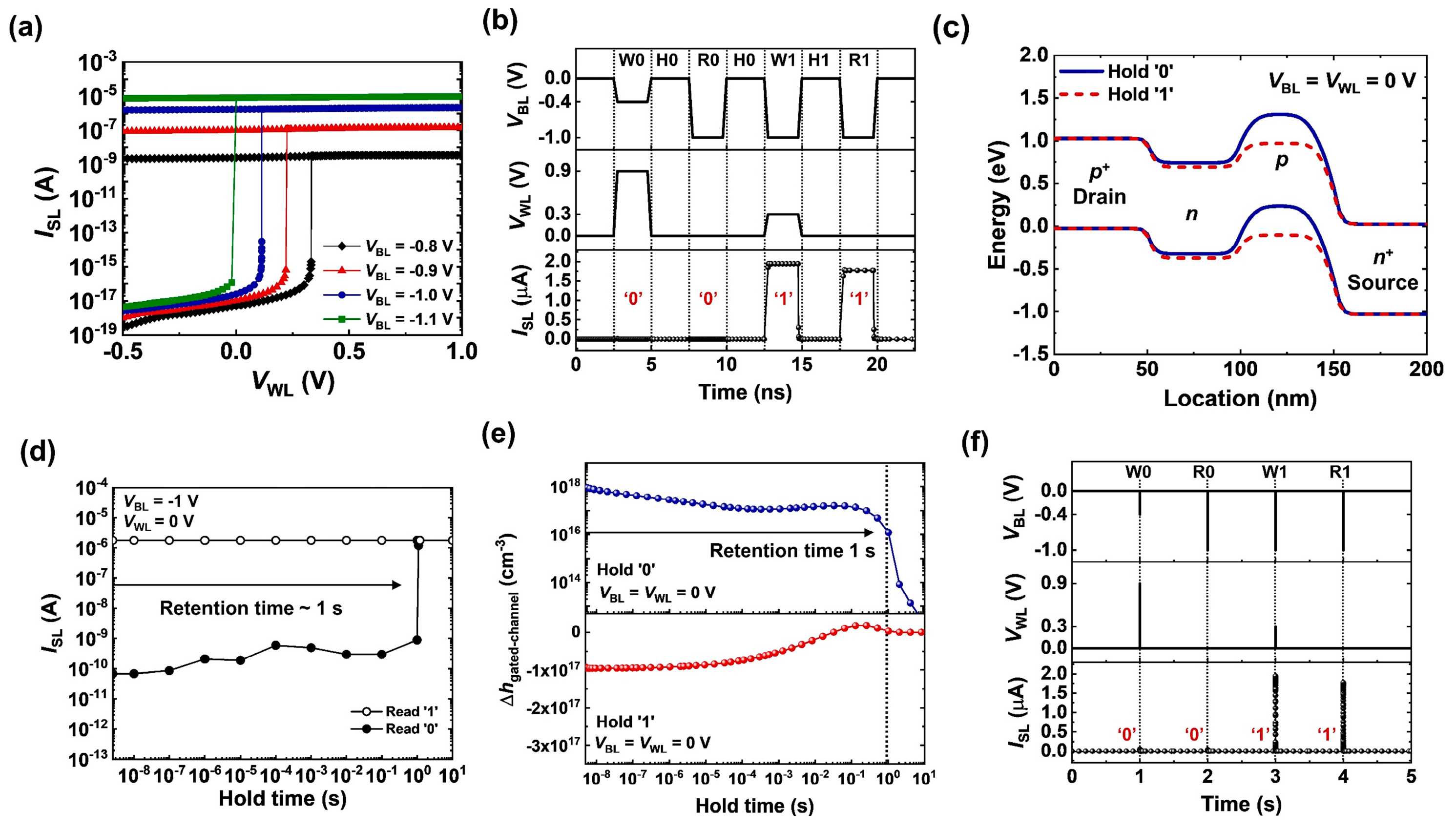

3.1. Characteristics of 1T DRAM Cell

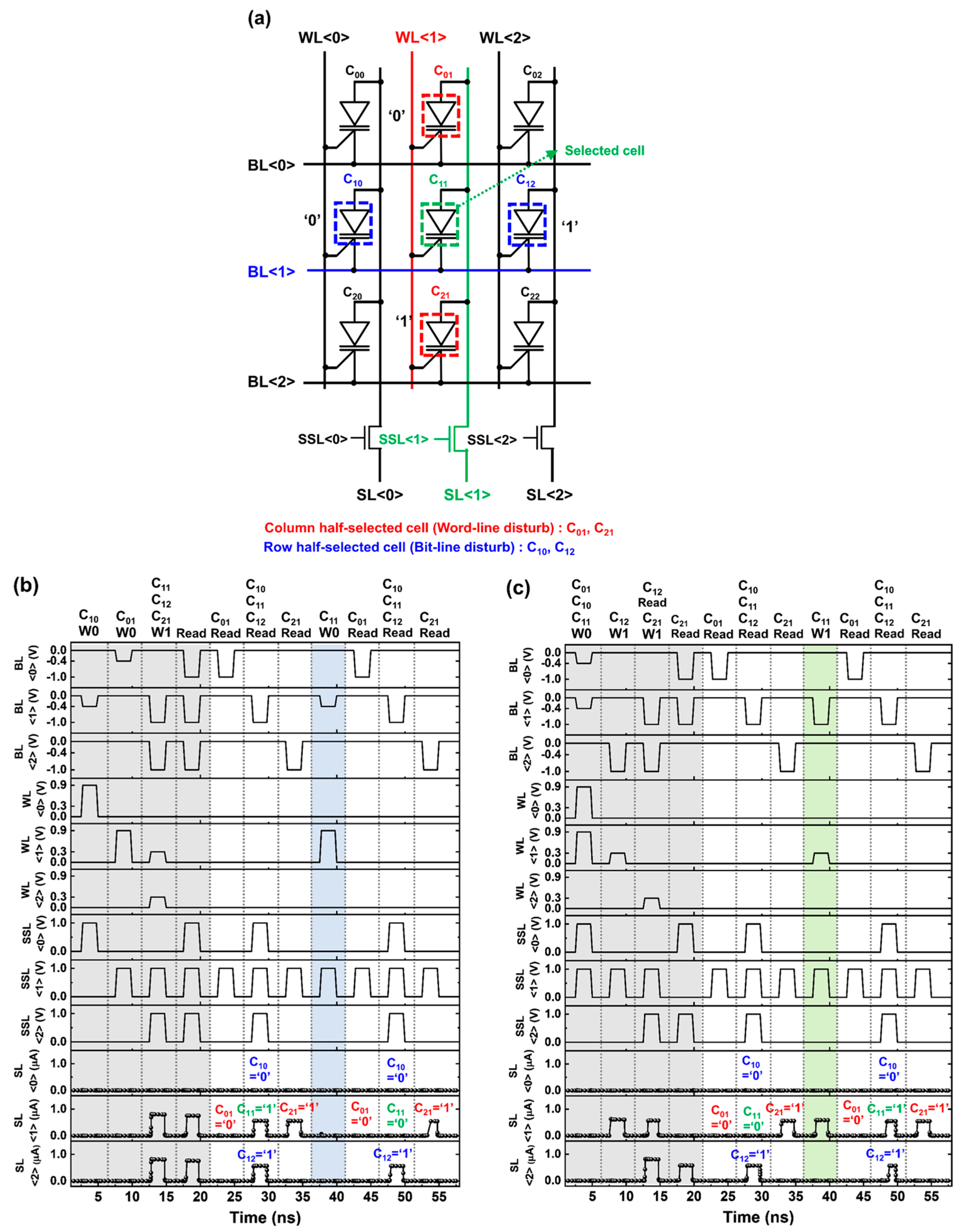

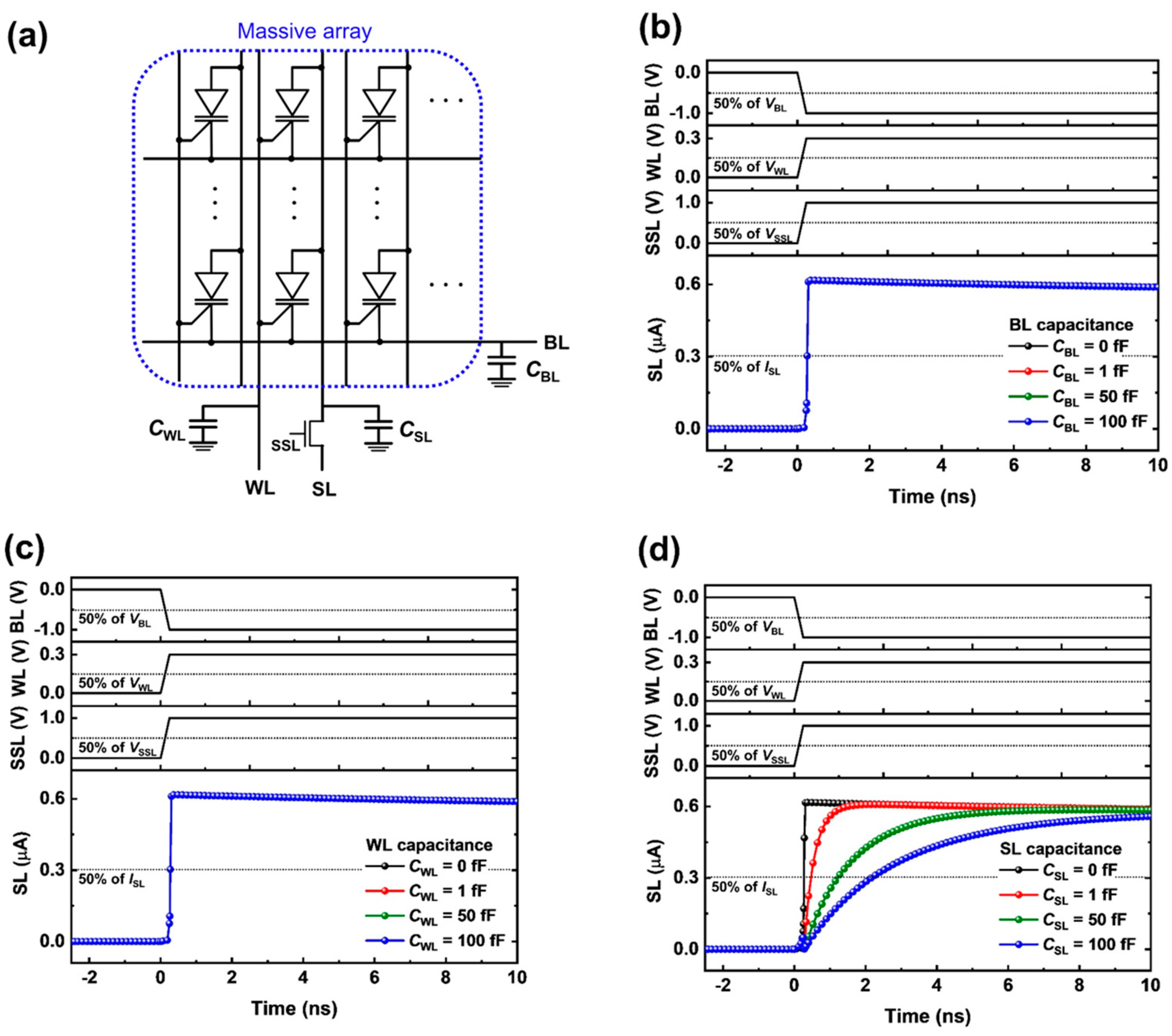

3.2. Array Characteristics of 1T DRAM

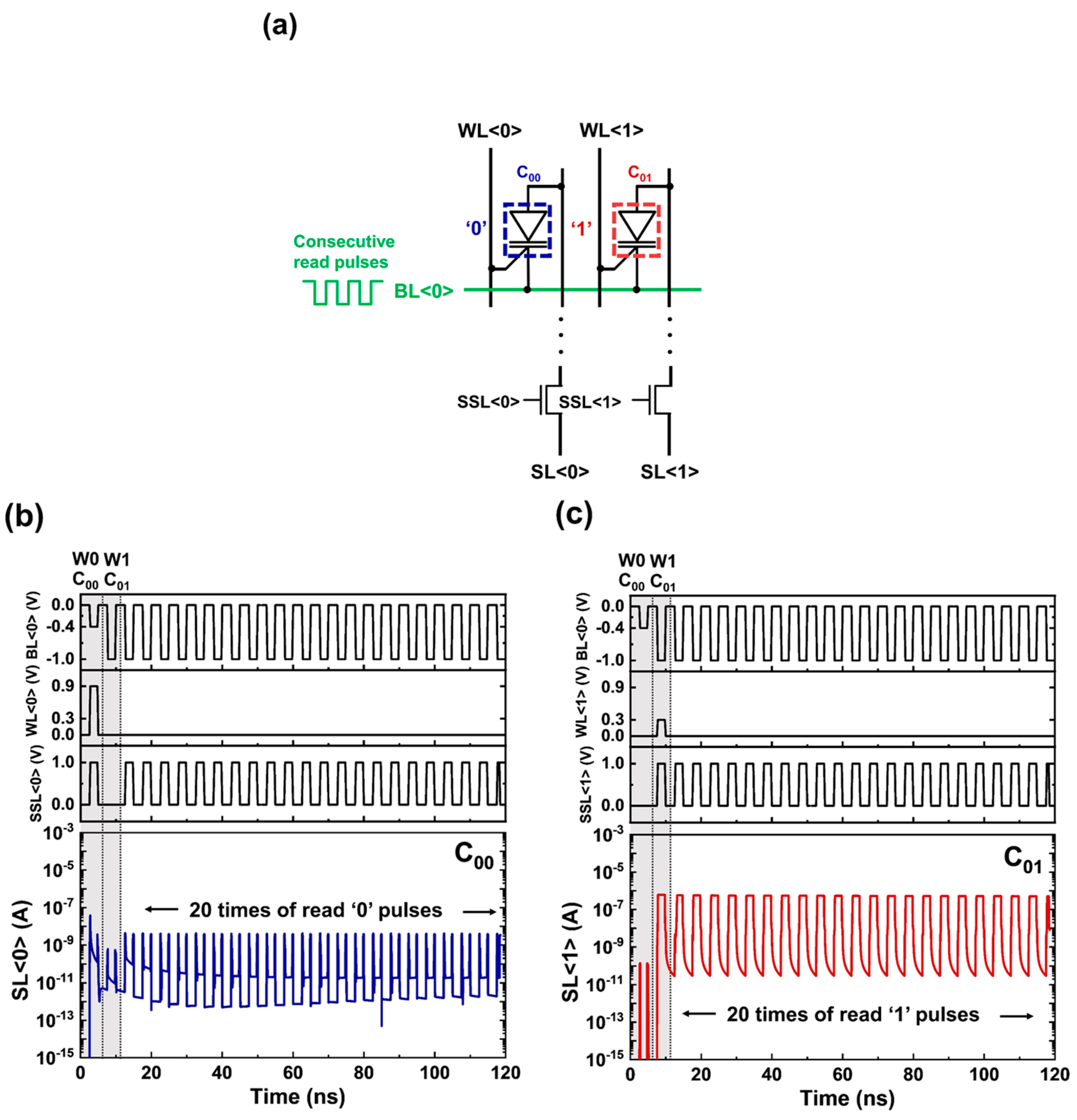

3.3. Performance of 1T DRAM

4. Conclusions

Author Contributions

Funding

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Khan, W.Z.; Ahmed, E.; Hakak, S.; Yaqoob, I.; Ahmed, A. Edge computing: A survey. Future Gener. Comput. Syst. 2019, 97, 219–235. [Google Scholar] [CrossRef]

- Capra, M.; Peloso, R.; Masera, G.; Roch, M.R.; Martina, M. Edge Computing: A Survey On the Hardware Requirements in the Internet of Things World. Future Internet 2019, 11, 100. [Google Scholar] [CrossRef]

- Steegen, A. Technology innovation in an IoT Era. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 17–19 June 2015. [Google Scholar]

- Park, J.M.; Hwang, Y.S.; Kim, S.W.; Han, S.Y.; Park, J.S.; Kim, J.; Seo, J.W.; Kim, B.S.; Shin, S.H.; Cho, C.H.; et al. 20 nm DRAM: A new beginning of another revolution. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 26.25.21–26.25.24. [Google Scholar]

- Spessot, A.; Oh, H. 1T-1C Dynamic Random Access Memory Status, Challenges, and Prospects. IEEE Trans. Electron Devices 2020, 67, 1382–1393. [Google Scholar] [CrossRef]

- Lee, S.-H. Technology scaling challenges and opportunities of memory devices. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016. [Google Scholar]

- Aoulaiche, M.; Bravaix, A.; Simoen, E.; Caillat, C.; Cho, M.; Witters, L.; Blomme, P.; Fazan, P.; Groeseneken, G.; Jurczak, M. Endurance of one transistor floating body RAM on UTBOX SOI. IEEE Trans. Electron Devices 2014, 61, 801–805. [Google Scholar] [CrossRef]

- Giusi, G. Floating body DRAM with body raised and source/drain separation. Electronics 2021, 10, 706. [Google Scholar] [CrossRef]

- Navarro, C.; Karg, S.; Marquez, C.; Navarro, S.; Convertino, C.; Zota, C.; Czornomaz, L.; Gamiz, F. Capacitor-less dynamic random access memory based on a III–V transistor with a gate length of 14 nm. Nat. Electron. 2019, 2, 412–419. [Google Scholar] [CrossRef]

- Biswas, A.; Ionescu, A.M. 1T capacitor-less DRAM cell based on asymmetric tunnel FET design. IEEE J. Electron Devices Soc. 2014, 3, 217–222. [Google Scholar] [CrossRef]

- Kang, H.; Cho, J.; Kim, Y.; Lim, D.; Woo, S.; Cho, K.; Kim, S. Nonvolatile and volatile memory characteristics of a silicon nanowire feedback field-effect transistor with a nitride charge-storage layer. IEEE Trans. Electron Devices 2019, 66, 3342–3348. [Google Scholar] [CrossRef]

- Lee, C.; Sung, J.; Shin, C. Understanding of feedback field-effect transistor and its applications. Appl. Sci. 2020, 10, 3070. [Google Scholar] [CrossRef]

- Oh, J.H.; Yu, Y.S. A Monolithic 3-Dimensional Static Random Access Memory Containing a Feedback Field Effect Transistor. Micromachines 2022, 13, 1625. [Google Scholar] [CrossRef] [PubMed]

- Kim, H.; Hwang, S.; Kwon, D.W.; Lee, J.-H.; Park, B.-G. Back biasing effects in a feedback steep switching device with charge spacer. In Proceedings of the 2016 IEEE Silicon Nanoelectronics Workshop (SNW), Honolulu, HI, USA, 12–13 June 2016; pp. 172–173. [Google Scholar]

- Lee, C.; Ko, E.; Shin, C. Steep slope silicon-on-insulator feedback field-effect transistor: Design and performance analysis. IEEE Trans. Electron Devices 2018, 66, 286–291. [Google Scholar] [CrossRef]

- Kim, M.; Kim, Y.; Lim, D.; Woo, S.; Cho, K.; Kim, S. Steep switching characteristics of single-gated feedback field-effect transistors. Nanotechnology 2016, 28, 055205. [Google Scholar] [CrossRef] [PubMed]

- Lim, D.; Son, J.; Cho, K.; Kim, S. Quasi-nonvolatile silicon memory device. Adv. Mater. Technol. 2020, 5, 2000915. [Google Scholar] [CrossRef]

- Jang, D.; Ansari, M.H.R.; Kim, G.; Cho, S.; Cho, I.H. Reliability improvement of 1T DRAM based on feedback transistor by using local partial insulators. Jpn. J. Appl. Phys. 2021, 60, 104002. [Google Scholar]

- Han, S.; Kim, Y.; Son, D.; Baac, H.W.; Won, S.M.; Shin, C. Study on memory characteristics of fin-shaped feedback field effect transistor. Semicond. Sci. Technol. 2022, 37, 065006. [Google Scholar] [CrossRef]

- Stathis, J.H. Reliability limits for the gate insulator in CMOS technology. IBM J. Res. Dev. 2002, 46, 265–286. [Google Scholar] [CrossRef]

- Li, Y.; Hwang, C.-H.; Li, T.-Y.; Han, M.-H. Process-variation effect, metal-gate work-function fluctuation, and random-dopant fluctuation in emerging CMOS technologies. IEEE Trans. Electron Devices 2009, 57, 437–447. [Google Scholar] [CrossRef]

- Pal, A.; Nainani, A.; Saraswat, K.C. Addressing key challenges in 1T-DRAM: Retention time, scaling and variability—Using a novel design with GaP source-drain. In Proceedings of the 2013 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Glasgow, UK, 3–5 September 2013; pp. 376–379. [Google Scholar]

- Navarro, S.; Navarro, C.; Marquez, C.; Salazar, N.; Galy, P.; Cristoloveanu, S.; Gamiz, F. Reliability study of thin-oxide zero-ionization, zero-swing FET 1T-DRAM memory cell. IEEE Electron Device Lett. 2019, 40, 1084–1087. [Google Scholar] [CrossRef]

- Park, S.-K.C. Technology scaling challenge and future prospects of DRAM and NAND flash memory. In Proceedings of the 2015 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 17–20 May 2015; pp. 1–4. [Google Scholar]

- Blagojevic, M.; Kayal, M.; Pastre, M.; Harik, L.; Declercq, M.J.; Okhonin, S.; Fazan, P.C. Capacitorless 1T DRAM sensing scheme with automatic reference generation. IEEE J. Solid-State Circuits 2006, 41, 1463–1470. [Google Scholar] [CrossRef]

- Zhou, J.; Kim, K.-H.; Lu, W. Crossbar RRAM arrays: Selector device requirements during read operation. IEEE Trans. Electron Devices 2014, 61, 1369–1376. [Google Scholar] [CrossRef]

- Bangsaruntip, S.; Balakrishnan, K.; Cheng, S.-L.; Chang, J.; Brink, M.; Lauer, I.; Bruce, R.; Engelmann, S.; Pyzyna, A.; Cohen, G. Density scaling with gate-all-around silicon nanowire MOSFETs for the 10 nm node and beyond. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 20.22.21–20.22.24. [Google Scholar]

- Lee, B.; Kim, M.; Kim, J.; Yoo, S.; Shim, T.; Park, J. Design of n+-base width of two-terminal-electrode vertical thyristor for cross-point memory cell without selector. Nanotechmology 2021, 32, 14LT01. [Google Scholar] [CrossRef]

- Sentaurus Device User Guide, O-2018.06; Synopsys: Mountain View, CA, USA, 2018.

- Shen, W.; Huang, P.; Wang, X.; Feng, Y.; Xu, W.; Gao, B.; Wu, H.; Qian, H.; Liu, L.; Liu, X. A novel capacitor-based stateful logic operation scheme for in-memory computing in 1T1R RRAM array. In Proceedings of the 2020 4th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Penang, Malaysia, 6–21 April 2020; pp. 1–4. [Google Scholar]

- Hou, J.; Shao, Z.; Miao, X. A High speed low power capacitorless SOI-DRAM cell using impact ionization and GIDL effect. In Proceedings of the 2009 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), Xi’an, China, 25–27 December 2009; pp. 517–520. [Google Scholar]

- Ansari, M.H.R.; Cho, S. Performance improvement of 1T DRAM by raised source and drain engineering. IEEE Trans. Electron Devices 2021, 68, 1577–1584. [Google Scholar] [CrossRef]

- Ansari, M.H.R.; Navlakha, N.; Lee, J.Y.; Cho, S. Double-gate junctionless 1T DRAM with physical barriers for retention improvement. IEEE Trans. Electron Devices 2020, 67, 1471–1479. [Google Scholar] [CrossRef]

- Yoon, Y.J.; Lee, J.S.; Kim, D.-S.; Lee, S.H.; Kang, I.M. One-transistor dynamic random-access memory based on gate-all-around junction-less field-effect transistor with a Si/SiGe heterostructure. Electronics 2020, 9, 2134. [Google Scholar] [CrossRef]

- Yoon, Y.J.; Seo, J.H.; Cho, M.S.; Kim, B.G.; Lee, S.H.; Kang, I.M. Capacitorless one-transistor dynamic random access memory based on double-gate GaAs junctionless transistor. Jpn. J. Appl. Phys. 2017, 56, 06GF01. [Google Scholar] [CrossRef]

- Kamal, N.; Kamal, A.K.; Singh, J. L-shaped tunnel field-effect transistor-based 1T DRAM with improved read current ratio, retention time, and sense margin. IEEE Trans. Electron Devices 2021, 68, 2705–2711. [Google Scholar] [CrossRef]

- Lacord, J.; Parihar, M.S.; Navarro, C.; Wakam, F.T.; Bawedin, M.; Cristoloveanu, S.; Gamiz, F.; Barbé, J.-C. MSDRAM, A2RAM and Z 2-FET performance benchmark for 1T-DRAM applications. In Proceedings of the 2018 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Austin, TX, USA, 24–26 September 2018; pp. 198–201. [Google Scholar]

- Lee, S.; Cho, H.; Son, Y.H.; Ro, Y.; Kim, N.S.; Ahn, J.H. Leveraging power-performance relationship of energy-efficient modern DRAM devices. IEEE Access 2018, 6, 31387–31398. [Google Scholar] [CrossRef]

- Yu, E.; Cho, S. A Highly Scalable and Energy-Efficient 1T DRAM Embedding a SiGe Quantum Well Structure for Significant Retention Enhancement. In Proceedings of the 2018 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Austin, TX, USA, 24–26 September 2018; pp. 255–257. [Google Scholar]

- Navarro, C.; Marquez, C.; Navarro, S.; Lozano, C.; Kwon, S.; Kim, Y.-T.; Gamiz, F. Simulation Perspectives of Sub-1V Single-Supply Z 2-FET 1T-DRAM Cells for Low-Power. IEEE Access 2019, 7, 40279–40284. [Google Scholar] [CrossRef]

| Device | Ref. | LCH1 (nm) | LG (nm) | SM (μA/μm) | Current Ratio (I1/I0) | Retention Time (ms) | Pulse Width (ns) | Supply Voltage (V) |

|---|---|---|---|---|---|---|---|---|

| DG FinFET | [31] | 60 | 60 | - | 9.4 × 105 | 0.007 | 1 | 2 |

| DG RSD MOSFET | [32] | 70 | 50 | 1.3 | 7.5 × 102 | 330 | 20 | 1.5 |

| DG JL 1T DRAM | [33] | 120 | 100 | 3.5 | - | 2500 | 50 | 1.5 |

| GAA-JLFET | [34] | 100 | 75 | 0.39 | 2.23 | 100 | 10 | 1.5 |

| DG GaAs JLT | [35] | 100 | 100 | 84.4 | - | 71 | 10 | 1.5 |

| L-shaped TFET | [36] | 114 | 50 | 6.2 | 1.2 × 106 | 1700 | 10 | 1 |

| Z2-FET | [37] | 200 | 100 | ~20 | 2.0 × 104 | ~3 | 1 | 1 |

| This study | - | 100 | 50 | 90 | 1.8 × 104 | ~1000 | 2.5 | 1 |

| Operation | |VBL| (V) | ISL (A) | Time (s) | Energy Consumption (J/bit) (E = |VBL| × ISL × Time) |

|---|---|---|---|---|

| Write ‘1’ | 1.0 | 2.0 × 10−6 | 2.5 × 10−9 | 5.0 × 10−15 |

| Write ‘0’ | 0.4 | ~1.0 × 10−10 | ~1.0 × 10−19 | |

| Read ‘1’ | 1.0 | 1.8 × 10−6 | 4.5 × 10−15 | |

| Read ‘0’ | 1.0 | ~1.0 × 10−10 | ~2.5 × 10−19 | |

| Hold | 0.0 | -- | -- | 0.0 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jeon, J.; Cho, K.; Kim, S. Disturbance Characteristics of 1T DRAM Arrays Consisting of Feedback Field-Effect Transistors. Micromachines 2023, 14, 1138. https://doi.org/10.3390/mi14061138

Jeon J, Cho K, Kim S. Disturbance Characteristics of 1T DRAM Arrays Consisting of Feedback Field-Effect Transistors. Micromachines. 2023; 14(6):1138. https://doi.org/10.3390/mi14061138

Chicago/Turabian StyleJeon, Juhee, Kyoungah Cho, and Sangsig Kim. 2023. "Disturbance Characteristics of 1T DRAM Arrays Consisting of Feedback Field-Effect Transistors" Micromachines 14, no. 6: 1138. https://doi.org/10.3390/mi14061138