Improvement of the Thermal Performance of the GaN-on-Si Microwave High-Electron-Mobility Transistors by Introducing a GaN-on-Insulator Structure

Abstract

1. Introduction

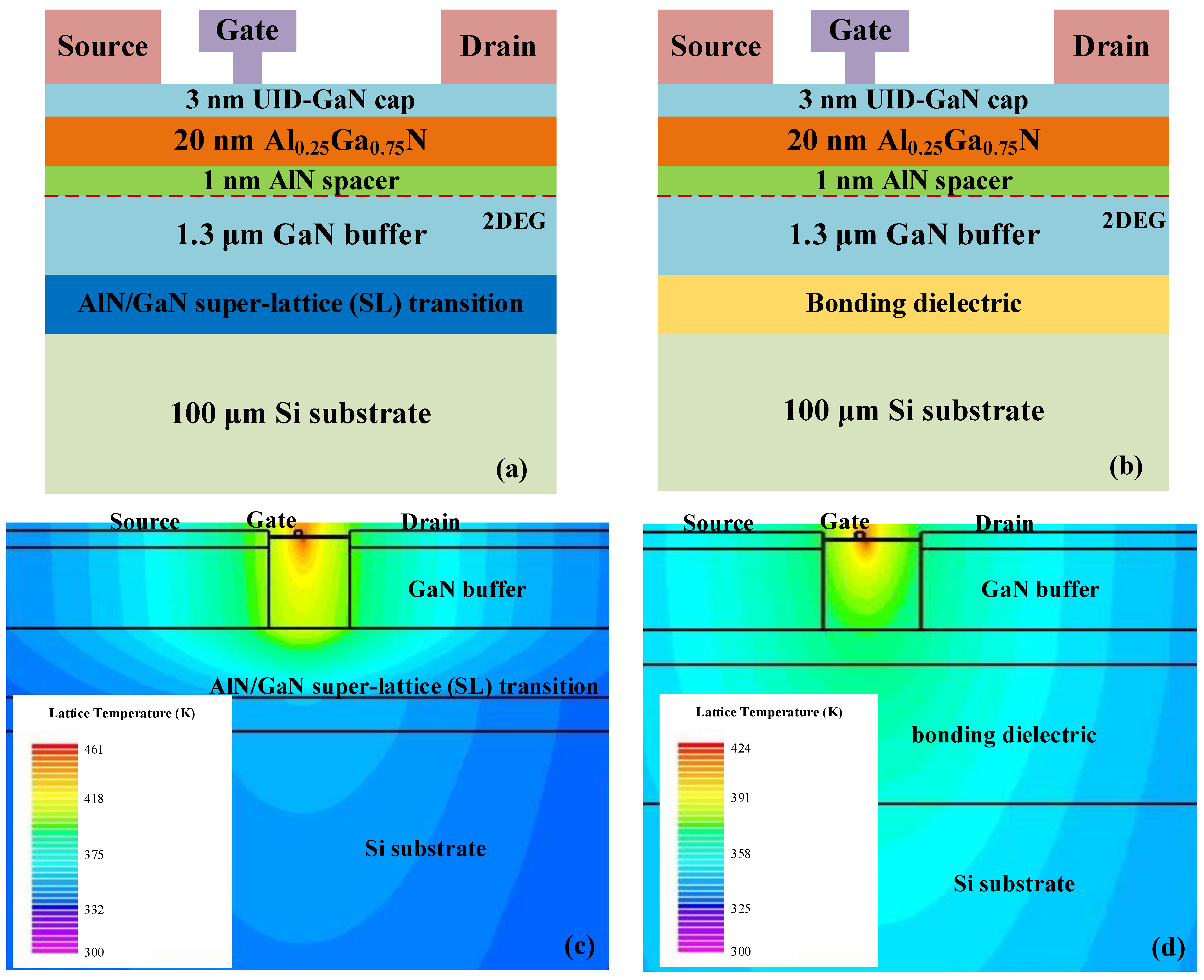

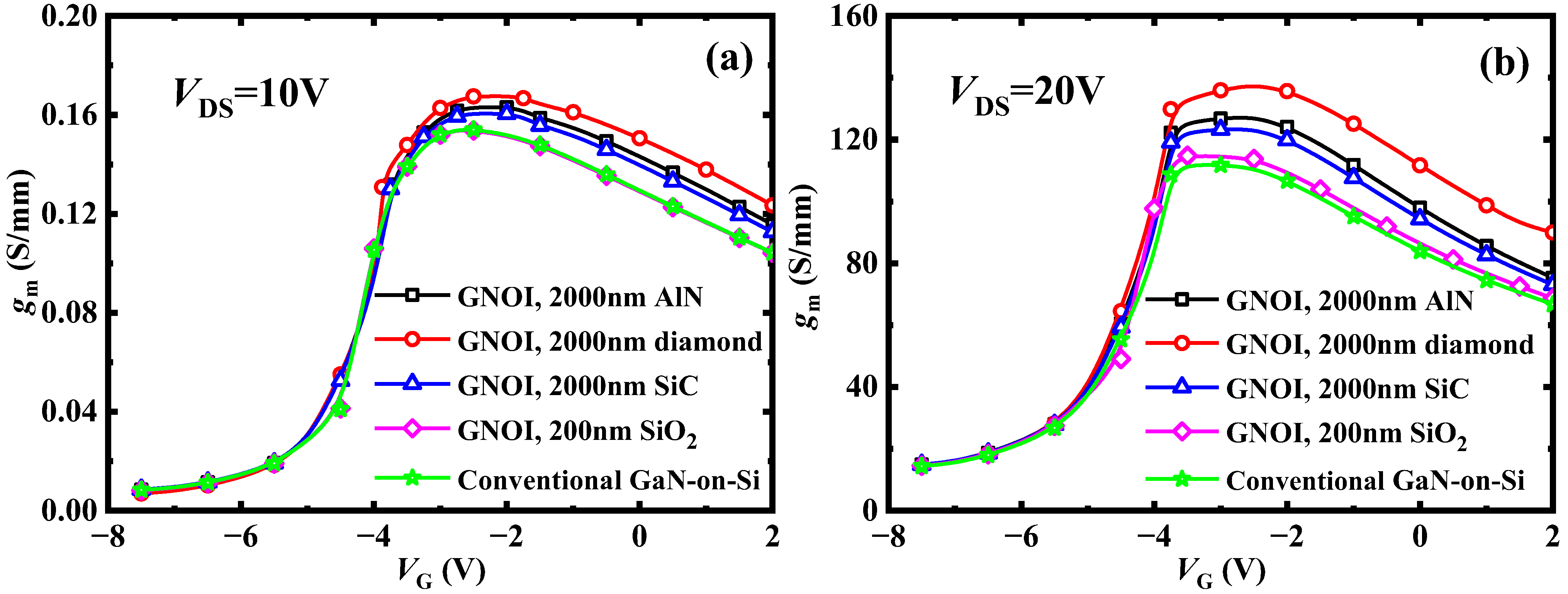

2. Electrothermal Simulation Models

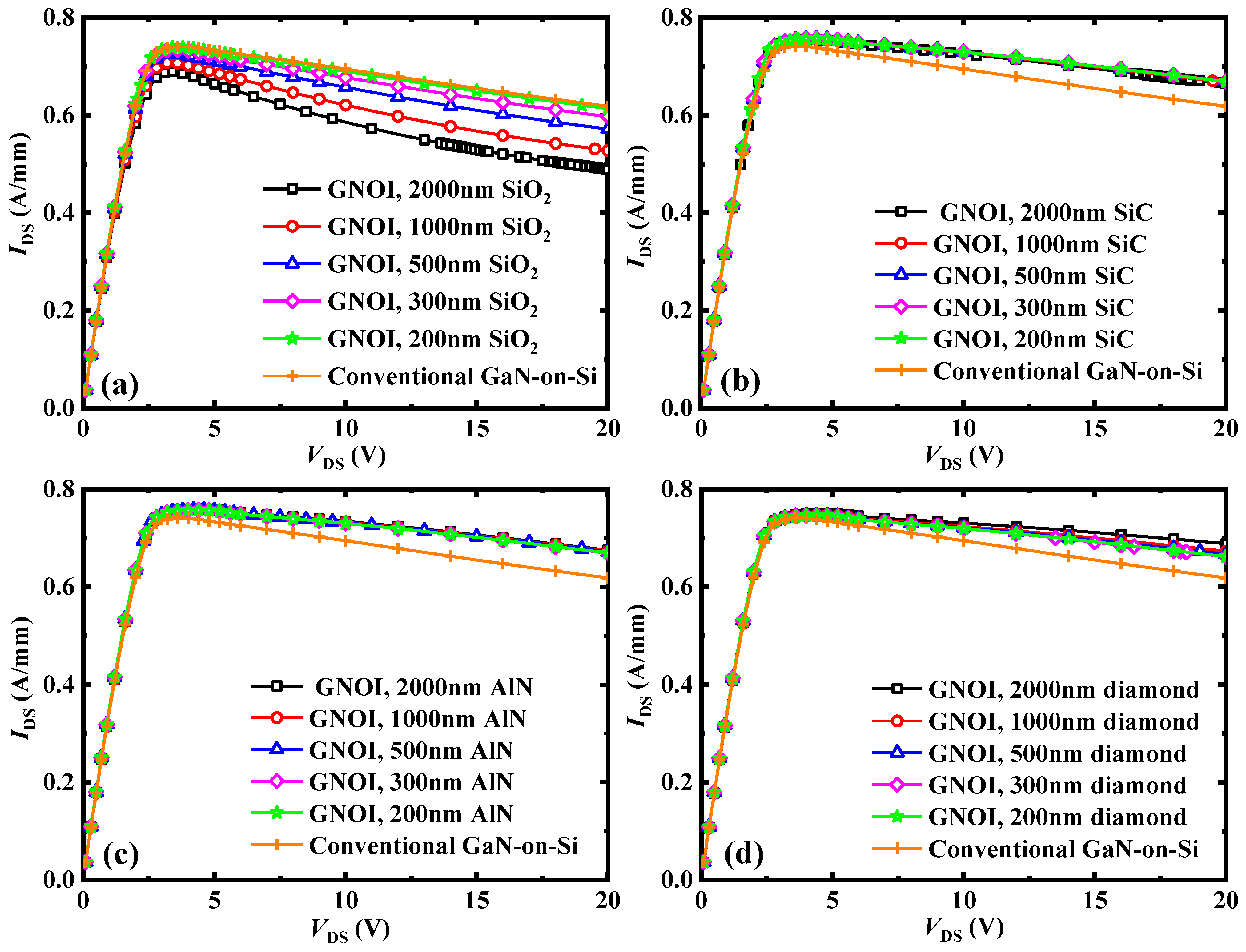

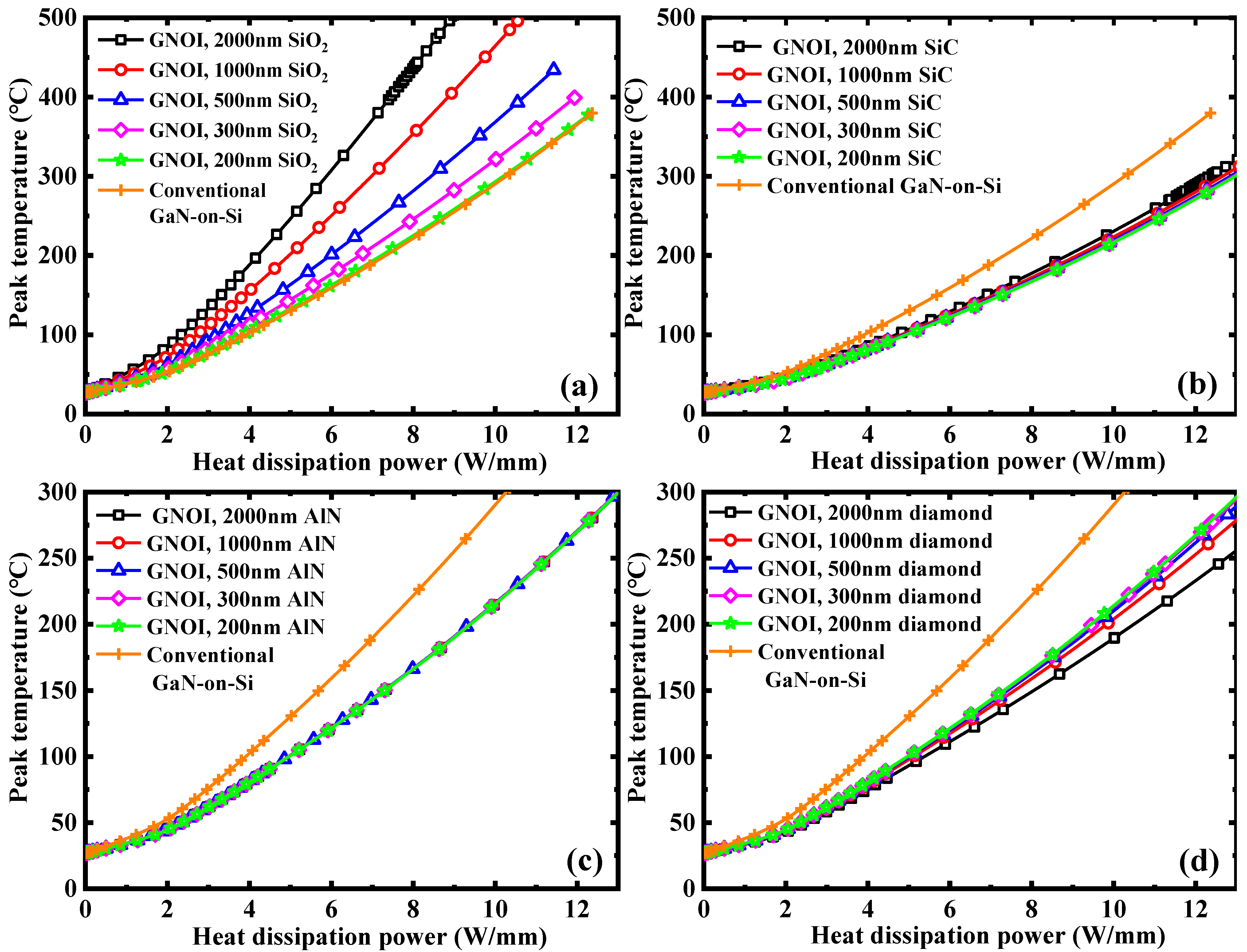

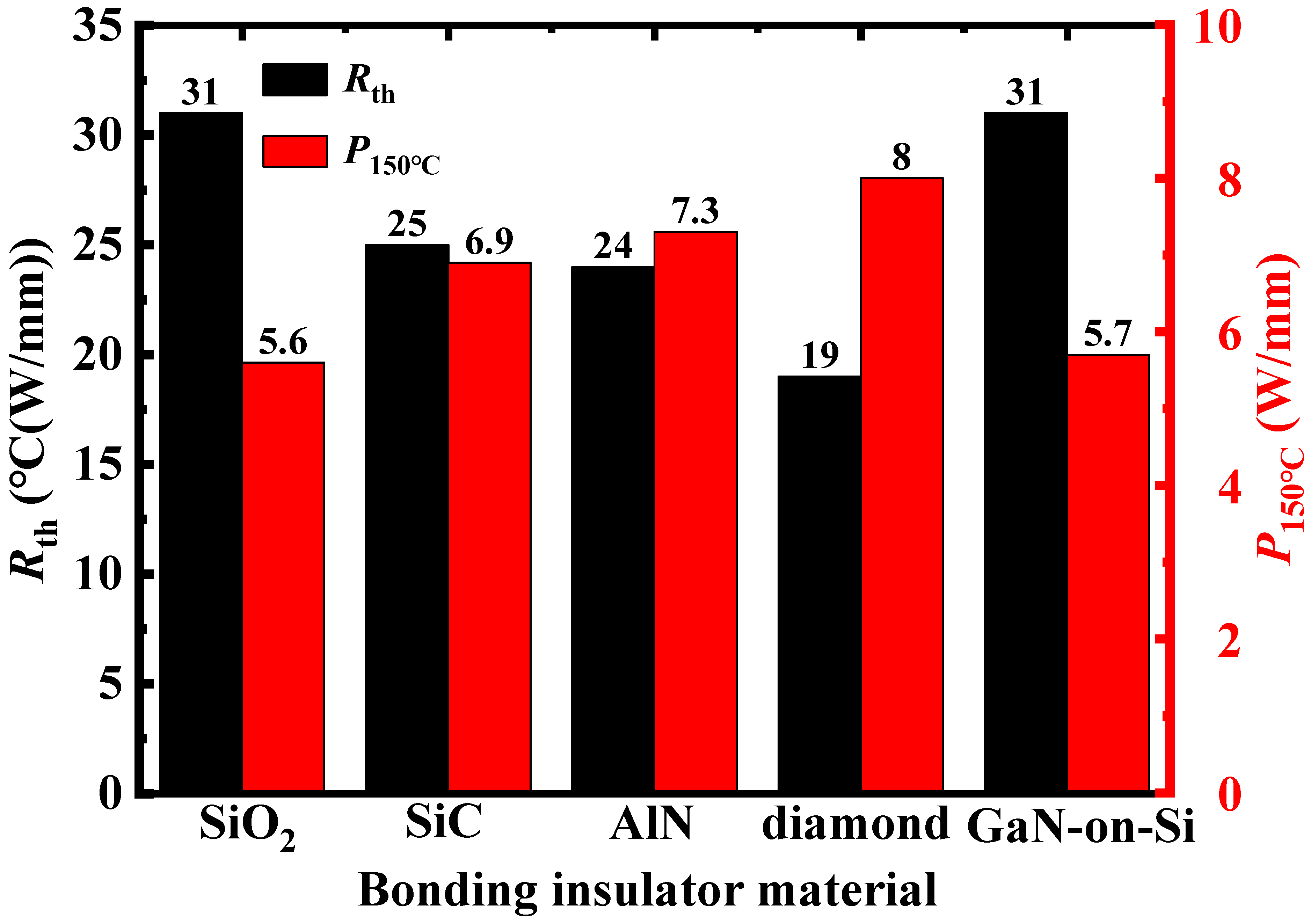

3. Simulation Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Xie, H.; Liu, Z.; Gao, Y.; Ranjan, K.; Lee, K.E.; Ng, G.I. Deeply-scaled GaN-on-Si high electron mobility transistors with record cut-off frequency fT of 310 GHz. Appl. Phys. Express 2019, 12, 126506. [Google Scholar] [CrossRef]

- Hoshi, S.; Itoh, M.; Marui, T.; Okita, H.; Morino, Y.; Tamai, I.; Toda, F.; Seki, S.; Egawa, T. 12.88 W/mm GaN high electron mobility transistor on silicon substrate for high voltage operation. Appl. Phys. Express 2009, 12, 061001. [Google Scholar] [CrossRef]

- Dumka, D.C.; Lee, C.; Tserng, H.Q.; Saunier, P.; Kumar, M. AlGaN/GaN HEMTs on Si substrate with 7 W/mm output power density at 10 GHz. Electron. Lett. 2004, 40, 1023–1024. [Google Scholar] [CrossRef]

- Marti, D.; Tirelli, S.; Alt, A.R.; Roberts, J.; Bolognesi, C.R. 150-GHz cutoff frequencies and 2-W/mm output power at 40 GHz in a millimeter-wave AlGaN/GaN HEMT technology on silicon. IEEE Electron Device Lett. 2012, 33, 1372–1374. [Google Scholar] [CrossRef]

- Shinohara, K.; Regan, D.C.; Tang, Y.; Corrion, A.L.; Brown, D.F.; Wong, J.C.; Robinson, J.F.; Fung, H.H.; Schmitz, A.; Oh, T.C.; et al. Scaling of GaN HEMTs and Schottky diodes for submillimeter-wave MMIC applications. IEEE Trans. Electron Devices 2013, 60, 2982–2996. [Google Scholar] [CrossRef]

- Wu, Y.-F.; Moore, M.; Saxler, A.; Wisleder, T.; Parikh, P. 40-W/mm double field-plated GaN HEMTs. In Proceedings of the 64th Device Research Conference, State College, PA, USA, 26–28 June 2006; pp. 151–152. [Google Scholar]

- Thompson, R.; Prunty, T.; Kaper, V.; Shealy, J.R. Performance of the AlGaN HEMT structure with a gate extension. IEEE Trans. Electron Devices 2004, 51, 292–295. [Google Scholar] [CrossRef]

- Palacios, T.; Chakraborty, A.; Rajan, S.; Poblenz, C.; Keller, S.; DenBaars, S.P.; Speck, J.S.; Mishra, U.K. High-power AlGaN/GaN HEMTs for Ka-band applications. IEEE Electron Device Lett. 2005, 26, 781–783. [Google Scholar] [CrossRef]

- Zhang, Y.; Sun, M.; Liu, Z.; Piedra, D.; Lee, H.-S.; Gao, F.; Fujishima, T.; Palacios, T. Electrothermal simulation and thermal performance study of GaN vertical and lateral power transistors. IEEE Trans. Electron Devices 2013, 60, 2224–2229. [Google Scholar] [CrossRef]

- Kuball, M.; Pomeroy, J.W. Review of raman thermography for electronic and opto-electronic device measurement with submicron spatial and nanosecond temporal resolution. IEEE Trans. Device Mater. Reliab. 2016, 16, 667–684. [Google Scholar] [CrossRef]

- Tsurumi, N.; Ueno, H.; Murata, T.; Ishida, H.; Uemoto, Y.; Ueda, T.; Inoue, K.; Tanaka, T. AlN passivation over AlGaN/GaN HFETs for surface heat spreading. IEEE Trans. Electron Devices 2010, 57, 980–985. [Google Scholar] [CrossRef]

- Lin, Z.; Liu, C.; Zhou, C.; Chai, Y.; Zhou, M.; Pei, Y. Improved performance of HEMTs with BN as heat dissipation. In Proceedings of the IEEE International Nanoelectronics Conference (INEC), Chengdu, China, 9–11 May 2016; pp. 1–2. [Google Scholar]

- Tadjer, M.J.; Anderson, T.J.; Hobart, K.D.; Feygelson, T.I.; Caldwell, J.D.; Eddy, C.R.; Kub, F.J.; Butler, J.E.; Pate, B.; Melngailis, J. Reduced self-heating in AlGaN/GaN HEMTs using nanocrystalline diamond Heat-spreading films. IEEE Electron Device Lett. 2012, 33, 23–25. [Google Scholar] [CrossRef]

- Pantellini, A.; Nanni, A.; Lanzieri, C. Thermal behavior of AlGaN/GaN HEMT on silicon microstrip technology. In Proceedings of the 6th European Microwave Integrated Circuit Conference, Manchester, UK, 10–11 October 2011; pp. 132–135. [Google Scholar]

- Belkacemi, K.; Hocine, R. Efficient 3D-TLM modeling and simulation for the thermal management of microwave AlGaN/GaN HEMT used in high power amplifiers SSPA. J. Low Power Electron. Appl. 2018, 8, 23. [Google Scholar] [CrossRef]

- Liu, Z.; Xie, H.; Lee, K.H.; Tan, C.S.; Ng, G.I.; Fitzgerald, E.A. GaN HEMTs with breakdown voltage of 2200 V realized on a 200 mm GaN-on-Insulator (GNOI)-on-Si Wafer. In Proceedings of the Symposium on VLSI Technology, Kyoto, Japan, 9–14 June 2019; pp. T242–T243. [Google Scholar]

- Liu, Z.; Xing, W.; Ng, G.I.; Fitzgerald, E.A. RF and power GaN HEMTs on 200 mm-diameter 725 μm-thick p-Si substrates. In Proceedings of the Electron Devices Technology and Manufacturing Conference (EDTM), Singapore, 12–15 March 2019; pp. 100–102. [Google Scholar]

- Zhu, W.; Zheng, G.; Cao, S.; He, H. Thermal conductivity of amorphous SiO2 thin film: A molecular dynamics study. Sci. Rep. 2018, 8, 10537. [Google Scholar] [CrossRef] [PubMed]

- Lei, M.I.; Mehregany, M. Characterization of thermoelectric properties of heavily doped n-Type polycrystalline silicon carbide thin films. IEEE Trans. Electron Devices 2013, 60, 513–517. [Google Scholar] [CrossRef]

- Belkerk, B.E.; Bensalem, S.; Soussou, A.; Carette, M.; Brithen, H.A.; Djouadi, M.A.; Scudeller, Y. Substrate-dependent thermal conductivity of aluminum nitride thin-films processed at low temperature. Appl. Phys. Lett. 2014, 105, 221905. [Google Scholar] [CrossRef]

- Duquenne, C.; Besland, M.P.; Tessier, P.Y.; Gautron, E.; Scudeller, Y.; Averty, D. Thermal conductivity of aluminium nitride thin films prepared by reactive magnetron sputtering. J. Phys. D Appl. Phys. 2012, 45, 015301. [Google Scholar] [CrossRef]

- Zhang, Y.; Teo, K.H.; Palacios, T. Beyond thermal management: Incorporating p-diamond back-barriers and cap layers into AlGaN/GaN HEMTs. IEEE Trans. Electron Devices 2016, 63, 2340–2345. [Google Scholar] [CrossRef]

- Tenbroek, B.; Bunyan, R.; Whiting, G.; Redman-White, W.; Uren, M.; Brunson, K.; Lee, M.; Edwards, C. Measurement of buried oxide thermal conductivity for accurate electrothermal simulation of SOI devices. IEEE Trans. Electron Devices 2019, 46, 251–253. [Google Scholar] [CrossRef]

- Li, X.; Wang, H.; Qiao, Z.; Zhang, Y.; Niu, Z.; Tong, C.; Liu, C. Design and Analysis of 2-μm InGaSb/GaSb Quantum Well Lasers Integrated Onto Silicon-on-Insulator (SOI) Waveguide Circuits Through an Al2O3 Bonding Layer. IEEE J. Sel. Top. Quantum Electron. 2016, 22, 16–22. [Google Scholar] [CrossRef]

- Ma, G.; Xiao, X.; Meng, B.; Ma, Y.; Xing, X.; Wang, X.; Mu, F.; Yuan, C. Robust Thermal Transport across the Surface-Active Bonding SiC-on-SiC. ACS Appl. Mater. Interfaces. 2024, 16, 20826–20834. [Google Scholar] [CrossRef]

- Bao, S.; Lee, K.H.; Chong, G.Y.; Fitzgerald, E.A.; Tan, C.S. AlN-AlN Layer Bonding and Its Thermal Characteristics. ECS J. Solid State Sci. Technol. 2015, 4, P200–P205. [Google Scholar] [CrossRef]

- Liang, J.; Kobayashi, A.; Shimizu, Y.; Ohno, Y.; Kim, S.-W.; Koyama, K.; Kasu, M.; Nagai, Y.; Shigekawa, N. Fabrication of GaN/Diamond Heterointerface and Interfacial Chemical Bonding State for Highly Efficient Device Design. Adv. Mater. 2021, 33, 2104564. [Google Scholar] [CrossRef] [PubMed]

- Cheng, Z.; Mu, F.; Yates, L.; Suga, T.; Graham, S. Interfacial Thermal Conductance across Room-Temperature-Bonded GaN/Diamond Interfaces for GaN-on-Diamond Devices. ACS Appl. Mater. Interfaces. 2020, 12, 8376–8384. [Google Scholar] [CrossRef] [PubMed]

| Material | Thermal Conductivity (W/cm·K) | Thickness (μm) |

|---|---|---|

| SiO2 | 0.012/0.012/0.012/0.012/0.012 | 0.2/0.3/0.5/1.0/2.0 |

| SiC | 0.014/0.64/0.64/0.64/0.64 | 0.2/0.3/0.5/1.0/2.0 |

| AlN | 1.0/1.0/1.05/1.2/1.3 | 0.2/0.3/0.5/1.0/2.0 |

| Diamond | 2.12/2.18/2.3/2.6/3.7 | 0.2/0.3/0.5/1.0/2.0 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hao, L.; Liu, Z.; Du, H.; Zhao, S.; Wang, H.; Zhang, J.; Hao, Y. Improvement of the Thermal Performance of the GaN-on-Si Microwave High-Electron-Mobility Transistors by Introducing a GaN-on-Insulator Structure. Micromachines 2024, 15, 1525. https://doi.org/10.3390/mi15121525

Hao L, Liu Z, Du H, Zhao S, Wang H, Zhang J, Hao Y. Improvement of the Thermal Performance of the GaN-on-Si Microwave High-Electron-Mobility Transistors by Introducing a GaN-on-Insulator Structure. Micromachines. 2024; 15(12):1525. https://doi.org/10.3390/mi15121525

Chicago/Turabian StyleHao, Lu, Zhihong Liu, Hanghai Du, Shenglei Zhao, Han Wang, Jincheng Zhang, and Yue Hao. 2024. "Improvement of the Thermal Performance of the GaN-on-Si Microwave High-Electron-Mobility Transistors by Introducing a GaN-on-Insulator Structure" Micromachines 15, no. 12: 1525. https://doi.org/10.3390/mi15121525

APA StyleHao, L., Liu, Z., Du, H., Zhao, S., Wang, H., Zhang, J., & Hao, Y. (2024). Improvement of the Thermal Performance of the GaN-on-Si Microwave High-Electron-Mobility Transistors by Introducing a GaN-on-Insulator Structure. Micromachines, 15(12), 1525. https://doi.org/10.3390/mi15121525