Solution Process-Based Thickness Engineering of InZnO Semiconductors for Oxide Thin-Film Transistors with High Performance and Stability

Abstract

:1. Introduction

2. Experimental Details [31]

2.1. Film and Device Fabrication

2.2. Film and Device Characteristics

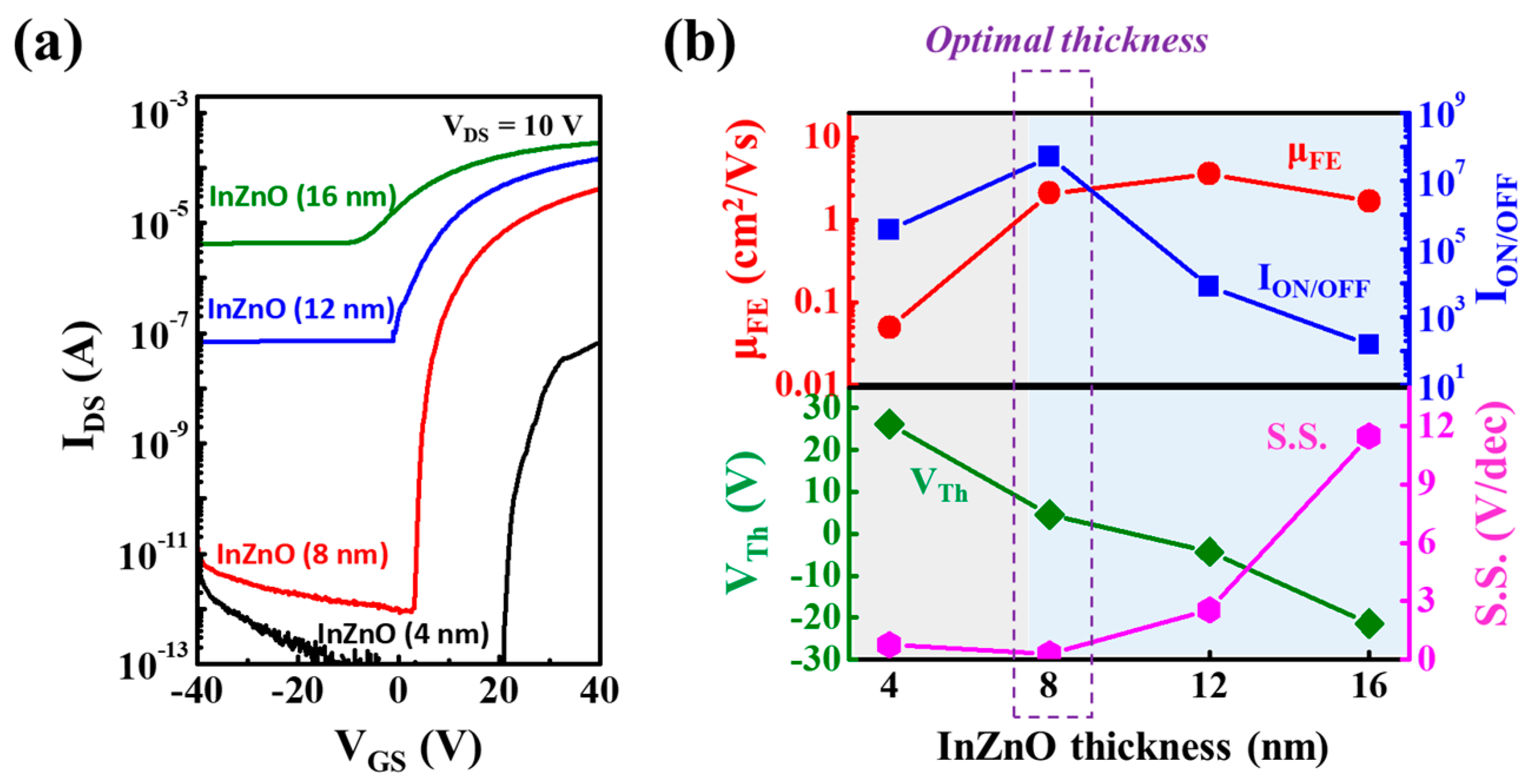

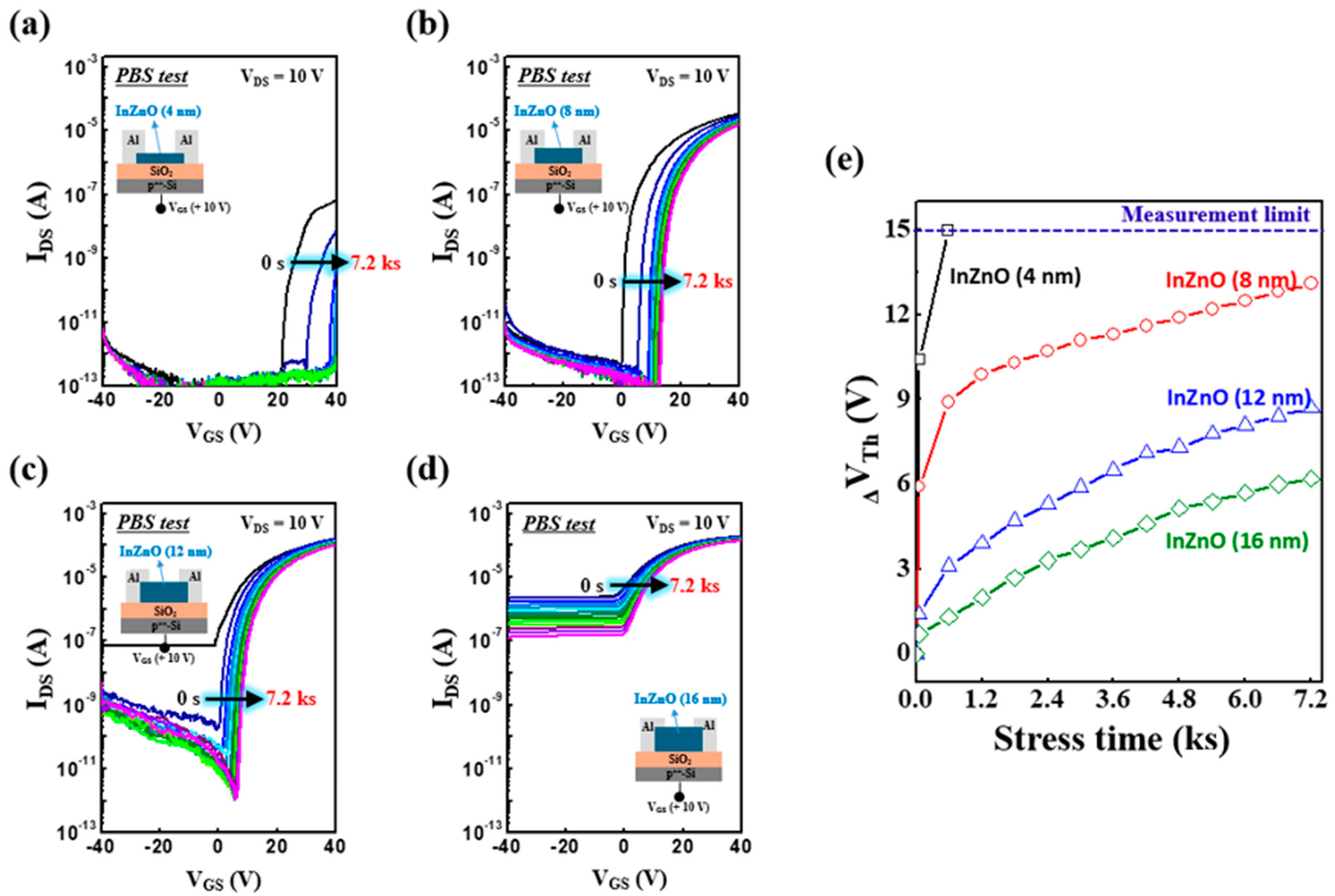

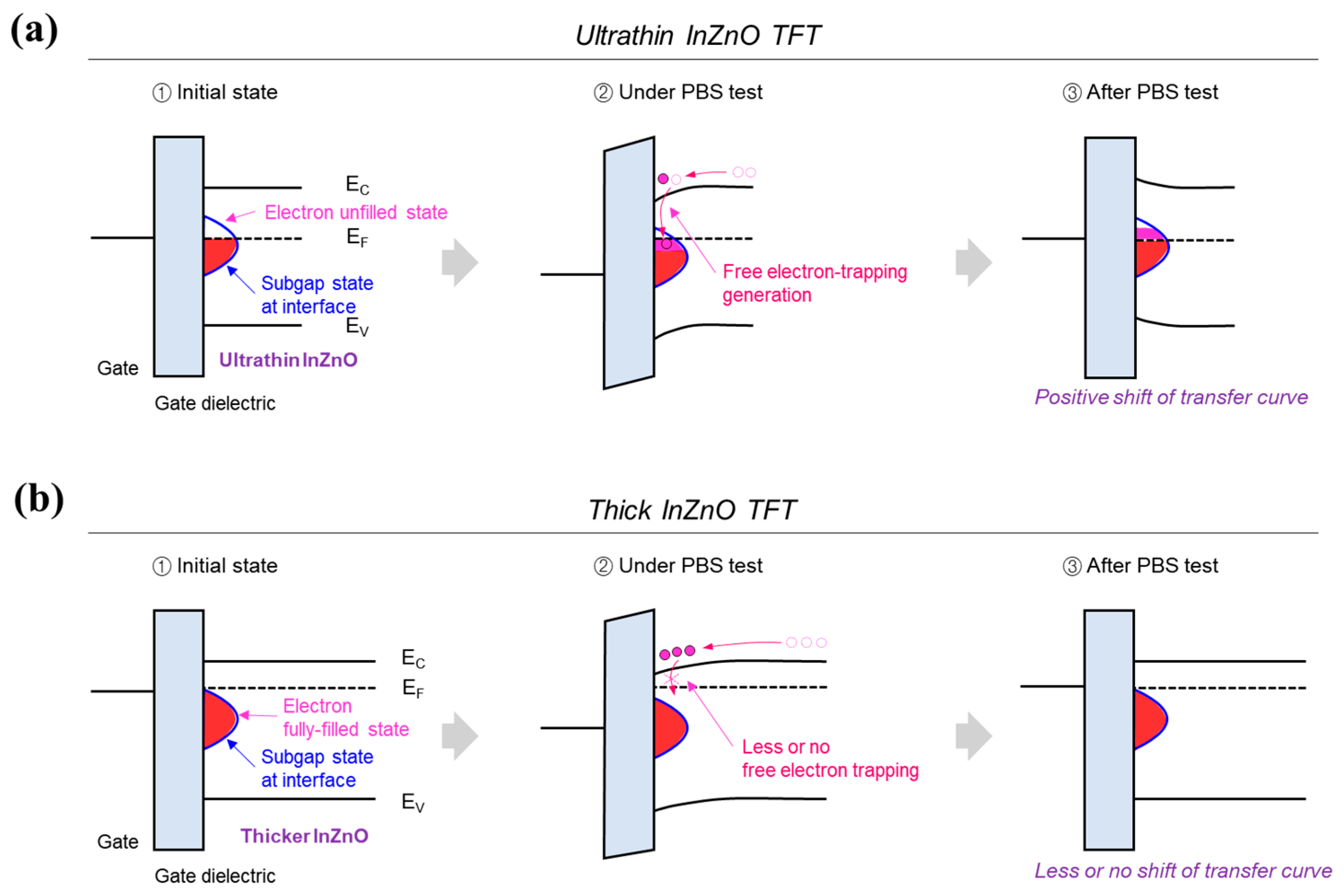

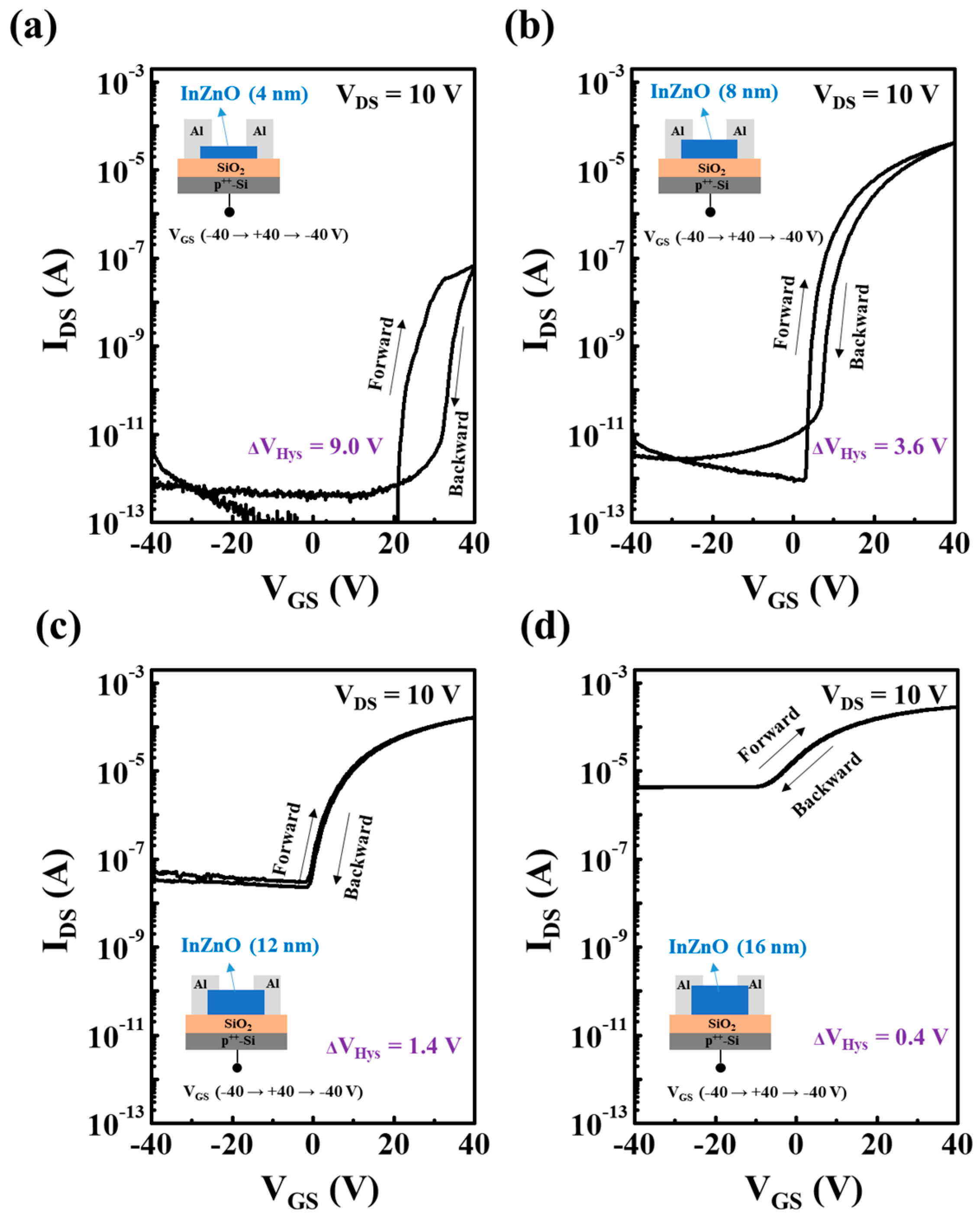

3. Results and Discussion

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhu, H.; Shin, E.-S.; Liu, A.; Ji, D.; Xu, Y.; Noh, Y.-Y. Printable Semiconductors for Backplane TFTs of Flexible OLED Displays. Adv. Funct. Mater. 2020, 30, 1904588. [Google Scholar] [CrossRef]

- Striakhilev, D.; Park, B.-K.; Tang, S.-J. Metal oxide semiconductor thin-film transistor backplanes for displays and imaging. MRS Bull. 2021, 46, 1063–1070. [Google Scholar] [CrossRef]

- Kamiya, T.; Hosono, H. Material characteristics and applications of transparent amorphous oxide semiconductors. NPG Asia Mater. 2010, 2, 15–22. [Google Scholar] [CrossRef]

- Shim, G.W.; Hong, W.; Cha, J.-H.; Park, J.H.; Lee, K.J.; Choi, S.-Y. TFT Channel Materials for Display Applications: From Amorphous Silicon to Transition Metal Dichalcogenides. Adv. Mater. 2020, 32, 1907166. [Google Scholar] [CrossRef]

- Shi, J.; Zhang, J.; Yang, L.; Qu, M.; Qi, D.-C.; Zhang, K.H.L. Wide Bandgap Oxide Semiconductors: From Materials Physics to Optoelectronic Devices. Adv. Mater. 2021, 33, 2006230. [Google Scholar] [CrossRef] [PubMed]

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef] [PubMed]

- Jo, J.-W.; Kang, S.-H.; Heo, J.S.; Kim, Y.-H.; Park, S.K. Flexible Metal Oxide Semiconductor Devices Made by Solution Methods. Chem. Eur. J. 2020, 26, 9126–9156. [Google Scholar] [CrossRef]

- Ni, Y.; Yang, L.; Liu, L.; Wei, H.; Xu, Z.; Liu, J.; Han, H.; Xu, W. Mimicking ion-balance-dependent synaptic plasticity in body fluid for adaptive environ-ment-responsive artificial neuromuscular reflexes. Mater. Today Nano 2022, 17, 100167. [Google Scholar] [CrossRef]

- Liu, L.; Cui, B.B.; Xu, W.L.; Ni, Y.; Zhang, S.; Xu, W.T. Highly aligned indium zinc oxide nanowire-based artificial synapses with low-energy consumption. J. Ind. Eng. Chem. 2020, 88, 111–116. [Google Scholar] [CrossRef]

- Xua, W.; Jianga, J.; Hanb, L.; Feng, X. Highly efficient UV-Ozone treatment for IAZO active layer to facilitate the low temperature fabrication of high performance thin film transistors. Ceram. Int. 2020, 46, 17295–17299. [Google Scholar] [CrossRef]

- Zhang, Q.; Ruan, C.; Gong, H.; Xia, G.; Wang, S. Low-temperature and high-performance ZnSnO thin film transistor activated by lightwave irradiation. Ceram. Int. 2021, 47, 20413–20421. [Google Scholar] [CrossRef]

- Jang, S.C.; Park, J.; Kim, H.-D.; Hong, H.; Chung, K.-B.; Kim, Y.J.; Kim, H.-S. Low temperature activation of amorphous In-Ga-Zn-O semiconductors using microwave and e-beam radiation, and the associated thin film transistor properties. AIP Adv. 2019, 9, 025204. [Google Scholar] [CrossRef]

- Cho, S.W.; Kim, D.E.; Kim, Y.B.; Kim, K.S.; Yoon, D.H.; Jung, S.H.; Kang, W.J.; Cho, H.K. Electrical and chemical stability engineering of solution-processed indium zinc oxide thin film transistors via a synergistic approach of annealing duration and self-combustion process. Ceram. Int. 2017, 43, 8956–8962. [Google Scholar] [CrossRef]

- Conley, J.F. Instabilities in Amorphous Oxide Semiconductor Thin-Film Transistors. IEEE Trans. Device Mater. Reliab. 2010, 10, 460–475. [Google Scholar] [CrossRef]

- Kwon, J.-Y.; Lee, D.-J.; Kim, K.-B. Transparent Amorphous Oxide Semiconductor Thin Film Transistor. Electron. Mater. Lett. 2011, 7, 1–11. [Google Scholar] [CrossRef]

- Moon, Y.-K.; Lee, S.; Kim, W.-S.; Kang, B.-W.; Jeong, C.-O.; Lee, D.-H.; Park, J.-W. Improvement in the bias stability of amorphous indium gallium zinc oxide thin-film transistors using an O2 plasma-treated insulator. Appl. Phys. Lett. 2009, 95, 013507. [Google Scholar] [CrossRef]

- Park, H.; Yoon, K.R.; Kim, S.K.; Kim, I.-D.; Jin, J.; Kim, Y.H.; Bae, B.-S. Highly Conducting In2O3 Nanowire Network with Passivating ZrO2 Thin Film for Solution-Processed Field Effect Transistors. Adv. Electron. Mater. 2016, 2, 1600218. [Google Scholar] [CrossRef]

- Cho, S.W.; Kim, D.E.; Kim, K.S.; Jung, S.H.; Cho, H.K. Towards environmentally stable solution-processed oxide thin-film transistors: A rare-metal-free oxide-based semiconductor/insulator heterostructure and chemically stable multi-stacking. J. Mater. Chem. C 2017, 5, 10498–10508. [Google Scholar] [CrossRef]

- Okamura, K.; Nikolova, D.; Mechau, N.; Hahn, H. Appropriate choice of channel ratio in thin-film transistors for the exact determination of field-effect mobility. Appl. Phys. Lett. 2009, 94, 183503. [Google Scholar] [CrossRef]

- Fortunato, E.; Barquinha, P.; Pimentel, A.; Gonçalves, A.; Marques, A.; Martins, R.; Pereira, L. Wide-bandgap high-mobility ZnO thin-film transistors produced at room temperature. Appl. Phys. Lett. 2004, 85, 2541–2543. [Google Scholar] [CrossRef]

- Hong, S.; Park, J.W.; Kim, H.J.; Kim, Y.; Kim, H.J. A review of multi-stacked active-layer structures for solution-processed oxide semiconductor thinfilm transistors. J. Inf. Disp. 2016, 17, 93–101. [Google Scholar] [CrossRef]

- Lin, Z.; Si, M.; Askarpour, V.; Niu, C.; Charnas, A.; Shang, Z.; Zhang, Y.; Hu, Y.; Zhang, Z.; Liao, P.-Y.; et al. Nanometer-Thick Oxide Semiconductor Transistor with Ultra-High Drain Current. ACS Nano 2022, 16, 21536–21545. [Google Scholar] [CrossRef]

- Li, S.; Tian, M.; Gao, Q.; Wang, M.; Li, T.; Hu, Q.; Li, X.; Wu, Y. Nanometre-thin indium tin oxide for advanced high-performance electronics. Nature Mater. 2019, 18, 1091–1097. [Google Scholar] [CrossRef]

- Yun, M.G.; Kim, S.H.; Ahn, C.H.; Cho, S.W.; Cho, H.K. Effects of channel thickness on electrical properties and stability of zinc tin oxide thin-film transistors. J. Phys. D Appl. Phys. 2013, 46, 475106. [Google Scholar] [CrossRef]

- AlGhamdi, W.S.; Fakieh, A.; Faber, H.; Lin, Y.-H.; Lin, W.-Z.; Lu, P.-Y.; Liu, C.-H.; Salama, K.N.; Anthopoulos, T.D. Impact of layer thickness on the operating characteristics of In2O3/ZnO heterojunction thin-film transistors. Appl. Phys. Lett. 2022, 121, 233503. [Google Scholar] [CrossRef]

- Li, Y.; Lan, L.; Sun, S.; Lin, Z.; Gao, P.; Song, W.; Song, E.; Zhang, P.; Peng, J. All Inkjet-Printed Metal-Oxide Thin-Film Transistor Array with Good Stability and Uniformity Using Surface-Energy Patterns. ACS Appl. Mater. Interfaces 2017, 9, 8194–8200. [Google Scholar] [CrossRef] [PubMed]

- Liang, K.; Li, D.; Ren, H.; Zhao, M.; Wang, H.; Ding, M.; Xu, G.; Zhao, X.; Long, S.; Zhu, S.; et al. Fully Printed High-Performance n-Type Metal Oxide Thin-Film Transistors Utilizing Coffee-Ring Effect. Nano-Micro Lett. 2021, 13, 164. [Google Scholar] [CrossRef]

- Kim, D.J.; Kim, D.L.; Rim, Y.S.; Kim, C.H.; Jeong, W.H.; Lim, H.S.; Kim, H.J. Improved Electrical Performance of an Oxide Thin-Film Transistor Having Multistacked Active Layers Using a Solution Process. ACS Appl. Mater. Interfaces 2012, 4, 4001–4005. [Google Scholar] [CrossRef]

- Shan, F.; Lee, J.-Y.; Zhao, H.-L.; Choi, S.G.; Koh, J.-H.; Kim, S.-J. Multi-stacking indium zinc oxide thin-film transistors post-annealed by femtosecond laser. Electron. Mater. Lett. 2021, 17, 451–458. [Google Scholar] [CrossRef]

- Shan, F.; Lee, J.-Y.; Sun, H.-Z.; Zhao, H.-L.; Wang, X.-L.; Kim, S.-J. Improvement of Electrical Performance in Solution-Processed InZnO Thin-Film Transistor with a Radio Frequency O2 Triggered Multistacked Architecture. IEEE Trans. Electron Devices 2022, 69, 4277–4282. [Google Scholar] [CrossRef]

- Zhang, X.; Cho, S.W. Composition Engineering of Indium Zinc Oxide Semiconductors for Damage-Free Back-Channel Wet Etching Metallization of Oxide Thin-Film Transistors. Micromachines 2023, 14, 1839. [Google Scholar] [CrossRef] [PubMed]

- Petti, L.; Münzenrieder, N.; Vogt, C.; Faber, H.; Büthe, L.; Cantarella, G.; Bottacchi, F.; Anthopoulos, T.D.; Tröster, G. Metal oxide semiconductor thin-film transistors for flexible electronics. Appl. Phys. Rev. 2016, 3, 021303. [Google Scholar] [CrossRef]

- Cho, S.W.; Kim, Y.B.; Jung, S.H.; Baek, S.K.; Kim, J.S.; Lee, M.; Cho, H.K.; Kim, Y.-H. All-Solution-Processed Metal Oxide/Chalcogenide Hybrid Full-Color Phototransistors with Multistacked Functional Layers and Composition-Gradient Heterointerface. Adv. Opt. Mater. 2018, 6, 1800196. [Google Scholar] [CrossRef]

- Jiang, Z.D.; Zhang, M.; Deng, S.B.; Wong, M.; Kwok, H.S. Degradation of InSnZnO Thin-Film Transistors Under Negative Bias Stress. IEEE Trans. Electron Devices 2023, 70, 6381–6386. [Google Scholar] [CrossRef]

- Jiang, Z.D.; Zhang, M.; Deng, S.B.; Yang, Y.Y.; Wong, M.; Kwok, H.S. Evaluation of Posi-tive-Bias-Stress-Induced Degradation in InSnZnO Thin-Film Transistors by Low Frequency Noise Measurement. IEEE Electron Device Lett. 2022, 43, 886–889. [Google Scholar] [CrossRef]

- Zhu, G.M.; Zhang, M.; Jiang, Z.D.; Huang, J.Y.; Huang, Y.X.; Deng, S.B.; Lu, L.; Wong, M.; Kwok, H.S. Significant Degradation Reduction in Metal Oxide Thin-Film Transistors via the Interaction of Ionized Oxygen Vacancy Redistribution, Self-Heating Effect, and Hot Carrier Effect. IEEE Trans. Electron Devices 2023, 70, 4198–4205. [Google Scholar] [CrossRef]

- Zhang, X.; Ndabakuranye, J.P.; Kim, D.W.; Choi, J.S.; Park, J. Stability Study of Solution-Processed Zinc Tin Oxide Thin-Film Transistors. Electron. Mater. Lett. 2015, 11, 964–972. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, X.; Cho, S.-W. Solution Process-Based Thickness Engineering of InZnO Semiconductors for Oxide Thin-Film Transistors with High Performance and Stability. Micromachines 2024, 15, 193. https://doi.org/10.3390/mi15020193

Zhang X, Cho S-W. Solution Process-Based Thickness Engineering of InZnO Semiconductors for Oxide Thin-Film Transistors with High Performance and Stability. Micromachines. 2024; 15(2):193. https://doi.org/10.3390/mi15020193

Chicago/Turabian StyleZhang, Xuan, and Sung-Woon Cho. 2024. "Solution Process-Based Thickness Engineering of InZnO Semiconductors for Oxide Thin-Film Transistors with High Performance and Stability" Micromachines 15, no. 2: 193. https://doi.org/10.3390/mi15020193

APA StyleZhang, X., & Cho, S.-W. (2024). Solution Process-Based Thickness Engineering of InZnO Semiconductors for Oxide Thin-Film Transistors with High Performance and Stability. Micromachines, 15(2), 193. https://doi.org/10.3390/mi15020193