A Cross-Process Signal Integrity Analysis (CPSIA) Method and Design Optimization for Wafer-on-Wafer Stacked DRAM

Abstract

:1. Introduction

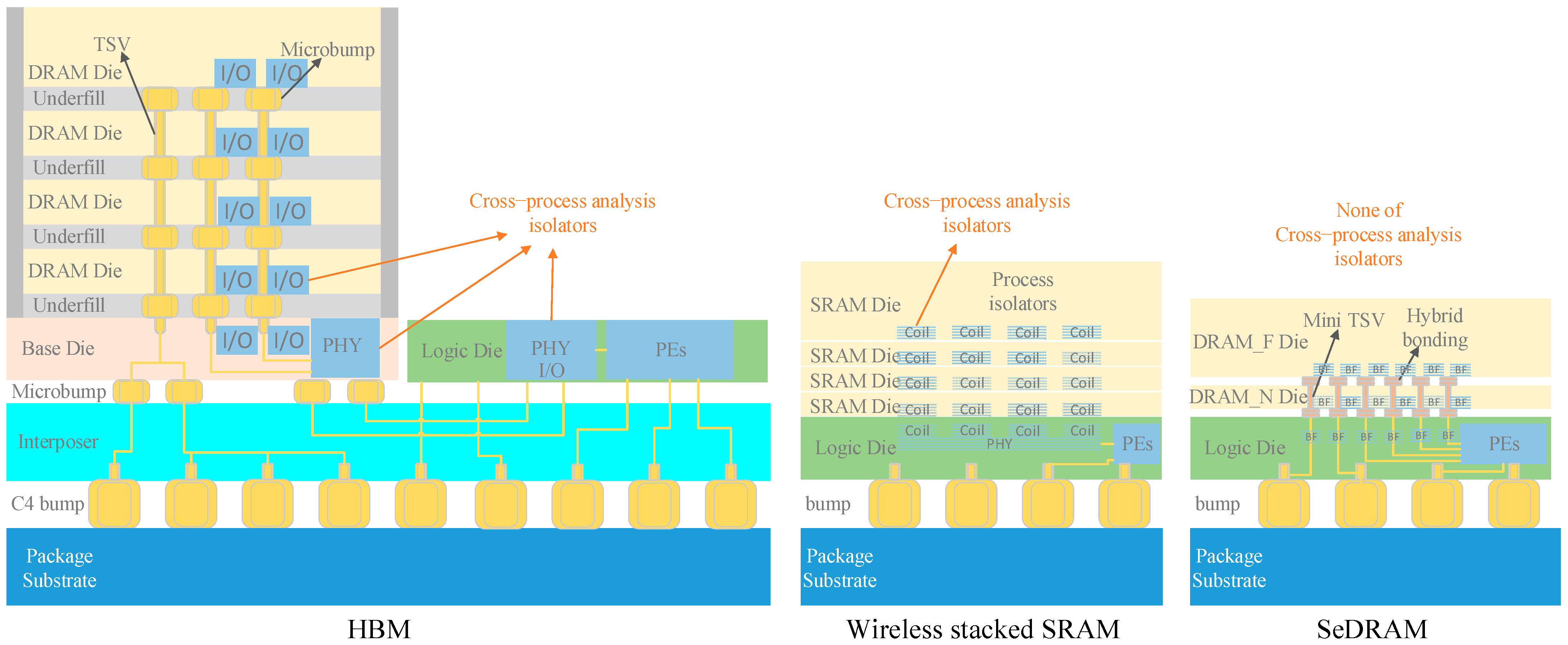

- High Bandwidth Memory (HBM) improves the memory access performance by a Through-Silicon Via (TSV) structured 2.5D near-memory architecture [22,23]. The DRAM dies in HBM are stacked through TSVs and microbumps, forming a DRAM stack. The DRAM stack is horizontally interconnected with logic through an interposer. All DRAM dies and logic dies are independently designed with their respective I/O circuits. These I/O circuits act as isolators for cross-process analysis, segmenting the design and analysis within the HBM package into DRAM, logic, and package-based interconnections. The SI design of constructing an HBM stack is fundamentally packaging design [20].

- Ref. [16] reports a wireless stacked Static Random Access Memory (SRAM) which utilizes semiconductor process coils to establish a vertical data path between four SRAM dies and a logic die, creating a 3D near-memory architecture. In ref. [16], there is no metal-based signal interconnect between SRAM dies and the logic die (“Power supplies are provided via bonded wires”). The interconnection between the two different semiconductor processes is achieved through a magnetic field model within the package of this structure. As a virtual model, the magnetic field model is not constrained by any stacking manufacturing process, simplifying the SI analysis of this structure.

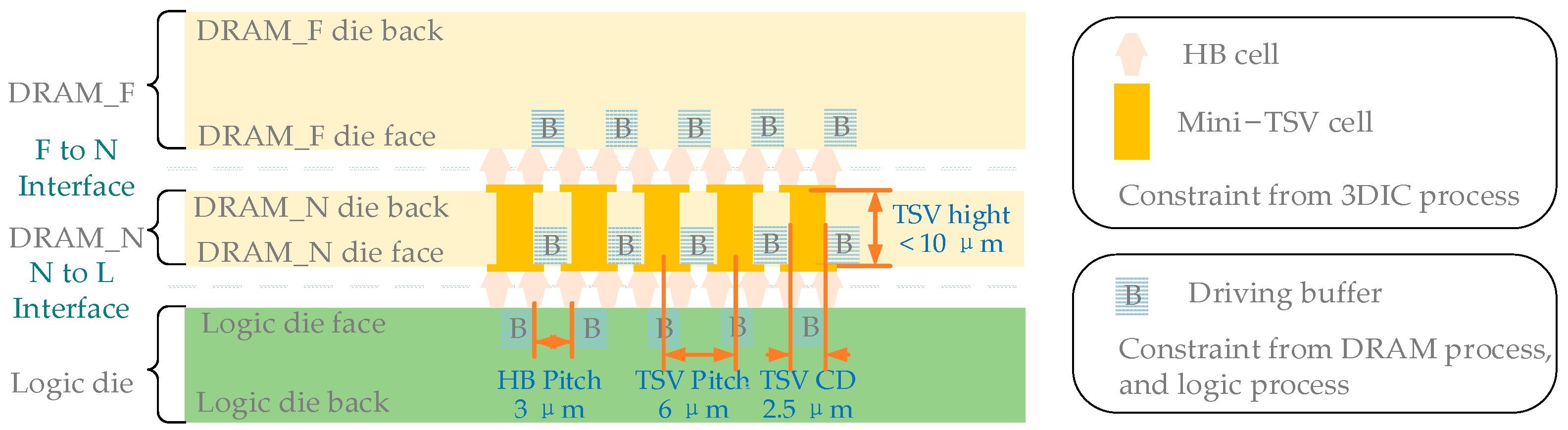

- Refs. [17,18] report a Stacked Embedded DRAM (SeDRAM) architecture, a noteworthy technology in the industry in recent years and the study target of this paper. SeDRAM vertically stacks DRAM dies and a logic die into a hybrid 3DIC package, resulting in the shortest physical distance for memory access at the micron level [24]. Unlike HBM’s packaging integration technology, SeDRAM utilizes a Wafer-on-Wafer (WoW) Back-End-of-the-Line (BEOL) 3DIC process for manufacturing mini-TSV and Hybrid Bonding (HB) to establish high-density vertical memory access interconnects between memory and computing units, significantly enhancing memory access efficiency [25]. In this 3DIC package, a substantial number of mini-TSV and HB cells are used for interconnecting data paths. 3DIC path of SeDRAM is driven by DRAM and logic buffers, creating a cross-process signal integrity analysis environment. As a result, three different semiconductor manufacturing processes, namely, DRAM, logic, and 3DIC, are integrated into the overall design, making it challenging to distinguish boundaries of signal integrity design and analysis. Addressing the aforementioned issues, this paper proposes the Cross-Process Signal Integrity Analysis (CPSIA) method.

2. Study of the 3DIC Model

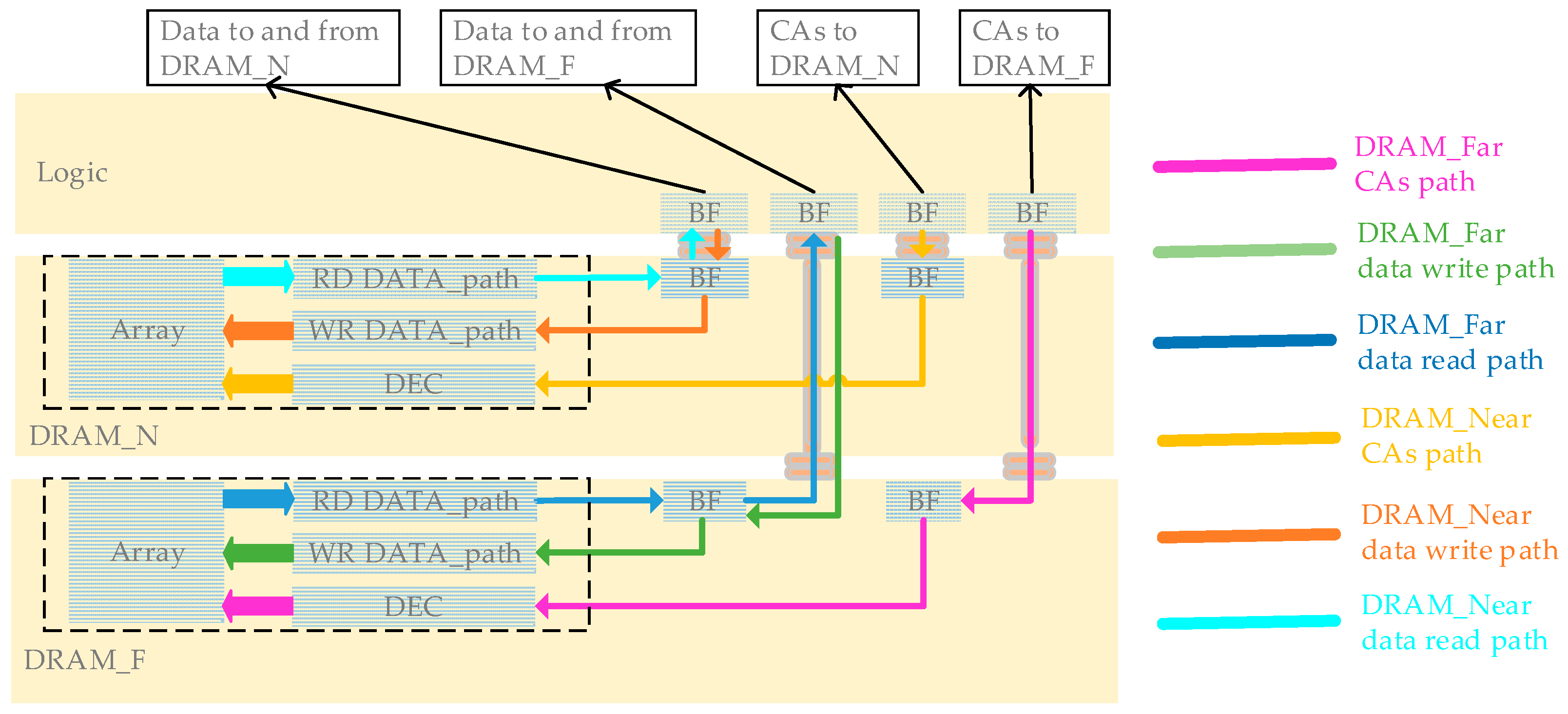

2.1. Introduction of Study Target

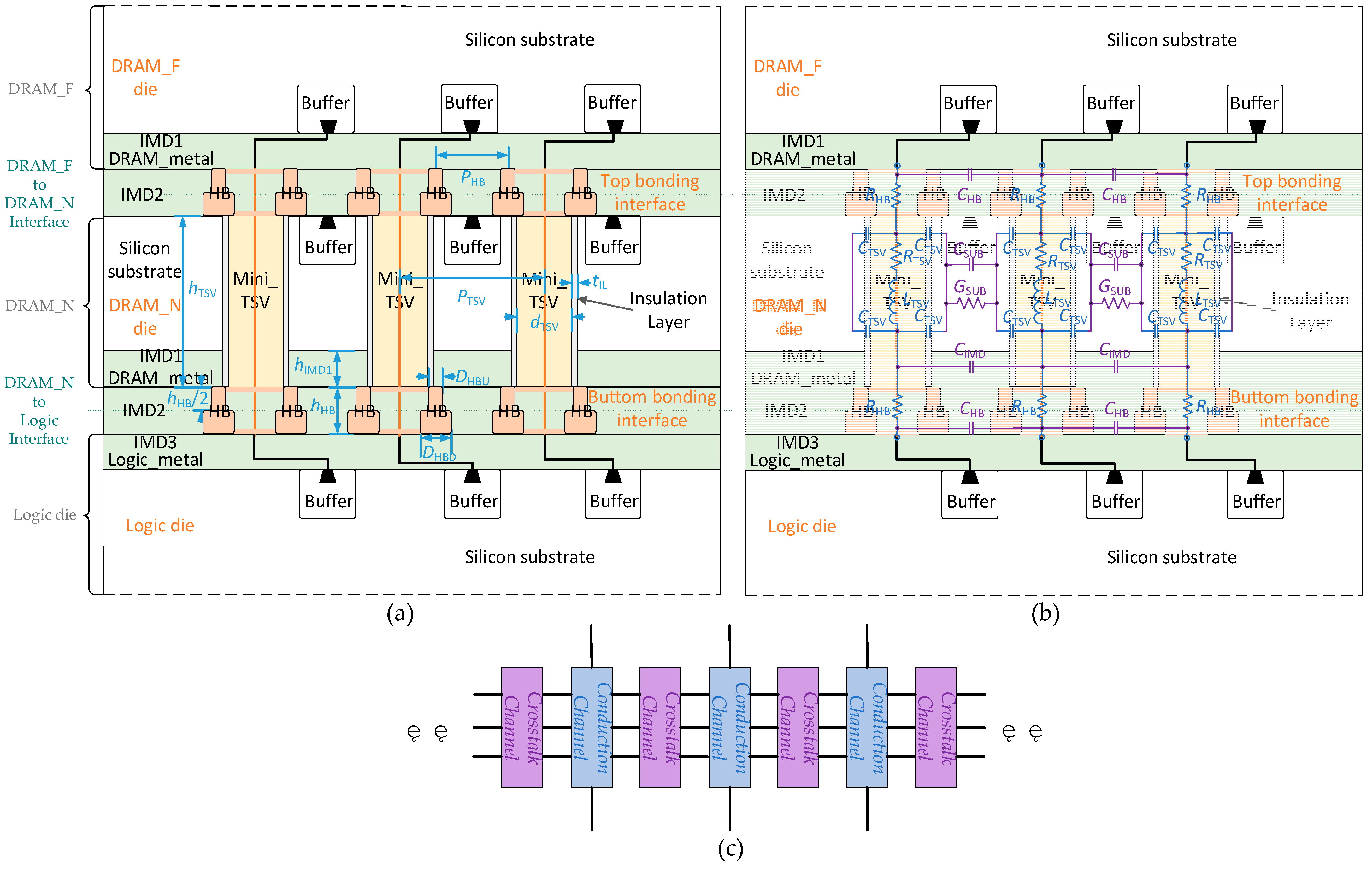

2.2. Lumped Circuit Model of Vertical Stacking Paths

- , the equivalent resistance of the dual HB cell structure;

- and , the equivalent resistance and inductance of the mini-TSV cell connecting the backside and top metal layers of DRAM_N;

- , the distributed capacitance formed by the outer surface of the mini-TSV copper pillar and the DRAM_N substrate, enclosed by the insulation layer (SiO2) surrounding the TSV.

- , the distributed capacitance formed by the adjacent dual HB cell structures through the IMD2 medium;

- , the distributed capacitance formed by the adjacent mini-TSV cells through the Inter-Metal Dielectric 1 (IMD1) medium (the metal layer of DRAM_N);

- and , the equivalent capacitance and conductance formed by the adjacent mini-TSV cells through the medium of the DRAM_N substrate.

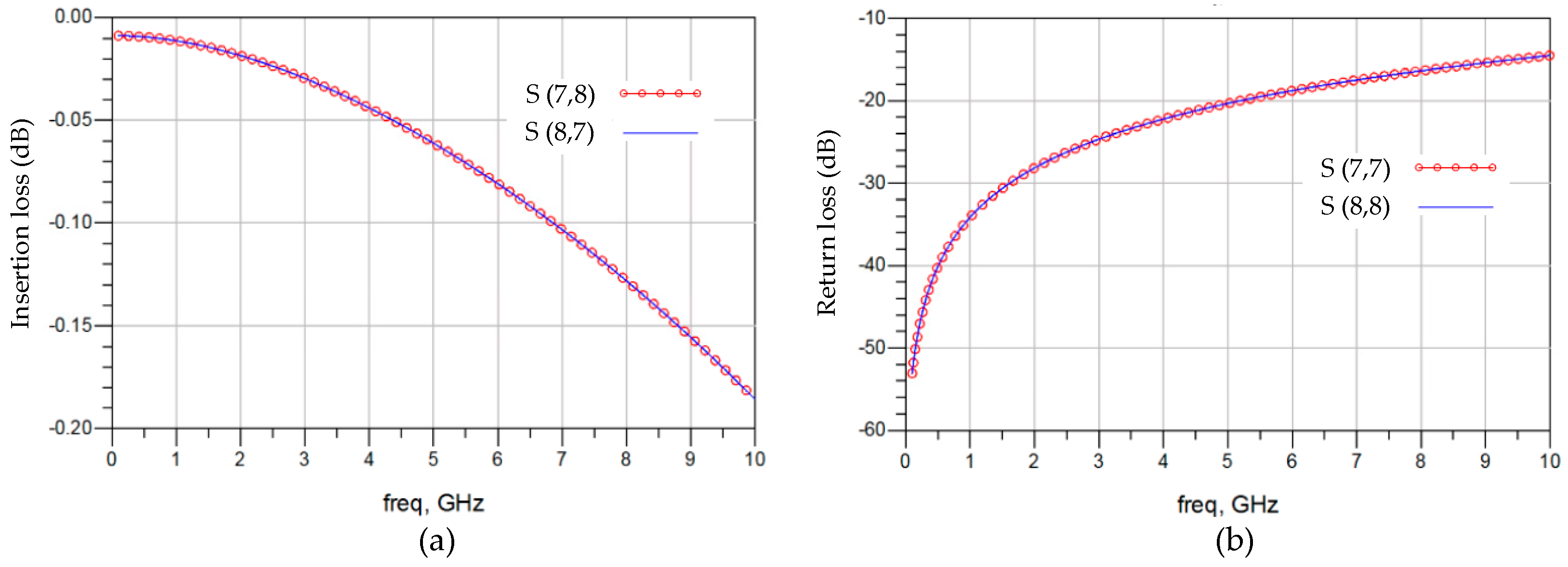

2.3. Frequency-Domain Analysis

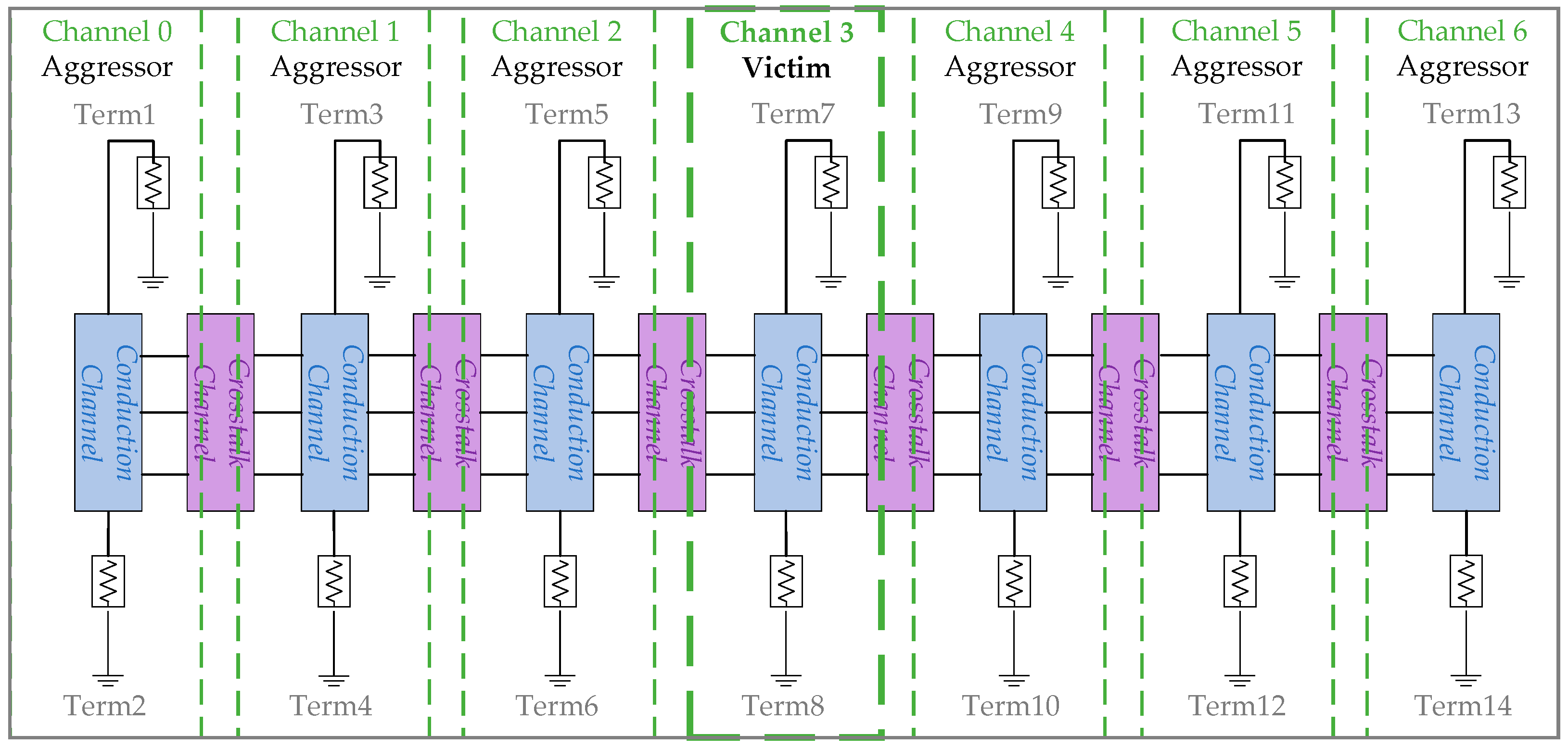

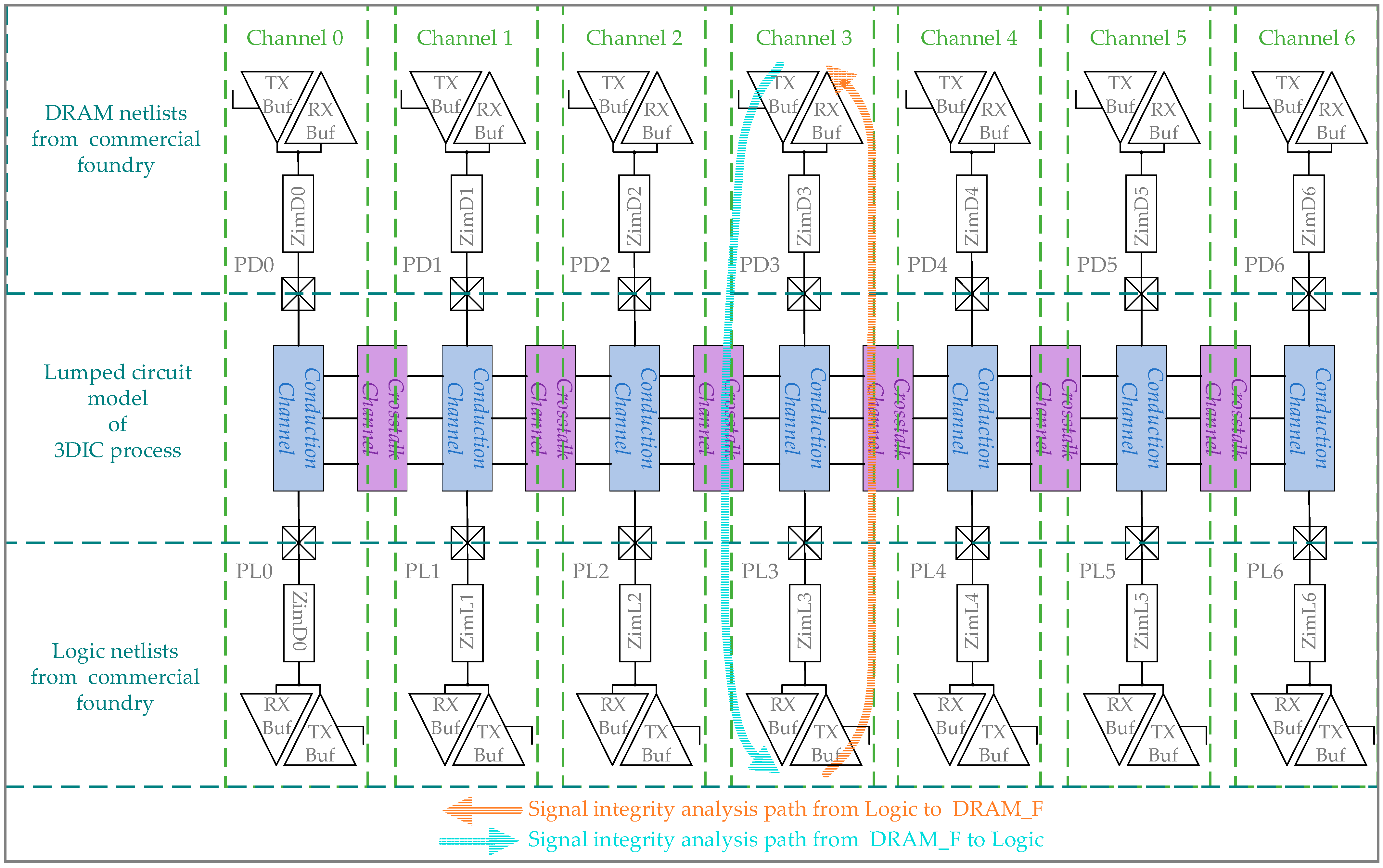

3. Cross-Process Analysis

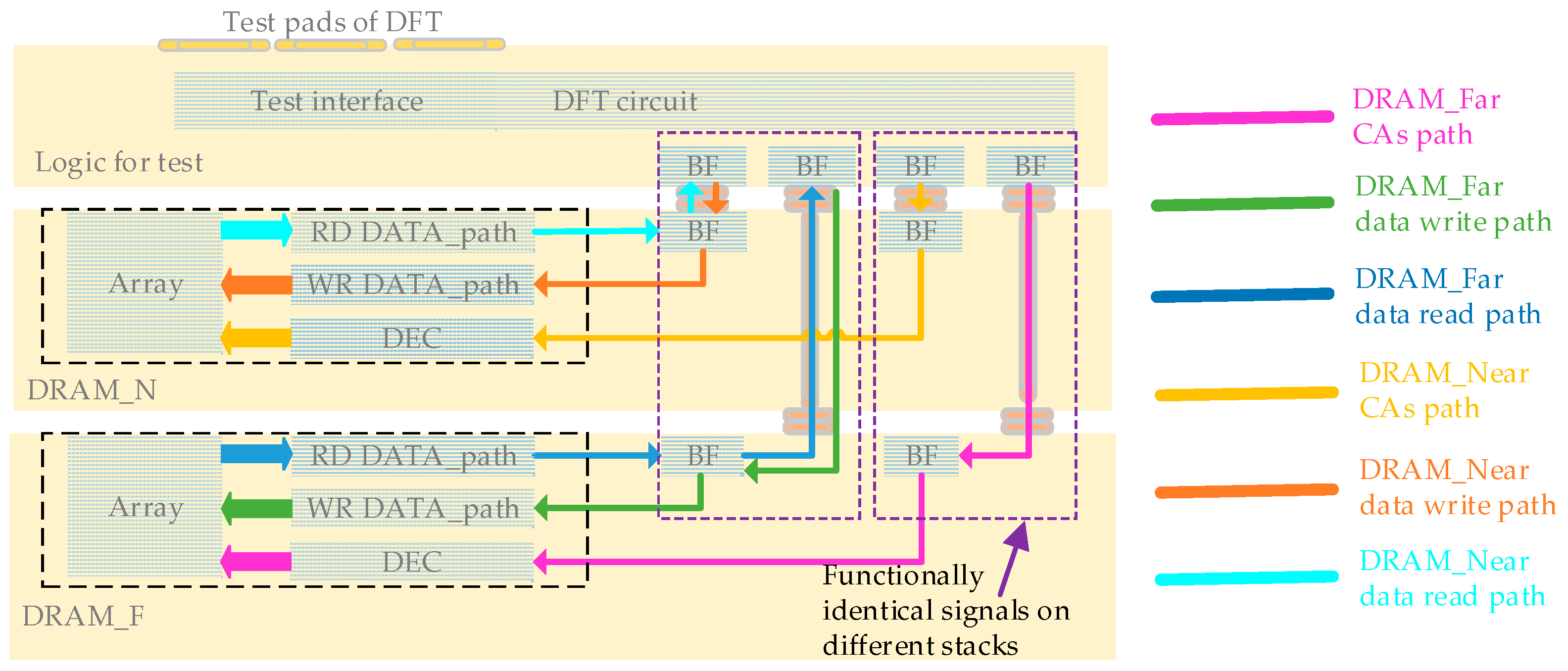

3.1. CPSIA Method

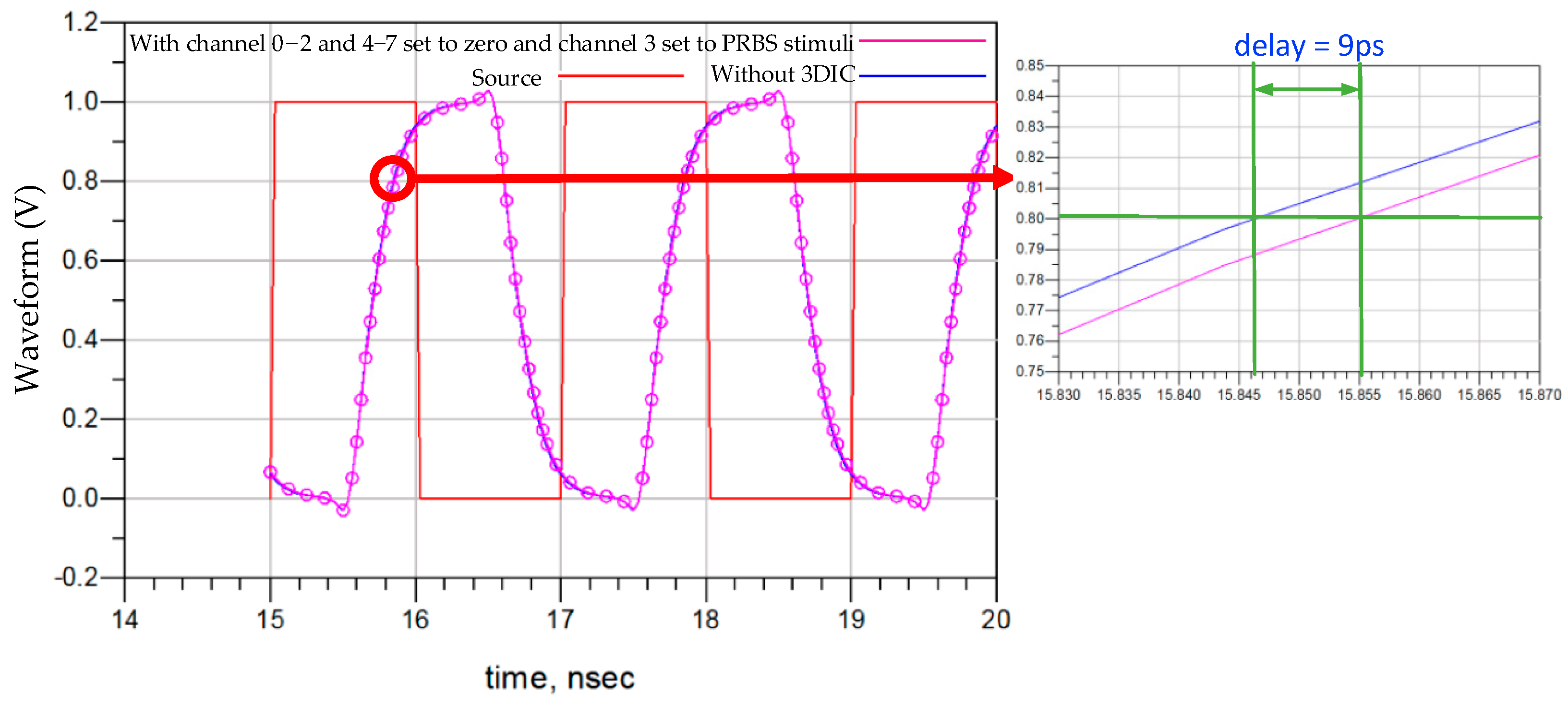

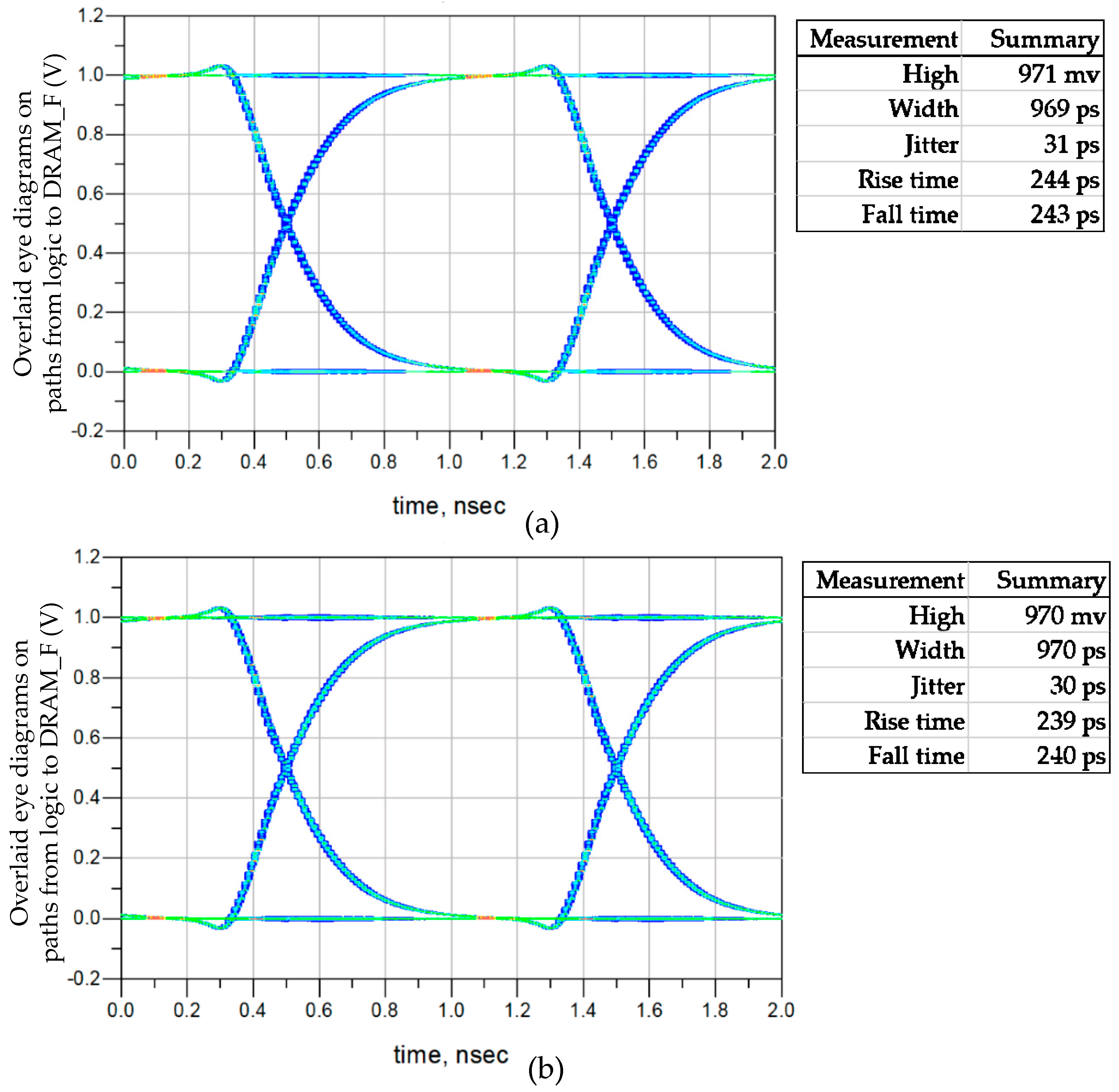

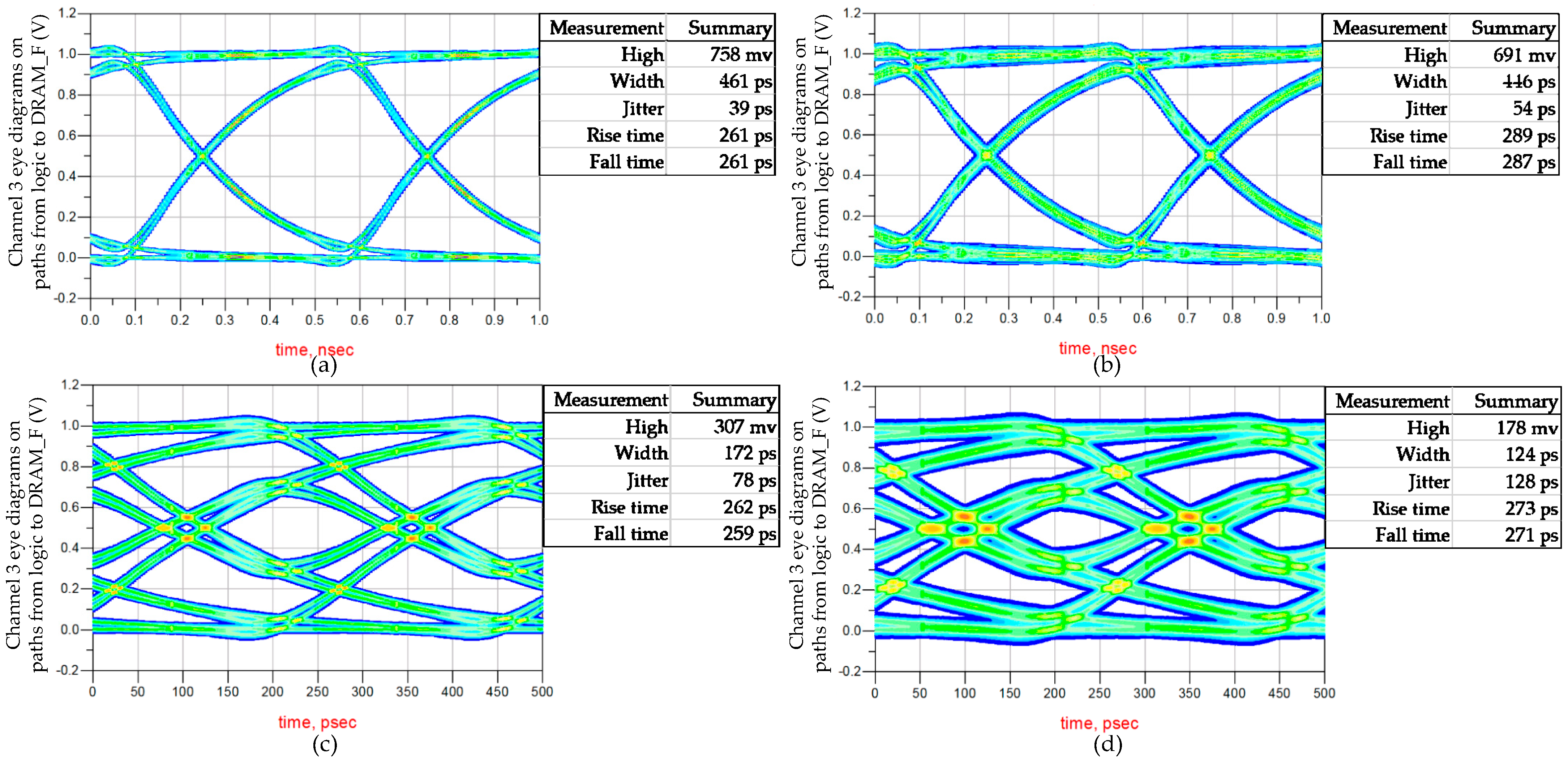

3.2. Impact Analysis Introduced by 3DIC

3.3. Design Optimization of Vertical Stacking

- A 1HB+1TSV+1HB structure is employed for testing signal interconnects.

- A 2HB+1TSV+2HB structure is employed for interconnecting memory access data signals, such as DQs and CAs. Its advantages include reducing the contact resistance of HB cells in the data path and enhancing the product yield targets.

- A 4HB+1TSV+4HB structure is utilized for the power network. Four sets of HBs in parallel are used to address the high contact resistance issue in HBs, reducing voltage drop and current density in HB cells.

4. Physical Testing and Result Analyses

4.1. The Test Chip

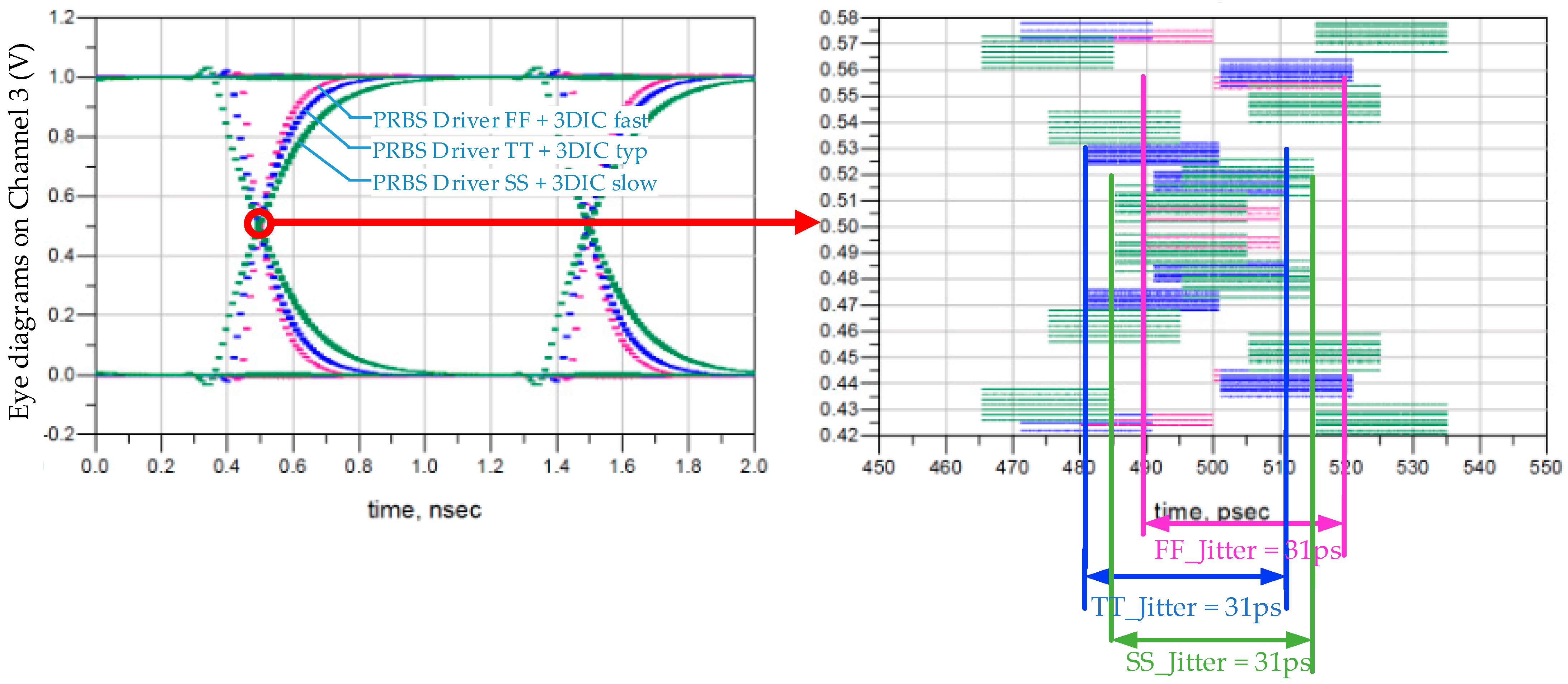

4.2. Analysis of Test Results

4.3. Model Extension

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Sebastian, S.; Gallo, M.L.; Khaddam-Aljameh, R.; Eleftheriou, E. Memory devices and applications for in-memory computing. Nat. Nanotechnol. 2020, 15, 529–544. [Google Scholar] [CrossRef] [PubMed]

- Khan, K.; Pasricha, S.; Kim, R.G. A Survey of Resource Management for Processing-in-Memory and Near-Memory Processing Architectures. J. Low Power Electron. Appl. 2020, 10, 30. [Google Scholar] [CrossRef]

- Santoro, G.; Turvani, G.; Graziano, H. New Logic-in-Memory Paradigms: An Architectural and Technological Perspective. Micromachines 2019, 10, 368. [Google Scholar] [CrossRef] [PubMed]

- Tian, W.; Li, B.; Li, Z.; Cui, H.; Shi, J.; Wang, Y.; Zhao, J. Using Chiplet Encapsulation Technology to Achieve Processing-in-Memory Functions. Micromachines 2022, 13, 1790. [Google Scholar] [CrossRef] [PubMed]

- Horowitz, M. Computing’s Energy Problem (and what we can do about it). In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 9–13 February 2014. [Google Scholar]

- Ke, L.; Zhang, X.; So, J.; Lee, J.G.; Kang, S.H.; Lee, S.; Han, S.; Cho, Y.G.; Kim, J.H.; Kwon, Y.; et al. Near-Memory Processing in Action: Accelerating Personalized Recommendation With AxDIMM. IEEE Micro 2022, 12, 116–127. [Google Scholar] [CrossRef]

- Mutlu, O.; Ghose, S.; Gómez-Luna, J.; Ausavarungnirun, R. Processing data where it makes sense: Enabling in-memory computation. Microprocess. Microsyst. 2019, 67, 28–41. [Google Scholar] [CrossRef]

- Spessot, A.; Oh, H. 1T-1C Dynamic Random Access Memory Status, Challenges, and Prospects. IEEE Trans. Electron. Devices 2020, 67, 1382–1393. [Google Scholar] [CrossRef]

- Lee, S.; Cho, H.; Son, Y.H.; Ro, Y.; Kim, N.S.; Ahn, J.U. Leveraging Power-Performance Relationship of Energy-Efficient Modern DRAM Devices. IEEE Access 2018, 6, 31387–31398. [Google Scholar] [CrossRef]

- Park, N.; Ryu, S.; Kung, J.; Kim, J.-J. High-throughput Near-Memory Processing on CNNs with 3D HBM-like Memory. ACM Trans. Des. Autom. Electron. Syst. 2021, 26, 1–20. [Google Scholar] [CrossRef]

- Bernhardt, A.; Koch, A.; Petrov, I. pimDB: From Main-Memory DBMS to Processing-In-Memory DBMS-Engines on Intelligent Memories. In Proceedings of the 19th International Workshop on Data Management on New Hardware, DaMoN ‘23, Seattle, WA, USA, 18–23 June 2023; pp. 44–52. [Google Scholar]

- Qureshi, Y.M.; Simon, W.A.; Zapater, M.; Olcoz, K.; Atienza, D. Gem5-X: A Many-core Heterogeneous Simulation Platform for Architectural Exploration and Optimization. ACM Trans. Archit. Code Optim. 2021, 18, 1–27. [Google Scholar] [CrossRef]

- Zhou, M.; Xu, W.; Kang, J.; Rosing, T. TransPIM: A Memory-based Acceleration via Software-Hardware Co-Design for Transformer. In Proceedings of the IEEE International Symposium on High-Performance Computer Architecture (HPCA), Seoul, Republic of Korea, 2–6 April 2022; pp. 1071–1085. [Google Scholar]

- Lee, D.U.; Cho, H.S.; Kim, J.; Ku, Y.J.; Oh, S.; Kim, C.D.; Kim, H.W.; Lee, W.Y.; Kim, T.K.; Yun, T.S.; et al. A 128 Gb 8-High 512 GB/s HBM2E DRAM with a Pseudo Quarter Bank Structure, Power Dispersion and an Instruction-Based At-Speed PMBIST. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 16–20 February 2020. [Google Scholar]

- Park, M.J.; Cho, H.S.; Yun, T.S.; Byeon, S.; Koo, Y.J.; Yoon, S.; Lee, D.U.; Choi, S.; Park, J.; Lee, J.; et al. A 192-Gb 12-High 896-GB/s HBM3 DRAM with a TSV Auto-Calibration Scheme and Machine-Learning-Based Layout Optimization. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022. [Google Scholar]

- Shiba, K.; Okada, M. A 7-nm FinFET 1.2-TB/s/mm2 3D-Stacked SRAM Module with 0.7-pJ/b Inductive Coupling Interface Using Over-SRAM Coil and Manchester-Encoded Synchronous Transceiver. IEEE J. Solid-State Circuits 2023, 58, 2075–2086. [Google Scholar] [CrossRef]

- Wang, S.; Jiang, X.; Bai, F.; Xiao, W.; Long, X.; Ren, Q.; Kang, Y. A True Process-Heterogeneous Stacked Embedded DRAM Structure Based on Wafer-Level Hybrid Bonding. Electronics 2023, 12, 1077. [Google Scholar] [CrossRef]

- Wang, S.; Yu, B.; Xiao, W.; Bai, F.; Long, X.; Bai, L.; Jia, X.; Zuo, F.; Tan, J.; Guo, Y.; et al. An 85 GBps/Gbit 0.66 pJ/bit Stacked DRAM with Multilayer Arrays by Fine Pitch Hybrid Bonding and Mini-TSV. In Proceedings of the IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Kyoto, Japan, 11–16 June 2023. [Google Scholar]

- Beyene, W.; Juneja, N.; Hahm, Y.-C.; Kollipara, R.; Kim, J. Signal and Power Integrity Analysis of High-Speed Links with Silicon Interposer. In Proceedings of the IEEE 67th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2017; pp. 2377–5726. [Google Scholar]

- Kim, J.; Pak, J.P.; Cho, J.; Song, E.; Cho, J.; Kim, H.; Song, T.; Lee, J.; Lee, H.; Park, K.; et al. High-Frequency Scalable Electrical Model and Analysis of a Through Silicon Via (TSV). IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 181–195. [Google Scholar]

- Tsai, Y.C.; Lee, C.H.; Chang, H.C.; Liu, J.H.; Hu, H.W.; Ito, H.; Kim, Y.S.; Ohba, T.; Chen, K.-N. Electrical Characteristics and Reliability of Wafer-on-Wafer (WOW) Bumpless Through-Silicon Via. IEEE Trans. Electron. Devices 2021, 68, 3520–3525. [Google Scholar] [CrossRef]

- Amin Farmahini-Farahani, A.; Gurumurthi, S.; Loh, G.; Ignatowski, M. Challenges of High-Capacity DRAM Stacks and Potential Directions. In Proceedings of the MCHPC’18: Proceedings of the Workshop on Memory Centric High Performance Computing, Dallas, TX, USA, 4–13 November 2018. [Google Scholar]

- Sakui, K.; Ohba, T. High Bandwidth Memory (HBM) and High Bandwidth NAND (HBN) with the Bumpless TSV Technology. In Proceedings of the International 3D Systems Integration Conference (3DIC), Sendai, Japan, 8–10 October 2019. [Google Scholar]

- Bai, F.; Jiang, X.; Wang, S.; Yu, B.; Tan, J.; Zuo, F.; Wang, C.; Wang, F.; Long, X.; Yu, G.; et al. A Stacked Embedded DRAM Array for LPDDR4/4X using Hybrid Bonding 3D Integration with 34 GB/s/1 Gb 0.88 pJ/b Logic-to-Memory Interface. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020. [Google Scholar]

- Niu, D.; Li, S.; Wang, Y.; Han, W.; Zhang, Z.; Guan, Y.; Guan, T.; Sun, F.; Xue, F.; Duan, L.; et al. 184QPSW 64 Mb/mm2 3D Logic-to-DRAM Hybrid Bonding with Process-Near-Memory Engine for Recommendation System. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022. [Google Scholar]

- Cho, J.; Song, E.; Yoon, K.; Pak, J.S.; Kim, J.; Lee, W.; Song, T.; Kim, K.; Lee, J.; Lee, H.; et al. Modeling and Analysis of Through-Silicon Via (TSV) Noise Coupling and Suppression Using a Guard Ring. IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 220–233. [Google Scholar] [CrossRef]

- Sadiku, M.N.O. Transmission Lines. In Book Elements of Electromagnetics, 7th ed.; Sedra, A.S., Ed.; Oxford University Press: New York, NY, USA, 2018; Volume II, pp. 554–555. [Google Scholar]

| HBM [14,15] | Wireless Stacked SRAM [16] | SeDRAM [17,18] | |

|---|---|---|---|

| Integration | 2.5D | 3D | 3D |

| Memory | DRAM | High-density SRAM | DRAM |

| Stacked Structure | 4~8 memory + 1 logic | 4 memory + 1 logic | 2~8 memory + 1 logic |

| Vertical Interconnection | TSV + microbump + interposer | None | HB + mini-TSV |

| Metal | Wireless | Metal | |

| Package | None | WoW BEOL | |

| Related Processes | DRAM and logic | Logic 1 and logic 2 | DRAM, logic, and 3DIC |

| Interface between Stacked Memory and Logic | I/O | Coil on logic die | Buffer |

| Separation of Processes | Yes, by I/O circuit | Yes, by magnetic field | No |

| SI Analysis Method | Package-based validation | Virtual model | CPSIA |

| Dimensions | Value | Unit | Description | |

|---|---|---|---|---|

| TSV | 10 | TSV height | ||

| 2.5 | TSV diameter | |||

| 6 | TSV pitch | |||

| HB | 2 | HB height | ||

| 0.6 | Up part of HB diameter | |||

| 1.5 | Down part of HB diameter | |||

| 3 | HB pitch | |||

| Insulation Layer | 0.2 | Insulation layer thick | ||

| IMD1 | 3 | IMD1 height |

| Parameters | Value | Unit | Description | |

|---|---|---|---|---|

| TSV | Resistivity of TSV (Cu) | |||

| 1 | \ | Relative permeability of TSV | ||

| HB | Resistivity of HB (Cu) | |||

| Si Sub | Conductivity of Si Sub | |||

| \ | Relative permittivity of Si Sub | |||

| IMD1/IMD2 | \ | Relative permittivity of IMD | ||

| Insulation Layer | \ | Relative permittivity of insulator | ||

| Free Space | Permittivity of free space | |||

| Permeability of free space |

| Function | Medium | Parameters | Value | Unit | Description |

|---|---|---|---|---|---|

| Conduction | TSV | 34.22 | Equivalent resistance of mini-TSV | ||

| 3.138 | Equivalent inductance of the dual HB structure | ||||

| HB | 34.46 | Equivalent resistance of the dual HB structure | |||

| Insulation Layer | 2.689 | Distributed capacitance between the mini-TSV copper pillar and the DRAM_N substrate | |||

| Crosstalk | IMD2 | 0.136 | Distributed capacitance between adjacent dual HBs | ||

| IMD1 | 0.225 | Distributed capacitance between adjacent mini-TSVs | |||

| Si Sub | 0.144 | mS | Equivalent conductance of SI Sub | ||

| 1.522 | Equivalent capacitance of SI Sub |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jiang, X.; Jia, X.; Wang, S.; Guo, Y.; Guo, F.; Long, X.; Geng, L.; Yang, J.; Liu, M. A Cross-Process Signal Integrity Analysis (CPSIA) Method and Design Optimization for Wafer-on-Wafer Stacked DRAM. Micromachines 2024, 15, 557. https://doi.org/10.3390/mi15050557

Jiang X, Jia X, Wang S, Guo Y, Guo F, Long X, Geng L, Yang J, Liu M. A Cross-Process Signal Integrity Analysis (CPSIA) Method and Design Optimization for Wafer-on-Wafer Stacked DRAM. Micromachines. 2024; 15(5):557. https://doi.org/10.3390/mi15050557

Chicago/Turabian StyleJiang, Xiping, Xuerong Jia, Song Wang, Yixin Guo, Fuzhi Guo, Xiaodong Long, Li Geng, Jianguo Yang, and Ming Liu. 2024. "A Cross-Process Signal Integrity Analysis (CPSIA) Method and Design Optimization for Wafer-on-Wafer Stacked DRAM" Micromachines 15, no. 5: 557. https://doi.org/10.3390/mi15050557

APA StyleJiang, X., Jia, X., Wang, S., Guo, Y., Guo, F., Long, X., Geng, L., Yang, J., & Liu, M. (2024). A Cross-Process Signal Integrity Analysis (CPSIA) Method and Design Optimization for Wafer-on-Wafer Stacked DRAM. Micromachines, 15(5), 557. https://doi.org/10.3390/mi15050557