Abstract

A novel high-speed and process-compatible carrier-stored trench-gate bipolar transistor (CSTBT) combined with split-gate technology is proposed in this paper. The device features a split polysilicon electrode in the trench, where the left portion is equipotential with the cathode. This design mitigates the impact of the anode on the trench gate, resulting in a reduction in the gate-collector capacitance (CGC) to improve the dynamic characteristics. On the left side of the device cell, the P-layer, the carrier-stored (CS) layer and the P-body are formed from the bottom up by ion implantation and annealing. The P-layer beneath the trench bottom can decrease the electric field at the bottom of the trench, thereby improving breakdown voltage (BV) performance. Simultaneously, the highly doped CS layer strengthens the hole-accumulation effect at the cathode. Moreover, the PNP doping layers on the left form a self-biased pMOS. In a short-circuit state, the self-biased pMOS turns on at a certain collector voltage, causing the potential of the CS-layer to be clamped by the hole channel. Consequently, the short-circuit current no longer increases with the collector voltage. The simulation results reveal significant improvements in comparison with the conventional CSTBT under the same on-state voltage (1.48 V for 100 A/cm2). Specifically, the turn-off time (toff) and turn-off loss (Eoff) are reduced by 38.4% and 41.8%, respectively. The short-circuit current is decreased by 50%, while the short-circuit time of the device is increased by 2.46 times.

1. Introduction

Currently, there is an urgent need for higher-speed, lower-cost, and higher-efficiency applications. The insulated-gate bipolar transistor (IGBT) stands out as a globally representative product of the third technological revolution in power electronics. As a composite full-controlled voltage-driven power semiconductor device, the IGBT exhibits excellent performance, with advantages such as a low cost, relatively large current, and easy switching, meaning that it forms the core of power converters [1,2,3,4,5].

Existing IGBTs can be roughly divided into planar-gate IGBTs and trench IGBTs, according to the characteristics of the gate electrode. Trench IGBTs have been shown to be competitive candidates for IGBT power applications, due to their superiority in terms of manufacturing, reliability, current handle capability, and cell density [6,7,8,9,10,11]. In planar-gate IGBTs, in the forward conduction state, the PN junction formed by the P-well and the N-drift region is in a slightly reverse-biased state. Consequently, a space-charge region with a certain width is formed, which occupies a certain space and increases the impedance in the current path [12,13,14,15]. Compared with the planar-gate IGBT, the trench IGBT can greatly reduce the turn-on voltage drop without increasing the turn-off loss (Eoff). Trench IGBTs also eliminate the JFET effect, increase the channel density, and enhance the carrier concentration near the surface to improve the turn-on voltage (Von) [16,17,18,19,20]. And an important development direction represented by CSTBT is IGBT surface structure design technology. Through the special surface structure design, the breaking voltage and anti-interference ability of the device can be improved, and the leakage current of the device can be reduced, so as to reduce the positive conduction voltage drop and reduce the loss during turn-off.

However, conventional shield-gate trench IGBTs (including CSTBTs) face two crucial challenges. Firstly, the electric field at the bottom of the trench is too concentrated, resulting in early breakdown at the bottom, and the breakdown voltage of the device is weakened. At the same time, the breakdown characteristics of the device are very sensitive to the trench depth and doping concentration near the bottom. Secondly, due to the existence of the Miller effect, the discharge of the trench capacitor is usually referred to as the part with the largest energy consumption in the entire discharge process. A tradeoff relationship exists between Von and Eoff, relying on trench size. Generally, a deeper trench can increase the channel density in the on-state of the device, achieving a smaller Von. However, the gate-collector capacitance (CGC) increases significantly as the trench depth increases. As a result, the dynamic characteristics of the device deteriorate, including the turn-off time (toff) and Eoff. Some approaches have been proposed to address CGC reduction for trench IGBTs, primarily focusing on the lower portion of the trench. These methods include implementing thick oxide to the trench bottom or, optionally, to the sidewalls [2,3,4,5]. Nonetheless, these methods suffer from poor process compatibility and the great impact of process variation on the device performance. At the same time, with the increase in power density in the IGBT, short-circuit characteristics are becoming more and more important and many new structures have been proposed [18,19]. If the short-circuit current density of the IGBT is too high, then the safe operating area (SOA) of the device becomes narrow in high-voltage and high-current applications. At present, the main solutions include reducing the effective channel density, which leads to an increase in conduction loss. The self-biased split-gate pMOS is thought to be an effective solution to this problem; however, currently similar structures suffer from poor process compatibility and the great impact of process variation on device performance.

To solve the problems of excessive turn-off loss and poor short-circuit tolerance in IGBT devices, this study introduces the design of a novel split-gate trench CSTBT, demonstrated by numerical simulations. This design features low Von, low Eoff, a low saturation current, and enhanced short-circuit capability. Notably, the device performance is unaffected by the deviation in the split-gate process.

2. Structure and Process Flow

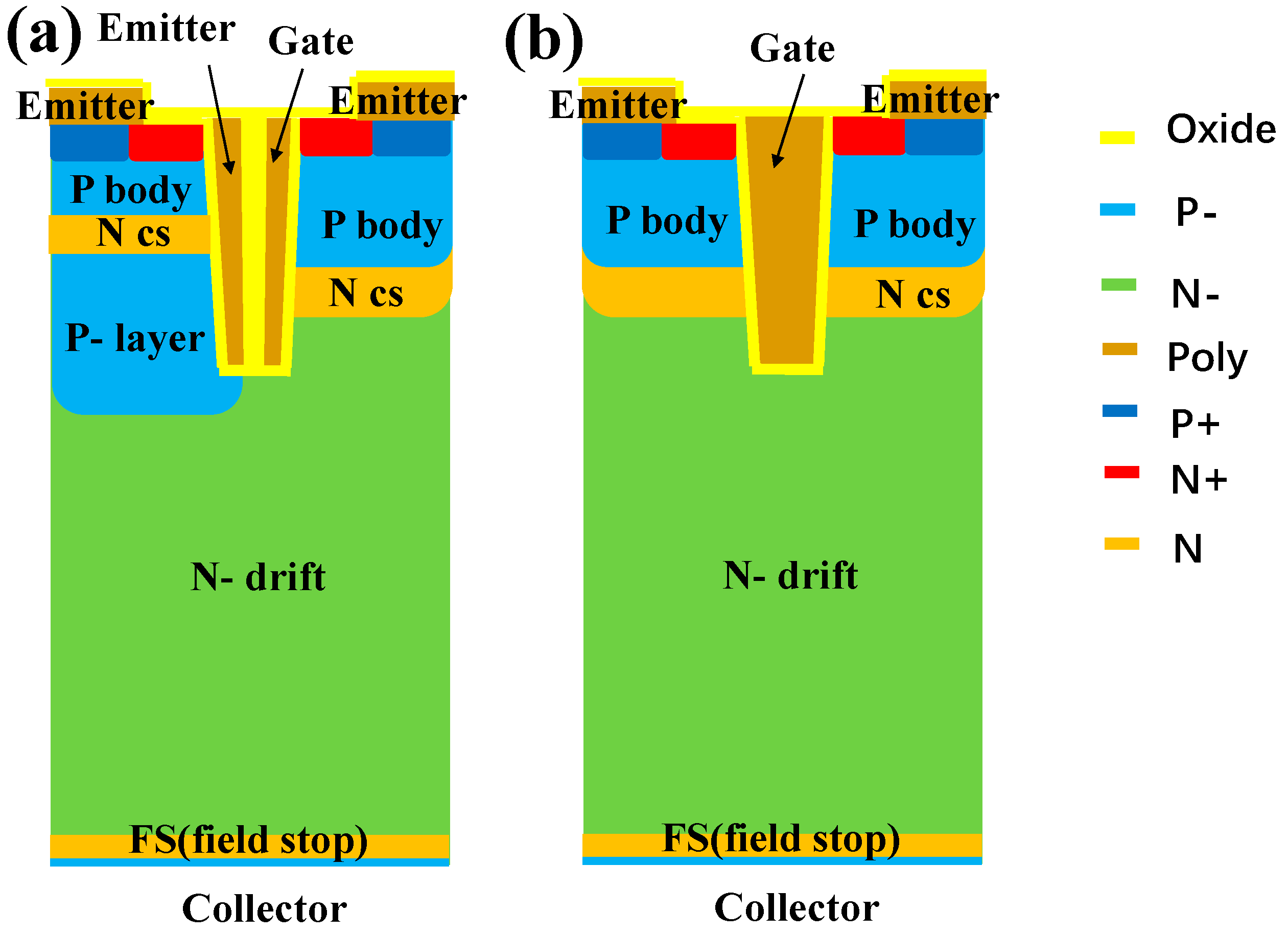

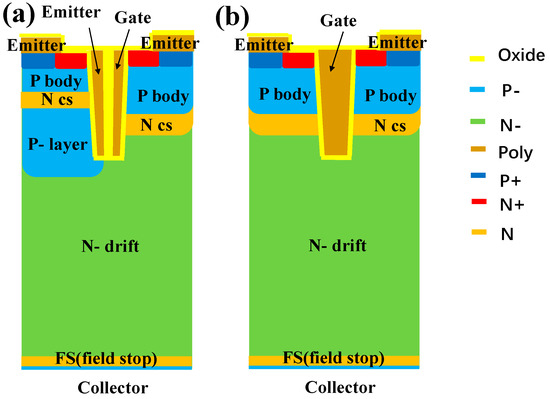

The schematic diagram of the proposed split-gate CSTBT is illustrated in Figure 1a, where the polysilicon electrode within the trench is divided into two segments: the split electrode on the left side is linked to the emitter cathode, while the split electrode on the right side functions as the conventional gate electrode. On the left side of the device cell, the P- layer, the carrier-stored (CS) layer, and the P-body are formed from the bottom upwards by ion implantation and annealing processes.

Figure 1.

(a) The proposed SGT-CSTBT and (b) conventional CSTBT.

The proposed SGT-CSTBT has the same doping profile as, and a similar structure to, the traditional structure, except for the split-gate structure. The right part includes the P-body and the identical doped CS layer. The drift zone thickness, doping concentration, and collector region doping remain identical, to ensure control variable. Major structural parameters are shown in Table 1.

Table 1.

Major structural parameters.

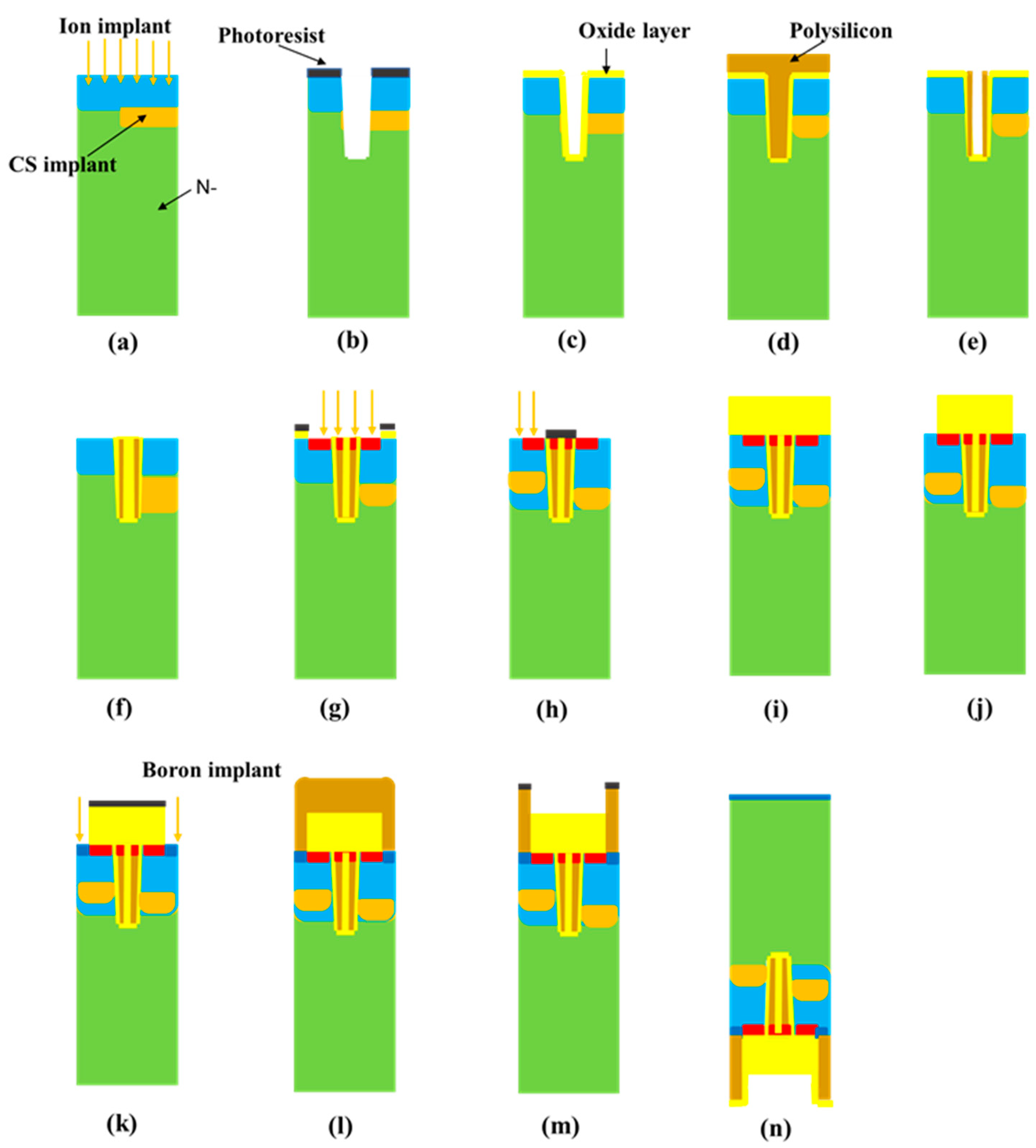

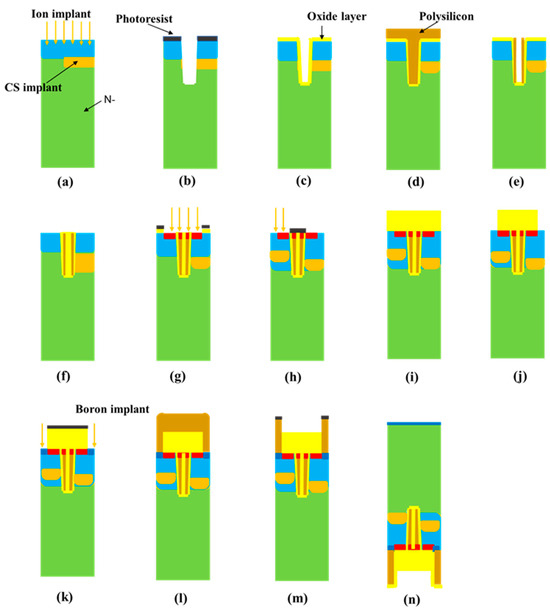

The general process flow of the device is shown in Figure 2 and mainly includes the following: (a) CS-layer ion implantation; (b) deep trench etching, (c) dielectric oxide layer growth; (d) polysilicon deposition; (e) polysilicon etching; (f) oxide layer etching; (g) N+ source area implantation and surface passivation layer deposition; (h) left higher doping CS-layer injection; (i) surface passivation; (j) surface oxide etching; (k) source area P+ implantation; (l) surface passivation; (m) source metallization; (n) back-collector ion implantation and metallization.

Figure 2.

Main process in the proposed split-gate device.

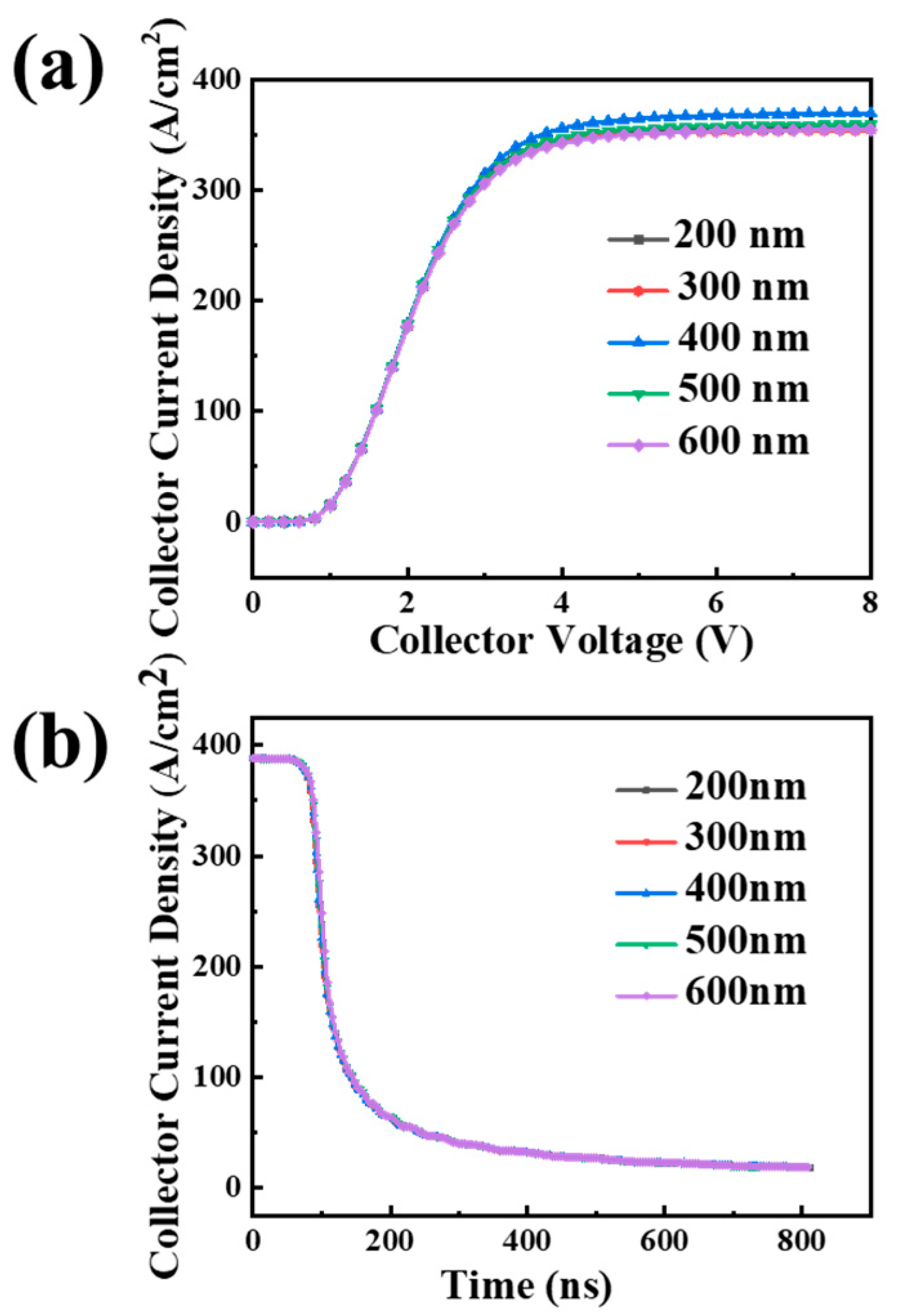

Taking into account the variation in the actual process, the deposition and etching rates of polysilicon is unstable, and the thickness of the polysilicon with the two separate electrodes on each side may be not a fixed value. The separation gate electrode devices with polysilicon thickness of 200 nm, 300 nm, 400 nm, 500 nm, and 600 nm are simulated, and device performances are compared.

The output characteristic curve and the turn-off characteristic curve are depicted in Figure 3. The output characteristic curves of the devices with different separation electrode thicknesses almost overlap, as do the turn-off characteristic curves, which means that the variation in the polysilicon thickness hardly affects the output characteristics (Von and Saturation current) and turn-off characteristics (Eoff) of the device.

Figure 3.

(a) Output characteristics of SGT-CSTBT with different separation polysilicon gate electrodes and (b) turn-off waves with different separation polysilicon gate electrodes.

These results show that the device has a high degree of insensitivity to the variation in the split-gate trench formation process.

3. Simulation Results and Discussion

The device model was established by the Sentaurus Technology Computer-Aided Design (TCAD) simulation, and the process conditions are based on the SMIC 0.18 µm process node.

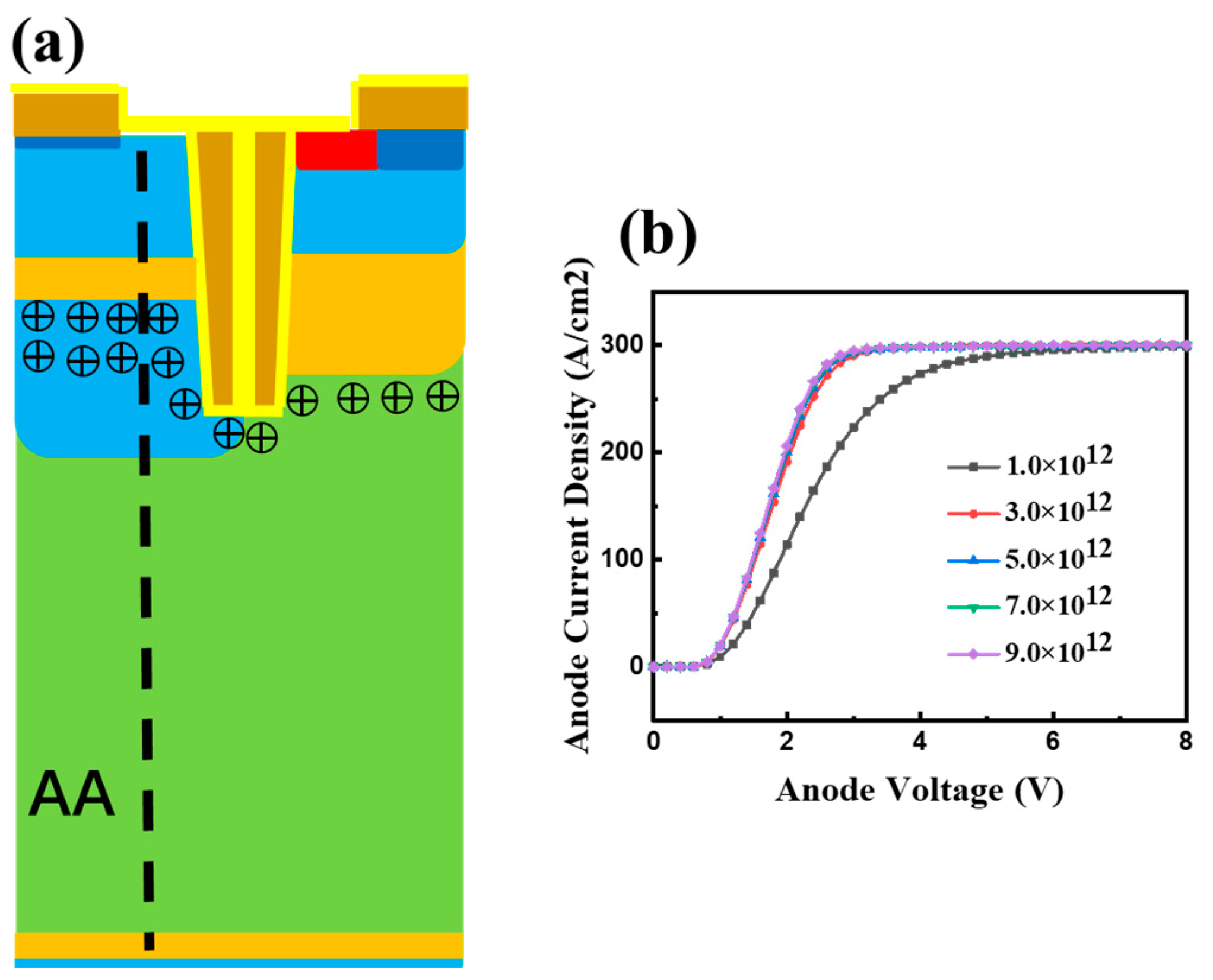

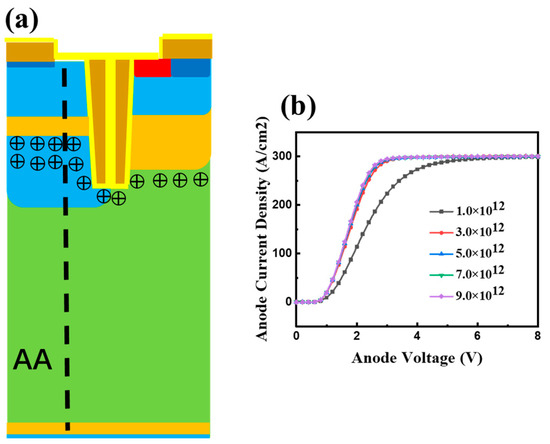

As shown in Figure 4a, the existence of the highly doped CS layer on the left increases the resistance of the holes traveling from the N-drift region to the emitter, simultaneously elevating the carrier concentration near the emitter side. This CS layer ensures that the device maintains a low Von drop and substantially reduces the toff.

Figure 4.

(a) Working mechanism of the device and (b) output characteristics of the device with different left-CS-layer doping.

Simulation results show that an increase in the CS doping concentration on the left leads to a reduction in Von. As shown in Figure 4b, the Von of the proposed device decreases with the increase in CS-layer injection dose on the left. This is attributed to the fact that a higher doping concentration of the CS layer on the left can enhance the hole-carrier storage effect. When the injection dose of the left CS layer reaches 9.0 × 1012/cm2, further increasing the injection dose has less effect on reducing Von in Figure 4b. The influence of the left CS layer on the increase in the hole accumulation effect reaches saturation. At the same time, the results show that, within the injection dose range from 3.0 × 1012/cm2 to 9.0 × 1012/cm2 for the left CS layer, the breakdown characteristics of the device remain constant. The Von of the proposed SGT-CSTBT and conventional CSTBT is compared in Figure 5c. It is clear the proposed SGT-CSTBT achieves a lower Von for a current density of 100 A/cm2, with both devices have the same doping profile on the right, and the left CS-layer injection dose is 3.0 × 1012/cm2.

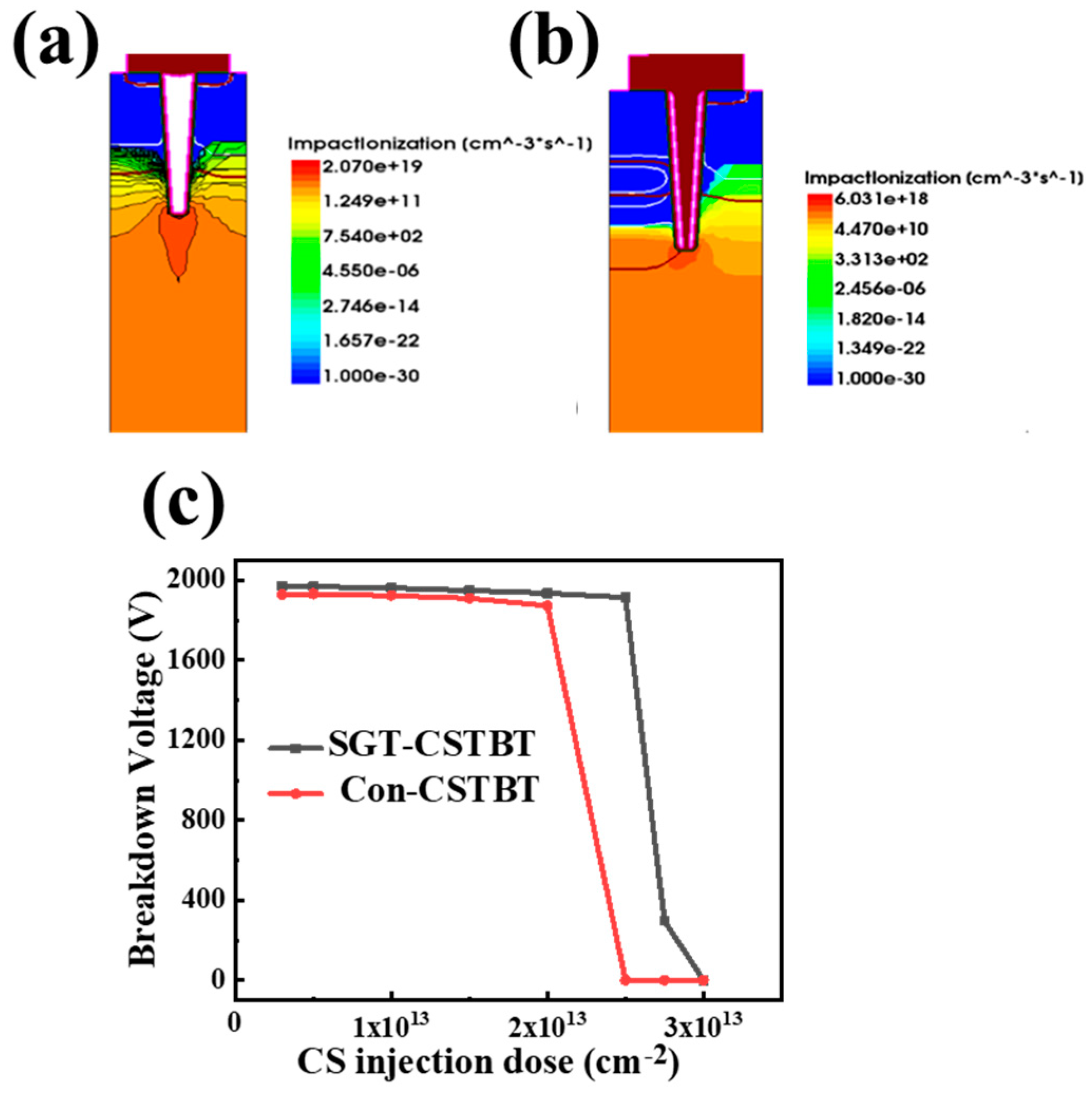

Figure 5.

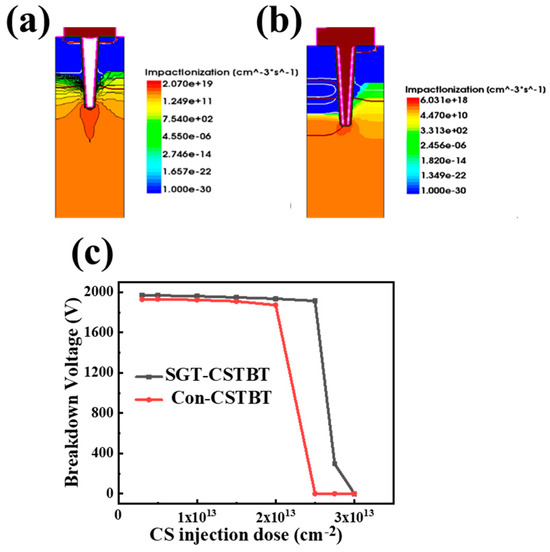

(a) Impact ionization rate of conventional CSTBT with 1900 V reverse bias. (b) Impact ionization rate of SGT-CSTBT with 1900 V reverse bias. (c) Relationship of the BV and Von with CS injection dose.

Compared to conventional CSTBT, a P-type buffer layer is introduced at the bottom of the trench to reduce the electric field, which helps to lower the impact ionization rate at the bottom of the trench by about 70%. This reduction in impact ionization allows for a more heavily doped CS layer, enabling a decrease in the on-state voltage without significantly affecting the breakdown capability.

By comparing the breakdown characteristics of conventional CSTBT and SGT-CSTBT, it can be seen that in Figure 5, with the same doping dose, the proposed SGT-CSTBT consistently demonstrates a higher breakdown voltage (BV). Specifically, as the doping dose increases, the BV of the SGT-CSTBT remains near 2000 V, while the BV of the conventional CSTBT drastically drops to 0 V when the injection dose exceeds 2.0 × 1013 cm−2. This highlights the improved breakdown performance of the SGT-CSTBT design compared to the conventional CSTBT in terms of maintaining a higher BV, even at higher injection doses.

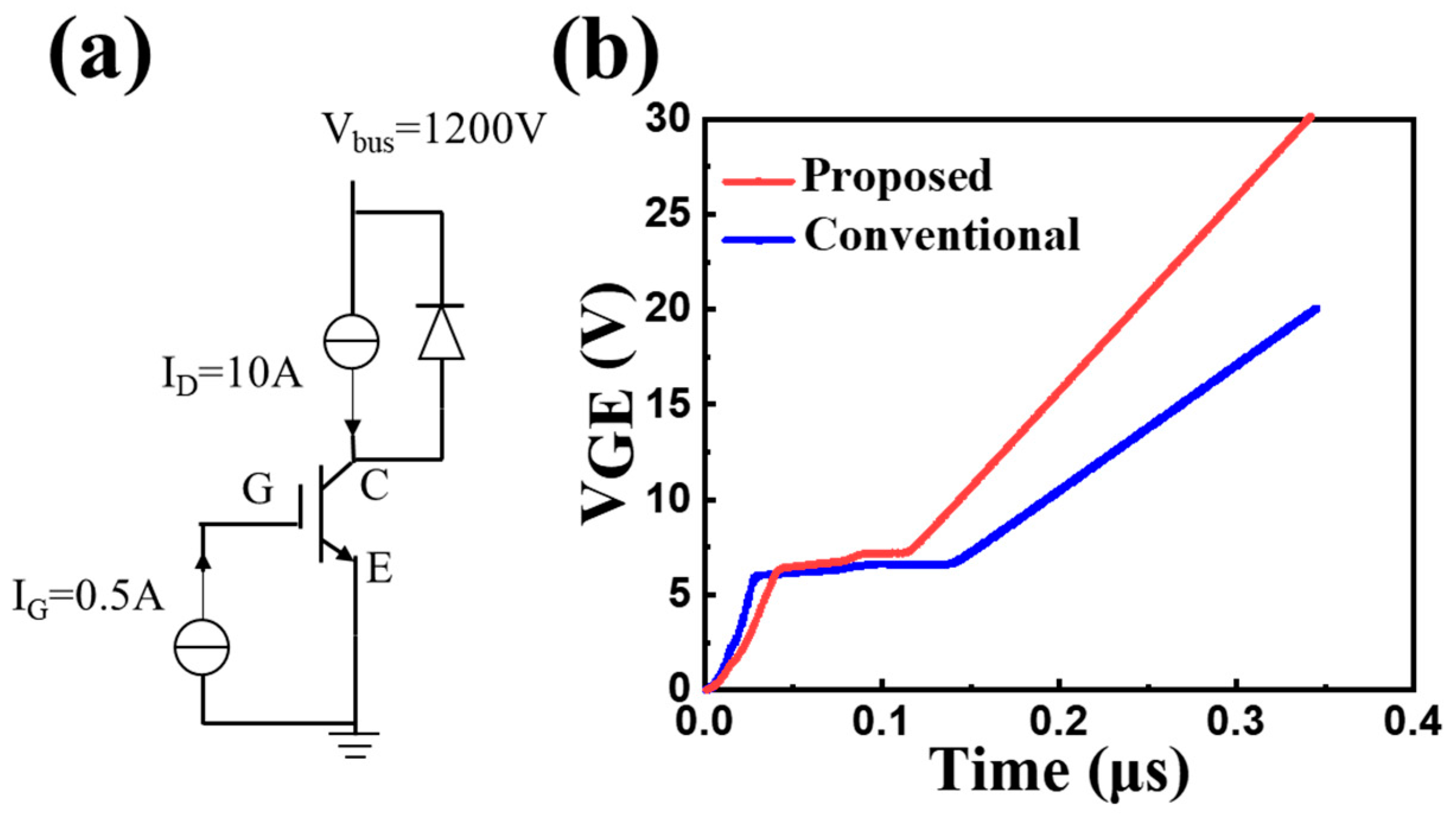

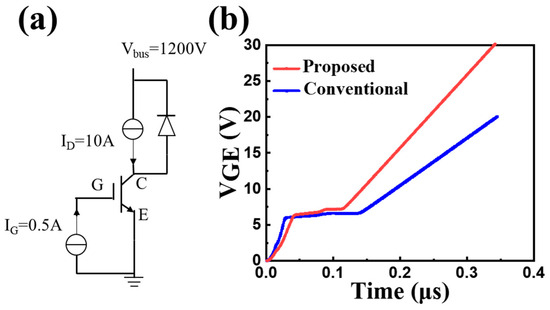

The Miller effect greatly increases the switching time and switching loss of the device. The value of CGC is usually used as the key basis for evaluating the Eoff of the device, and the size of CGC can be inferred by the length of the plateau period of VGE in the stage. Figure 6. shows a gate charge test circuit and gate charge curve for both CSTBTs. First, the gate voltage increases linearly, which charges up the capacitance CGE. Then, the gate voltage remains almost constant within a period of time, charging up the Miller capacitance.

Figure 6.

(a) Gate-charging test circuit and (b) gate-charging curve.

The charging time of the proposed SGT-CSTBT for the Miller capacitance decreases by 40.8%, compared with the conventional CSTBT. The Miller capacitance of the proposed SGT-CSTBT, equivalently, decreases from 8.523 to 4.81 nF/cm2. The cathode-connected gate in the trench can eliminate the impact of the anode on the trench gate to some extent. And the gate-collector capacitance (CGC) of the proposed device decreases as the coupling area between the trench and anode is greatly reduced. Therefore, a better dynamic performance is achieved.

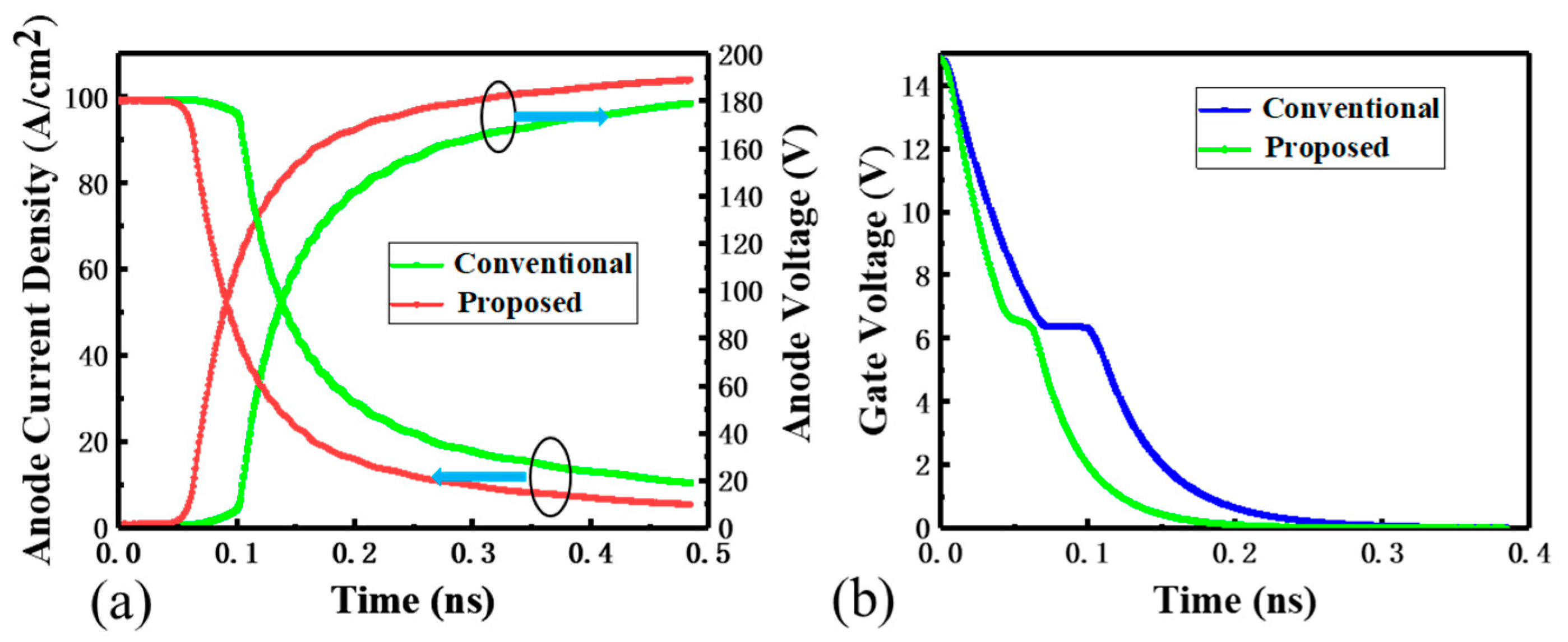

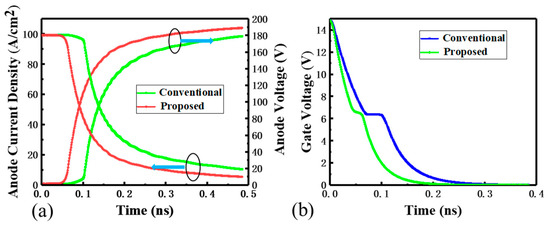

Figure 7a depicts the turn-off waves under the inductive load for both devices with the same Von. The turn-off time is defined as the time from the t1 (VG = 13.5 V) to t2 (Janode = 10 A/cm2). Obviously, the turn-off time of the SGT-CSTBT is shorter than that of the conventional CSTBT. The turn-off time of the SGT-CSTBT achieves a 38.4% reduction, which indicates an excellent Eoff performance in the SGT-CSTBT. Additionally, the proposed SGT-CSTBT has a smaller tail current at the current falling stage of the turning-off. This reduction is attributed to the lighter-doped P-collector (by adjusting the doping of the P-collector to make the Von consistent). As mentioned earlier, in the turn-off state, the Miller effect is effectively suppressed, as depicted in Figure 7b. And the turn-on loss and turn-on time are also optimized, mainly due to the reduction in Miller capacitance.

Figure 7.

(a). Turn-off waves under inductive load in the conventional CSTBT and SGT-CSTBT with the same Von (Vcc = 1200 V Lc = 1.5 mH Rg = 10 ῼ Ci = 50 pF). (b) Gate voltage waves during turn-off.

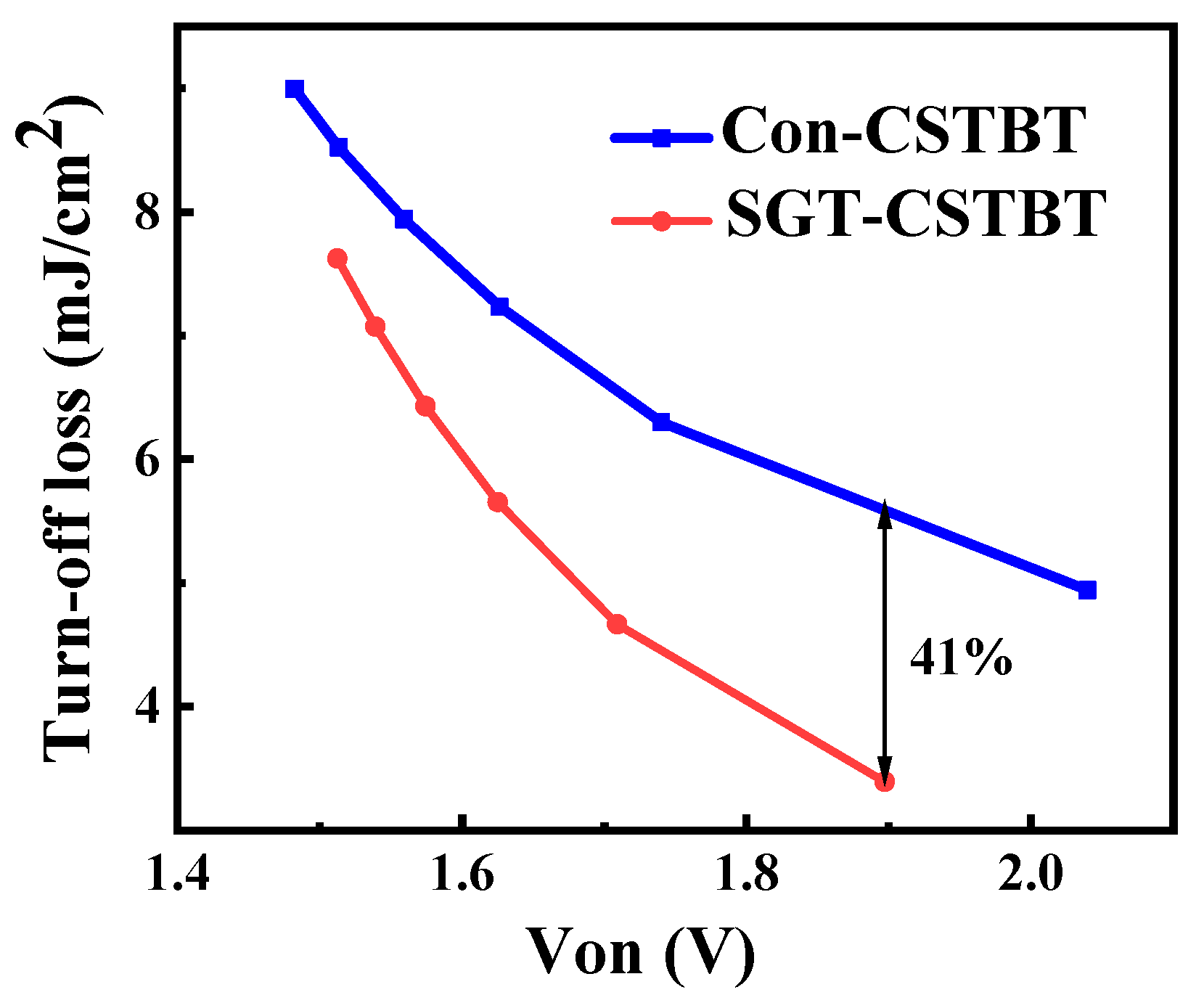

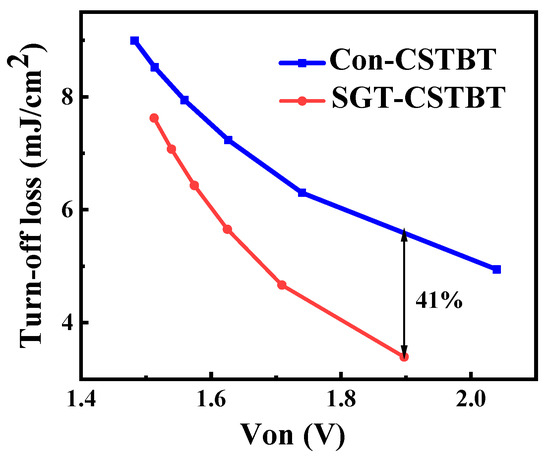

Figure 8 illustrates the relationship between the Eoff and Von of the two different structures after changing the peak P-collector doping concentration. Under Eoff = 5 mJ/cm2, the Von of the SGT-CSTBT is 1.68 V, which is 17.5% lower than the 2.04 V of the Con-CSTBT. As Von changes from 1.5 V to 2.0 V, the proposed device can effectively reduce the Eoff as expected. Under Von = 1.9 V, the Eoff of the SGT-CSTBT is 3.3 mJ/cm2, which is nearly 41.8% lower than the 5.67 mJ/cm2 of the Con-CSTBT. It is clear the proposed SGT-CSTBT can significantly improve the trade-off relationship, as expected.

Figure 8.

Trade-off relationships between Von and Eoff (obtained by varying the doping concentration of the P emitter at the anode side).

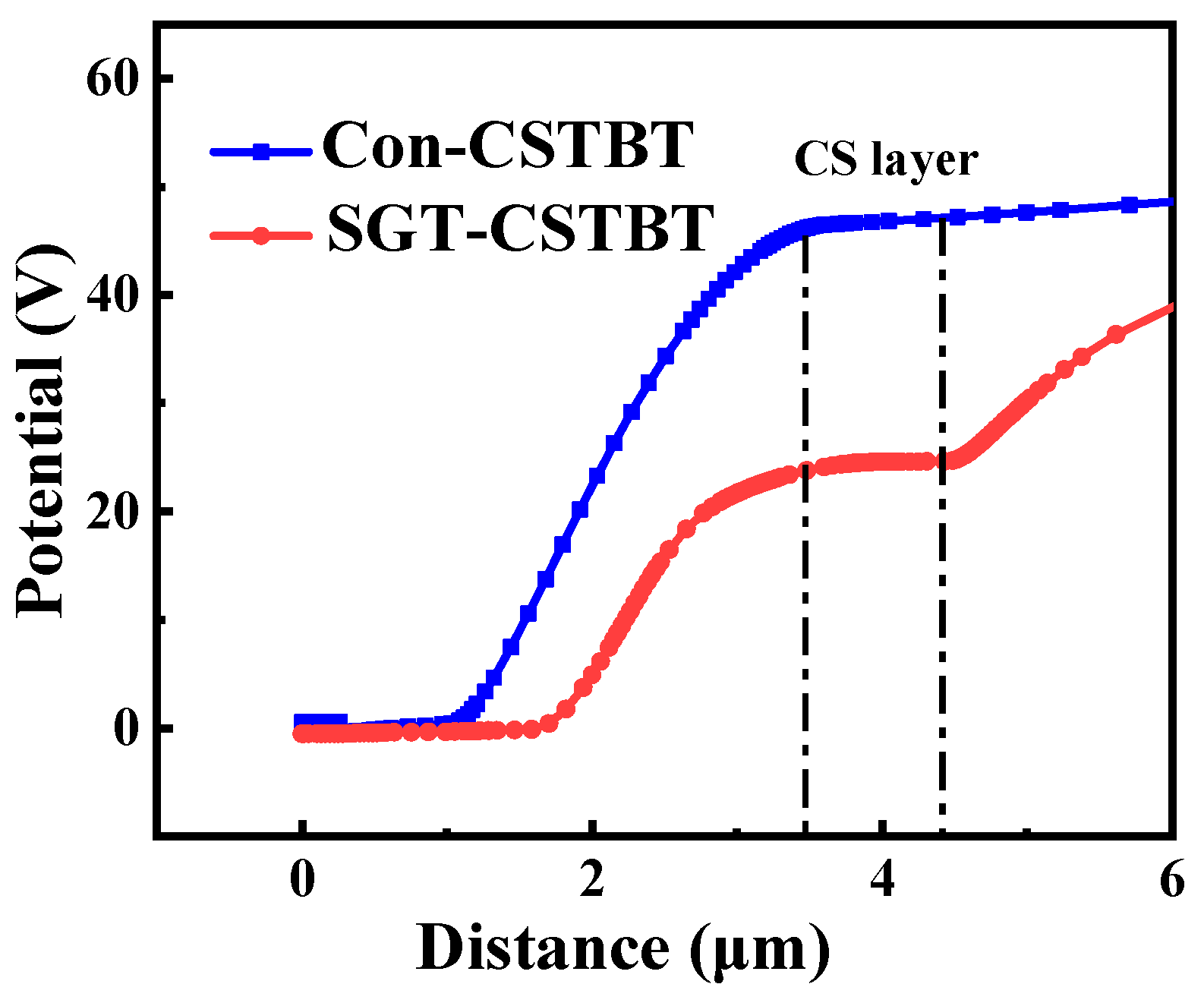

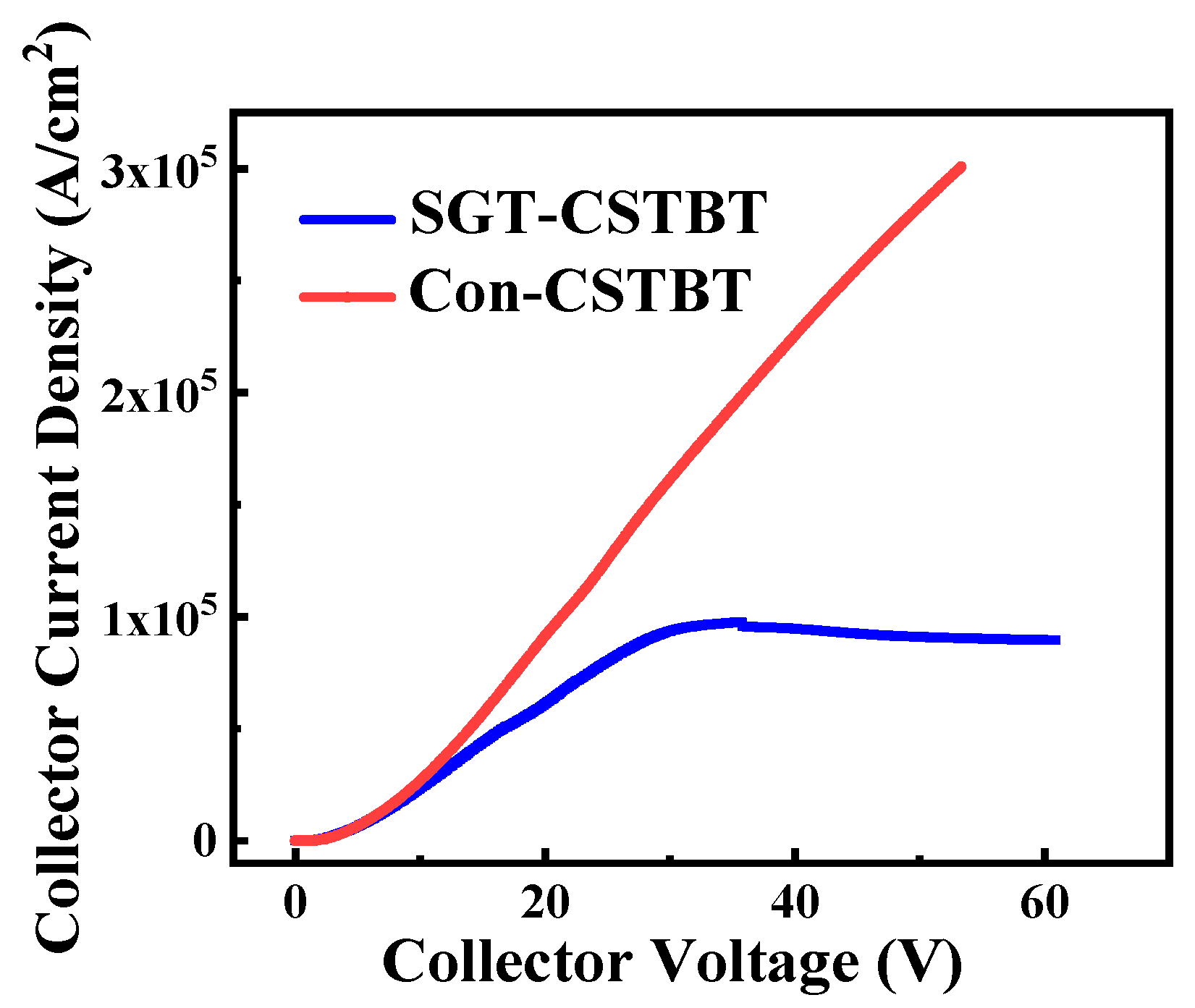

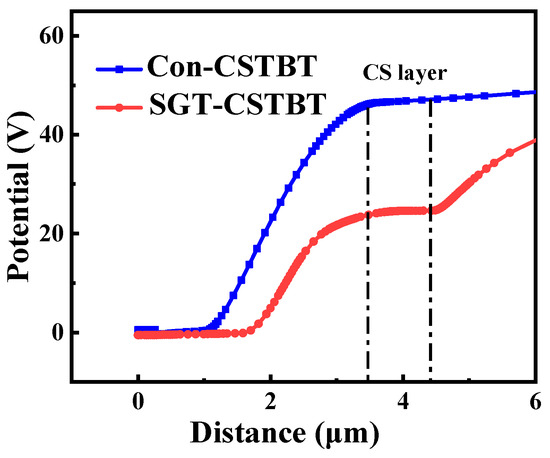

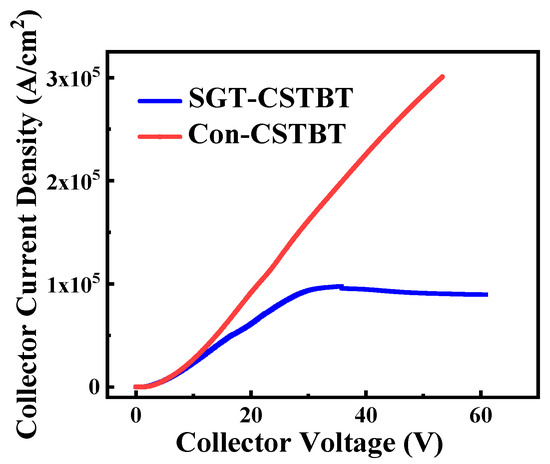

The potential distribution of the proposed SGT-CSTBT and conventional CSTBT with 100 V anode voltage (VG = 15 V) are compared in Figure 9. It is clear that VCS (the potential of the N-layer) of the proposed SGT-CSTBT is much lower than that of the conventional device. And when the voltage of the anode exceeds 35 V, the short-circuit current of the proposed device no longer increases and even appears to decrease, as shown in Figure 10. The reason for the enhanced short-circuit roughness of the device is that, with the increase in collector voltage, the potential of the left CS layer increases. When the potential of the second P-type base reaches the threshold voltage of the PMOS, the PMOS is turned on, and the excess holes are discharged from the PMOS channel, so the potential of the second P-type base no longer increases.

Figure 9.

The vertical potential distribution (VG = 15 V, VC = 100 V).

Figure 10.

Short-circuit current at different collector voltages.

The short-circuit current simulation results show that the proposed SGT-CSTBT structure is obviously optimized under different short-circuit voltages, as shown in Figure 10. The short-circuit current is reduced by 50% at a 40 V short-circuit voltage.

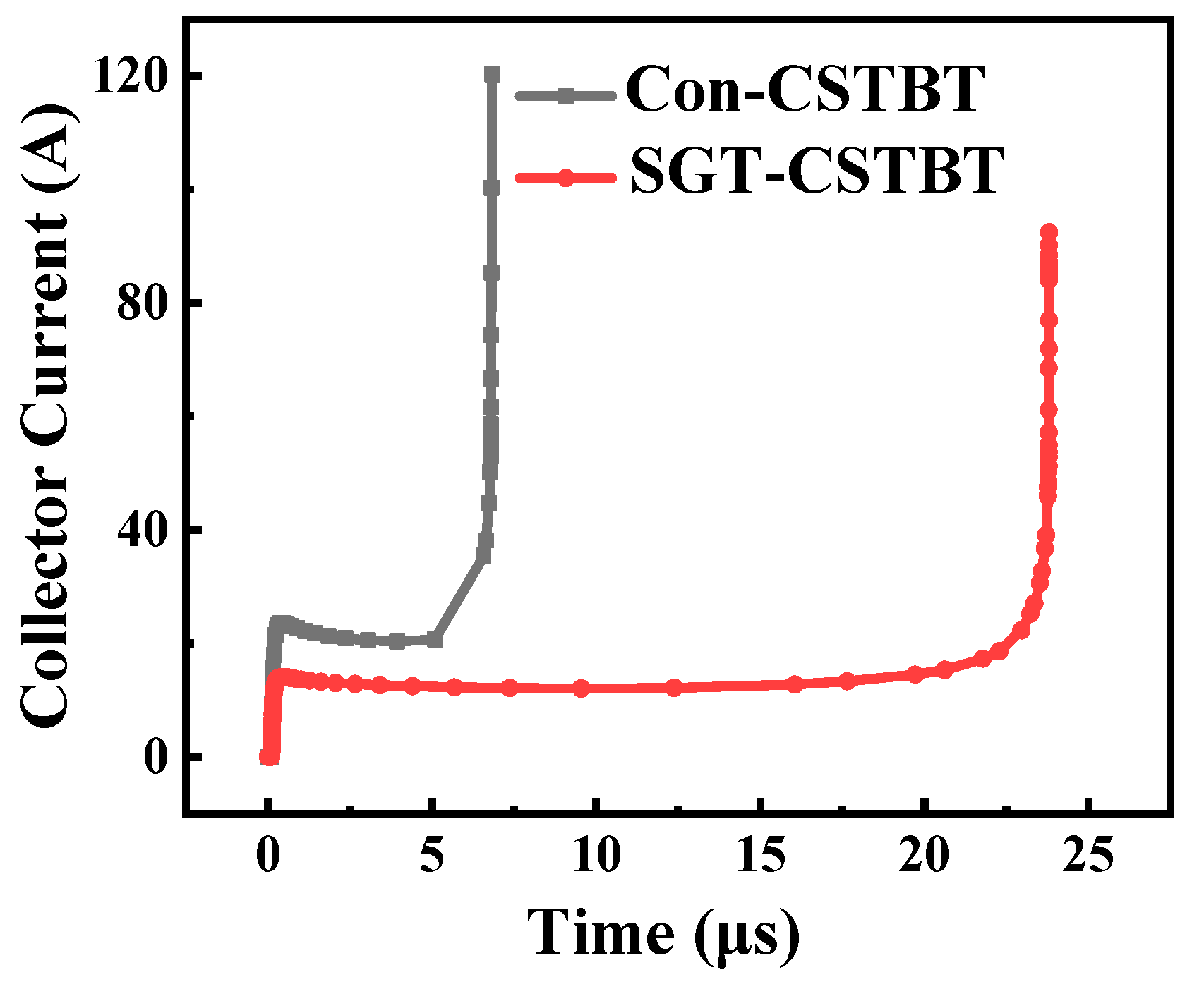

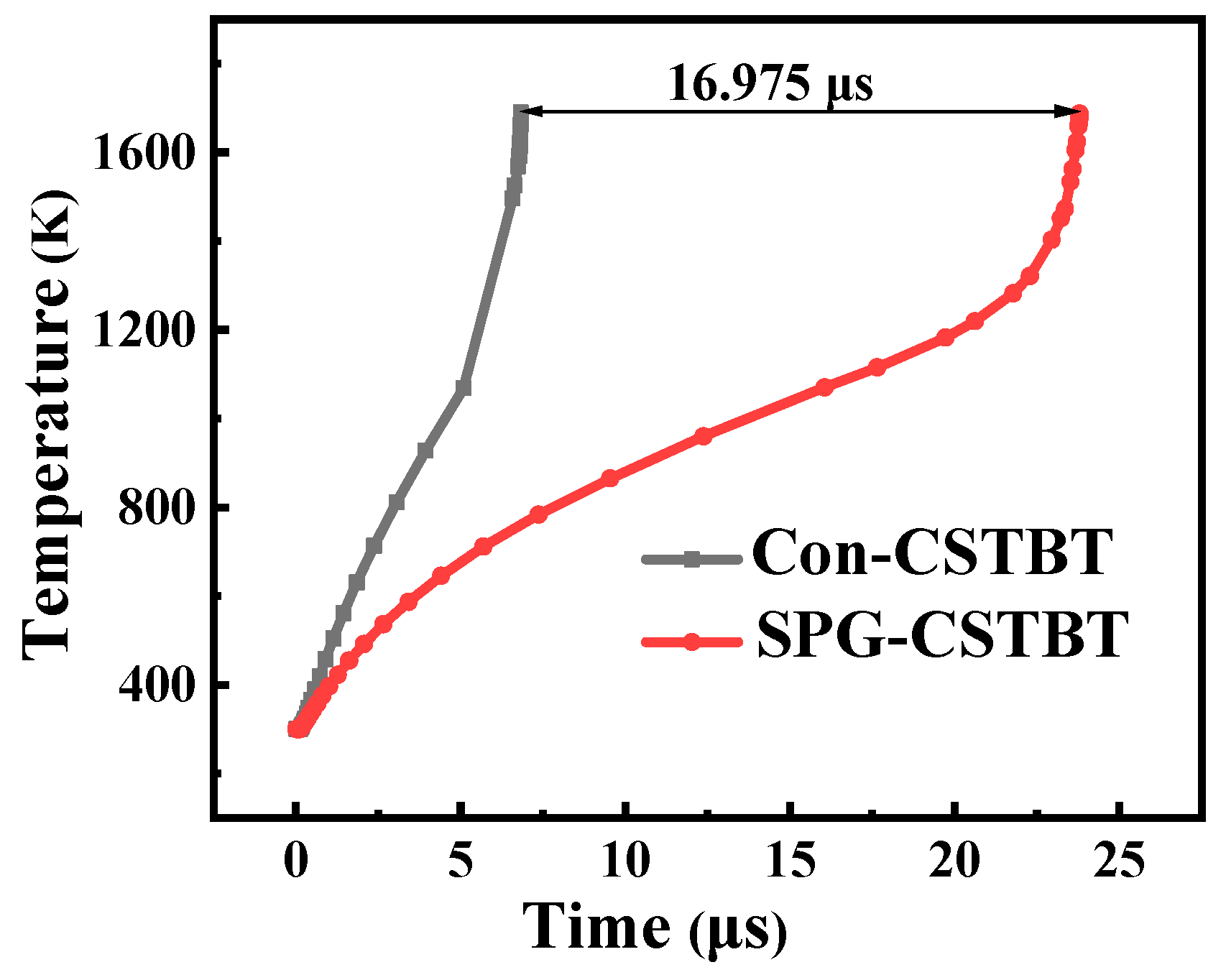

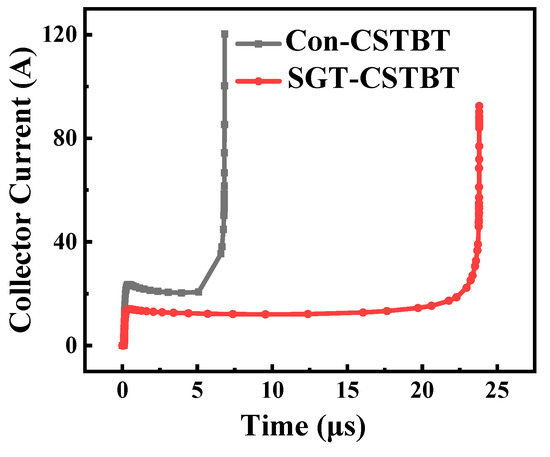

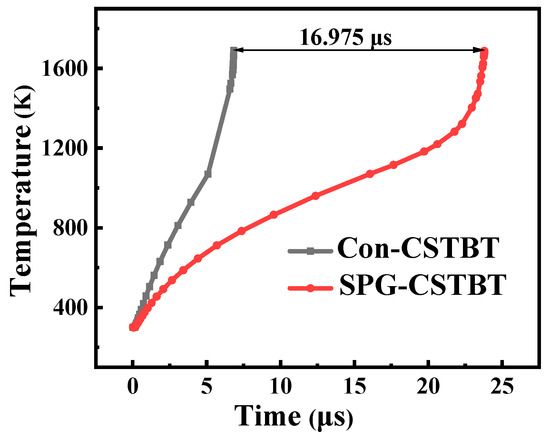

Figure 11 and Figure 12 illustrate short-circuit waves. They indicate that the SGT-CSTBT withstands a significantly longer short-circuit duration time (the device failure time is defined when the lattice temperature reaches 1687 K) than that of the conventional CSTBT before failure. Owing to the smaller saturation current density, the short-circuit safe operating area (SCSOA) of the proposed SGT-CSTBT structure is about 2.46 times larger than that of the conventional CSTBT structure.

Figure 11.

Simulated short-circuit failures in the conventional CSTBT and SGT-CSTBT.

Figure 12.

Maximum device temperature curves in the short-circuit situation of CSTBT and SGT-CSTBT. The self-heating effect is considered by the LAT.TEMP model, with the initial device temperature of 300 K.

4. Conclusions

A novel split-gate CSTBT is proposed and investigated via numerical simulations. Using a combination of the hole-channel and carrier-stored technologies, the SGT-CSTBT presented has excellent performance. toff is reduced without sacrificing the conduction loss and Von. The P channel is closed in on state, servicing as a hole-stop layer to enhance the accumulation of holes near the cathode. During the turn-off process, this P channel provides an additional low resistance path for the hole current and reduces the toff. In the blocking state, the P layer beneath the trench can significantly alleviate the trade-off of the BV- and CS-layer concentrations. And the short-circuit duration time increases by 246%.

Author Contributions

Writing—Original Draft, Z.Q., H.X. and Y.Y.; validation, T.F.; software, W.C.; supervision, Q.S. and D.W.Z. All authors have read and agreed to the published version of the manuscript.

Funding

This work was supported by the National Natural Science Foundation of China (623B2028).

Data Availability Statement

Data are included within the article.

Conflicts of Interest

The authors declare no conflicts of interest.

References

- Takahashi, H.; Haruguchi, H.; Hagino, H.; Yamada, T. Carrier stored trench-gate bipolar transistor (CSTBT)-a novel power device for high voltage application. In Proceedings of the 8th International Symposium on Power Semiconductor Devices and Ics, ISPSD’96, Proceedings, Maui, HI, USA, 23 May 1996; pp. 349–352. [Google Scholar]

- Takahashi, T.; Tomomatsu, Y.; Sato, K. CSTBT (III) as the next generation IGBT. In Proceedings of the 20th International Symposium on Power Semiconductor Devices and IC’s, Orlando, FL, USA, 18–22 May 2008; pp. 72–75. [Google Scholar]

- Honda, S.; Haraguchi, Y.; Narazaki, A.; Terashima, T.; Terasaki, Y. Next generation 600V CSTBT™ with an advanced fine pattern and a thin wafer process technologies. In Proceedings of the 24th International Symposium on Power Semiconductor Devices and ICs, Bruges, Belgium, 3–7 June 2012; pp. 149–152. [Google Scholar]

- Zhang, J.; Xiao, X.; Zhu, R.; Zhao, Q.; Zhang, B. Low loss and low EMI noise CSTBT with split gate and recessed emitter trench. IEEE J. Electron Devices Soc. 2021, 9, 704–712. [Google Scholar] [CrossRef]

- Nakamura, K.; Sadamatsu, K.; Oya, D.; Shigeoka, H.; Hatade, K. Wide Cell Pitch LPT (II)-CSTBT™(III) technology rating up to 6500 V for low loss. In Proceedings of the 22nd International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hiroshima, Japan, 6–10 June 2010; pp. 387–390. [Google Scholar]

- Xu, X.; Chen, W.; Liu, C.; Wang, Y.; Chen, N.; Wang, F.; Shi, Q.; Zhang, K.; Zhou, Q.; Li, Z.; et al. A Novel CSTBT with Hole Barrier for High dV/dt Controllability and Low EMI Noise. In Proceedings of the 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019; pp. 331–334. [Google Scholar] [CrossRef]

- Li, P.; Kong, M.; Chen, X. A novel diode-clamped CSTBT with ultra-low on-state voltage and saturation current. In Proceedings of the 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, Czech Republic, 12–16 June 2016; pp. 307–310. [Google Scholar]

- Kamibaba, R.; Konishi, K.; Fukada, Y.; Narazaki, A.; Tarutani, M. Next generation 650V CSTBT TM with improved SOA fabricated by an advanced thin wafer technology. In Proceedings of the 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hong Kong, China, 10–14 May 2015; pp. 29–32. [Google Scholar]

- Iwamuro, N.; Laska, T. IGBT history, state-of-the-art, and future prospects. IEEE Trans. Electron Devices 2017, 64, 741–752. [Google Scholar] [CrossRef]

- Zhang, J.; Wang, K.; Luo, J.; Zhao, Y.; Li, Z.; Ren, M.; Gao, W.; Zhang, B. Numerical analysis of impact of shield gate on trench IGBT and CSTBT. In Proceedings of the 2019 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Xi’an, China, 12–14 June 2019; pp. 1–3. [Google Scholar]

- Xu, H.; Feng, T.; Guo, J.; Cui, W.; Yang, Y.; Sun, Q.Q.; Zhang, D.W. A Low Conduction Loss IGBT with Hole Path and Temperature Sensing. IEEE Trans. Electron Devices 2023, 70, 5236–5241. [Google Scholar] [CrossRef]

- Xu, H.; Yang, Y.; Tan, J.; Zhu, H.; Sun, Q.-Q.; Zhang, D.W. Carrier Stored Trench-Gate Bipolar Transistor with Stepped Split Trench-Gate Structure. IEEE Trans. Electron Devices 2022, 69, 5450–5455. [Google Scholar] [CrossRef]

- Laska, T.; Munzer, M.; Pfirsch, F.; Scaeffer, C.; Schmidt, T. The field stop IGBT (FS IGBT). A new power device concept with a great improvement potential. In Proceedings of the 12th International Symposium on Power Semiconductor Devices & ICs, Proceedings (Cat. No. 00CH37094), Toulouse, France, 22–25 May 2000; pp. 355–358. [Google Scholar] [CrossRef]

- Kitagawa, M.; Omura, I.; Hasegawa, S.; Inoue, T.; Nakagawa, A. A 4500 V injection enhanced insulated gate bipolar transistor (IEGT)operating in a mode similar to a thyristor. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 5–8 December 1993; pp. 679–682. [Google Scholar] [CrossRef]

- Antoniou, M.; Lophitis, N.; Bauer, F.; Nistor, I.; Bellini, M.; Rahimo, M.; Amaratunga, G.; Udrea, F. Novel approach toward plasma enhancement in trench-insulated gate bipolar transistors. IEEE Electron. Device Lett. 2015, 36, 823–825. [Google Scholar] [CrossRef]

- Williams, R.K.; Darwish, M.N.; Blanchard, R.A.; Siemieniec, R.; Rutter, P.; Kawaguchi, Y. The Trench Power MOSFET: Part I—History, Technology, and Prospects. IEEE Trans. Electron Devices 2017, 64, 674–691. [Google Scholar] [CrossRef]

- Huang, J.; Huang, H.; Lyu, X.; Chen, X.B. Simulation Study of a Low Switching Loss FD-IGBT with High dI/dt and dV/dt Controllability. IEEE Trans. Electron Devices 2018, 65, 5545–5548. [Google Scholar] [CrossRef]

- Huang, J.; Huang, H.; Chen, X.B. Simulation Study of a Low ON-State Voltage Superjunction IGBT with Self-Biased PMOS. IEEE Trans. Electron Devices 2019, 66, 3242–3246. [Google Scholar] [CrossRef]

- Jiang, M.; Gao, L. Simulation Study of a Thyristor Conduction-Insulated Gate Bipolar Transistor (TC-IGBT) with a p-n-p Base and an n-p-n Collector for Reducing Turn-Off Loss. IEEE Trans. Electron Devices 2020, 67, 2854–2858. [Google Scholar] [CrossRef]

- Saito, W.; Nishizawa, S. Alternated Trench-Gate IGBT for Low Loss and Suppressing Negative Gate Capacitance. IEEE Trans. Electron Devices 2020, 67, 3285–3290. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).