A Novel IGBT with SIPOS Pillars Achieving Ultralow Power Loss in TCAD Simulation Study

Abstract

1. Introduction

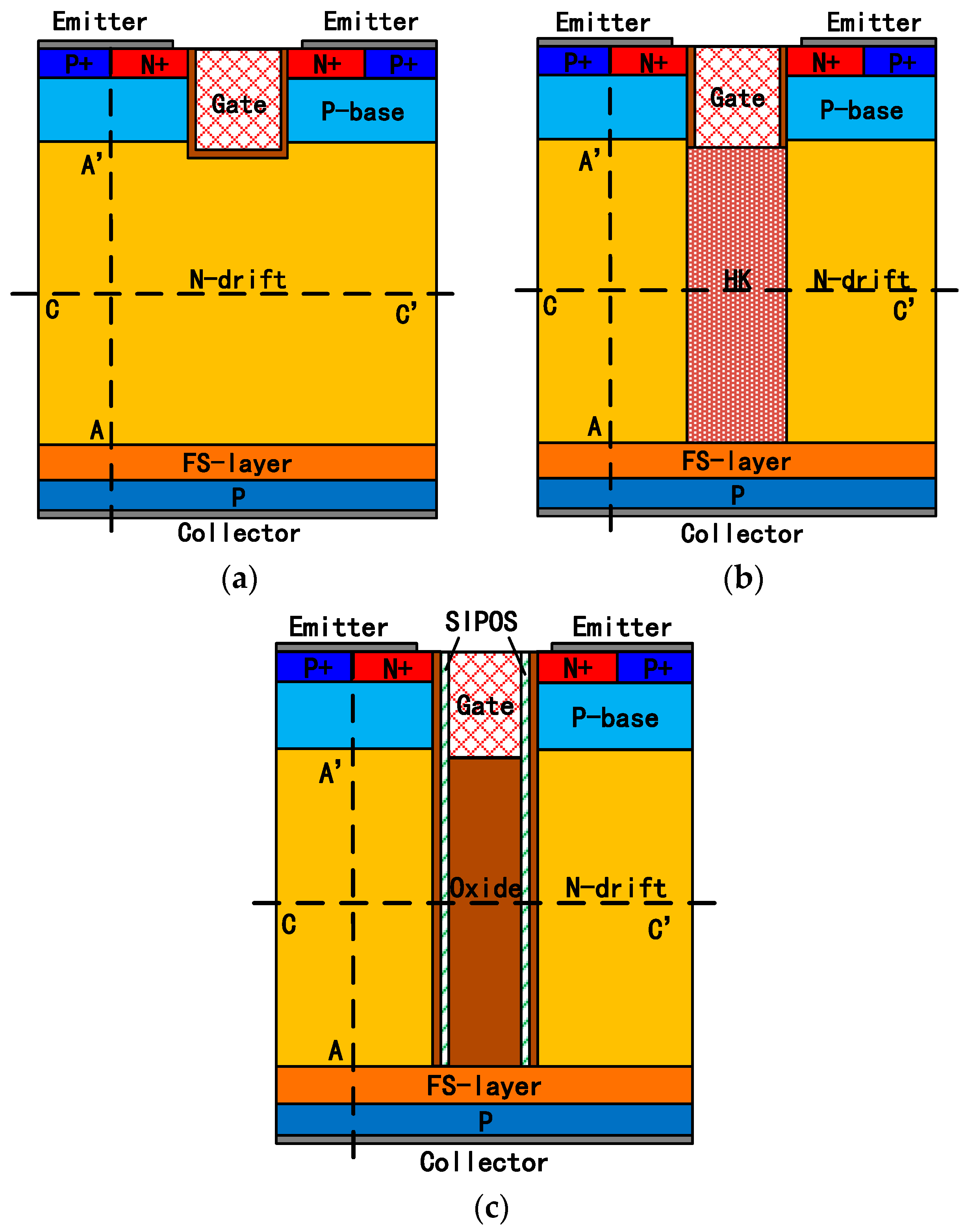

2. Device Structure and Mechanism

3. Results and Discussion

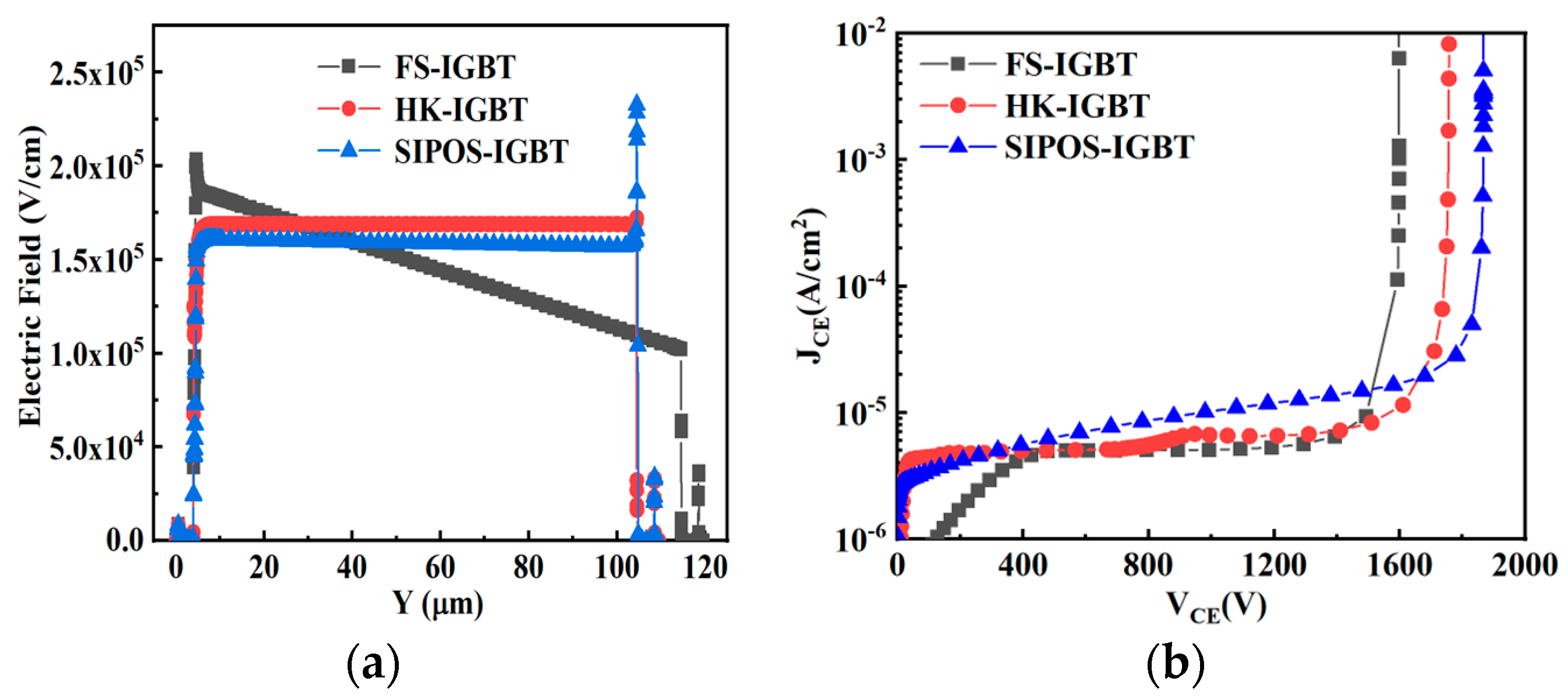

3.1. Breakdown Characteristics

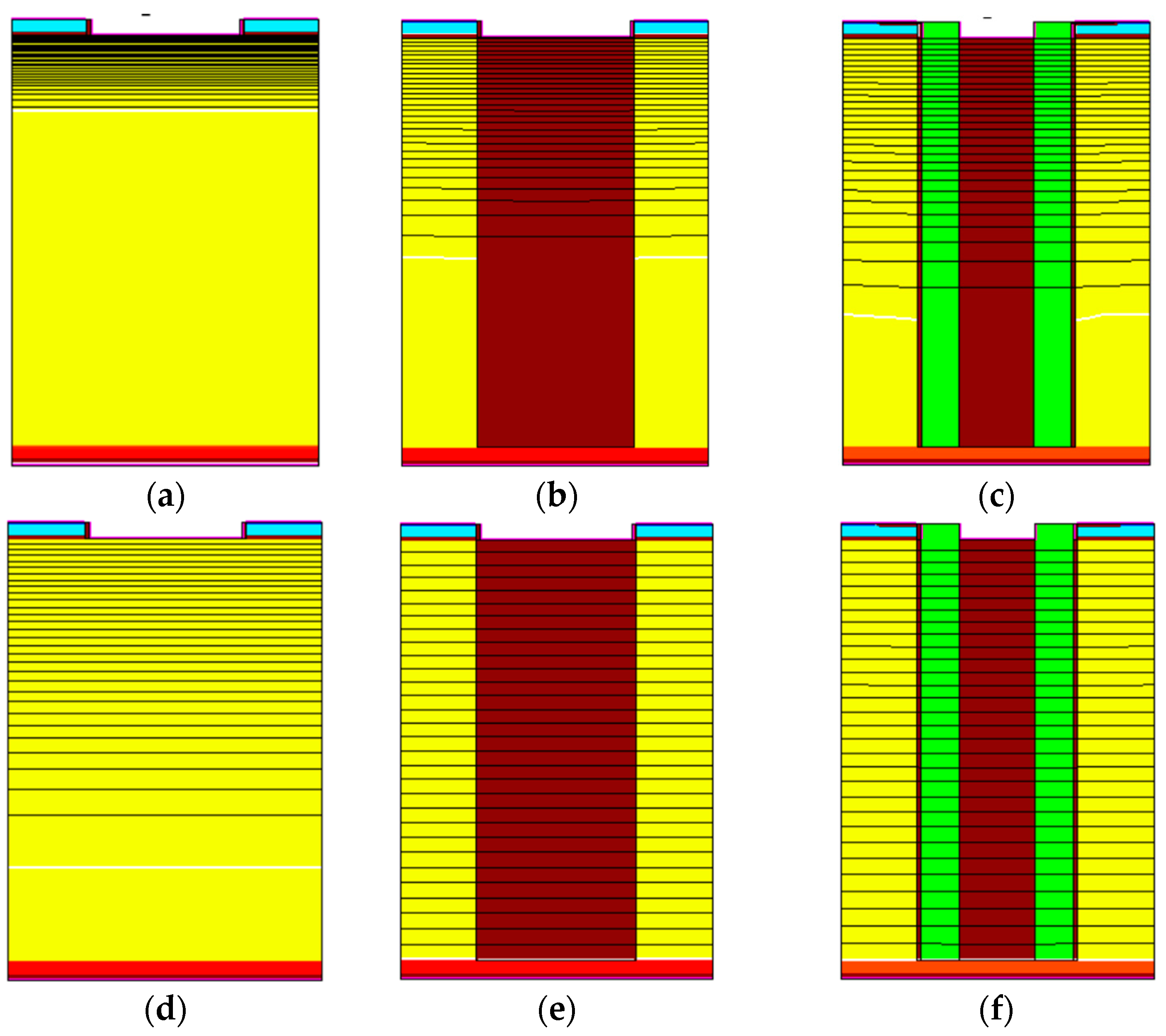

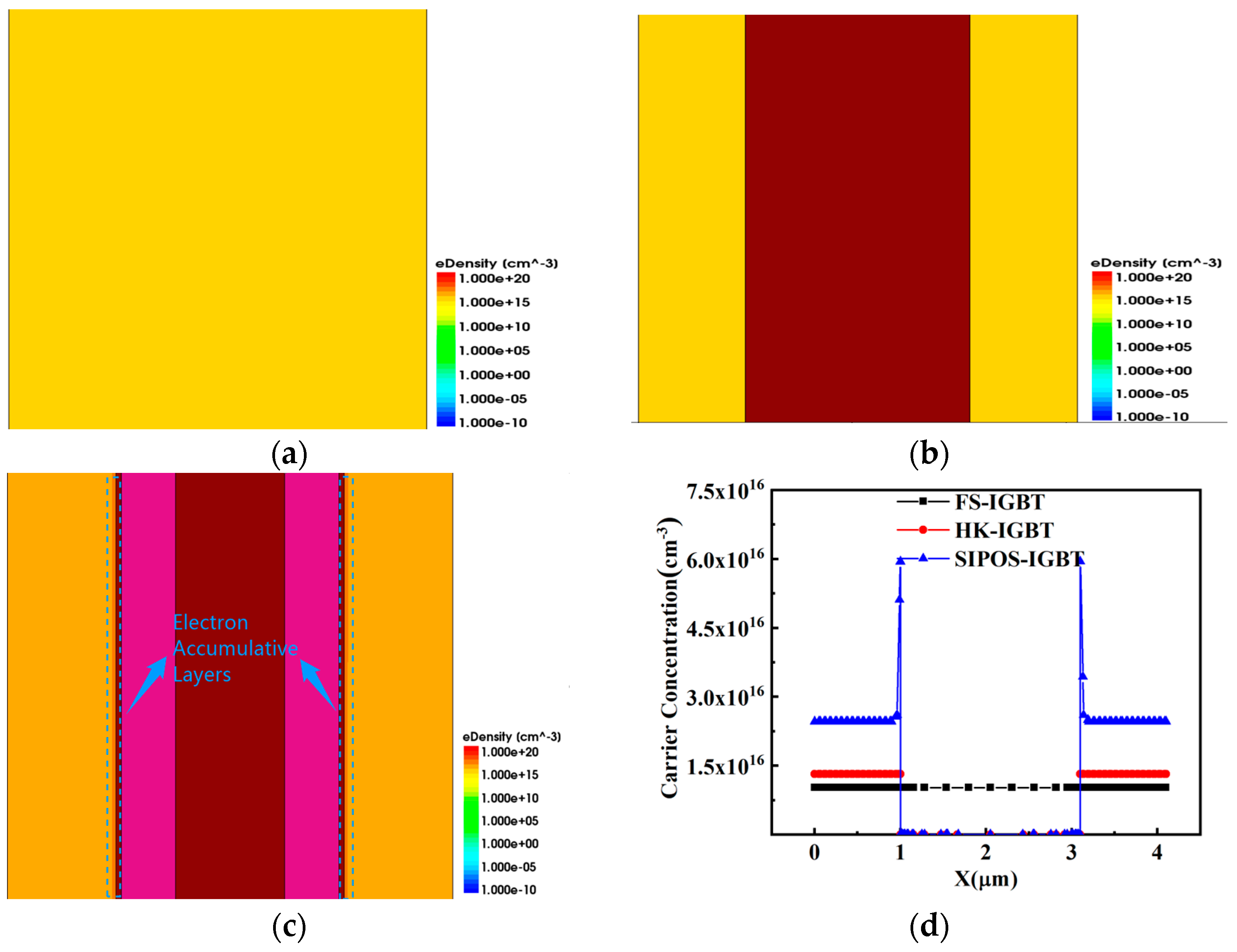

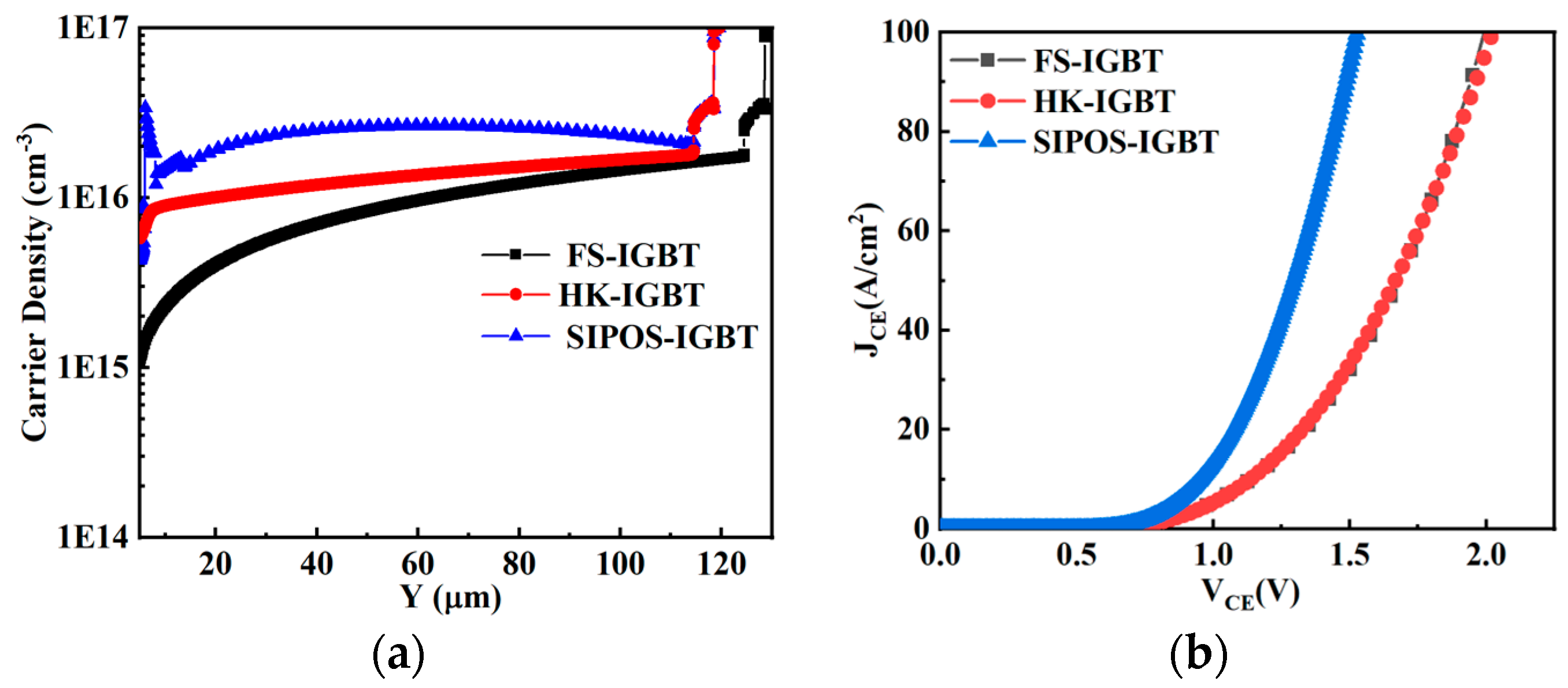

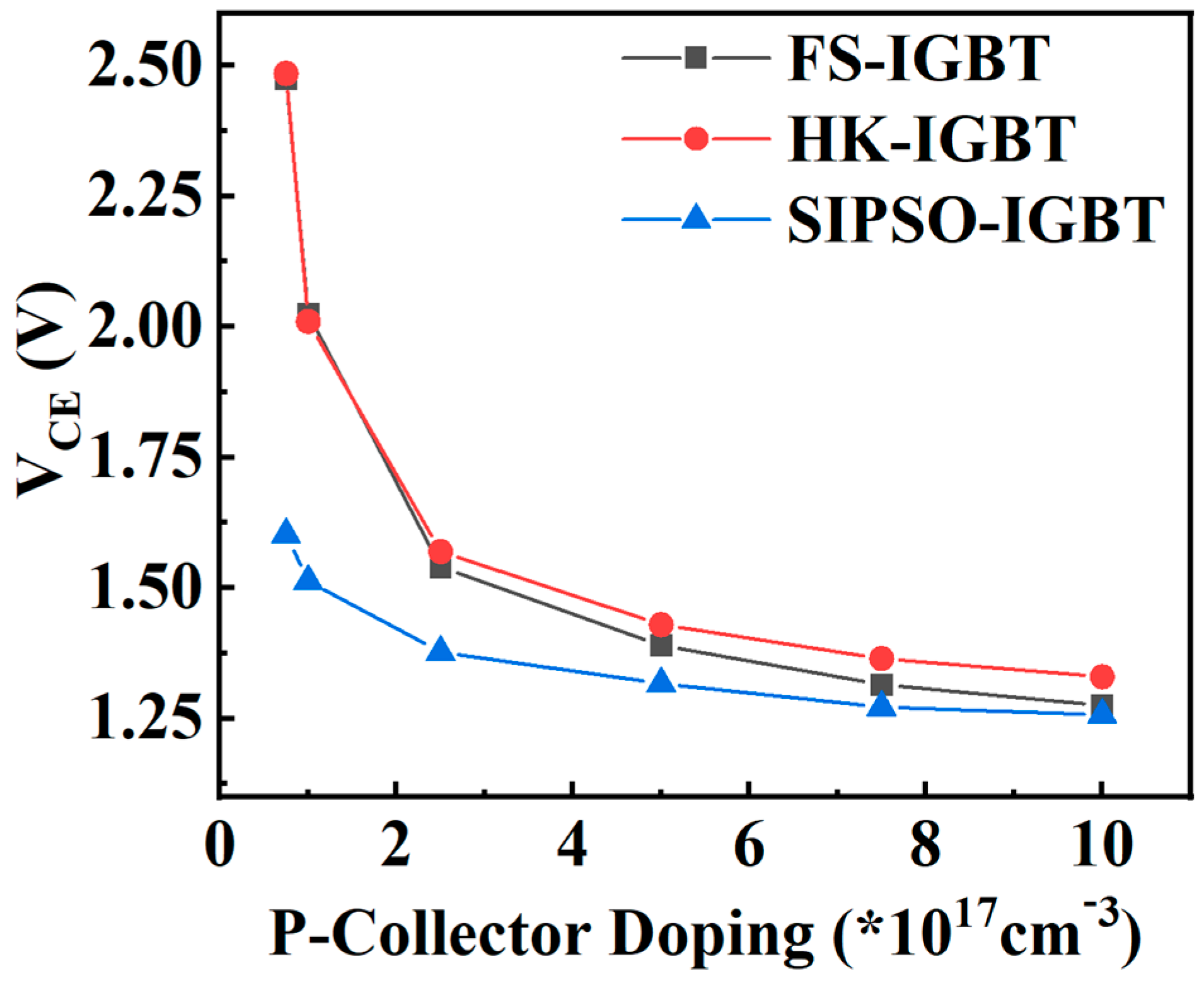

3.2. On-State Characteristics

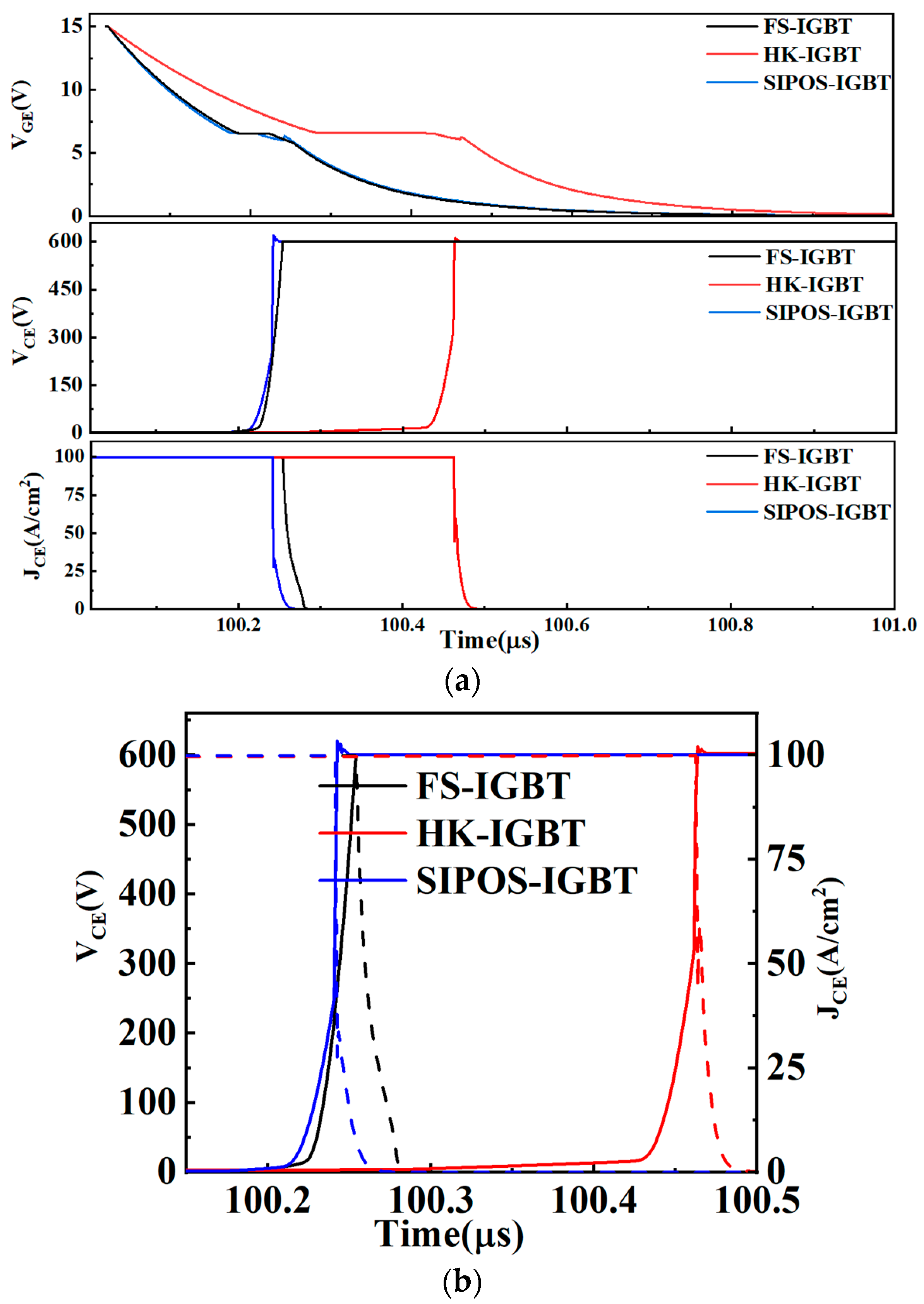

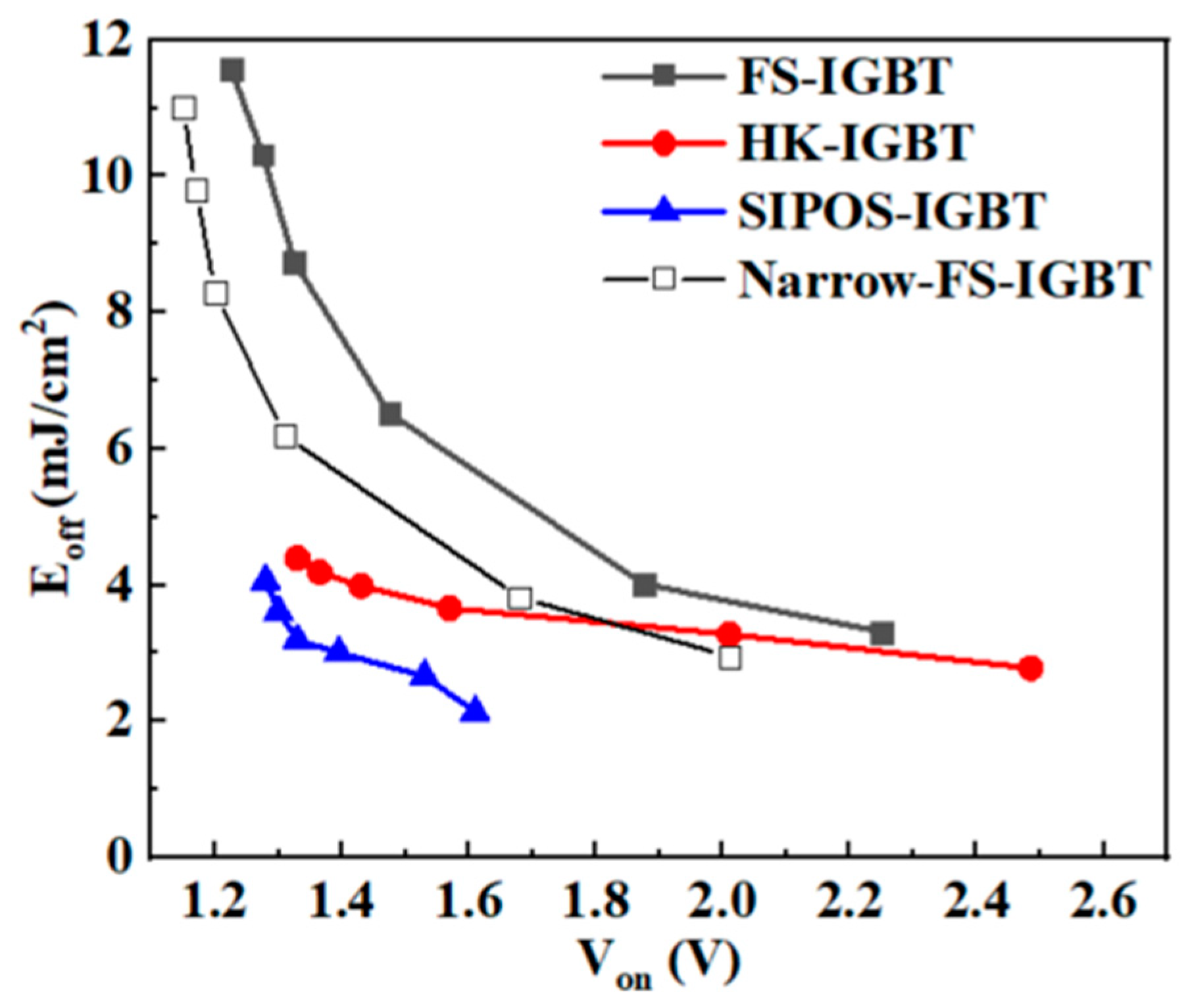

3.3. Turn-Off Characteristics

3.4. Process Flow

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Iwamuro, N.; Laska, T. IGBT History, State-of-the-Art, and Future Prospects. IEEE Trans. Electron Devices 2017, 64, 741–752. [Google Scholar] [CrossRef]

- Laska, T.; Munzer, M.; Pfirsch, F.; Schaeffer, C.; Schmidt, T. The Field Stop IGBT (FS IGBT). A new power device concept with a great improvement potential. In Proceedings of the 2000 12th International Symposium on Power Semiconductor Devices & ICs (ISPSD), Toulouse, France, 22–25 May 2000. [Google Scholar]

- Kitagawa, M.; Omura, I.; Hasegawa, S.; Inoue, T.; Nakagawa, A. A 4500 V injection enhanced insulated gate bipolar transistor (IEGT) operating in a mode similar to a thyristor. In Proceedings of the 1993 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–8 December 1993. [Google Scholar]

- Takahashi, H.; Haruguchi, H.; Hagino, H.; Yamada, T. Carrier stored trench-gate bipolar transistor (CSTBT)-a novel power device for high voltage application. In Proceedings of the 1996 8th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Maui, HI, USA, 20–23 May 1996. [Google Scholar]

- Feng, H.; Yang, W.; Onozawa, Y.; Yoshimura, T.; Tamenori, A.; Sin, J.K.O. A New Fin p-Body Insulated Gate Bipolar Transistor with Low Miller Capacitance. IEEE Electron Device Lett. 2015, 36, 591–593. [Google Scholar] [CrossRef]

- Antoniou, M.; Udrea, F.; Bauer, F. The Superjunction Insulated Gate Bipolar Transistor Optimization and Modeling. IEEE Trans. Electron Devices 2010, 57, 594–600. [Google Scholar] [CrossRef]

- Bauer, F.; Nistor, I.; Mihaila, A.; Antoniou, M.; Udrea, F. Superjunction IGBT Filling the Gap between SJ MOSFET and Ultrafast IGBT. IEEE Electron Device Lett. 2012, 33, 1288–1290. [Google Scholar] [CrossRef]

- Chen, W.; Cheng, J.; Huang, H.; Zhang, B.; Chen, X.B. The oppositely doped islands IGBT achieving ultralow turn off loss. IEEE Trans. Electron Devices 2019, 66, 3690–3693. [Google Scholar] [CrossRef]

- Antoniou, M.; Lophitis, N.; Udrea, F.; Bauer, F.; Vemulapati, U.R.; Badstuebner, U. On the investigation of the “anode side” superjunction IGBT design concept. IEEE Electron Device Lett. 2017, 38, 1063–1066. [Google Scholar] [CrossRef]

- Wei, J.; Zhang, M.; Chen, K.J. Superjunction IGBT with Conductivity Modulation Actively Controlled by Two Separate Driving Signals. IEEE Trans. Electron Devices 2020, 67, 4335–4339. [Google Scholar] [CrossRef]

- Wang, Z.; Lin, Z.; Zeng, W.; Hu, S.; Zhou, J. Comparison of Short-Circuit Safe Operating Areas between the Conventional Field-Stop IGBT and the Superjunction Field-Stop IGBT. IEEE J. Electron Devices Soc. 2022, 10, 146–151. [Google Scholar] [CrossRef]

- Wang, Z.; Zhang, H.; Kuo, J.B. Turn-OFF Transient Analysis of Superjunction IGBT. IEEE Trans. Electron Devices 2019, 66, 991–998. [Google Scholar] [CrossRef]

- Hsieh, A.P.-S.; Camuso, G.; Udrea, F.; Ng, C.; Tang, Y.; Vytla, R.K.; Ranjan, N.; Charles, A. Superjunction IGBT vs. FS IGBT for 200 °C operation. In Proceedings of the 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hong Kong, China, 10–14 May 2015. [Google Scholar]

- Huang, M.; Gao, B.; Yang, Z.; Lai, L.; Gong, M. A Carrier-Storage-Enhanced Superjunction IGBT with Ultralow Loss and On-State Voltage. IEEE Electron Device Lett. 2018, 39, 264–267. [Google Scholar] [CrossRef]

- Deboy, G.; Marz, N.; Stengl, J.P.; Strack, H.; Tihanyi, J.; Weber, H. A new generation of high voltage MOSFETs breaks the limit line of silicon. In Proceedings of the 1998 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 6–9 December 1998. [Google Scholar]

- Yamauchi, S.; Hattori, Y.; Yamaguchi, H. Electrical properties of super junction p-n diodes fabricated by trench filling. In Proceedings of the 2003 15th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Cambridge, UK, 14–17 April 2003. [Google Scholar]

- Huang, H.; Chen, X. Optimization of Specific On-Resistance of Balanced Symmetric Superjunction MOSFETs Based on a Better Approximation of Ionization Integral. IEEE Trans. Electron Devices 2012, 59, 2742–2747. [Google Scholar] [CrossRef]

- Chen, X.; Huang, M. A vertical power MOSFET with an interdigitated drift region using high-k insulator. IEEE Trans. Electron Devices 2012, 59, 2430–2437. [Google Scholar] [CrossRef]

- Lyu, X.; Chen, X. Vertical power Hk-MOSFET of hexagonal layout. IEEE Trans. Electron Devices 2013, 60, 1709–1715. [Google Scholar] [CrossRef]

- Chen, W.; Cheng, J.; Chen, X.B. A Novel IGBT with High-k Dielectric Modulation Achieving Ultralow Turn-Off Loss. IEEE Trans. Electron Devices 2020, 67, 1066–1070. [Google Scholar] [CrossRef]

- Chen, W.; Cheng, J. Study on the IGBT Using a Deep Trench Filled with SiO2 and High-k Dielectric Film. IEEE J. Electron Devices Soc. 2020, 8, 1025–1030. [Google Scholar] [CrossRef]

- Lutz, J.; Baburske, R. Dynamic avalanche in bipolar power devices. Microelectron. Reliab. 2012, 52, 475–481. [Google Scholar] [CrossRef]

- De Falco, G.; Würfel, A.; Maresca, L.; Kaminski, N.; Irace, A.; Silber, D. Effects of current filaments during dynamic avalanche on the collector-emitter-voltage of high voltage Trench-IGBTs. In Proceedings of the 2015 17th European Conference on Power Electronics and Applications (EPE’15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015. [Google Scholar]

- Ying, W.; Zhu, C.; Wu, C.; Liu, J. Improving reliability of beveled power semiconductor devices passivated by SIPOS. Microelectron. Reliab. 2005, 45, 535–539. [Google Scholar]

- Reggiani, S.; Giordano, C.; Gnudi, A.; Gnani, E.; Baccarani, G.; Dobrzynska, J.; Vobecky, J.; Bellini, M. TCAD-based investigation on transport properties of Diamond-like carbon coatings for HV-ICs. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016. [Google Scholar]

- Matsushita, T.; Aoki, T.; Ohtsu, T.; Yamoto, H.; Hayashi, H.; Okayama, M.; Kawana, Y. Highly reliable high-voltage transistors by use of the SIPOS process. IEEE Trans. Electron Devices 1976, 23, 826–830. [Google Scholar] [CrossRef]

- Baditoiu, C.; Ravariu, C.; Rusu, A.; Udrea, F. Dynamic behavior optimization of the junctions with SIPOS layer termination. In Proceedings of the 2004 International Semiconductor Conference. CAS 2004 Proceedings (IEEE Cat. No. 04TH8748), Sinaia, Romania, 4–6 October 2004. [Google Scholar]

- Cao, Z.; Duan, B.; Shi, T.; Yuan, S.; Yang, Y. A Superjunction U-MOSFET with SIPOS Pillar Breaking Superjunction Silicon Limit by TCAD Simulation Study. IEEE Electron Device Lett. 2017, 38, 794–797. [Google Scholar] [CrossRef]

- Duan, B.; Ma, J.; Yang, L.; Wang, Y.; Yang, Y. Simulation of AlGaN/GaN MISFET with 3.6-GW/cm2 High FOM by SIPOS Field Plates Electric Field Modulation. IEEE Trans. Electron Devices 2023, 70, 429–434. [Google Scholar] [CrossRef]

- SentaurusTM Structure Editor User Guide; Synopsys Inc.: Mountain View, CA, USA, 2018.

- Lutz, J.; Schlangenotto, H.; Scheuermann, U.; De Doncker, R. Semiconductor Power Devices: Physics, Characteristics, Reliability; Springer: Berlin/Heidelberg, Germany, 2018. [Google Scholar]

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer: New York, NY, USA, 2008. [Google Scholar]

| Parameter | FS-IGBT | HK-IGBT | SIPOS-IGBT |

|---|---|---|---|

| Cell pitch/μm | 4 | 4 | 4 |

| Thickness/μm | 120 | 110 | 110 |

| N-drift Dop/cm−3 | 5 × 1013 | 5 × 1013 | 5 × 1013 |

| Width of N-drift/μm | 4 | 2 | 2 |

| Width of SIPOS/μm | / | / | 0.5 |

| Width of HK/μm | / | 2 | / |

| FS layer thickness/μm | 5 | 5 | 5 |

| FS layer Dop/cm−3 | 1 × 1016 | 1 × 1016 | 1 × 1016 |

| Collector thickness/μm | 1 | 1 | 1 |

| Collector Dop/cm−3 | 1 × 1017 | 1 × 1017 | 1 × 1017 |

| K | / | 150 | / |

| SIPOS thickness/μm | / | / | 0.4 |

| SIPOS resistivity/Ω·cm | / | / | 1010 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yuan, S.; Yan, Z.; Li, Y.; Wang, Y.; Liu, Q.; Zhan, X.; Jiang, X.; He, Y.; Gong, X. A Novel IGBT with SIPOS Pillars Achieving Ultralow Power Loss in TCAD Simulation Study. Micromachines 2024, 15, 759. https://doi.org/10.3390/mi15060759

Yuan S, Yan Z, Li Y, Wang Y, Liu Q, Zhan X, Jiang X, He Y, Gong X. A Novel IGBT with SIPOS Pillars Achieving Ultralow Power Loss in TCAD Simulation Study. Micromachines. 2024; 15(6):759. https://doi.org/10.3390/mi15060759

Chicago/Turabian StyleYuan, Song, Zhaoheng Yan, Yanzuo Li, Ying Wang, Qifan Liu, Xinbin Zhan, Xi Jiang, Yanjing He, and Xiaowu Gong. 2024. "A Novel IGBT with SIPOS Pillars Achieving Ultralow Power Loss in TCAD Simulation Study" Micromachines 15, no. 6: 759. https://doi.org/10.3390/mi15060759

APA StyleYuan, S., Yan, Z., Li, Y., Wang, Y., Liu, Q., Zhan, X., Jiang, X., He, Y., & Gong, X. (2024). A Novel IGBT with SIPOS Pillars Achieving Ultralow Power Loss in TCAD Simulation Study. Micromachines, 15(6), 759. https://doi.org/10.3390/mi15060759