An In-Depth Study of Ring Oscillator Reliability under Accelerated Degradation and Annealing to Unveil Integrated Circuit Usage

Abstract

:1. Introduction

2. Experimental Setup

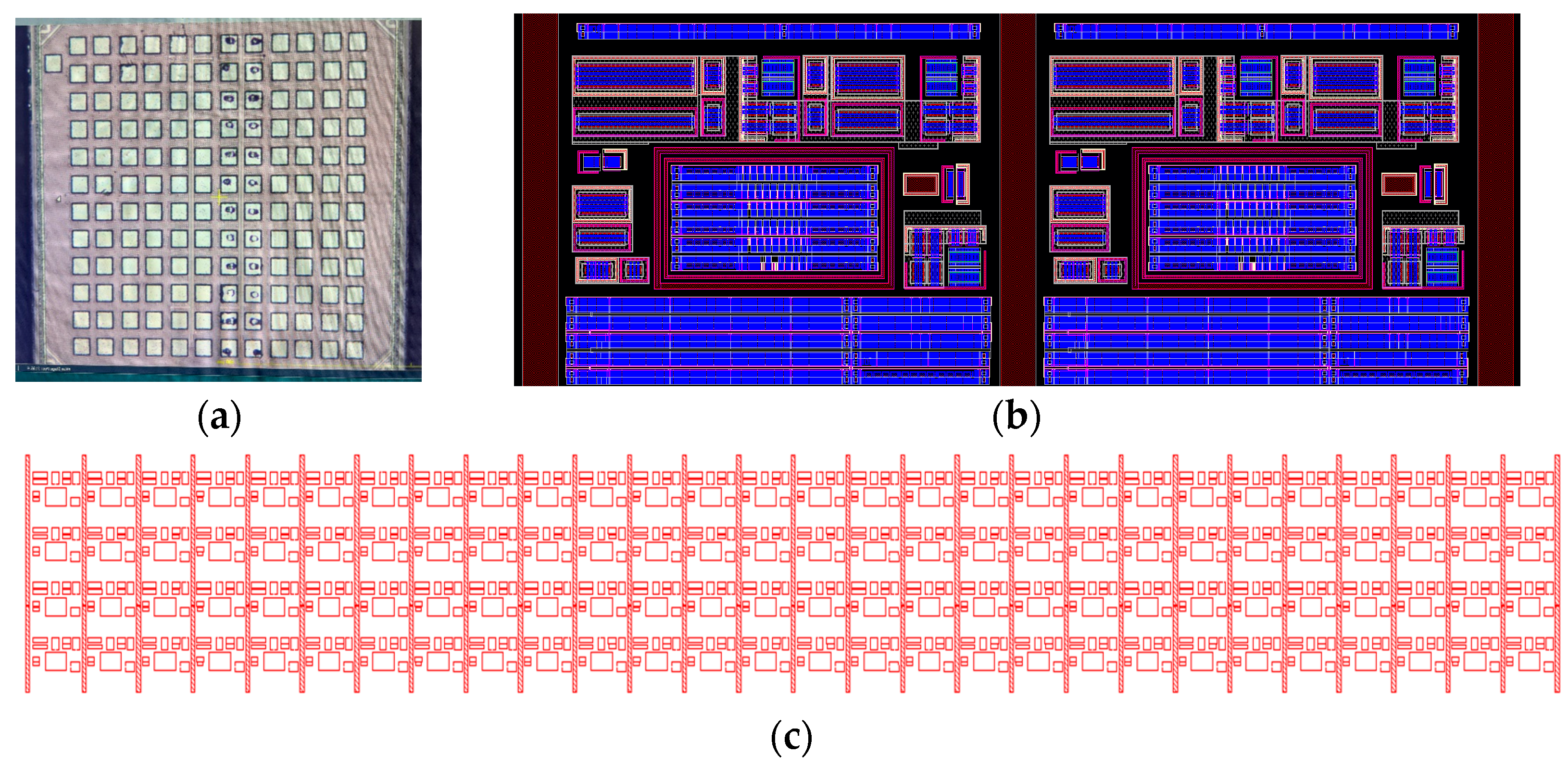

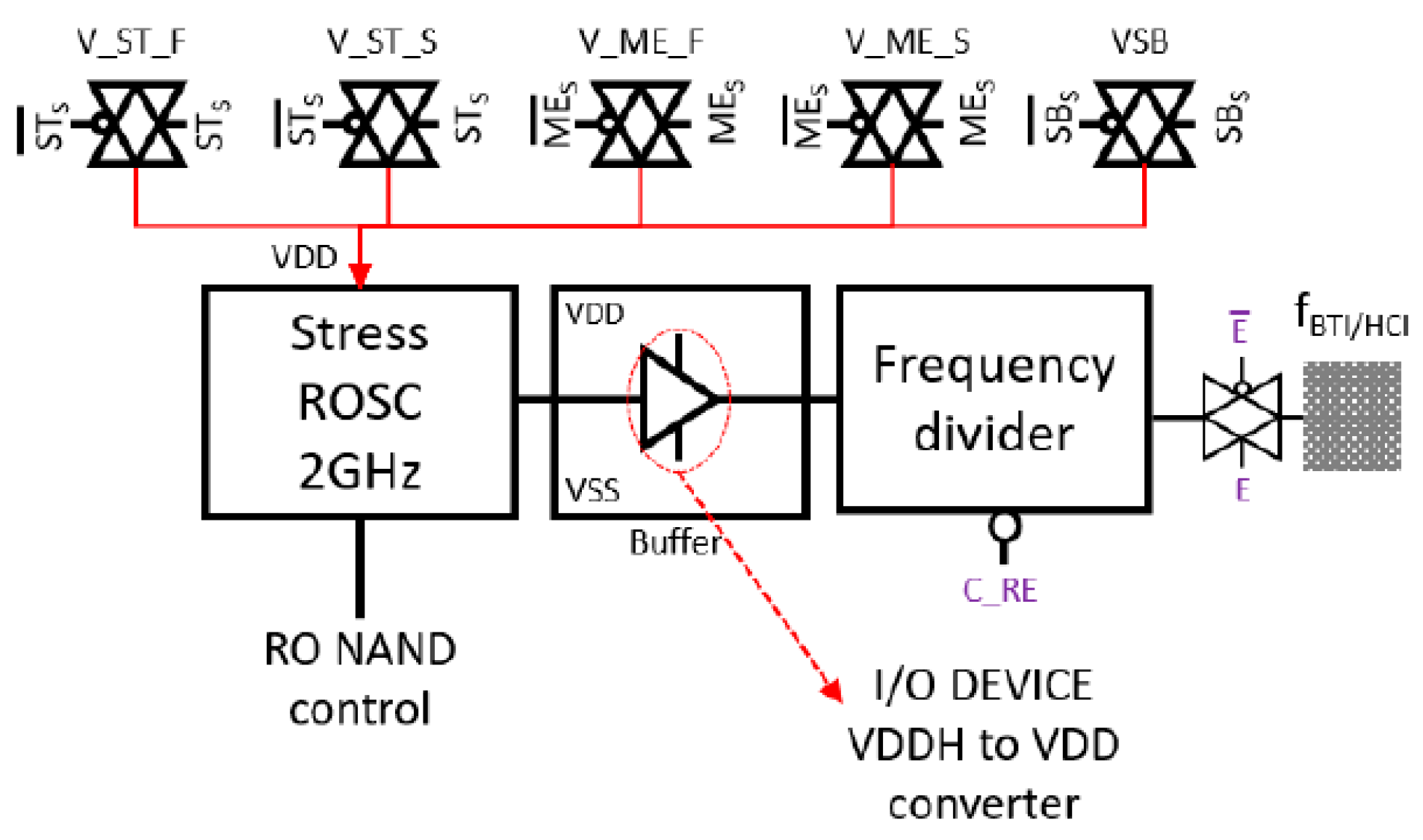

2.1. Chip Design and Architecture

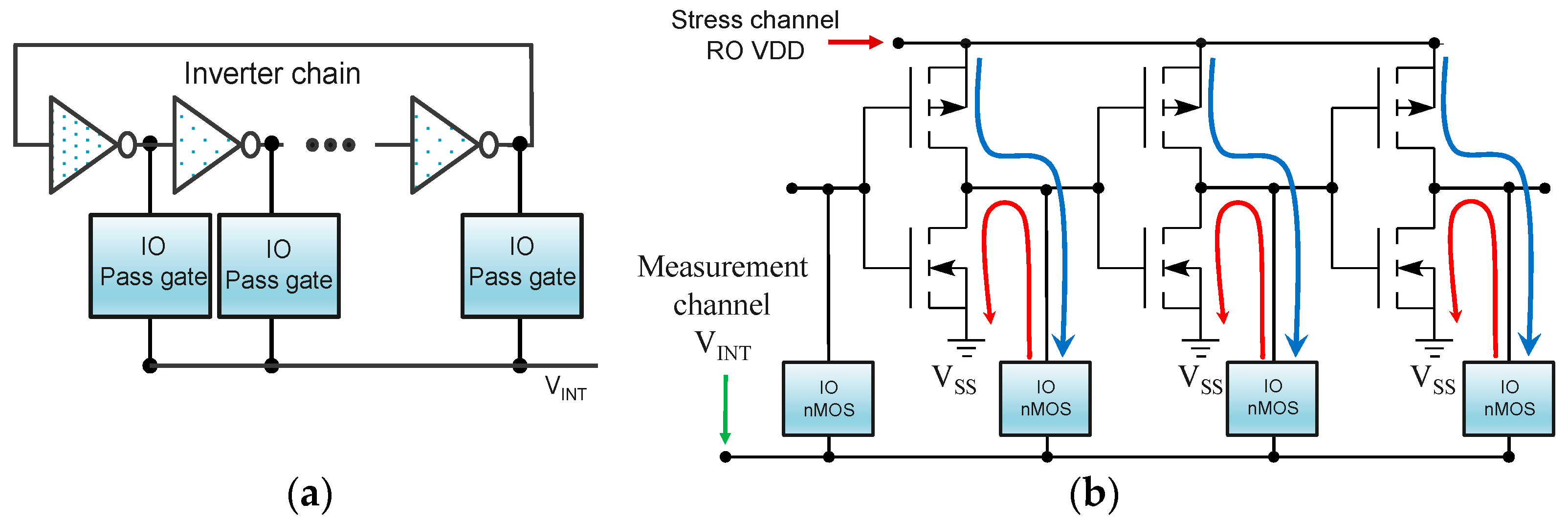

2.2. Unit Cell Building Blocks

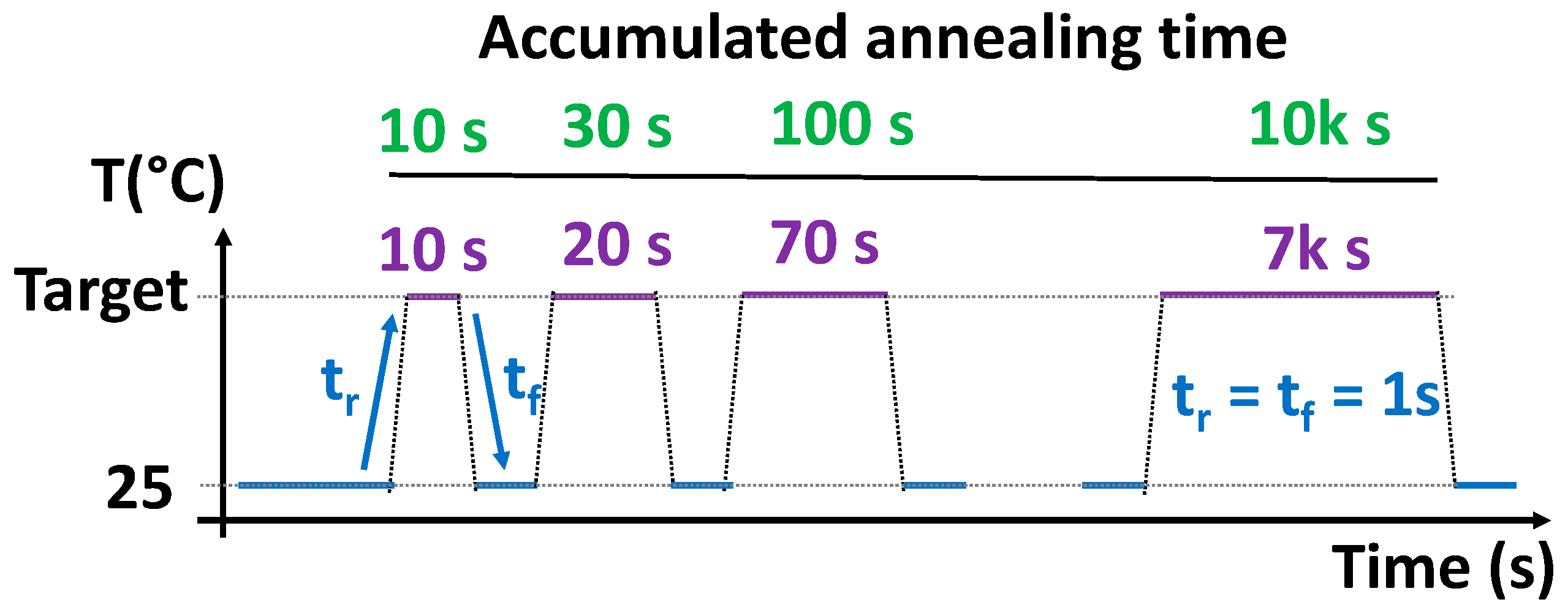

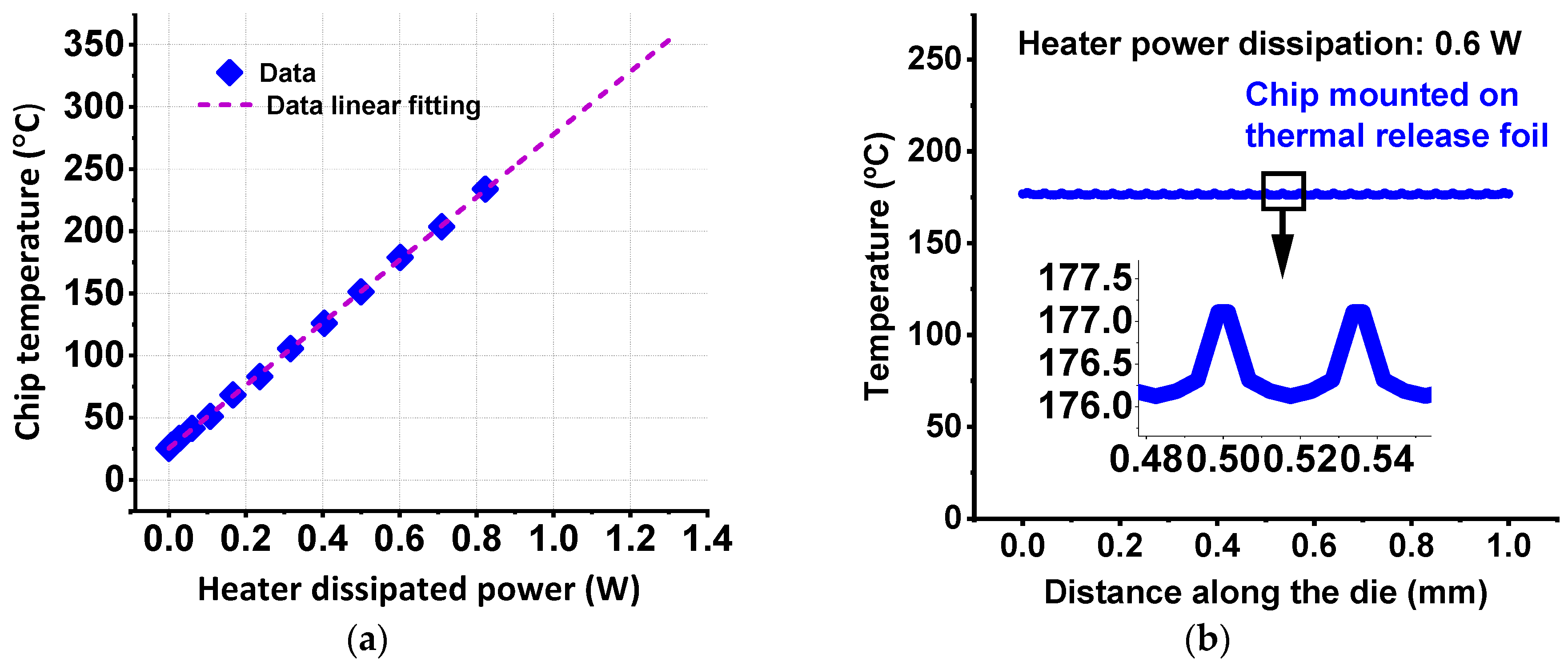

2.3. On-Chip Heaters for Accelerated Degradation/Annealing Experiments

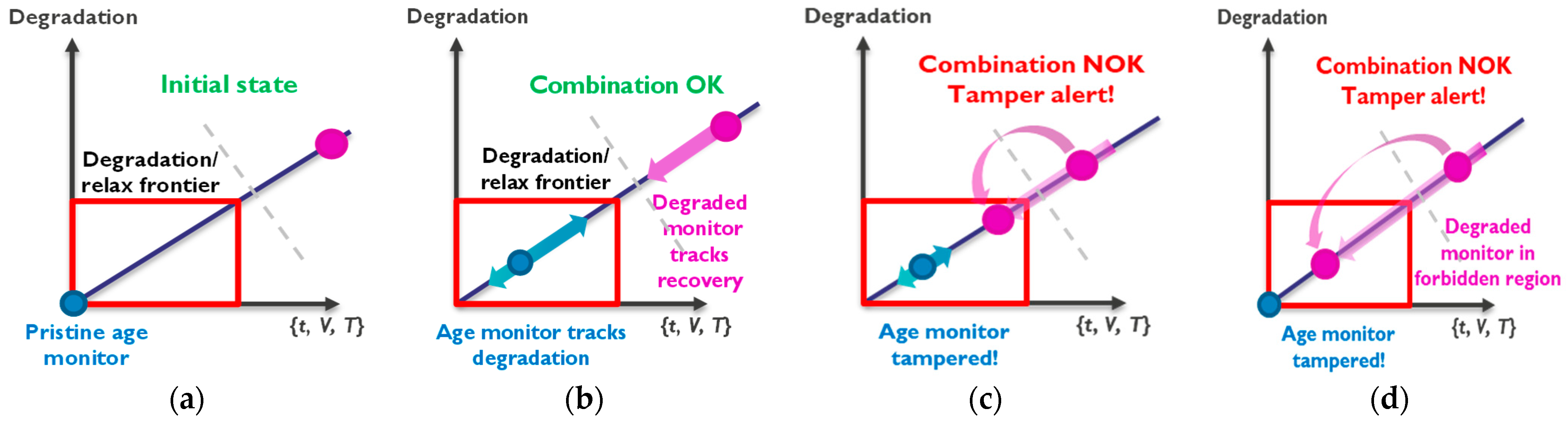

3. The On-Chip Degradation Monitor with Tamper-Aware Capability Concept

- After nominal and legitimate IC use: following regular IC operation within the technology-defined voltage and temperature margins, the degradation monitors will progressively accumulate wear-out, while the pre-stressed ones will gradually relax. As depicted in Figure 6b, under regular operation, neither of the two monitors will go beyond a maximum degradation/relaxation window, i.e., the red box. In this scenario, both monitors will show that the IC has been operating trustfully;

- After nominal use and mild tamper annealing: in this situation, the chip has been used and tampered with to pretend that the IC is less used than it really is, like rolling back kilometers from an odometer in a car. In this scenario, the pre-stressed monitor enters its forbidden relaxation window because the anneal attempt accelerates its relaxation. When this happens, the tamper flag shows an illegitimate combination of the monitors, as depicted in Figure 6c, unveiling the tamper procedure and, more importantly, invalidating the IC age determination with the blue monitors;

- After a strong annealing procedure: in this scenario, the chip has undergone a strong annealing procedure to illegally rejuvenate it. In this case, both aging monitors will show almost complete relaxation status, as depicted in Figure 6d. Even though the IC seems to be brand new according to the first degradation monitor, the pre-stressed monitor is located deep in its forbidden region, revealing the strong annealing, maintaining the tamper awareness of the monitor system, and invalidating, also in this case, the IC’s age determination with the blue monitors.

4. Results

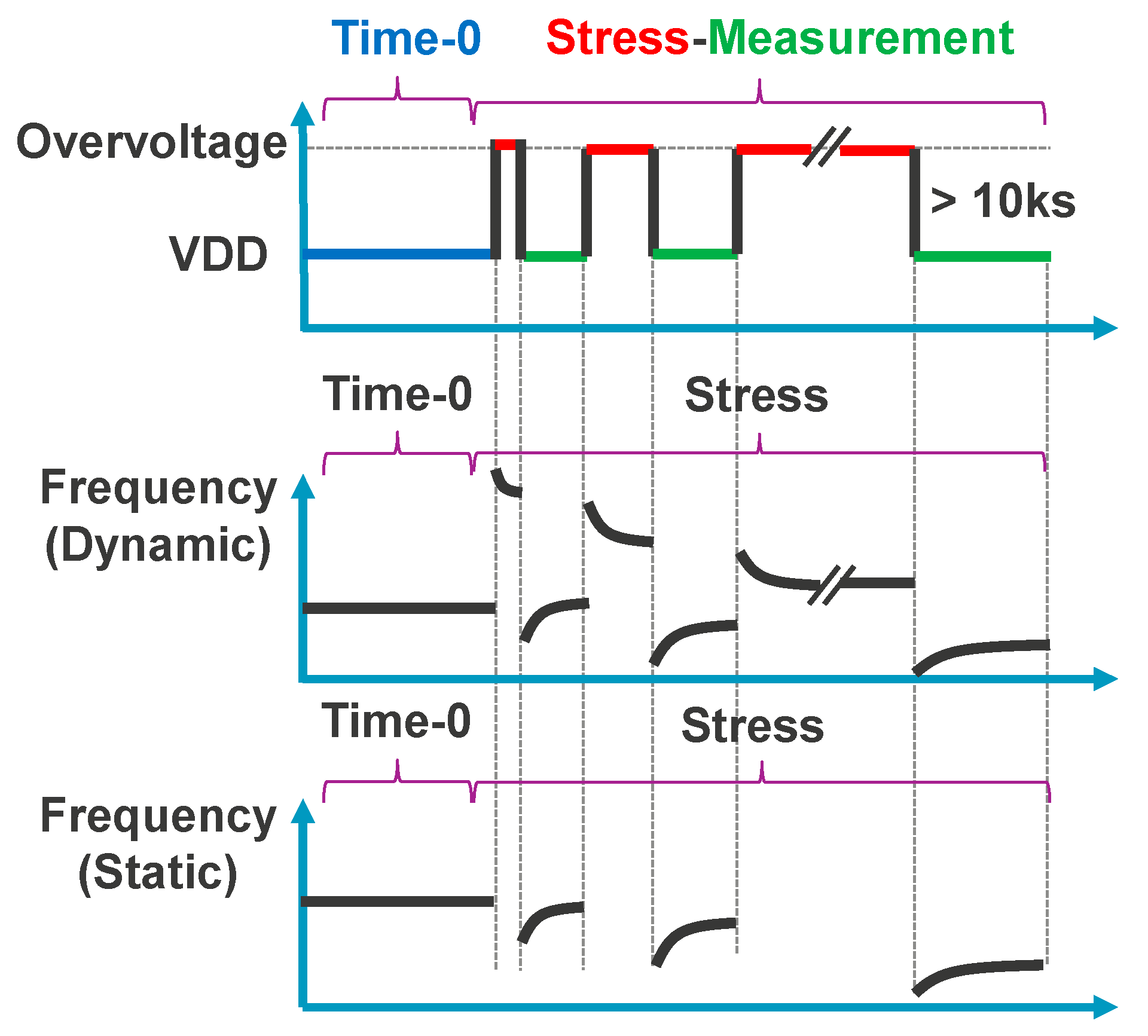

4.1. Evaluation Methodology

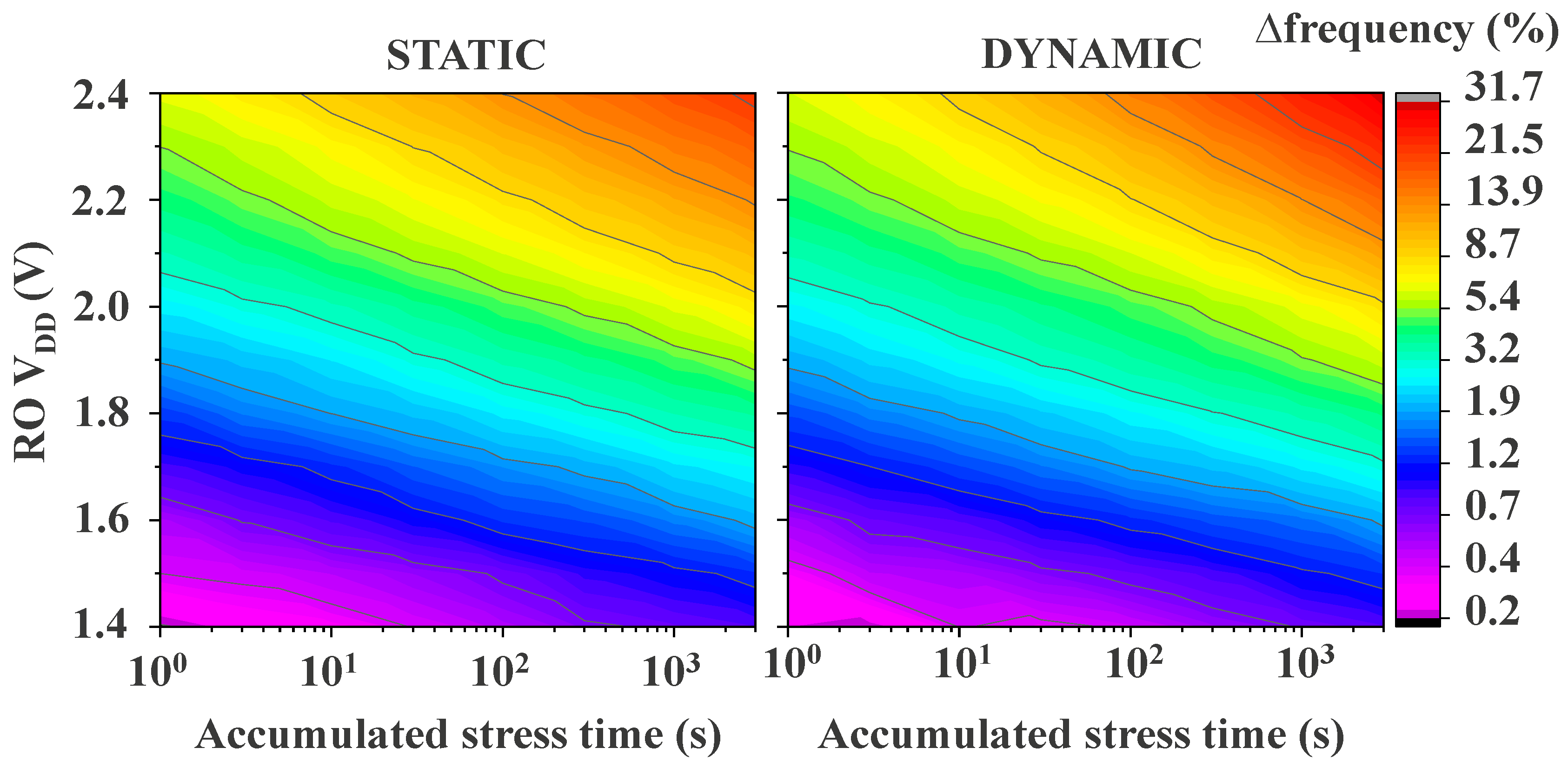

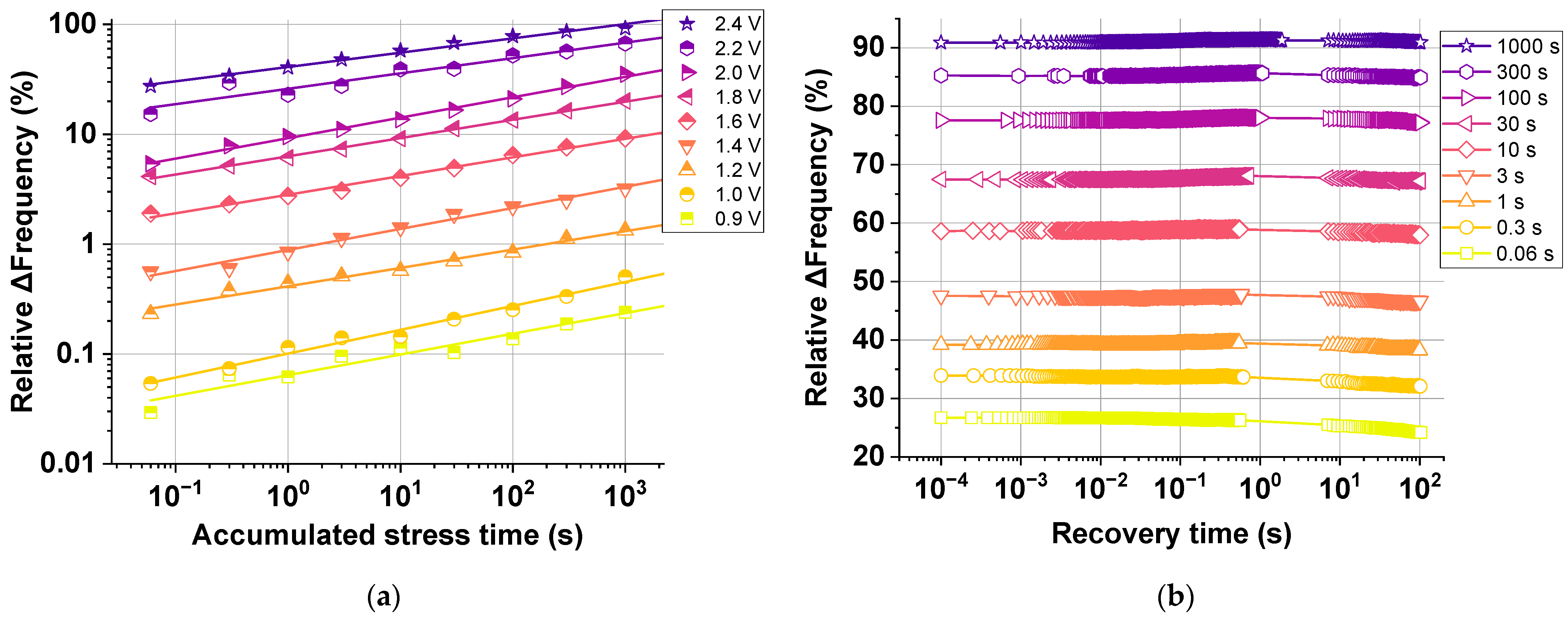

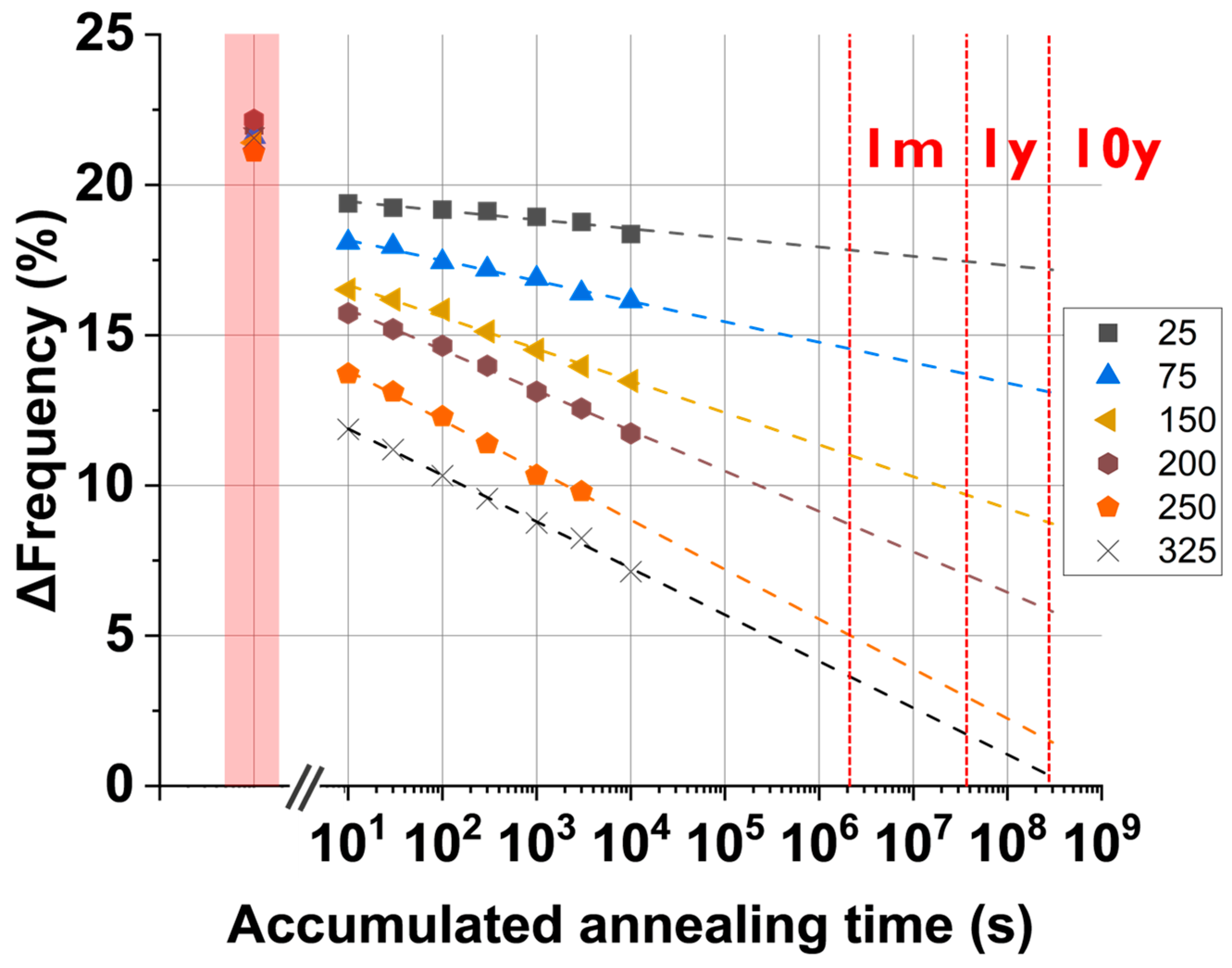

4.2. Regular-RO-Based Monitors: Frequency Degradation and Recovery

4.3. True-RO-Based Monitors: Frequency Degradation and Recovery

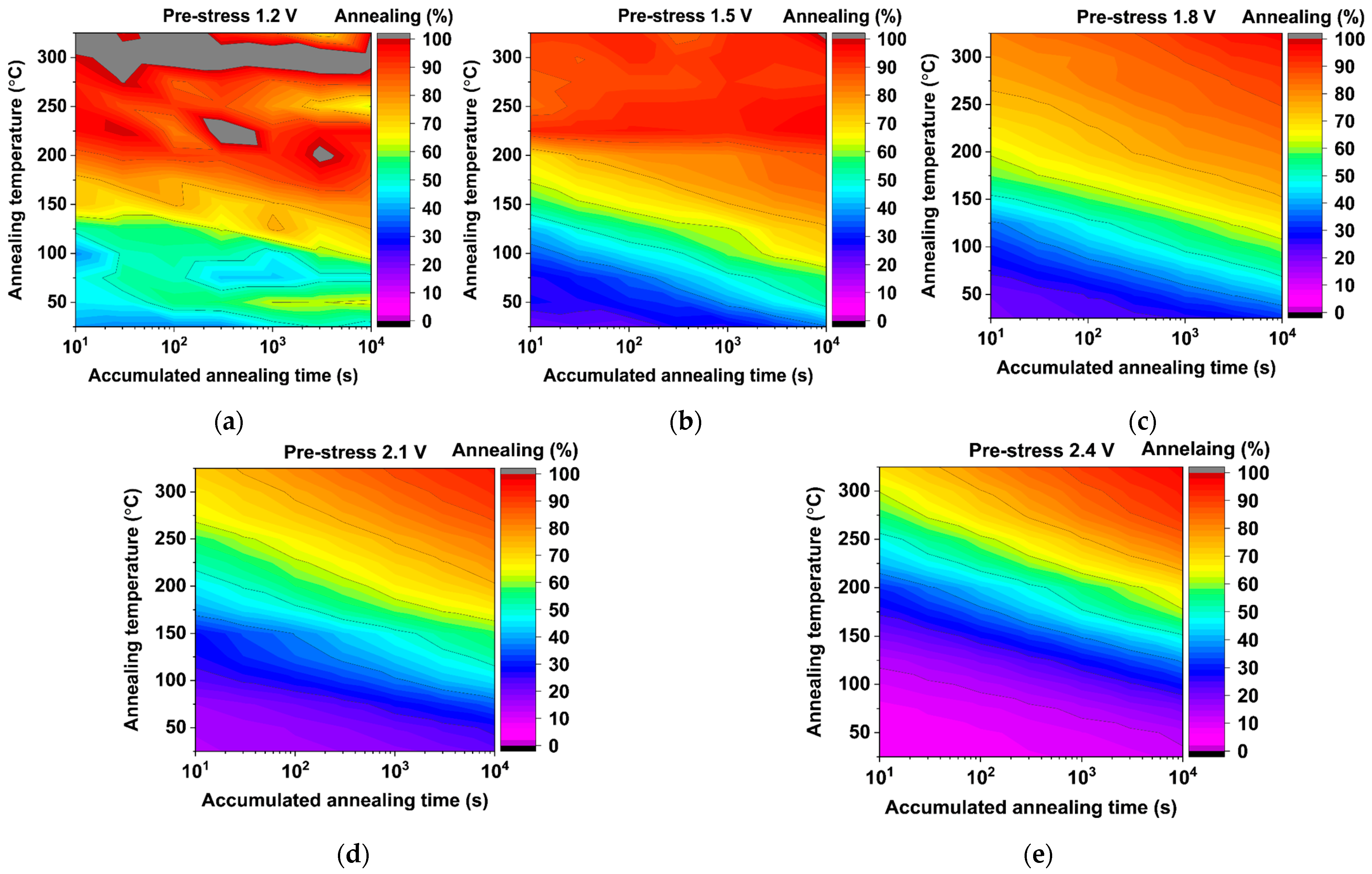

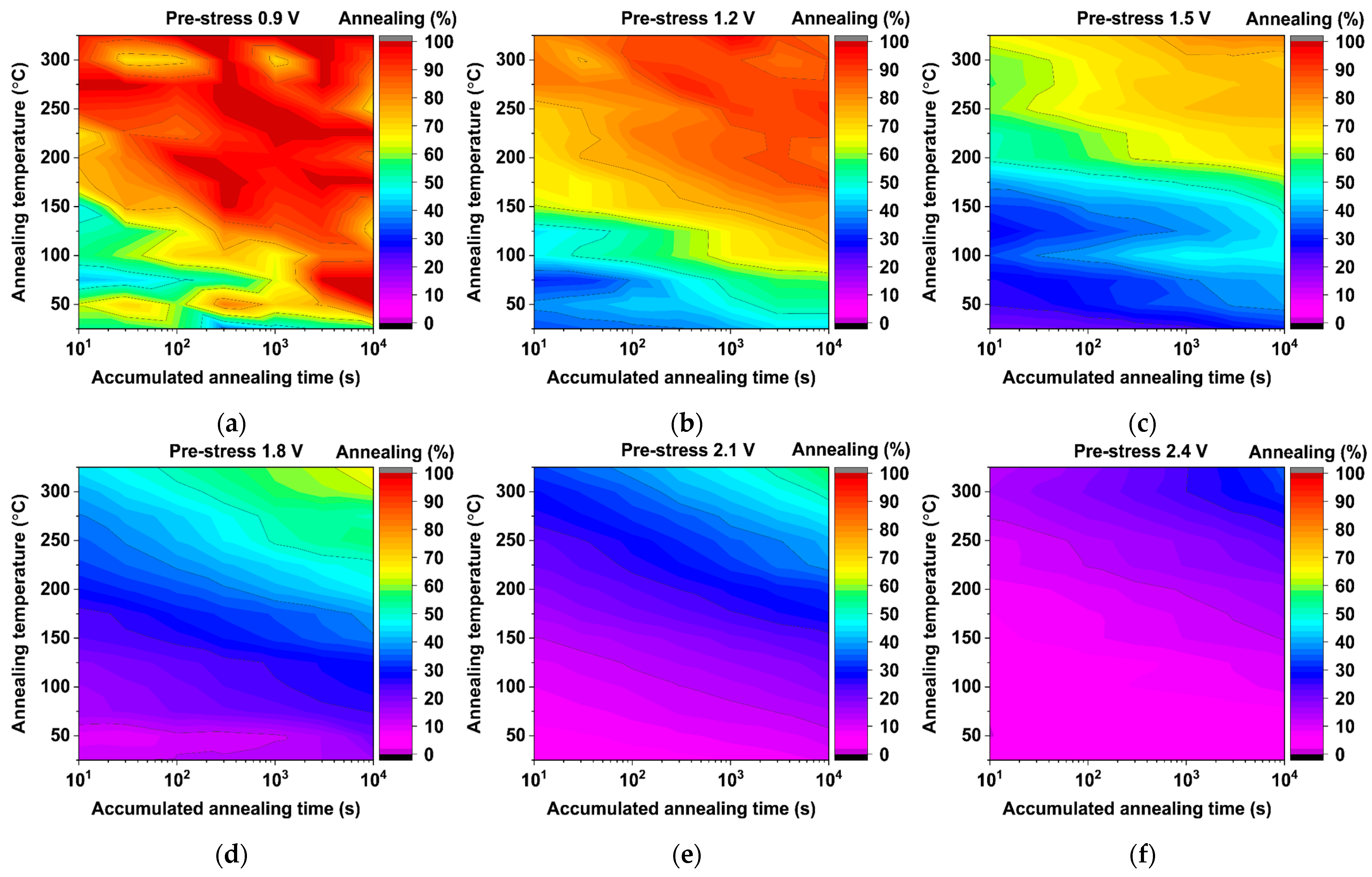

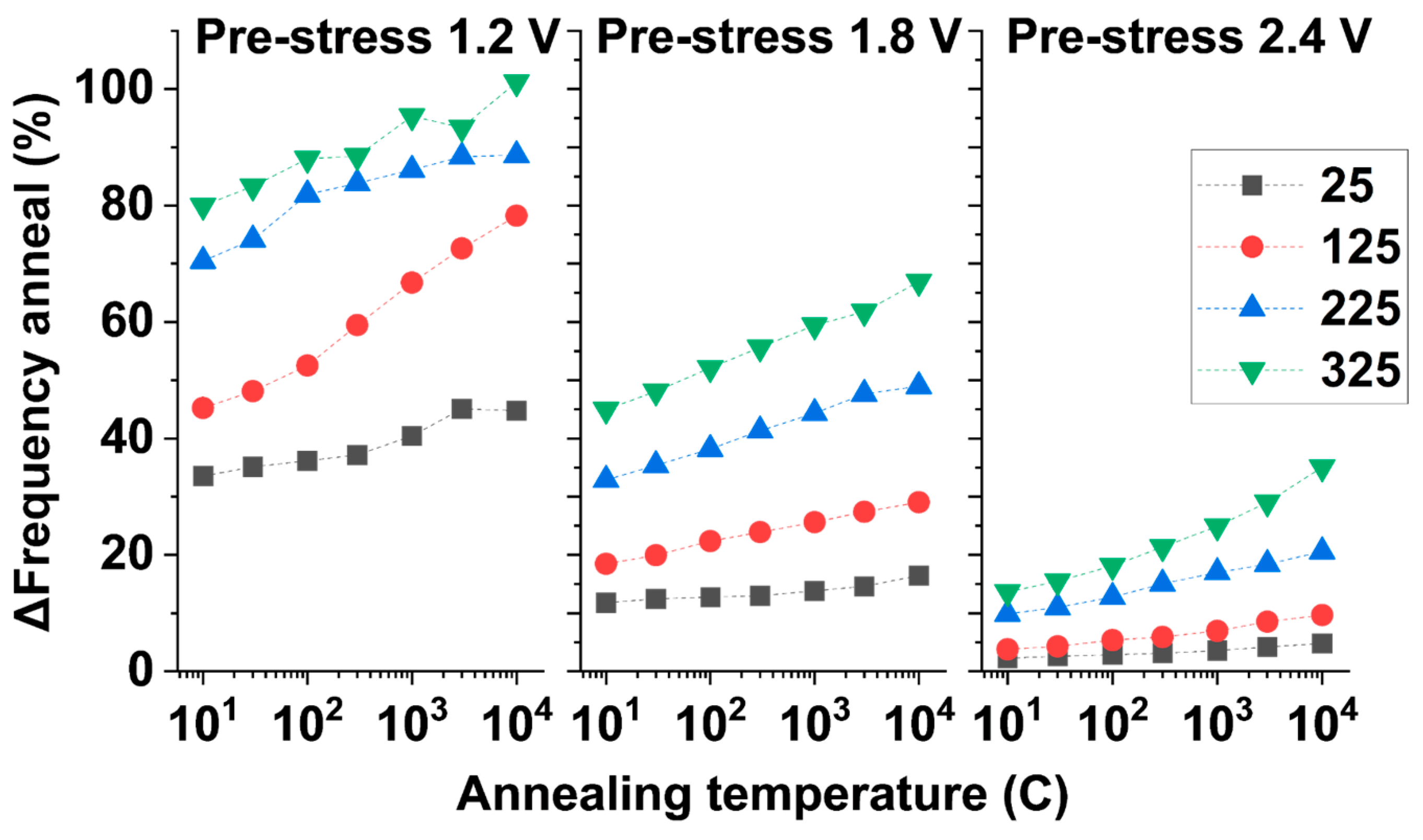

4.4. Tamper-Flag Capability of the True-HCD Monitor

4.5. Utilizing Annealing of True-HCD Monitors for IC Age Determination

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| BTI | bias temperature instability |

| CPU | Central Processing Unit |

| eMSM | Enhanced Measurement Stress Measurement |

| F&S | Force-and-Sense |

| HPC | high-performance computing |

| HCD | hot carrier degradation |

| IC | integrated circuit |

| IO | Input/Output |

| n | Time acceleration factor |

| PDN | Power Delivery Network |

| RO | ring oscillator |

| VINT | Internal Voltage |

| Vj | junction voltage |

| VAF | voltage acceleration factor |

References

- Kerwin, K.; Andrews, D.; Whitehead, B.; Adibi, N.; Lavandeira, S. The significance of product design in the circular economy: A sustainable approach to the design of data centre equipment as demonstrated via the CEDaCI design case study. Mater. Today Proc. 2022, 64, 1283–1289. [Google Scholar] [CrossRef]

- Boakes, L.; Bardon, M.G.; Schellekens, V.; Liu, I.-Y.; Vanhouche, B.; Mirabelli, G.; Sebaai, F.; Van Winckel, L.; Gallagher, E.; Rolin, C.; et al. Cradle-to-gate Life Cycle Assessment of CMOS Logic Technologies. In Proceedings of the Technical Digest—International Electron Devices Meeting, IEDM, San Francisco, CA, USA, 9–13 December 2023; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2023. [Google Scholar] [CrossRef]

- Kashyap, R. Silicon lifecycle management (SLM) with in-chip monitoring. In Proceedings of the IEEE International Reliability Physics Symposium Proceedings, Monterey, CA, USA, 21–25 March 2021; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2021. [Google Scholar] [CrossRef]

- Fish, R.; Athavale, J. Silicon Lifecycle Managements Addressing Reliability, Availability and Serviceability Requirements in HPC Datacenter and Automotive Systems. IEICE ESS Fundam. Rev. 2024, 17, 257–264. [Google Scholar] [CrossRef]

- Sudarshan, C.C.; Matkar, N.; Vrudhula, S.; Sapatnekar, S.S.; Chhabria, V.A. ECO-CHIP: Estimation of Carbon Footprint of Chiplet-based Architectures for Sustainable VLSI. In Proceedings of the 2024 IEEE International Symposium on High-Performance Computer Architecture (HPCA), Edinburgh, UK, 2–6 March 2024; IEEE: Piscataway, NJ, USA, 2024; pp. 671–685. [Google Scholar] [CrossRef]

- Ragnarsson, L.-A.; Bardon, M.G.; Wuytens, P.; Mirabelli, G.; Jang, D.; Willems, G.; Mallik, A.; Spessot, A.; Ryckaert, J.; Parvais, B. Environmental Impact of CMOS Logic Technologies. In Proceedings of the 6th IEEE Electron Devices Technology and Manufacturing Conference, EDTM 2022, Oita, Japan, 6–9 March 2022; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2022; pp. 82–84. [Google Scholar] [CrossRef]

- Bashroush, R.; Rteil, N.; Kenny, R.; Wynne, A. Optimizing Server Refresh Cycles: The Case for Circular Economy with an Aging Moore’s Law. IEEE Trans. Sustain. Comput. 2022, 7, 189–200. [Google Scholar] [CrossRef]

- Hill, I.; Chanawala, P.; Singh, R.; Sheikholeslam, S.A.; Ivanov, A. CMOS Reliability from Past to Future: A Survey of Requirements, Trends, and Prediction Methods. IEEE Trans. Device Mater. Reliab. 2022, 22, 1–18. [Google Scholar] [CrossRef]

- Jopling, J. Risk Management Informed by an Uncertain Bathtub Curve (Invited). In Proceedings of the IEEE International Reliability Physics Symposium Proceedings, Monterey, CA, USA, 26–30 March 2023; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2023. [Google Scholar] [CrossRef]

- Grasser, T.; Kaczer, B.; Goes, W.; Reisinger, H.; Aichinger, T.; Hehenberger, P.; Wagner, P.-J.; Schanovsky, F.; Franco, J.; Luque, M.T.; et al. The paradigm shift in understanding the bias temperature instability: From reaction-diffusion to switching oxide traps. IEEE Trans. Electron Devices 2011, 58, 3652–3666. [Google Scholar] [CrossRef]

- Kaczer, B.; Grasser, T.; Roussel, P.J.; Franco, J.; Degraeve, R.; Ragnarsson, L.-A.; Simoen, E.; Groeseneken, G.; Reisinger, H. Origin of NBTI variability in deeply scaled pFETs. In Proceedings of the IEEE International Reliability Physics Symposium Proceedings, Anaheim, CA, USA, 2–6 May 2010; pp. 26–32. [Google Scholar] [CrossRef]

- Mahapatra, S.; Saha, D.; Varghese, D.; Kumar, P.B. On the generation and recovery of interface traps in MOSFETs subjected to NBTI, FN, and HCI stress. IEEE Trans. Electron Devices 2006, 53, 1583–1592. [Google Scholar] [CrossRef]

- Vandemaele, M.; Kaczer, B.; Tyaginov, S.; Franco, J.; Degraeve, R.; Chasin, A.; Wu, Z.; Bury, E.; Xiang, Y.; Mertens, H.; et al. The properties, effect and extraction of localized defect profiles from degraded FET characteristics. In Proceedings of the IEEE International Reliability Physics Symposium Proceedings, Monterey, CA, USA, 21–25 March 2021; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2021. [Google Scholar] [CrossRef]

- Wu, Z.; Franco, J.; Truijen, B.; Roussel, P.; Kaczer, B.; Linten, D.; Groeseneken, G. Investigation of the Impact of Hot-Carrier-Induced Interface State Generation on Carrier Mobility in nMOSFET. IEEE Trans. Electron Devices 2021, 68, 3246–3253. [Google Scholar] [CrossRef]

- Jech, M.; Rott, G.; Reisinger, H.; Tyaginov, S.; Rzepa, G.; Grill, A.; Jabs, D.; Jungemann, C.; Waltl, M.; Grasser, T. Mixed Hot-Carrier/Bias Temperature Instability Degradation Regimes in Full VG, VD Bias Space: Implications and Peculiarities. IEEE Trans. Electron Devices 2020, 67, 3315–3322. [Google Scholar] [CrossRef]

- Mahapatra, S.; Sharma, U. A Review of Hot Carrier Degradation in n-Channel MOSFETs—Part I: Physical Mechanism. IEEE Trans. Electron Devices 2020, 67, 2660–2671. [Google Scholar] [CrossRef]

- Khdr, H.; Amrouch, H.; Henkel, J. Aging-Aware Boosting. IEEE Trans. Comput. 2018, 67, 1217–1230. [Google Scholar] [CrossRef]

- Misra, P.A.; Manousakis, I.; Choukse, E.; Jalili, M.; Goiri, I.; Raniwala, A.; Warrier, B.; Alissa, H.; Ramakrishnan, B.; Tuma, P.; et al. Overclocking in Immersion-Cooled Datacenters. IEEE Micro 2022, 42, 10–17. [Google Scholar] [CrossRef]

- Veitch, P.; Macnamara, C.; Browne, J.J. Precise Turbo Frequency Tuning and Shared Resource Optimisation for Energy-Efficient Cloud Native Workloads. In Proceedings of the 2023 IEEE 9th International Conference on Network Softwarization: Boosting Future Networks through Advanced Softwarization, NetSoft 2023—Proceedings, Madrid, Spain, 19–23 June 2023; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2023; pp. 222–226. [Google Scholar] [CrossRef]

- Cai, E.; Marculescu, D. TEI-Turbo: Temperature effect inversion-aware turbo boost for finfet-based multi-core systems. In Proceedings of the 2015 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Austin, TX, USA, 2–6 November 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 500–507. [Google Scholar] [CrossRef]

- Sachdeva, S.; Zhang, J.; Amrouch, H.; Tan, S.X.D. Long-Term Aging Impacts on Spatial On-Chip Power Density and Temperature. In Proceedings of the 2023 19th International Conference on Synthesis, Modeling, Analysis and Simulation Methods, and Appli-cations to Circuit Design, SMACD 2023, Funchal, Portugal, 3–5 July 2023; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2023. [Google Scholar] [CrossRef]

- Zhang, D.; Ren, Q.; Su, D. An On-Chip Path Delay Measurement Sensor for Aging Monitoring. In Proceedings of the International Conference on ASIC, Kunming, China, 26–29 October 2021; IEEE Computer Society: Piscataway, NJ, USA, 2021. [Google Scholar] [CrossRef]

- Wu, J.; Sun, Y.; Wang, Y.; Lin, Y.; Fan, M.; Huang, J. Research on Path Delay with BTI Recovery Effect. In Proceedings of the European Test Workshop, Barcelona, Spain, 23–27 May 2022; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2022. [Google Scholar] [CrossRef]

- Kandula, K.; Kolisetti, R.; Chimmad, S. Path Margin Monitor for Silicon Lifecycle. In Proceedings of the WINTECHCON 2023—IEEE Women in Technology Conference: Emerging Technologies from Silicon to Software for a Sustainable Future, Bangalore, India, 21 September 2023; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2023. [Google Scholar] [CrossRef]

- Chakraborty, S.; Hasan, M.M.; Paul, M.; Tran, D.-D.; Geury, T.; Davari, P.; Blaabjerg, F.; El Baghdadi, M.; Hegazy, O. Real-Life Mission Profile-Oriented Lifetime Estimation of a SiC Interleaved Bidirectional HV DC/DC Converter for Electric Vehicle Drivetrains. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 5142–5167. [Google Scholar] [CrossRef]

- Ahmed, B.; Bepary, M.K.; Pundir, N.; Borza, M.; Raikhman, O.; Garg, A.; Donchin, D.; Cron, A.; Abdel-moneum, M.A.; Farahmandi, F.; et al. Quantifiable Assurance: From IPs to Platforms. arXiv 2022, arXiv:2204.07909. [Google Scholar]

- Wang, X.; Han, Y.; Tehranipoor, M. System-Level Counterfeit Detection Using On-Chip Ring Oscillator Array. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2019, 27, 2884–2896. [Google Scholar] [CrossRef]

- Keane, J.; Wang, X.; Persaud, D.; Kim, C.H. An all-in-one silicon odometer for separately monitoring HCI, BTI, and TDDB. IEEE J. Solid-State Circuits 2010, 45, 817–829. [Google Scholar] [CrossRef]

- Mamun, M.A.Z.; Conrad, N.J.; Mohammadi, S.; Alam, M.A. Validating Supply Chain against Recycled COTS ICs using I/O Pad Transistors: A Zero-Area Intrinsic Odometer Approach. In Proceedings of the 2024 IEEE International Reliability Physics Symposium (IRPS), Grapevine, TX, USA, 14–18 April 2024; IEEE: Piscataway, NJ, USA, 2024; pp. 1–8. [Google Scholar] [CrossRef]

- Diaz-Fortuny, J.; Saraza-Canflanca, P.; Bury, E.; Vandemaele, M.; Kaczer, B.; Degraeve, R. A Ring-Oscillator-Based Degradation Monitor Concept with Tamper Detection Capability. In Proceedings of the 2022 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 27–31 March 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 1–7. [Google Scholar] [CrossRef]

- Gromala, P.; Dietz, F.; Rzepka, S.; Han, B. Concept of the 3rd Generation of Reliability for Electronic Smart Systems. In Proceedings of the 2019 18th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), Las Vegas, NV, USA, 28–31 May 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 917–922. [Google Scholar] [CrossRef]

- Rahman, F.; Forte, D.; Tehranipoor, M.M. Reliability vs. security: Challenges and opportunities for developing reliable and secure integrated circuits. In Proceedings of the 2016 IEEE International Reliability Physics Symposium (IRPS), Pasadena, CA, USA, 17–21 April 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 4C-6-1–4C-6-10. [Google Scholar] [CrossRef]

- Diaz-Fortuny, J.; Sangani, D.; Saraza-Canflanca, P.; Bury, E.; Degraeve, R.; Kaczer, B. Improving the Tamper-Aware Odometer Concept by Enhancing Dynamic Stress Operation. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; IEEE: Piscataway, NJ, USA, 2023; pp. 1–9. [Google Scholar] [CrossRef]

- Sengupta, D.; Sapatnekar, S.S. Estimating Circuit Aging Due to BTI and HCI Using Ring-Oscillator-Based Sensors. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2017, 36, 1688–1701. [Google Scholar] [CrossRef]

- Kaczer, B.; Degraeve, R.; Rasras, M.; Van de Mieroop, K.; Roussel, P.J.; Groeseneken, G. Impact of MOSFET gate oxide breakdown on digital circuit operation and reliability. IEEE Trans. Electron Devices 2002, 49, 500–506. [Google Scholar] [CrossRef]

- Kerber, A.; Srinivasan, P.; Cimino, S.; Paliwoda, P.; Chandrashekhar, S.; Chbili, Z.; Uppal, S.; Ranjan, R.; Mahmud, M.-I.; Singh, D.; et al. Device reliability metric for end-of-life performance optimization based on circuit level assessment. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 2D-3.1–2D-3.5. [Google Scholar] [CrossRef]

- Nigam, T.; Paliwoda, P.; Wang, X.; Kerber, A. Addressing reliability challenges in advance nodes for commercial and automotive application. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 21.1.1–21.1.4. [Google Scholar] [CrossRef]

- Kerber, A.; Nigam, T.; Paliwoda, P.; Guarin, F. Reliability Characterization of Ring Oscillator Circuits for Advanced CMOS Technologies. IEEE Trans. Device Mater. Reliab. 2020, 20, 230–241. [Google Scholar] [CrossRef]

- Kerber, A.; Kliza, P.; Beckmeier, D.; Ravindranath, A.; Yuan, L.; Liu, Y.; Jungroth, O.W. Ring Oscillator Aging Characterization in Conventional CMOS Technologies. In Proceedings of the 2023 37th Symposium on Microelectronics Technology and Devices (SBMicro), Rio de Janeiro, Brazil, 28 August–1 September 2023; IEEE: Piscataway, NJ, USA, 2023; pp. 1–5. [Google Scholar] [CrossRef]

- Diaz-Fortuny, J.; Saraza-Canflanca, P.; Lofrano, M.; Bury, E.; Degraeve, R.; Kaczer, B. Towards Complete Recovery of Circuit Degradation by Annealing with On-Chip Heaters. IEEE Electron Device Lett. 2023, 44, 201–204. [Google Scholar] [CrossRef]

- Diaz-Fortuny, J.; Saraza-Canflanca, P.; Vandemaele, M.; Bury, E.; Degraeve, R.; Kaczer, B. Dedicated ICs for the Characterization of Variability and Aging Studies and their Use in Lightweight Security Applications: Invited paper. In Proceedings of the 2022 IEEE Latin American Electron Devices Conference (LAEDC), Cancun, Mexico, 4–6 July 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 1–4. [Google Scholar] [CrossRef]

- Diaz-Fortuny, J.; Martin-Martinez, J.; Rodriguez, R.; Nafria, M.; Castro-Lopez, R.; Roca, E.; Fernandez, F.; Barajas, E.; Aragones, X.; Mateo, D. A transistor array chip for the statistical characterization of process variability, RTN and BTI/CHC aging. In Proceedings of the 2017 14th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Appli-cations to Circuit Design (SMACD), Giardini Naxos, Italy, 12–15 June 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Diaz-Fortuny, J.; Martin-Martinez, J.; Rodriguez, R.; Castro-Lopez, R.; Roca, E.; Aragones, X.; Barajas, E.; Mateo, D.; Fernandez, F.V.; Nafria, M. A Versatile CMOS Transistor Array IC for the Statistical Characterization of Time-Zero Variability, RTN, BTI, and HCI. IEEE J. Solid-State Circuits 2019, 54, 476–488. [Google Scholar] [CrossRef]

- Diaz-Fortuny, J.; Saraza-Canflanca, P.; Romano-Molar, A.; Bury, E.; Degraeve, R.; Kaczer, B. Demonstration of Chip Overclock Detection by Employing Tamper-Aware Odometer Technology. In Proceedings of the 2024 IEEE International Reliability Physics Symposium (IRPS), Grapevine, TX, USA, 14–18 April 2024; IEEE: Piscataway, NJ, USA, 2024. [Google Scholar]

- Diaz-Fortuny, J.; Saraza-Canflanca, P.; Castro-Lopez, R.; Roca, E.; Martin-Martinez, J.; Rodriguez, R.; Fernandez, F.V.; Nafria, M. Flexible Setup for the Measurement of CMOS Time-Dependent Variability with Array-Based Integrated Circuits. IEEE Trans. Instrum. Meas. 2020, 69, 853–864. [Google Scholar] [CrossRef]

- Bury, E.; Kaczer, B.; Chuang, K.; Franco, J.; Weckx, P.; Chasin, A.; Simicic, M.; Linten, D.; Groeseneken, G. Statistical assessment of the full VG/VD degradation space using dedicated device arrays. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 2D-5.1–2D-5.6. [Google Scholar] [CrossRef]

- Xhafa, X.; Gungordu, A.D.; Erol, D.; Yavuz, Y.; Yelten, M.B. An Automated Setup for the Characterization of Time-Based Degradation Effects Including the Process Variability in 40-nm CMOS Transistors. IEEE Trans. Instrum. Meas. 2021, 70, 2005110. [Google Scholar] [CrossRef]

- Weckx, P.; Kaczer, B.; Chen, C.; Franco, J.; Bury, E.; Chanda, K.; Watt, J.; Roussel, P.J.; Catthoor, F.; Groeseneken, G. Characterization of time-dependent variability using 32k transistor arrays in an advanced HK/MG technology. In Proceedings of the 2015 IEEE International Reliability Physics Symposium, Monterey, CA, USA, 19–23 April 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 3B.1.1–3B.1.6. [Google Scholar] [CrossRef]

- Park, J.-Y.; Moon, D.-I.; Lee, G.-B.; Choi, Y.-K. Curing of Aged Gate Dielectric by the Self-Heating Effect in MOSFETs. IEEE Trans. Electron Devices 2020, 67, 777–788. [Google Scholar] [CrossRef]

- Aichinger, T.; Nelhiebel, M.; Grasser, T. On the temperature dependence of NBTI recovery. Microelectron. Reliab. 2008, 48, 1178–1184. [Google Scholar] [CrossRef]

- Han, J.-W.; Peterson, R.; Moon, D.-I.; Senesky, D.G.; Meyyappan, M. Monolithically Integrated Microheater for On-Chip Annealing of Oxide Defects. IEEE Electron Device Lett. 2017, 38, 831–834. [Google Scholar] [CrossRef]

- Franco, J.; Kaczer, B.; Groeseneken, G. Poly-Si heaters for ultra-fast local temperature control of on-wafer test structures. Microelectron. Eng. 2014, 114, 47–51. [Google Scholar] [CrossRef]

- Amor, S.; Kilchytska, V.; Flandre, D.; Galy, P. Trap Recovery by in-Situ Annealing in Fully-Depleted MOSFET with Active Silicide Resistor. IEEE Electron Device Lett. 2021, 42, 1085–1088. [Google Scholar] [CrossRef]

- Vandemaele, M.; Chuang, K.-H.; Bury, E.; Tyaginov, S.; Groeseneken, G.; Kaczer, B. The Influence of Gate Bias on the Anneal of Hot-Carrier Degradation. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 1–7. [Google Scholar] [CrossRef]

- de Jong, M.J.; Salm, C.; Schmitz, J. Towards understanding recovery of hot-carrier induced degradation. Microelectron. Reliab. 2018, 88–90, 147–151. [Google Scholar] [CrossRef]

- Ioannou, D.P.; Mittl, S.; Brochu, D. Burn-in stress induced BTI degradation and post-burn-in high temperature anneal (Bake) effects in advanced HKMG and oxynitride based CMOS ring oscillators. In Proceedings of the 2012 IEEE International Reliability Physics Symposium (IRPS), Anaheim, CA, USA, 15–19 April 2012; IEEE: Piscataway, NJ, USA, 2012; pp. 5C.2.1–5C.2.5. [Google Scholar] [CrossRef]

- Kobayashi, K.; Kishita, T.; Nakano, H.; Furuta, J.; Igarashi, M.; Kumashiro, S.; Yabuuchi, M.; Sakamoto, H. Ultra Long-term Measurement Results of BTI-induced Aging Degradation on 7-nm Ring Oscillators. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; IEEE: Piscataway, NJ, USA, 2023; pp. 1–7. [Google Scholar] [CrossRef]

- Igarashi, M.; Takazawa, Y.; Tsukamoto, Y.; Takeuchi, K.; Shibutani, K. NBTI/PBTI separated BTI monitor with 4.2x sensitivity by standard cell based unbalanced ring oscillator. In Proceedings of the 2017 IEEE Asian Solid-State Circuits Conference (A-SSCC), Seoul, Republic of Korea, 6–8 November 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 201–204. [Google Scholar] [CrossRef]

- Igarashi, M.; Takeuchi, K.; Okagaki, T.; Shibutani, K.; Matsushita, H.; Nii, K. An on-die digital aging monitor against HCI and xBTI in 16 nm Fin-FET bulk CMOS technology. In Proceedings of the ESSCIRC Conference 2015—41st European Solid-State Circuits Conference (ESSCIRC), Graz, Austria, 14–18 September 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 112–115. [Google Scholar] [CrossRef]

- Kim, Y.; Shim, H.; Jin, M.; Bae, J.; Liu, C.; Pae, S. Investigation of HCI effects in FinFET based ring oscillator circuits and IP blocks. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 4C-2.1–4C-2.4. [Google Scholar] [CrossRef]

- Kerber, A.; Wan, X.; Liu, Y.; Nigam, T. Fast Wafer-Level Stress-and-Sense Methodology for Characterization of Ring-Oscillator Degradation in Advanced CMOS Technologies. IEEE Trans. Electron Devices 2015, 62, 1427–1432. [Google Scholar] [CrossRef]

- Saraza-Canflanca, P.; Diaz-Fortuny, J.; Castro-Lopez, R.; Roca, E.; Martin-Martinez, J.; Rodriguez, R.; Nafria, M.; Fernandez, F.V. New method for the automated massive characterization of Bias Temperature Instability in CMOS transistors. In Proceedings of the 2019 Design, Automation & Test in Europe Conference & Exhibition (DATE), Florence, Italy, 25–29 March 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 150–155. [Google Scholar] [CrossRef]

- Diaz-Fortuny, J.; Martin-Martinez, J.; Rodriguez, R.; Nafria, M.; Castro-Lopez, R.; Roca, E.; Fernandez, F. TARS: A toolbox for statistical reliability modeling of CMOS devices. In Proceedings of the 2017 14th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Appli-cations to Circuit Design (SMACD), Giardini Naxos, Italy, 12–15 June 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Saraza-Canflanca, P.; Diaz-Fortuny, J.; Castro-Lopez, R.; Roca, E.; Martin-Martinez, J.; Rodriguez, R.; Nafria, M.; Fernandez, F. TiDeVa: A Toolbox for the Automated and Robust Analysis of Time-Dependent Variability at Transistor Level. In Proceedings of the 2019 16th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Appli-cations to Circuit Design (SMACD), Lausanne, Switzerland, 15–18 July 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 197–200. [Google Scholar] [CrossRef]

- Sangani, D.; Diaz-Fortuny, J.; Bury, E.; Kaczer, B.; Gielen, G. The Role of Mobility Degradation in the BTI-Induced RO Aging in a 28-nm Bulk CMOS Technology: (Student Paper). In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; IEEE: Piscataway, NJ, USA, 2023; pp. 1–6. [Google Scholar] [CrossRef]

- Sangani, D.; Diaz-Fortuny, J.; Bury, E.; Franco, J.; Kaczer, B.; Gielen, G. Modeling Analysis of BTI-Driven Degradation of a Ring Oscillator Designed in a 28-nm CMOS Technology. IEEE Trans. Device Mater. Reliab. 2023, 23, 346–354. [Google Scholar] [CrossRef]

- Pobegen, G.; Tyaginov, S.; Nelhiebel, M.; Grasser, T. Observation of Normally Distributed Energies for Interface Trap Recovery After Hot-Carrier Degradation. IEEE Electron Device Lett. 2013, 34, 939–941. [Google Scholar] [CrossRef]

- Islam, T.; Kim, J.; Kim, C.H.; Tipple, D.; Nelson, M.; Jin, R.; Jarrar, A. A Calibration-Free Synthesizable Odometer Featuring Automatic Frequency Dead Zone Escape and Start-up Glitch Removal. In Proceedings of the 2022 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 27–31 March 2022; IEEE: Piscataway, NJ, USA, 2022; pp. P2-1–P2-6. [Google Scholar] [CrossRef]

- Kaczer, B.; Grasser, T.; Roussel, J.; Martin-Martinez, J.; O’Connor, R.; O’Sullivan, B.J.; Groeseneken, G. Ubiquitous relaxation in BTI stressing—New evaluation and insights. In Proceedings of the 2008 IEEE International Reliability Physics Symposium, Phoenix, AZ, USA, 27 April–1 May 2008; IEEE: Piscataway, NJ, USA, 2008; pp. 20–27. [Google Scholar] [CrossRef]

- Grasser, T.; Kaczer, B.; Hehenberger, P.; Gos, W.; O’Connor, R.; Reisinger, H.; Gustin, W.; Schlunder, C. Simultaneous Extraction of Recoverable and Permanent Components Contributing to Bias-Temperature Instability. In Proceedings of the 2007 IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; IEEE: Piscataway, NJ, USA, 2007; pp. 801–804. [Google Scholar] [CrossRef]

| Target Devices | RO VDD = StressV VINT = 0 V | RO VDD = VINT = StressV |

|---|---|---|

| pMOS | VDS = VGS = −StressV | VDS = VGS = 0 V |

| nMOS | VDS = VGS = 0 V | VDS = VGS = StressV |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Diaz-Fortuny, J.; Saraza-Canflanca, P.; Bury, E.; Degraeve, R.; Kaczer, B. An In-Depth Study of Ring Oscillator Reliability under Accelerated Degradation and Annealing to Unveil Integrated Circuit Usage. Micromachines 2024, 15, 769. https://doi.org/10.3390/mi15060769

Diaz-Fortuny J, Saraza-Canflanca P, Bury E, Degraeve R, Kaczer B. An In-Depth Study of Ring Oscillator Reliability under Accelerated Degradation and Annealing to Unveil Integrated Circuit Usage. Micromachines. 2024; 15(6):769. https://doi.org/10.3390/mi15060769

Chicago/Turabian StyleDiaz-Fortuny, Javier, Pablo Saraza-Canflanca, Erik Bury, Robin Degraeve, and Ben Kaczer. 2024. "An In-Depth Study of Ring Oscillator Reliability under Accelerated Degradation and Annealing to Unveil Integrated Circuit Usage" Micromachines 15, no. 6: 769. https://doi.org/10.3390/mi15060769

APA StyleDiaz-Fortuny, J., Saraza-Canflanca, P., Bury, E., Degraeve, R., & Kaczer, B. (2024). An In-Depth Study of Ring Oscillator Reliability under Accelerated Degradation and Annealing to Unveil Integrated Circuit Usage. Micromachines, 15(6), 769. https://doi.org/10.3390/mi15060769