Efficient Modeling of Single Event Transient Effect with Limited Peak Current: Implications for Logic Circuits

Abstract

:1. Introduction

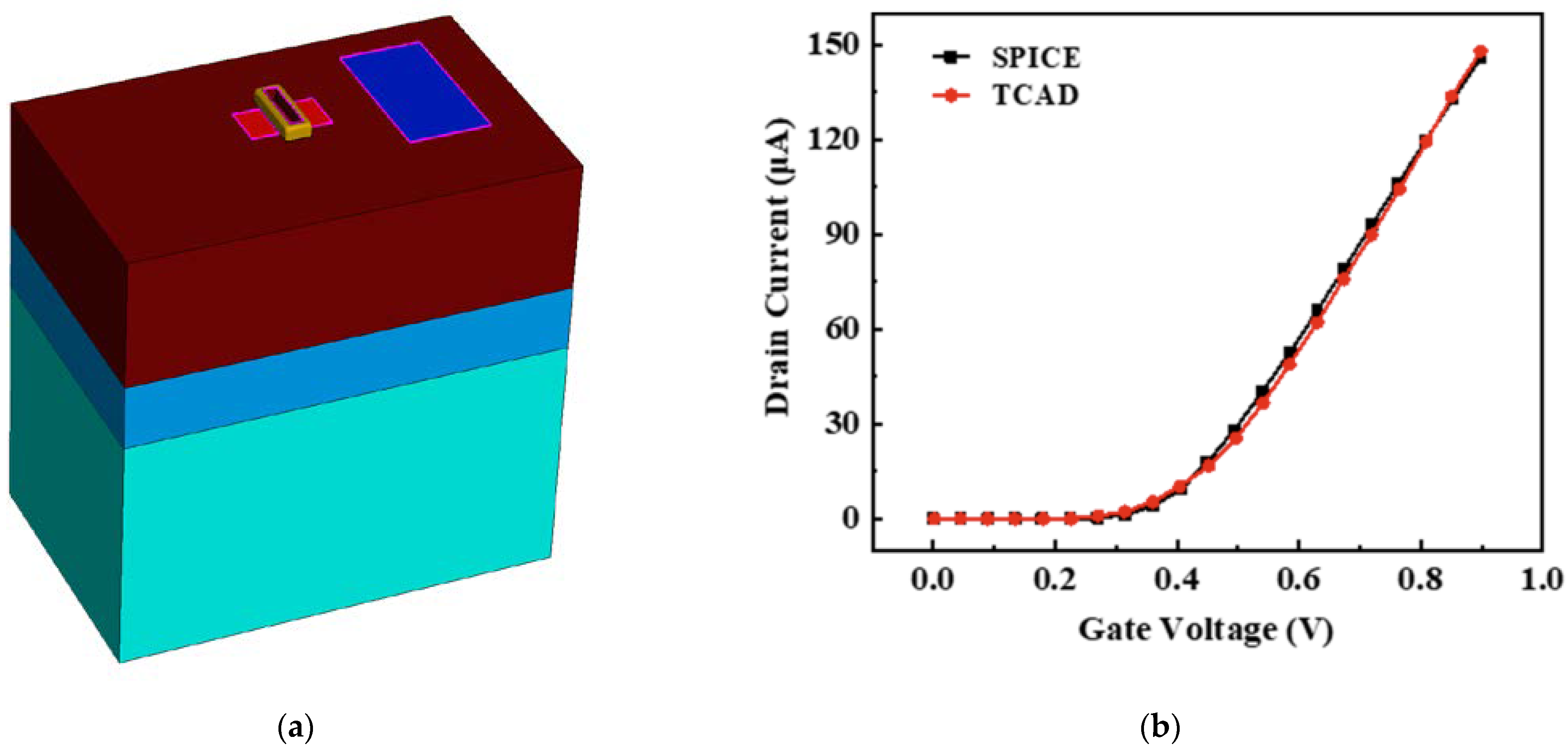

2. Background

2.1. Motivation

2.2. Limitation of the Models

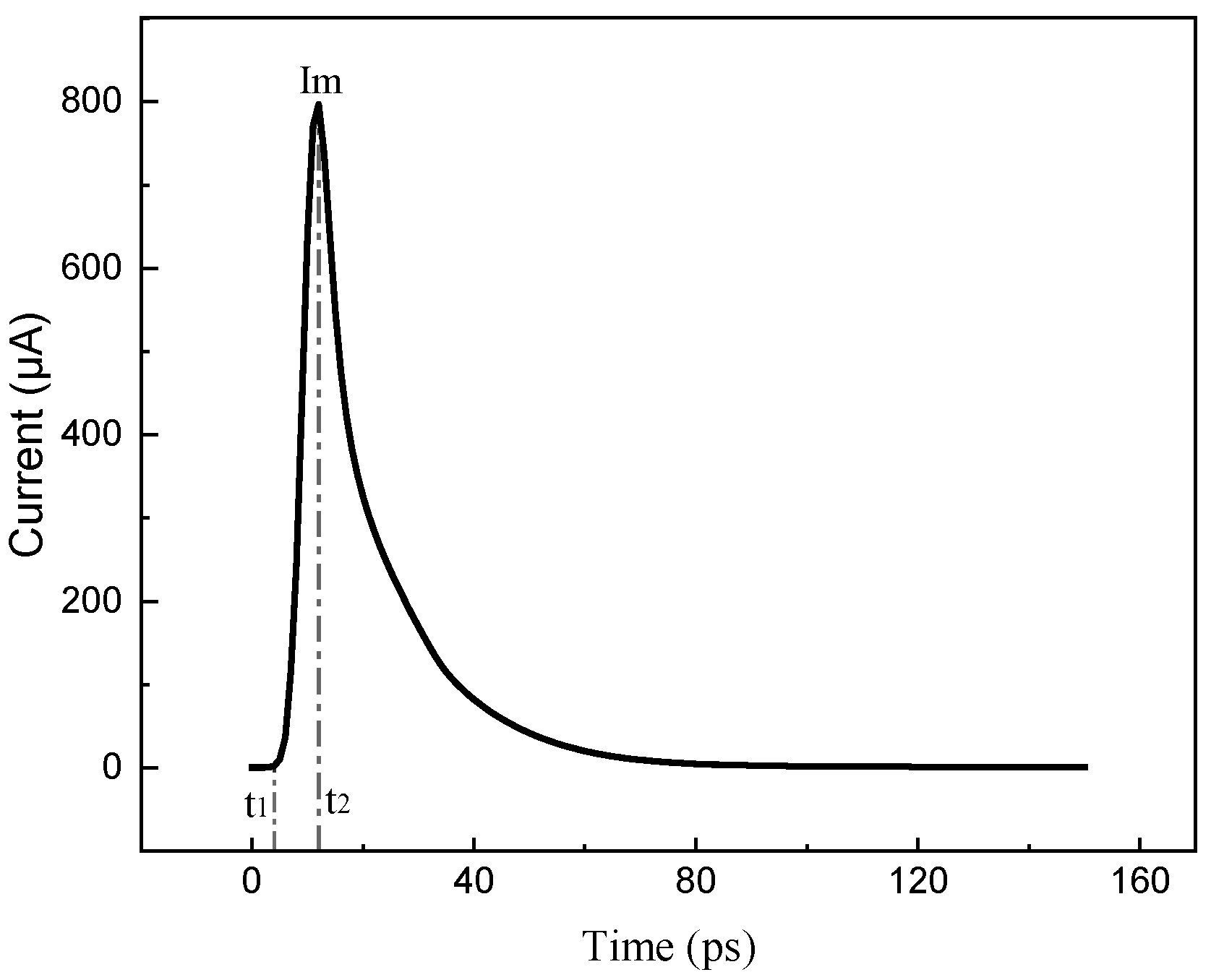

2.3. Transient Model

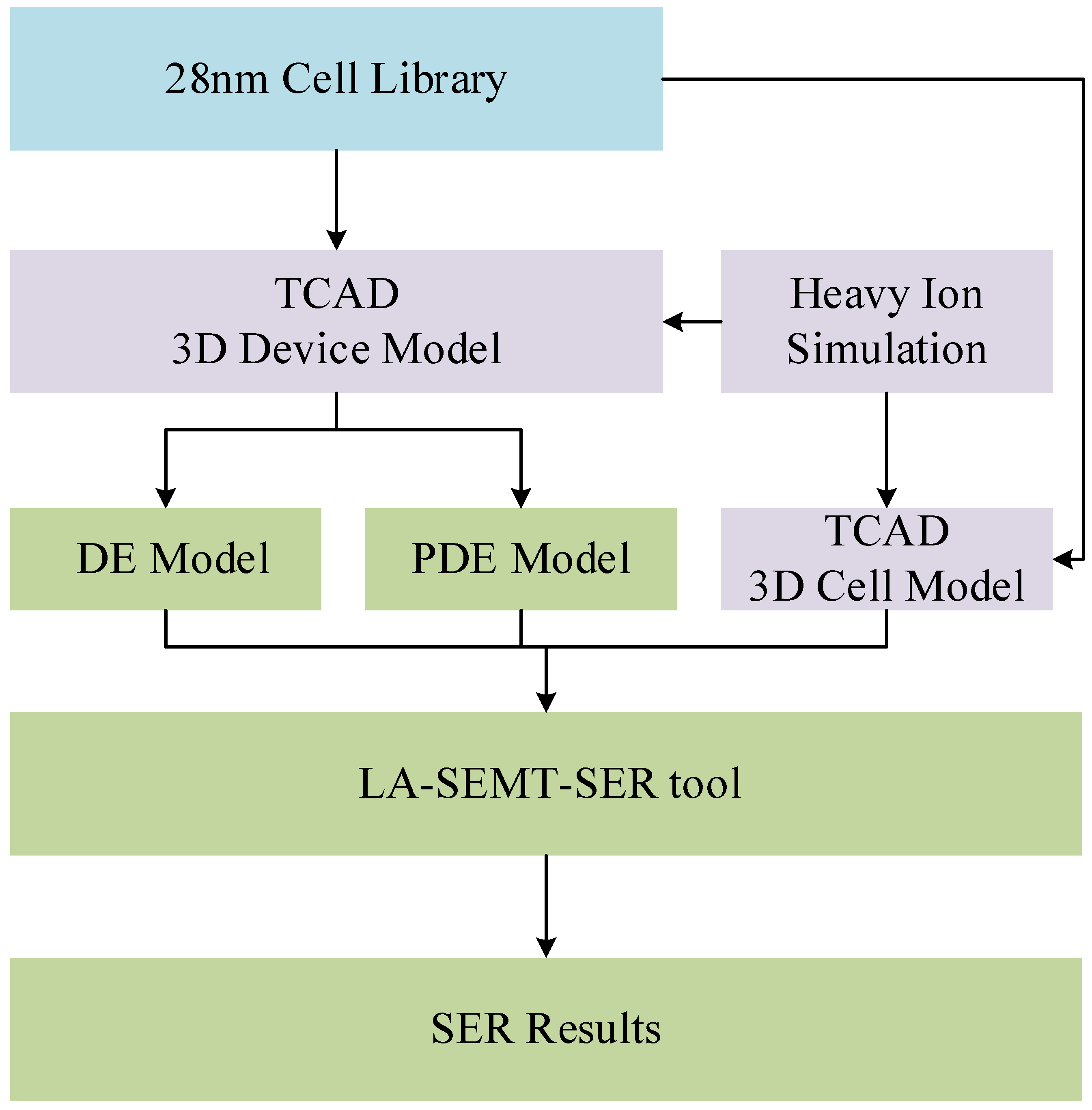

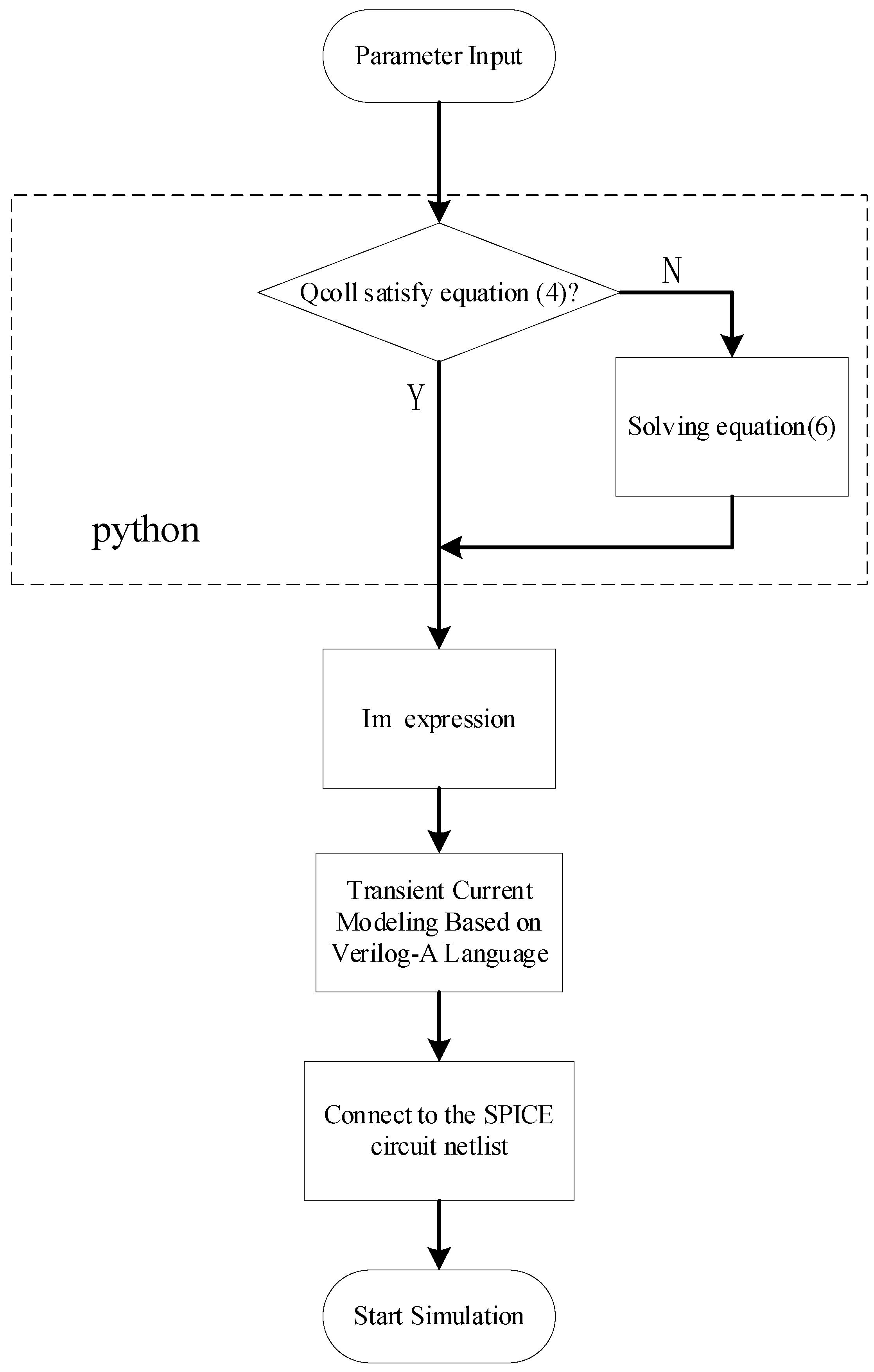

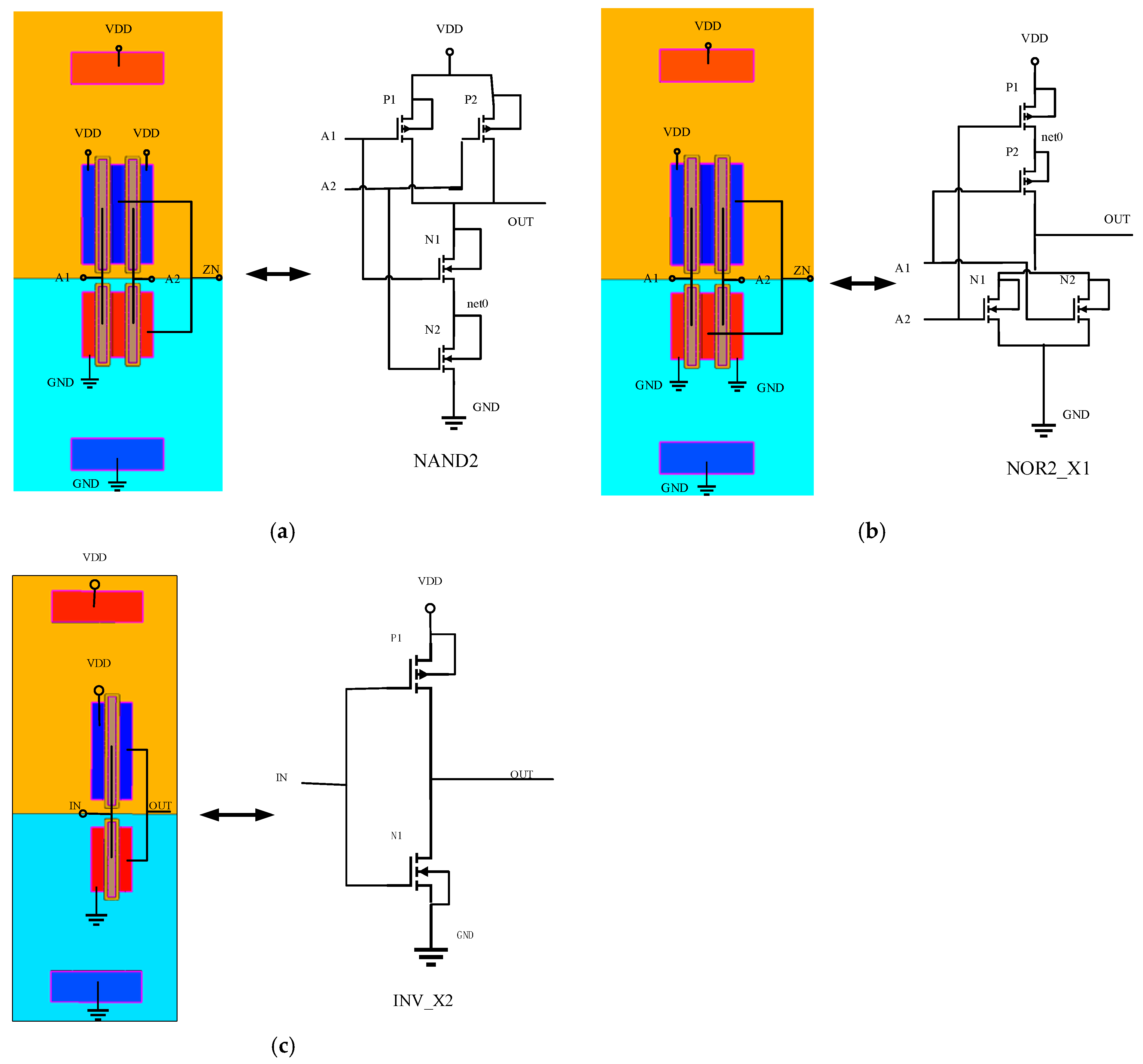

3. Injection of Transient Model Source

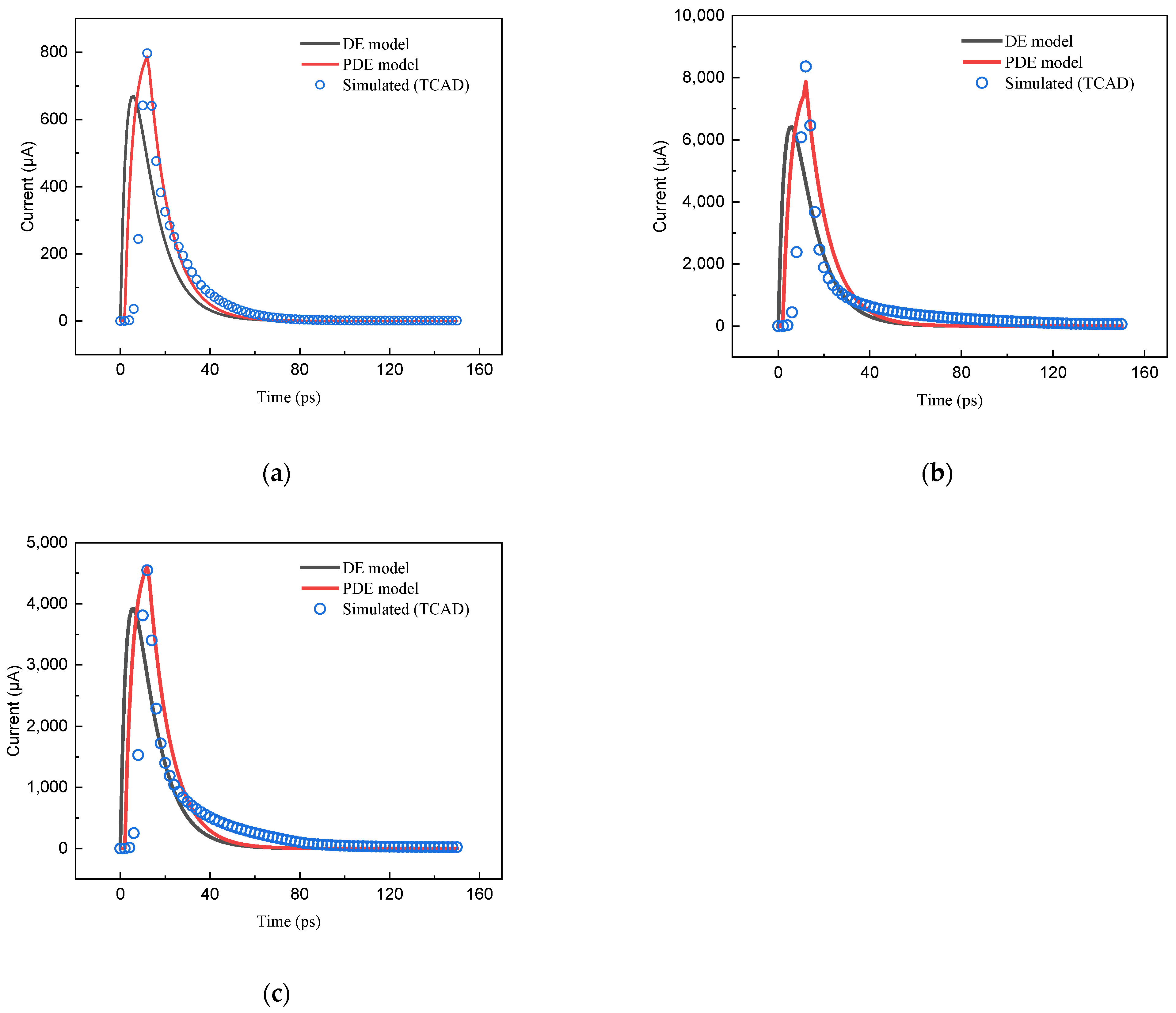

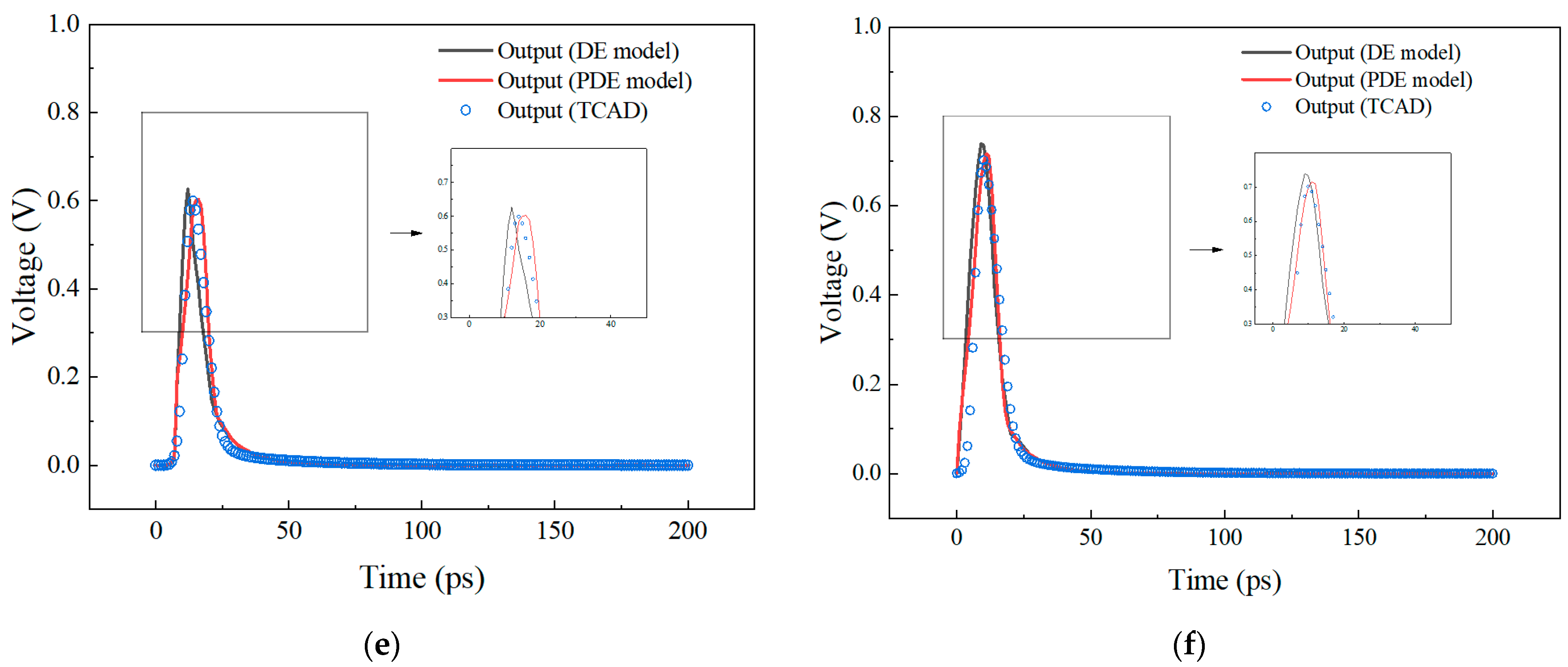

4. Validation to Experimental Data for CMOS Combinational Cells

5. Discussion

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Francis, A.M.; Turowski, M.; Holmes, J.A.; Mantooth, H.A. Efficient modeling of single event transients directly in compact device models. In Proceedings of the 2007 IEEE International Behavioral Modeling and Simulation Workshop, San Jose, CA, USA, 20–21 September 2007; pp. 73–77. [Google Scholar] [CrossRef]

- Chen, S.; Du, Y.; Liu, B.; Qin, J. Calculating the Soft Error Vulnerabilities of Combinational Circuits by Re-Considering the Sensitive Area. IEEE Trans. Nucl. Sci. 2014, 61, 646–653. [Google Scholar] [CrossRef]

- Mochizuki, A.; Onizawa, N.; Tamakoshi, A.; Hanyu, T. Multiple-event-transient soft-error gate-level simulator for harsh radiation environments. In Proceedings of the TENCON 2015—2015 IEEE Region 10 Conference, Macao, China, 1–4 November 2015; pp. 1–6. [Google Scholar] [CrossRef]

- Mo, Y.; Yue, S. An Efficient Design of Single Event Transients Tolerance for Logic Circuits. In Proceedings of the 4th IEEE International Symposium on Electronic Design, Test and Applications (Delta 2008), Hong Kong, China, 23–25 January 2008; pp. 125–128. [Google Scholar] [CrossRef]

- Guo, S.; Li, J.; Gui, P.; Ren, Y.; Chen, L.; Bhuva, B.L. Single-Event Transient Effect on a Self-Biased Ring-Oscillator PLL and an LC PLL Fabricated in SOS Technology. IEEE Trans. Nucl. Sci. 2013, 60, 4668–4672. [Google Scholar] [CrossRef]

- Gadlage, M.J.; Schrimpf, R.; Benedetto, J.; Eaton, P.; Mavis, D.; Sibley, M.; Avery, K.; Turflinger, T. Single event transient pulse widths in digital microcircuits. IEEE Trans. Nucl. Sci. 2004, 51, 3285–3290. [Google Scholar] [CrossRef]

- Ahlbin, J.R.; Atkinson, N.M.; Gadlage, M.J.; Gaspard, N.J.; Bhuva, B.L.; Loveless, T.D.; Zhang, E.X.; Chen, L.; Massengill, L.W. Influence of N-Well Contact Area on the Pulse Width of Single-Event Transients. IEEE Trans. Nucl. Sci. 2011, 58, 2585–2590. [Google Scholar] [CrossRef]

- Ahlbin, J.R.; Gadlage, M.J.; Ball, D.R.; Witulski, A.W.; Bhuva, B.L.; Reed, R.A.; Vizkelethy, G.; Massengill, L.W. The Effect of Layout Topology on Single-Event Transient Pulse Quenching in a 65 nm Bulk CMOS Process. IEEE Trans. Nucl. Sci. 2010, 57, 3380–3385. [Google Scholar] [CrossRef]

- Turowski, M.; Pellish, J.A.; Moen, K.A.; Raman, A.; Cressler, J.D.; Reed, R.A.; Niu, G. Reconciling 3-D Mixed-Mode Simulations and Measured Single-Event Transients in SiGe HBTs. IEEE Trans. Nucl. Sci. 2010, 57, 3342–3348. [Google Scholar] [CrossRef]

- Dodd, P.E.; Massengill, L.W. Basic mechanisms and modeling of single-event upset in digital microelectronics. IEEE Trans. Nucl. Sci. 2003, 50, 583–602. [Google Scholar] [CrossRef]

- Huang, P.; Chen, S.; Chen, J.; Liang, B.; Chi, Y. Heavy-Ion-Induced Charge Sharing Measurement with a Novel Uniform Vertical Inverter Chains (UniVIC) SEMT Test Structure. IEEE Trans. Nucl. Sci. 2015, 62, 3330–3338. [Google Scholar] [CrossRef]

- Evans, A.; Glorieux, M.; Alexandrescu, D.; Polo, C.B.; Ferlet-Cavrois, V. Single event multiple transient (SEMT) measurements in 65 nm bulk technology. In Proceedings of the 2016 16th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Bremen, Germany, 19–23 September 2016; pp. 1–6. [Google Scholar] [CrossRef]

- Liu, B.; Cai, L.; Li, C. An Analytical Model for Deposited Charge of Single Event Transient (SET) in FinFET. J. Electron. Test. 2024, 40, 159–169. [Google Scholar] [CrossRef]

- Amat, E.; Calomarde, A.; Canal, R.; Rubio, A. Optimization of FinFET-based gain cells for low power sub-VT embedded DRAMs. J. Low Power Electron. 2018, 14, 236–243. [Google Scholar] [CrossRef]

- Calomarde, A.; Amat, E.; Moll, F.; Vigara, J.; Rubio, A. SET and noise fault tolerant circuit design techniques: Application to 7 nm FinFET. Microelectron. Reliab. 2014, 54, 738–745. [Google Scholar] [CrossRef]

- Kauppila, J.S.; Sternberg, A.L.; Alles, M.L.; Francis, A.M.; Holmes, J.; Amusan, O.A.; Massengill, L.W. A Bias-Dependent Single-Event Compact Model Implemented Into BSIM4 and a 90 nm CMOS Process Design Kit. IEEE Trans. Nucl. Sci. 2009, 56, 3152–3157. [Google Scholar] [CrossRef]

- Messenger, G.C. Collection of Charge on Junction Nodes from Ion Tracks. IEEE Trans. Nucl. Sci. 1982, 29, 2024–2031. [Google Scholar] [CrossRef]

- Black, D.A.; Robinson, W.H.; Wilcox, I.Z.; Limbrick, D.B.; Black, J.D. Modeling of Single Event Transients with Dual Double-Exponential Current Sources: Implications for Logic Cell Characterization. IEEE Trans. Nucl. Sci. 2015, 62, 1540–1549. [Google Scholar] [CrossRef]

- Warren, K.M.; Sternberg, A.L.; Weller, R.A.; Baze, M.P.; Massengill, L.W.; Reed, R.A.; Mendenhall, M.H.; Schrimpf, R.D. Integrating Circuit Level Simulation and Monte-Carlo Radiation Transport Code for Single Event Upset Analysis in SEU Hardened Circuitry. IEEE Trans. Nucl. Sci. 2008, 55, 2886–2894. [Google Scholar] [CrossRef]

- Xu, C.-Q.; Liu, Y.; Weng, X.-D.; Li, Z.-B.; Yang, Y.-T. Single Event Transient Pulses Fault Injection Model based on LET for Circuit-Level Simulation. In Proceedings of the 2020 IEEE 15th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Kunming, China, 3–6 November 2020; pp. 1–3. [Google Scholar] [CrossRef]

- Kauppila, J.S.; Ball, D.R.; Maharrey, J.A.; Harrington, R.C.; Haeffner, T.D.; Sternberg, A.L.; Alles, M.L.; Massengill, L.W. A Bias-Dependent Single-Event-Enabled Compact Model for Bulk FinFET Technologies. IEEE Trans. Nucl. Sci. 2019, 66, 635–642. [Google Scholar] [CrossRef]

- Loveless, T.D.; Kauppila, J.S.; Jagannathan, S.; Ball, D.R.; Rowe, J.D.; Gaspard, N.J.; Atkinson, N.M.; Blaine, R.W.; Reece, T.R.; Ahlbin, J.R.; et al. On-Chip Measurement of Single-Event Transients in a 45 nm Silicon-on-Insulator Technology. IEEE Trans. Nucl. Sci. 2012, 59, 2748–2755. [Google Scholar] [CrossRef]

- DasGupta, S.; Witulski, A.F.; Bhuva, B.L.; Alles, M.L.; Reed, R.A.; Amusan, O.A.; Ahlbin, J.R.; Schrimpf, R.D.; Massengill, L.W. Effect of Well and Substrate Potential Modulation on Single Event Pulse Shape in Deep Submicron CMOS. IEEE Trans. Nucl. Sci. 2007, 54, 2407–2412. [Google Scholar] [CrossRef]

- Sayil, S.; Wang, J. Single-Event Soft Errors in CMOS Logic. IEEE Potentials 2012, 31, 15–22. [Google Scholar] [CrossRef]

- Dong, R.; Lu, H.; Yang, C.; Zhang, Y.; Yao, R.; Wang, Y.; Zhang, Y. A Method for Automatically Predicting the Radiation-Induced Vulnerability of Unit Integrated Circuits. Micromachines 2024, 15, 541. [Google Scholar] [CrossRef]

- Warren, K.M.; Weller, R.A.; Sierawski, B.D.; Reed, R.A.; Mendenhall, M.H.; Schrimpf, R.D.; Massengill, L.W.; Porter, M.E.; Wilkinson, J.D.; LaBel, K.A.; et al. Application of RADSAFE to Model the Single Event Upset Response of a 0.25 μm CMOS SRAM. IEEE Trans. Nucl. Sci. 2007, 54, 898–903. [Google Scholar] [CrossRef]

- Wrobel, F.; Iacconi, P. Parameterization of neutron-induced SER in bulk SRAMs from reverse Monte Carlo Simulations. IEEE Trans. Nucl. Sci. 2005, 52, 2313–2318. [Google Scholar] [CrossRef]

| Cell | Input | TCAD | SPICE |

|---|---|---|---|

| INV | 0 | 2.08 | 2.12 |

| 1 | 1.71 | 1.77 |

| Cells | TCAD (Golden) | DE Model (FIT) | Error | PDE Model (FIT) | Error |

|---|---|---|---|---|---|

| NAND2_X1 | 9.9628 | 10.1722 | 2.1% | 10.1646 | 2% |

| NOR2_X1 | 12.1850 | 13.3332 | 9.4% | 11.7606 | 3.4% |

| INV_X2 | 1.0451 | 1.1720 | 12.1% | 1.0142 | 2.9% |

| INV_X4 | 0.2641 | 0.3039 | 15.1% | 0.2595 | 1.7% |

| INV_X16 | 0.0128 | 0.0166 | 29.7% | 0.0116 | 9.4% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Y.; Lu, H.; Yang, C.; Zhang, Y.; Yao, R.; Dong, R.; Zhang, Y. Efficient Modeling of Single Event Transient Effect with Limited Peak Current: Implications for Logic Circuits. Micromachines 2024, 15, 885. https://doi.org/10.3390/mi15070885

Wang Y, Lu H, Yang C, Zhang Y, Yao R, Dong R, Zhang Y. Efficient Modeling of Single Event Transient Effect with Limited Peak Current: Implications for Logic Circuits. Micromachines. 2024; 15(7):885. https://doi.org/10.3390/mi15070885

Chicago/Turabian StyleWang, Yujian, Hongliang Lu, Caozhen Yang, Yutao Zhang, Ruxue Yao, Rui Dong, and Yuming Zhang. 2024. "Efficient Modeling of Single Event Transient Effect with Limited Peak Current: Implications for Logic Circuits" Micromachines 15, no. 7: 885. https://doi.org/10.3390/mi15070885