Reliability Simulation Analysis of TSV Structure in Silicon Interposer under Temperature Cycling

Abstract

:1. Introduction

2. Numerical Methods

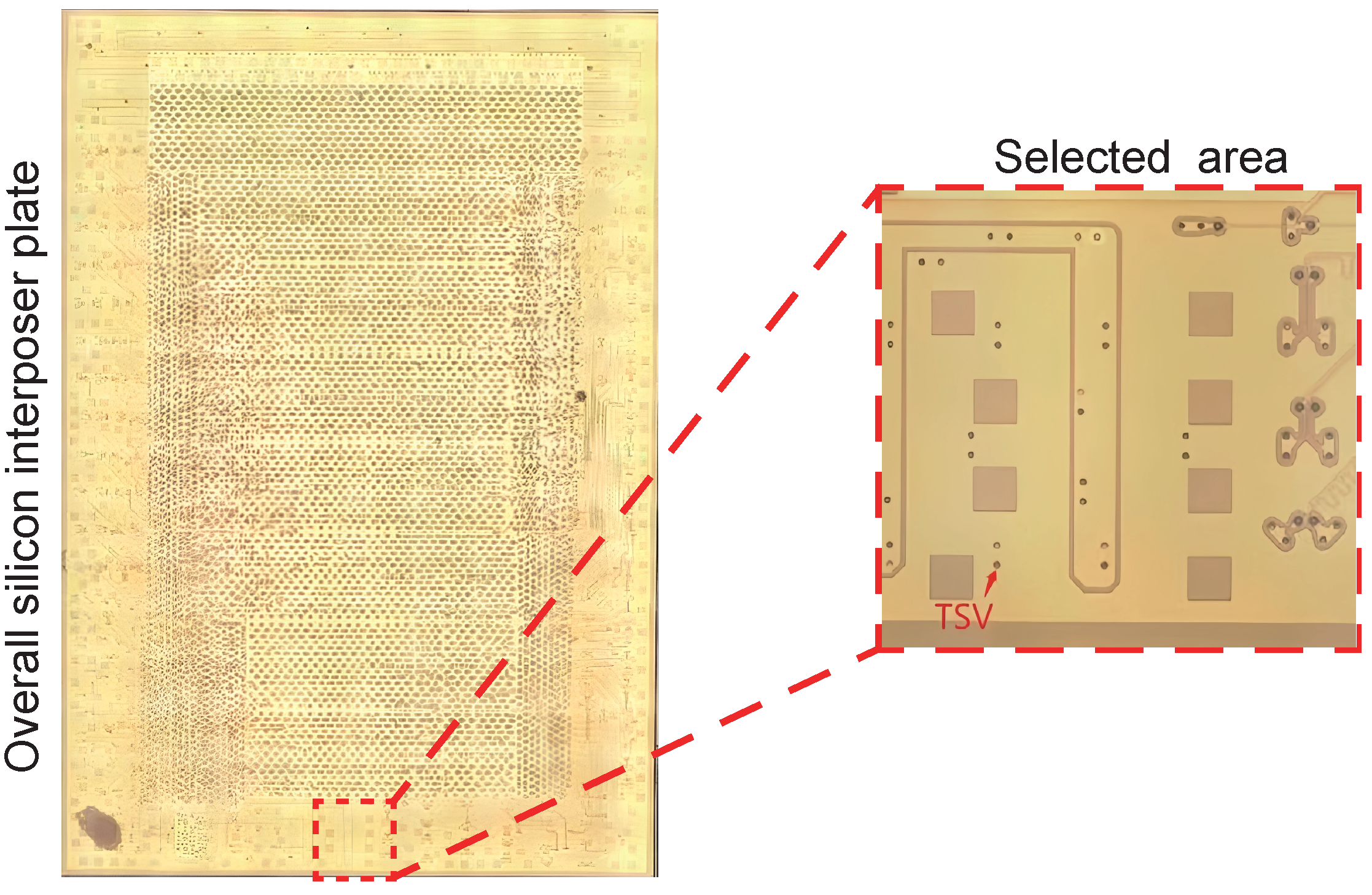

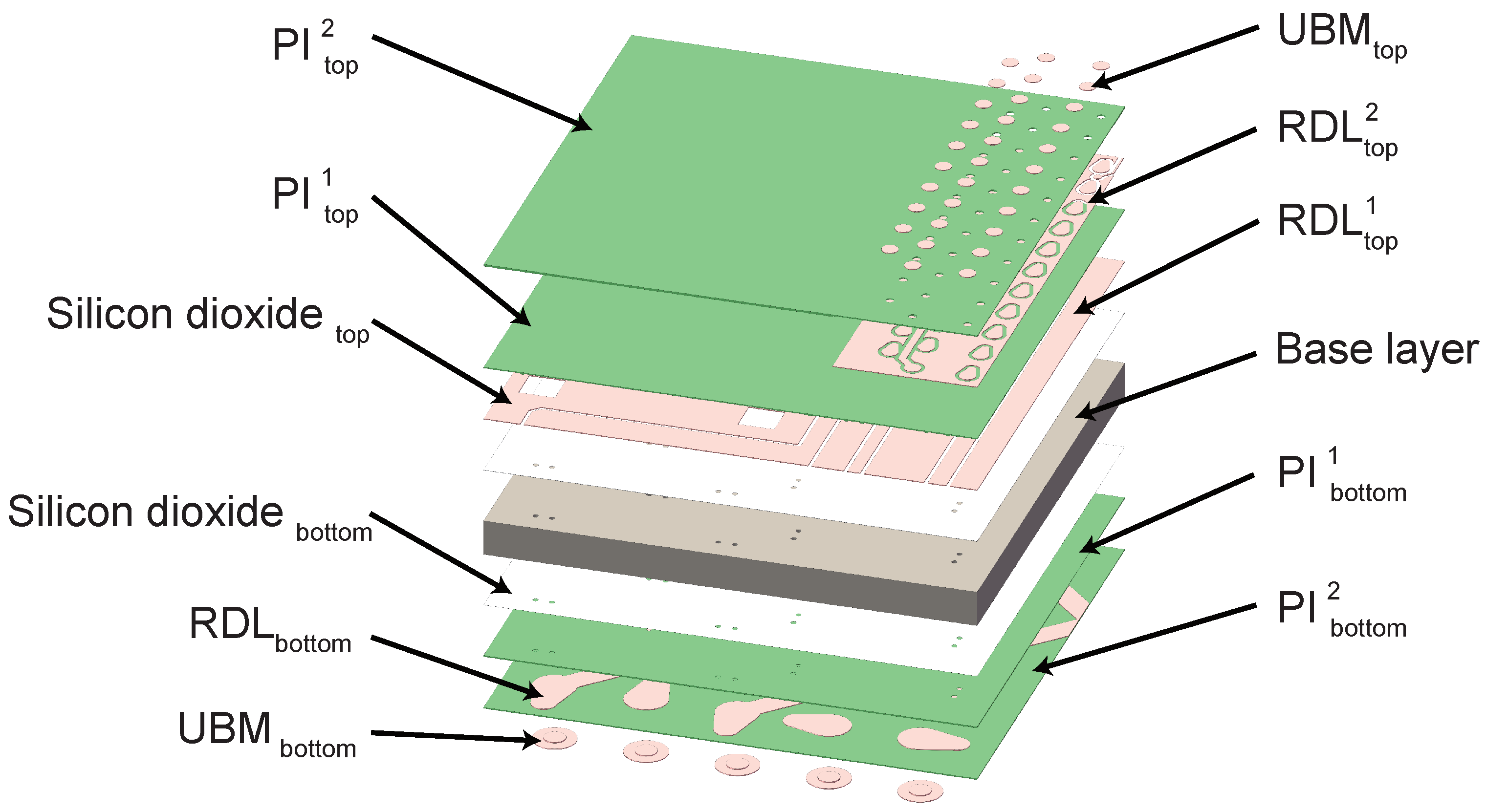

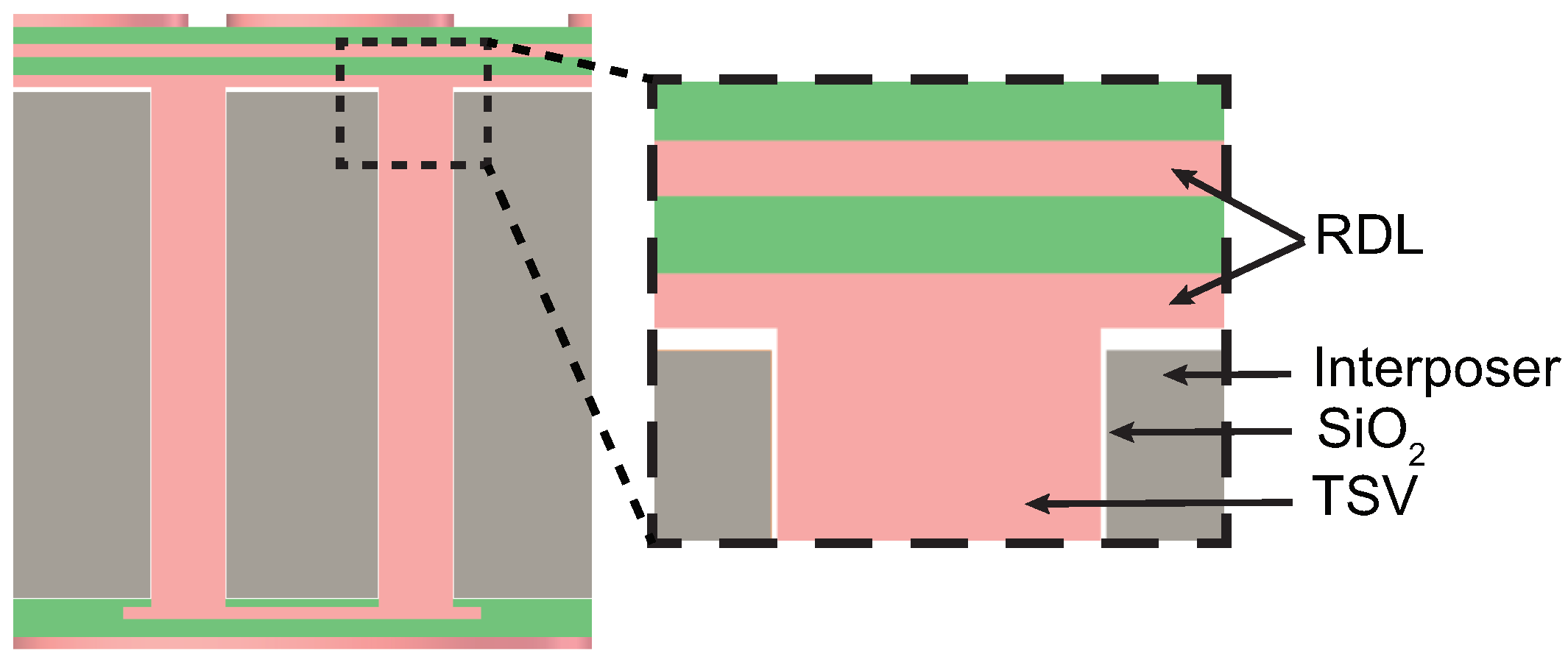

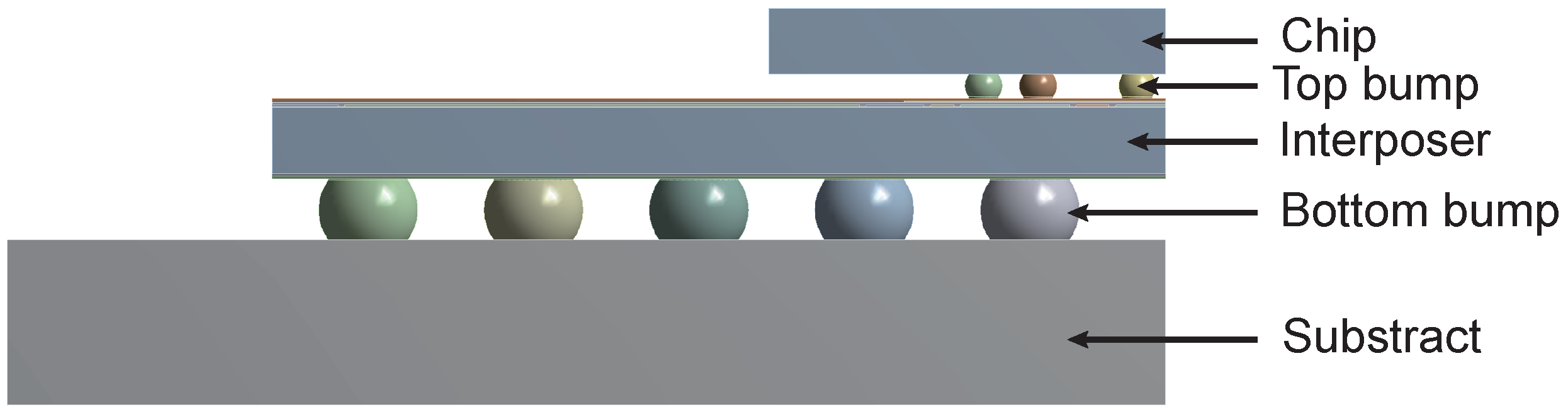

2.1. Model Geometry and Numerical Scheme

2.2. Material Parameters

2.3. Meshing of Models

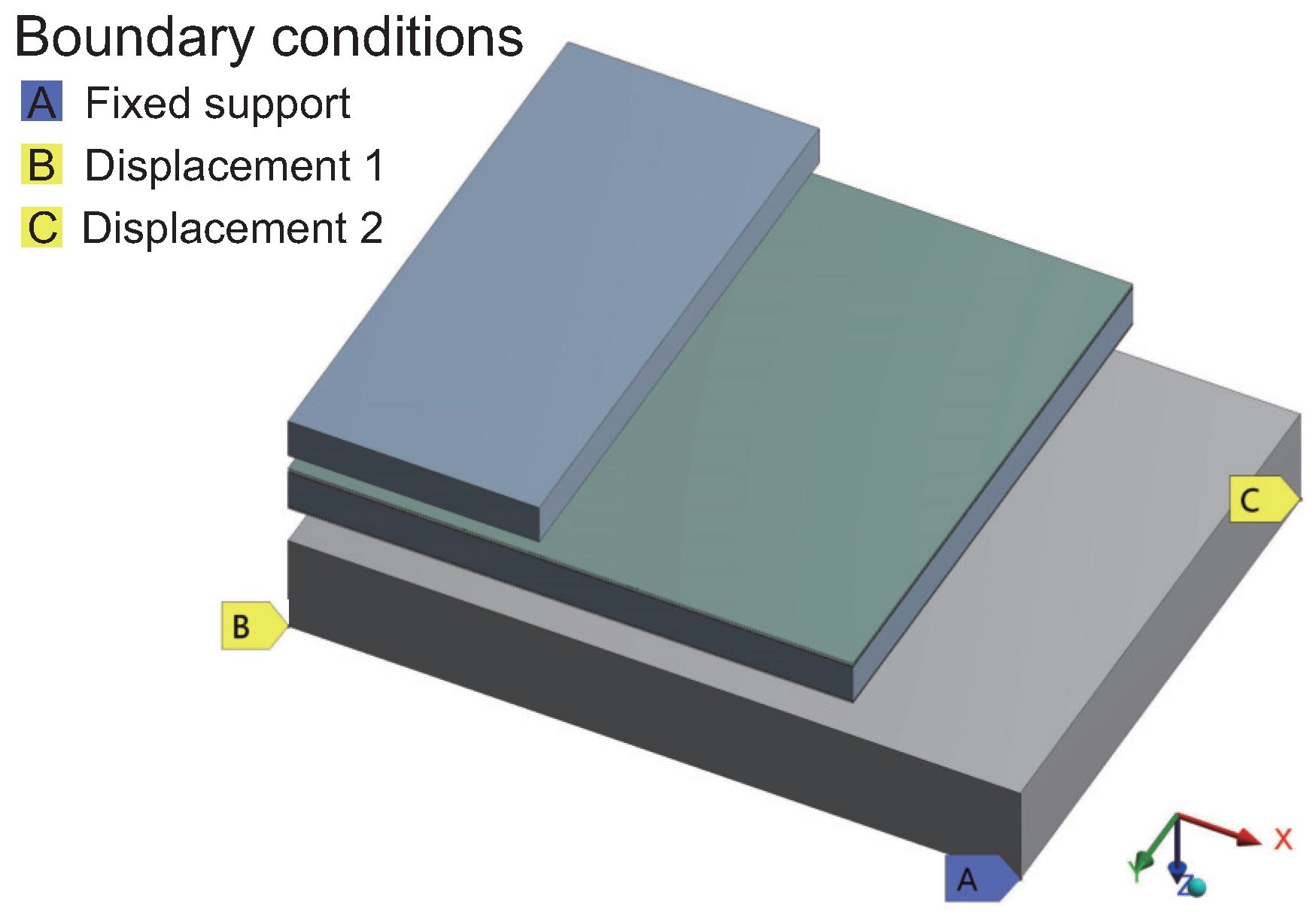

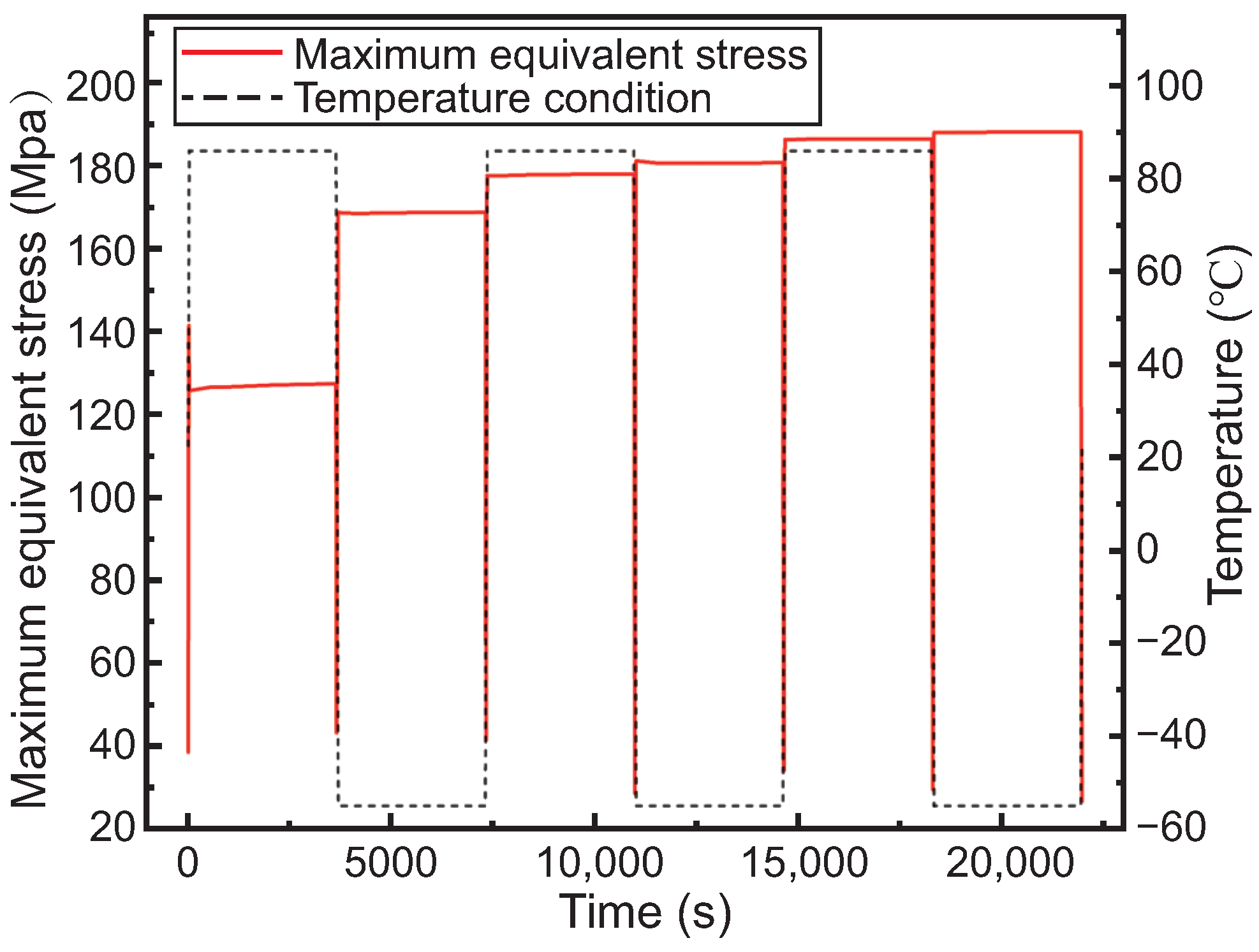

2.4. Boundary Conditions

3. Results and Discussion

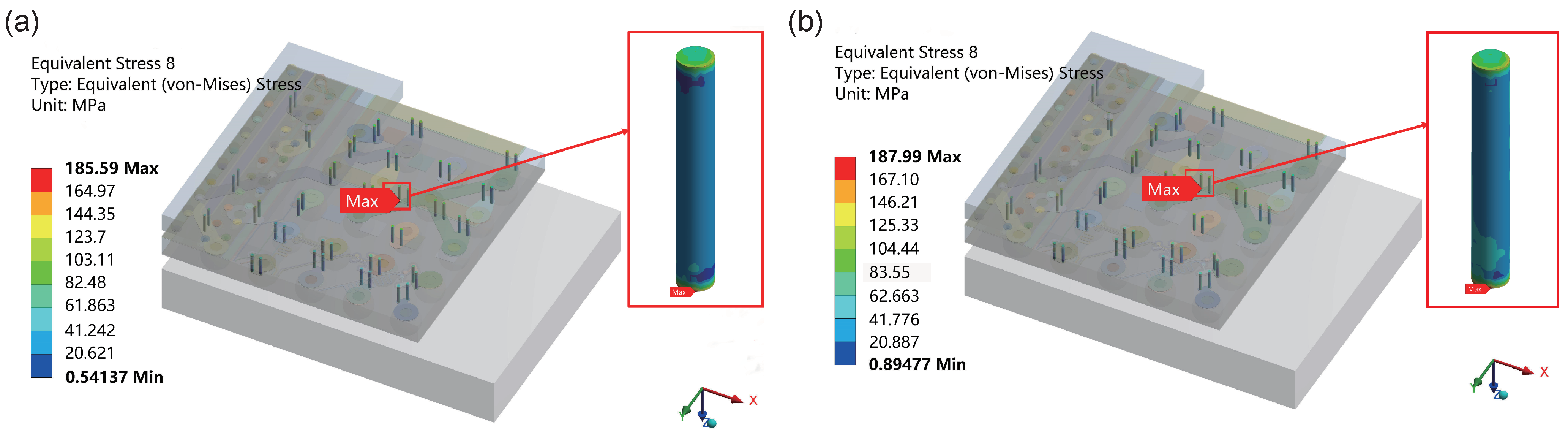

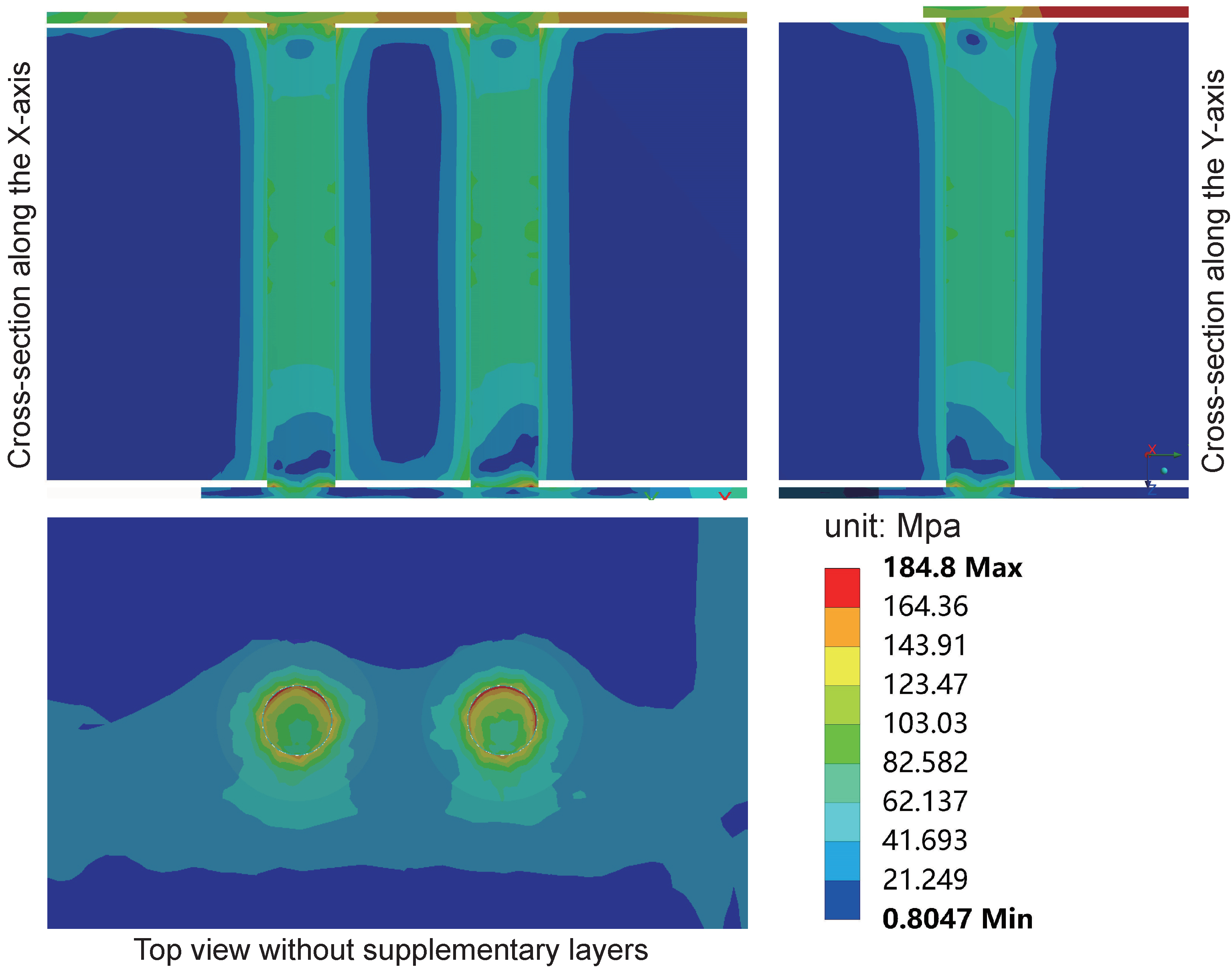

3.1. Stress Analysis of Overall Model

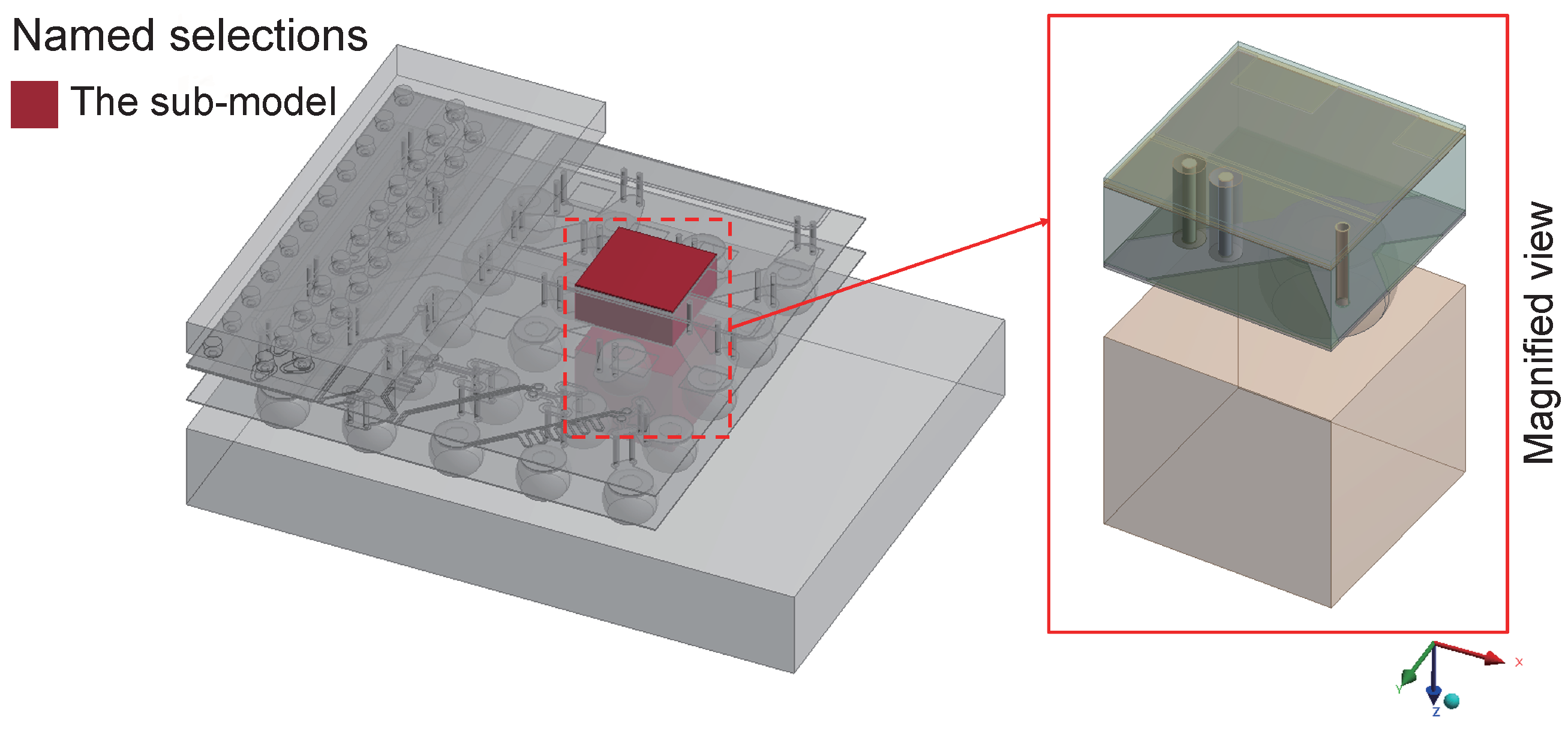

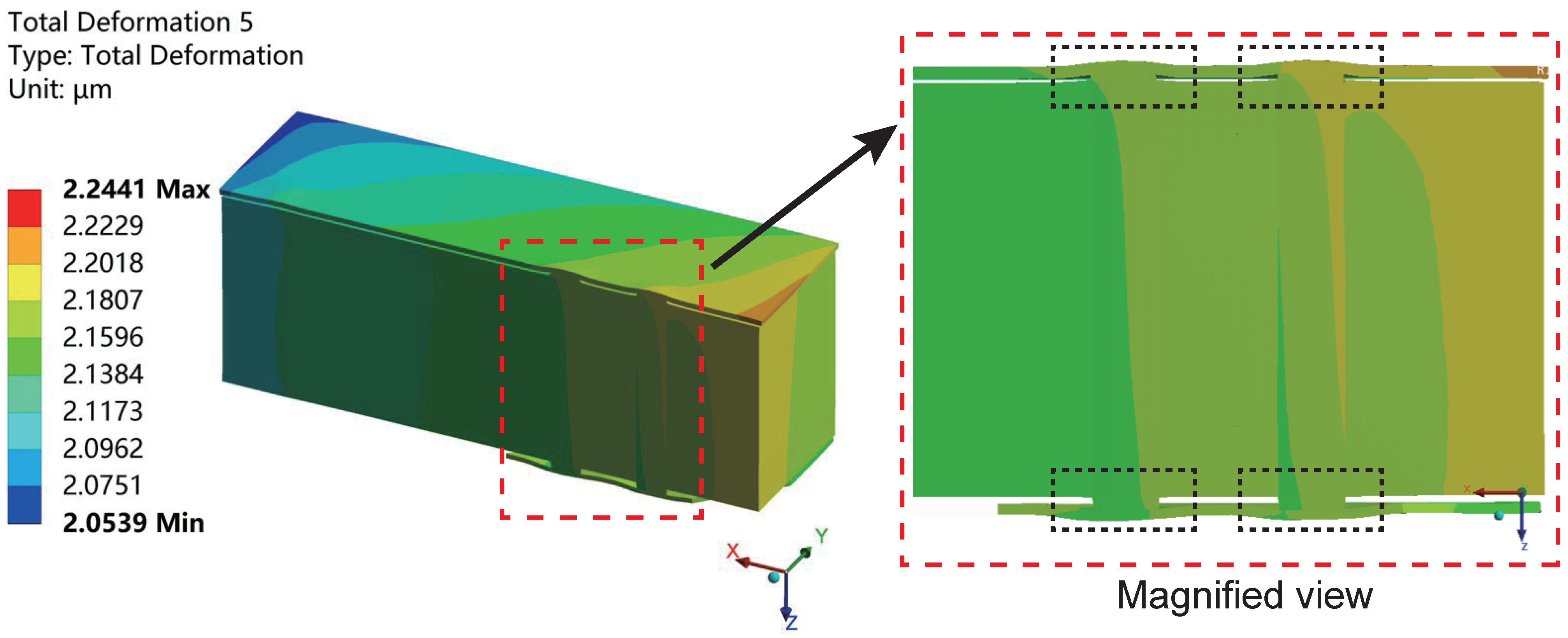

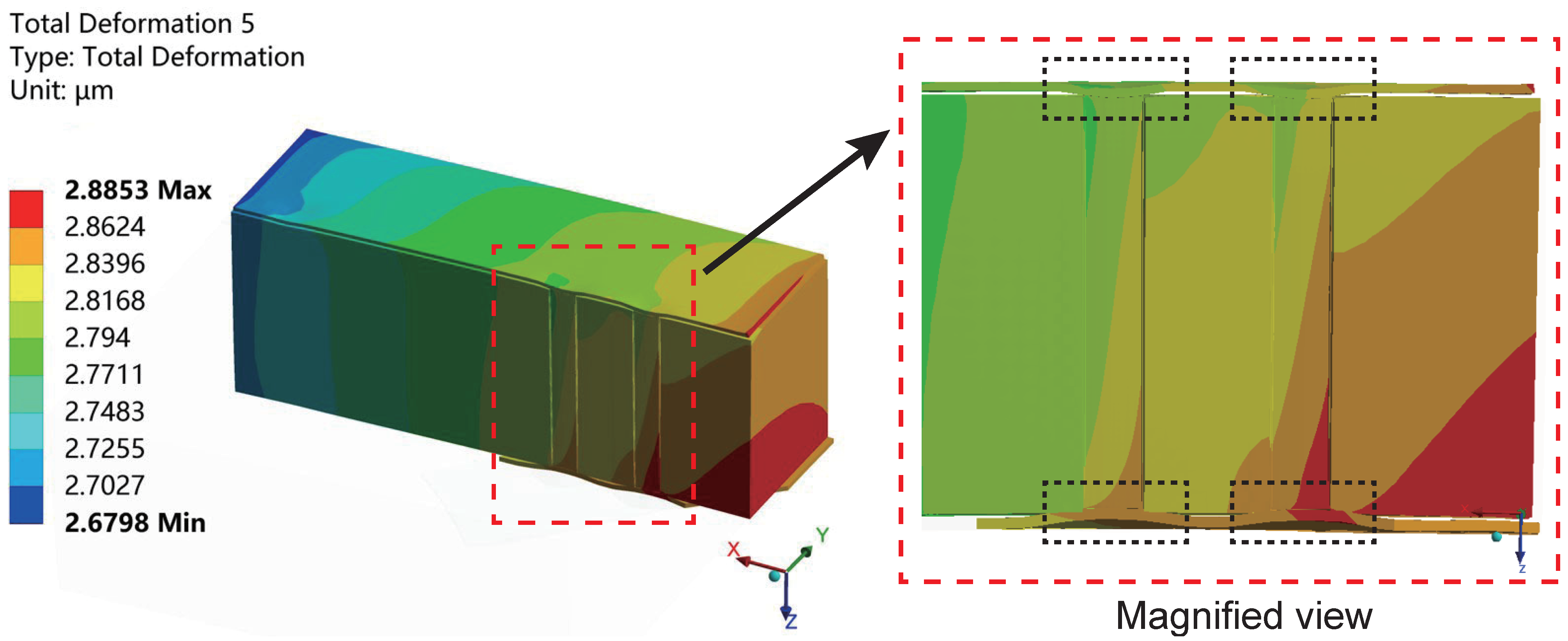

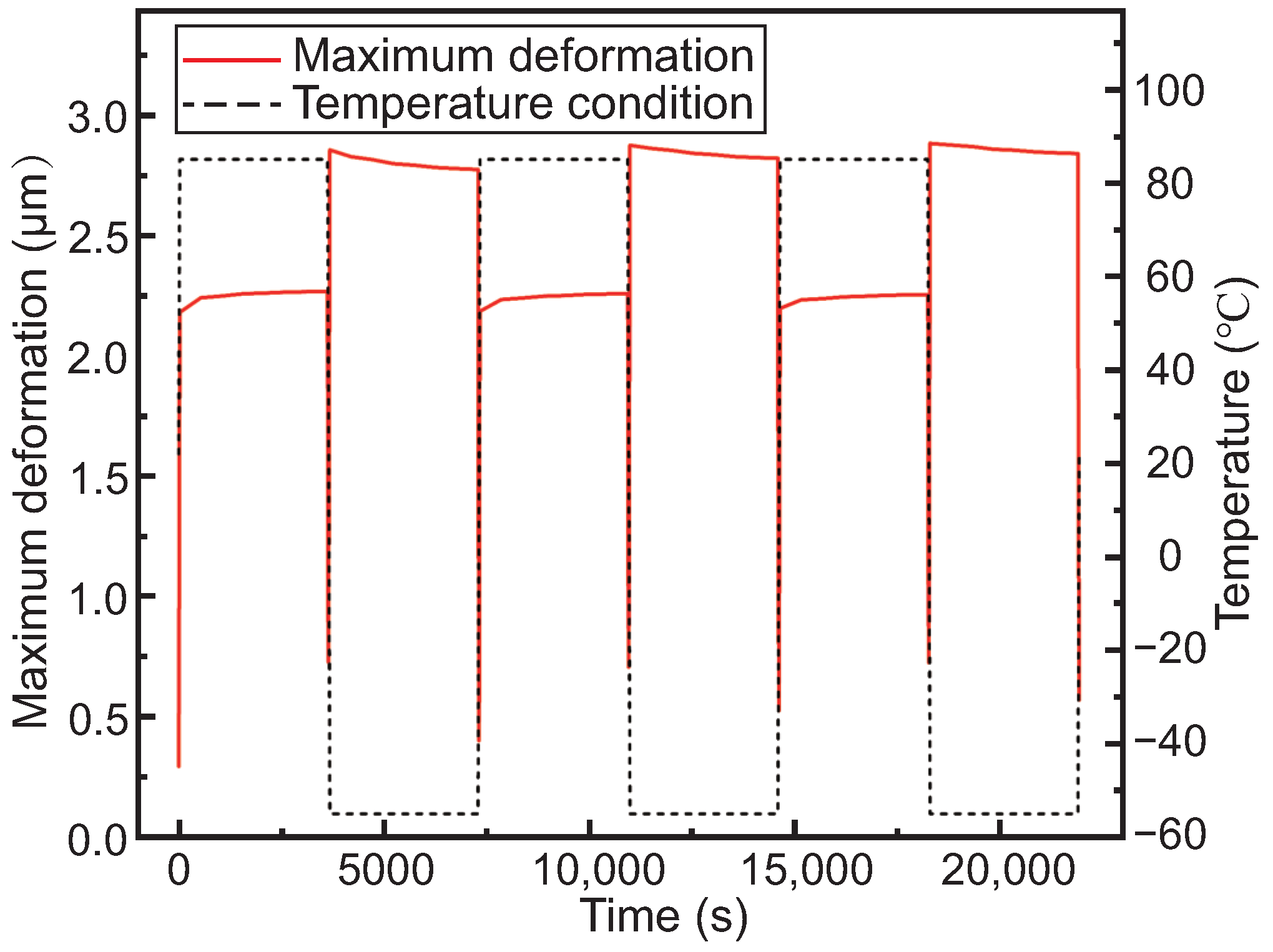

3.2. Deformation and Stress Analysis of Sub-Model

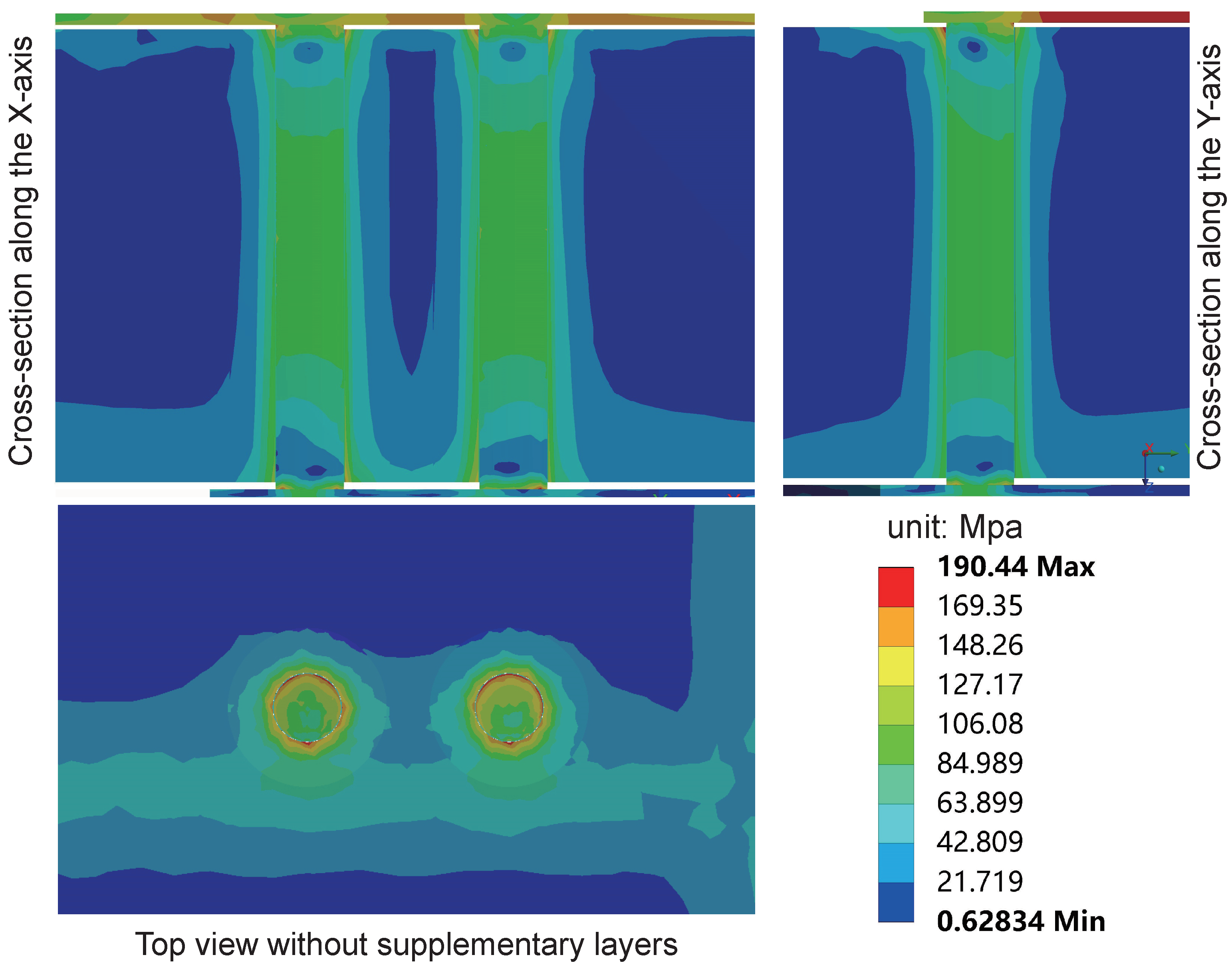

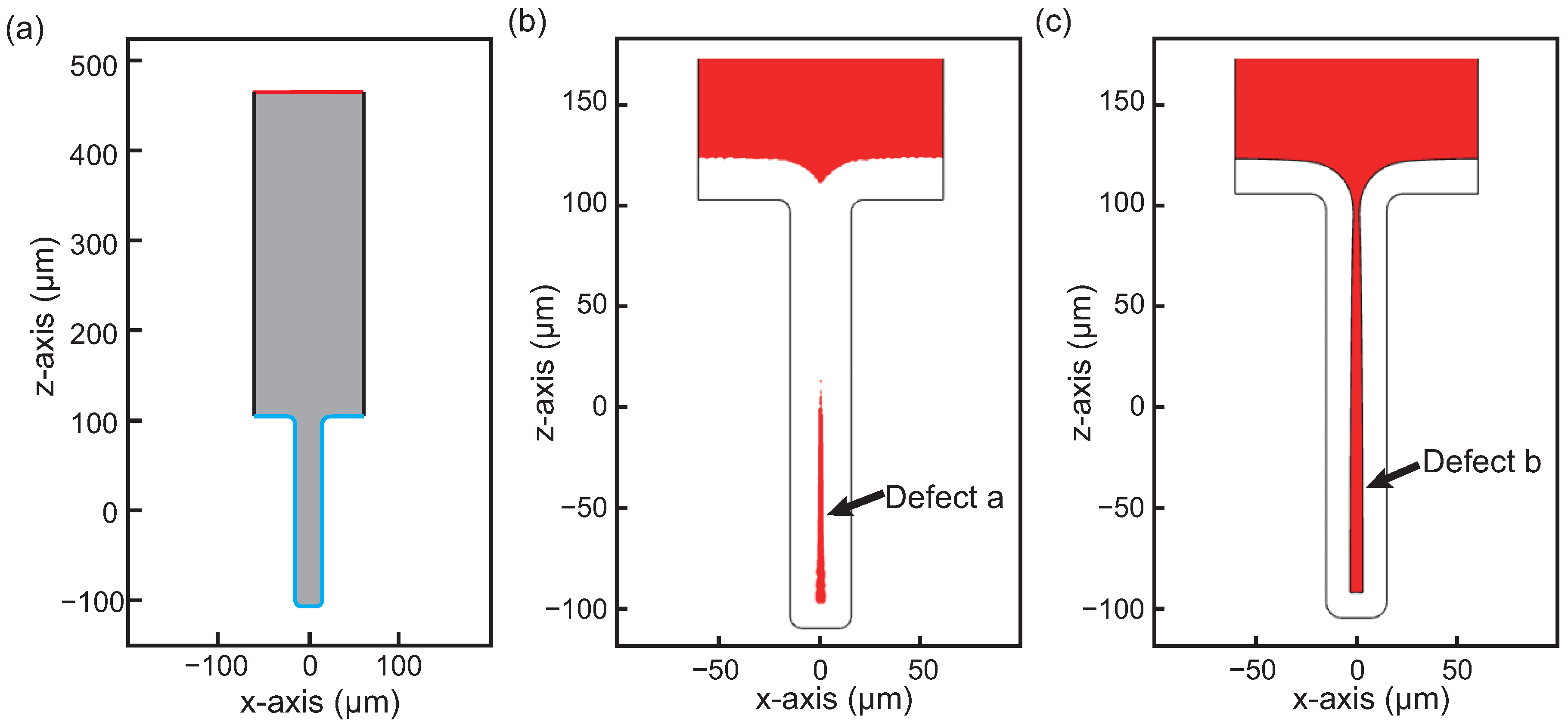

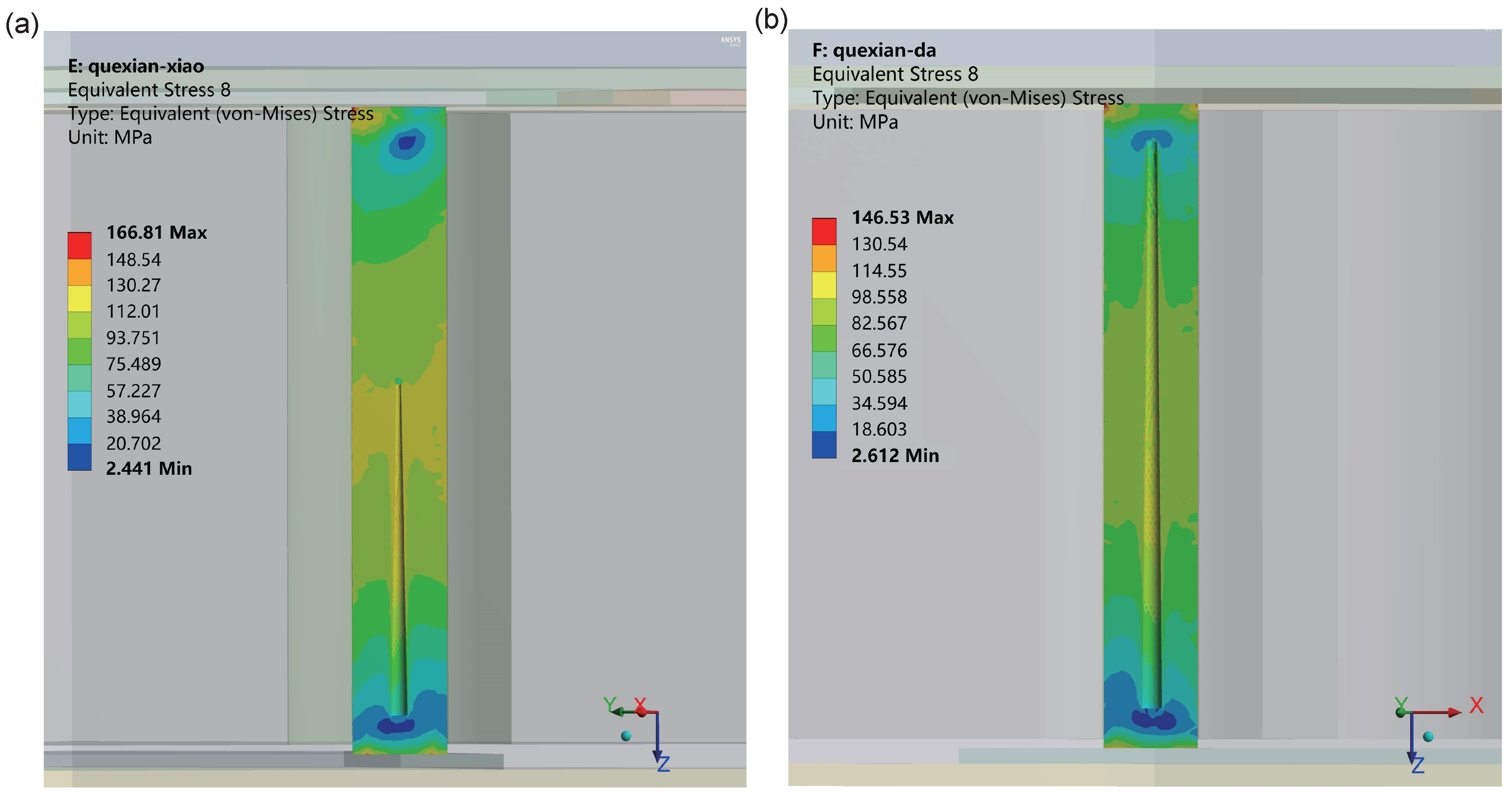

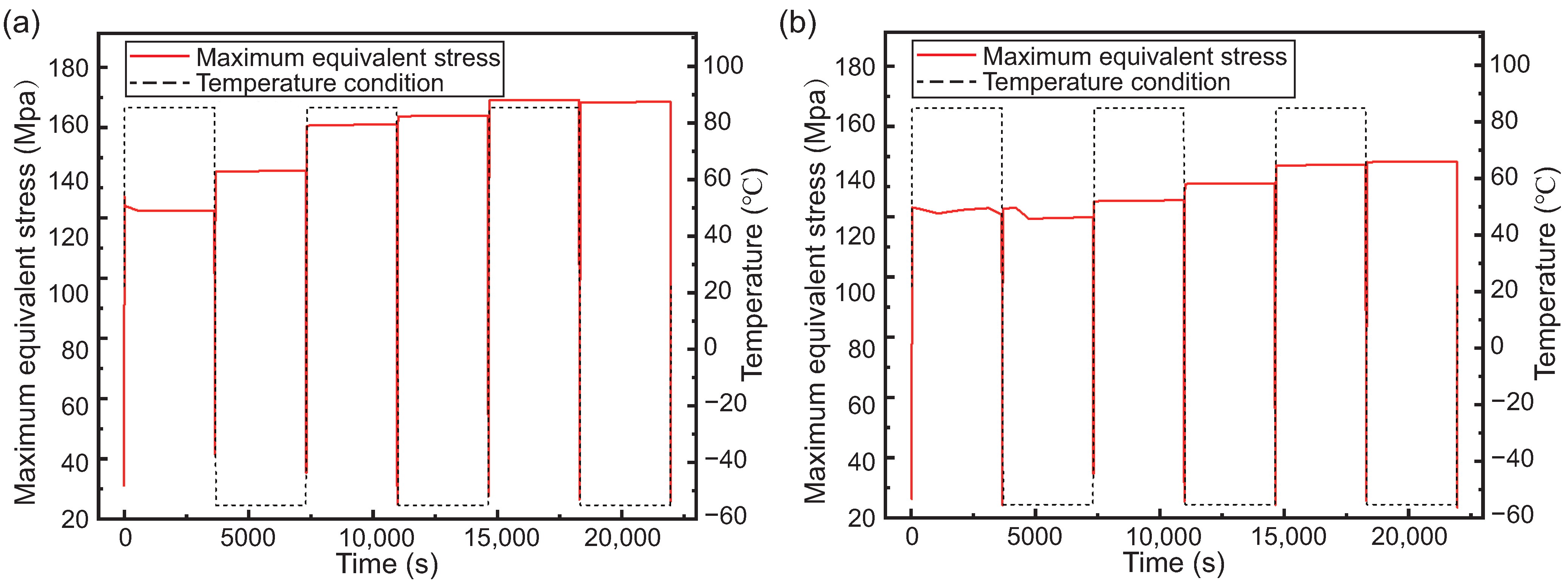

3.3. Stress Analysis of Copper Pillars Containing Defects in TSV

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Tu, K. Reliability challenges in 3D IC packaging technology. Microelectron. Reliab. 2011, 51, 517–523. [Google Scholar] [CrossRef]

- Kim, J.; Murali, G.; Park, H.; Qin, E.; Kwon, H.; Chekuri, V.C.K.; Rahman, N.M.; Dasari, N.; Singh, A.K.; Lee, M.; et al. Architecture, Chip, and Package Codesign Flow for Interposer-Based 2.5-D Chiplet Integration Enabling Heterogeneous IP Reuse. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2020, 28, 2424–2437. [Google Scholar] [CrossRef]

- Chen, K.N.; Tan, C.S. Integration schemes and enabling technologies for three-dimensional integrated circuits. IET Comput. Digit. Tech. 2011, 5, 160–168. [Google Scholar] [CrossRef]

- Saraswat, K.C. 3-D ICs: Motivation, performance analysis, technology and applications. In Proceedings of the 2010 17th IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits, Singapore, 5–9 July 2010; pp. 1–6. [Google Scholar] [CrossRef]

- Panigrahy, A.K.; Chen, K.N. Low Temperature Cu–Cu Bonding Technology in Three-Dimensional Integration: An Extensive Review. J. Electron. Packag. 2018, 140, 010801. [Google Scholar] [CrossRef]

- Han, C.F.; Guo, Y.Z.; Chung, C.J.; Shen, C.H.; Lin, J.F. Effects of SiO2 film thickness and operating temperature on thermally-induced failures in through-silicon-via structures. Microelectron. Reliab. 2018, 83, 1–13. [Google Scholar] [CrossRef]

- Liu, Y.; Yao, C.; Sun, F.; Fang, H. Numerical simulation of reliability of 2.5D/3D package interconnect structure under temperature cyclic load. Microelectron. Reliab. 2021, 125, 114343. [Google Scholar] [CrossRef]

- Ni, H.; He, L.; Chen, H.; Jia, X. Reliability simulation and life prediction of TSV under a thermoelectric coupling field in a 3D integrated circuit. J. Electron. Mater. 2021, 50, 3592–3602. [Google Scholar] [CrossRef]

- Shao, S.; Niu, Y.; Wang, J.; Liu, R.; Park, S.; Lee, H.; Refai-Ahmed, G.; Yip, L. Comprehensive Study on 2.5D Package Design for Board-Level Reliability in Thermal Cycling and Power Cycling. In Proceedings of the 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 9 May–1 June 2018; pp. 1668–1675. [Google Scholar] [CrossRef]

- Wang, G.; Ding, G.; Liu, R.; Xie, D.; Wu, Y.; Miao, X. Multi-objective optimization of a bidirectional-ribbed microchannel based on CFD and NSGA-II genetic algorithm. Int. J. Therm. Sci. 2022, 181, 107731. [Google Scholar] [CrossRef]

- Gururatana, S. Numerical Simulation of Micro-Channel Heat Sink with Dimpled Surfaces. Am. J. Appl. Sci. 2012, 9, 399–404. [Google Scholar]

- Lu, G.; Zhai, X. Analysis on heat transfer and pressure drop of a microchannel heat sink with dimples and vortex generators. Int. J. Therm. Sci. 2019, 145, 105986. [Google Scholar] [CrossRef]

- Wang, G.; Wang, Z.; Lai, L.; Xie, D.; Zhu, Y.; Ding, G.; Xu, Q. Experimental and numerical investigation of hydrothermal performance of a microchannel heat sink with pin fins. Case Stud. Therm. Eng. 2024, 60, 104631. [Google Scholar] [CrossRef]

- Xu, M.; Lu, H.; Gong, L.; Chai, J.C.; Duan, X. Parametric numerical study of the flow and heat transfer in microchannel with dimples. Int. Commun. Heat Mass Transf. 2016, 76, 348–357. [Google Scholar] [CrossRef]

- Frank, T.; Moreau, S.; Chappaz, C.; Leduc, P.; Arnaud, L.; Thuaire, A.; Chery, E.; Lorut, F.; Anghel, L.; Poupon, G. Reliability of TSV interconnects: Electromigration, thermal cycling, and impact on above metal level dielectric. Microelectron. Reliab. 2013, 53, 17–29. [Google Scholar] [CrossRef]

- Li, L.; Ton, P.; Nagar, M.; Chia, P. Reliability Challenges in 2.5D and 3D IC Integration. In Proceedings of the 2017 IEEE 67th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2017; pp. 1504–1509. [Google Scholar] [CrossRef]

- Kong, L.; Rudack, A.C.; Krueger, P.; Zschech, E.; Arkalgud, S.; Diebold, A. 3D-interconnect: Visualization of extrusion and voids induced in copper-filled through-silicon vias (TSVs) at various temperatures using X-ray microscopy. Microelectron. Eng. 2012, 92, 24–28. [Google Scholar] [CrossRef]

- De Wolf, I.; Croes, K.; Varela Pedreira, O.; Labie, R.; Redolfi, A.; Van De Peer, M.; Vanstreels, K.; Okoro, C.; Vandevelde, B.; Beyne, E. Cu pumping in TSVs: Effect of pre-CMP thermal budget. Microelectron. Reliab. 2011, 51, 1856–1859. [Google Scholar] [CrossRef]

- Liu, X.; Thadesar, P.A.; Taylor, C.L.; Kunz, M.; Tamura, N.; Bakir, M.S.; Sitaraman, S.K. Experimental Stress Characterization and Numerical Simulation for Copper Pumping Analysis of Through-Silicon Vias. IEEE Trans. Compon. Packag. Manuf. Technol. 2016, 6, 993–999. [Google Scholar] [CrossRef]

- Lu, K.H.; Zhang, X.; Ryu, S.K.; Im, J.; Huang, R.; Ho, P.S. Thermo-mechanical reliability of 3-D ICs containing through silicon vias. In Proceedings of the 2009 59th Electronic Components and Technology Conference, San Diego, CA, USA, 26–29 May 2009; pp. 630–634. [Google Scholar] [CrossRef]

- Liu, Z.; Jiang, H.; Zhu, Z.; Chen, L.; Sun, Q.; Sun, Y.; Zhang, D.W. Thermal–Mechanical and Signal Reliability of a New Differentiated TSV. IEEE Trans. Electron Devices 2022, 69, 5766–5772. [Google Scholar] [CrossRef]

- Qu, C.; Dai, R.; Zheng, J.; Hu, Y.; Zhang, J. Thermal and mechanical reliability of thermal through-silicon vias in three-dimensional integrated circuits. Microelectron. Reliab. 2023, 143, 114952. [Google Scholar] [CrossRef]

- Liu, X.; Chen, Q.; Sundaram, V.; Simmons-Matthews, M.; Wachtler, K.P.; Tummala, R.R.; Sitaraman, S.K. Thermo-mechanical behavior of through silicon vias in a 3D integrated package with inter-chip microbumps. In Proceedings of the 2011 IEEE 61st Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 31 May–3 June 2011; pp. 1190–1195. [Google Scholar] [CrossRef]

- Wang, F.; Zhao, Z.; Nie, N.; Wang, F.; Zhu, W. Dynamic through-silicon-via filling process using copper electrochemical deposition at different current densities. Sci. Rep. 2017, 7, 46639. [Google Scholar] [CrossRef]

- Beyne, E. Reliable Via-Middle Copper Through-Silicon Via Technology for 3-D Integration. IEEE Trans. Compon. Packag. Manuf. Technol. 2016, 6, 983–992. [Google Scholar] [CrossRef]

- Le, Y. TSV Filling with Copper Electro-deposition by Using Sodium 3-[[(dimethylamino) thioxomethyl] thio] Propane Sulphonate. J. Phys. Conf. Ser. 2023, 2566, 012019. [Google Scholar] [CrossRef]

- Zhang, Y.; Ding, G.; Wang, H.; Cheng, P.; Liu, R. Optimization of innovative approaches to the shortening of filling times in 3D integrated through-silicon vias (TSVs). J. Micromech. Microeng. 2015, 25, 045009. [Google Scholar] [CrossRef]

- Zhu, Q.S.; Zhang, X.; Liu, C.Z.; Liu, H.Y. Effect of Reverse Pulse on Additives Adsorption and Copper Filling for Through Silicon Via. J. Electrochem. Soc. 2018, 166, D3006. [Google Scholar] [CrossRef]

- Zhang, Y.; Sun, Y.; Ding, G.; Wang, Y.; Wang, H.; Cheng, P. Numerical Simulation and Mechanism Analysis of Through-Silicon Via (TSV) Filling Using an Arbitrary Lagrange-Eulerian (ALE) Method. J. Electrochem. Soc. 2015, 162, D540. [Google Scholar] [CrossRef]

| Structure | Layer’s Number | Layer’s Name | Material | Thickness |

|---|---|---|---|---|

| Top | First | Top silicon dioxide | SiO2 | 2 m |

| Second | Top RDL1 | Cu | 5 m | |

| Third | Top PI1 | PI | 7 m | |

| Forth | Top RDL2 | Cu | 5 m | |

| Fifth | Top PI1 | PI | 7 m | |

| Sixth | Top UBM | Cu | Thickness: 5 m Diameter: 90 m | |

| Middle | — | Base layer | Si | 200 m |

| Bottom | First | Bottom silicon dioxide | SiO2 | 0.5 m |

| Second | Bottom PI1 | PI | 3 m | |

| Third | Bottom RDL | Cu | 5 m | |

| Forth | Bottom PI2 | PI | 7 m | |

| Fifth | Bottom UBM | Cu | Thickness: 5 m Diameter: 240 m |

| Material | (g/cm3) | E (Mpa) | (1 × 10−6) | (W × m−1 × K−1) | C (J × kg−1 × K−1) | |

|---|---|---|---|---|---|---|

| Cu | 8.9 | 128 | 0.34 | 16.5 | 380 | 385 |

| SiO2 | 2.648 | 75 | 0.17 | 0.5 | 1.3 | 1000 |

| Si | 2.329 | 169 | 0.26 | 2.49 | 156 | 713 |

| PI | 1.1 | 2.2 | 0.3 | 20 | 0.19 | 1100 |

| Sn63Pb37 | 8.4 | 30.0 | 0.36 | 24.7 | 50 | 183 |

| Substrate | 3.9 | 380 | 0.27 | 5.8 | 27 | 900 |

| Stress (MPa) | 121 | 186 | 217 | 234 | 248 |

|---|---|---|---|---|---|

| strain | 0.001 | 0.004 | 0.01 | 0.02 | 0.04 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tian, W.; Dang, H.; Li, D.; Cong, Y.; Chen, Y. Reliability Simulation Analysis of TSV Structure in Silicon Interposer under Temperature Cycling. Micromachines 2024, 15, 986. https://doi.org/10.3390/mi15080986

Tian W, Dang H, Li D, Cong Y, Chen Y. Reliability Simulation Analysis of TSV Structure in Silicon Interposer under Temperature Cycling. Micromachines. 2024; 15(8):986. https://doi.org/10.3390/mi15080986

Chicago/Turabian StyleTian, Wenchao, Haojie Dang, Dexin Li, Yunhao Cong, and Yuanming Chen. 2024. "Reliability Simulation Analysis of TSV Structure in Silicon Interposer under Temperature Cycling" Micromachines 15, no. 8: 986. https://doi.org/10.3390/mi15080986