Novel Bidirectional ESD Circuit for GaN HEMT

Abstract

:1. Introduction

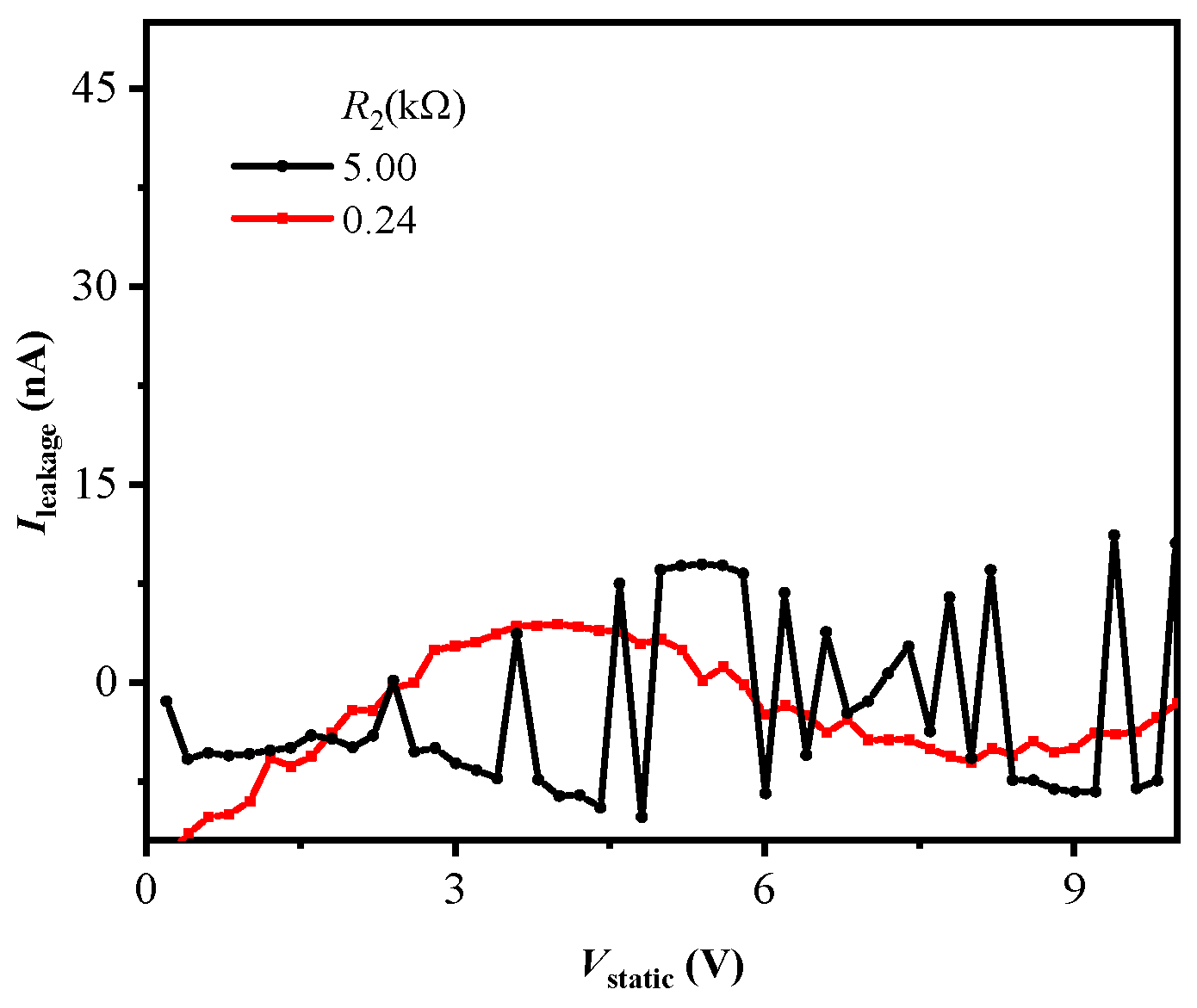

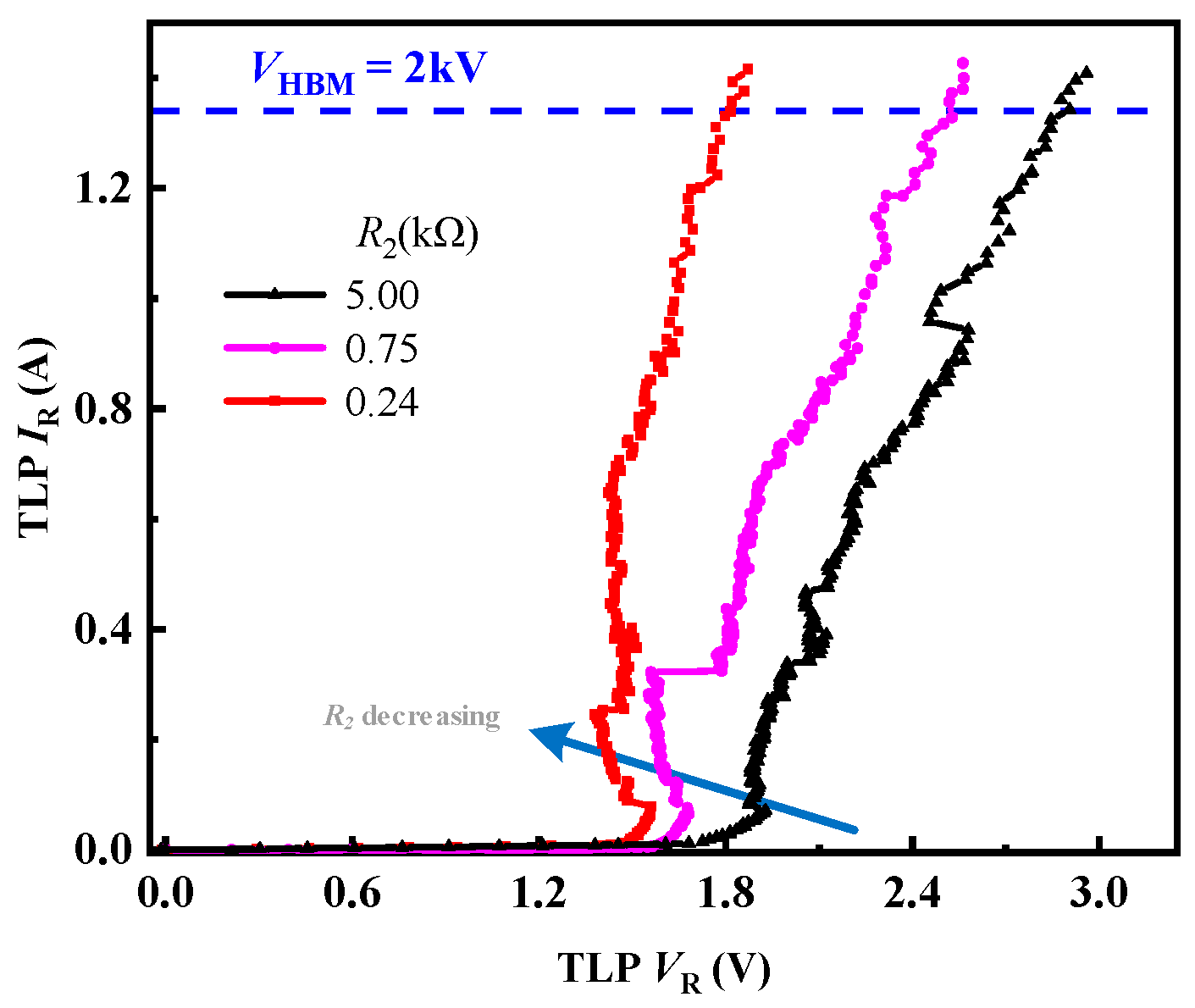

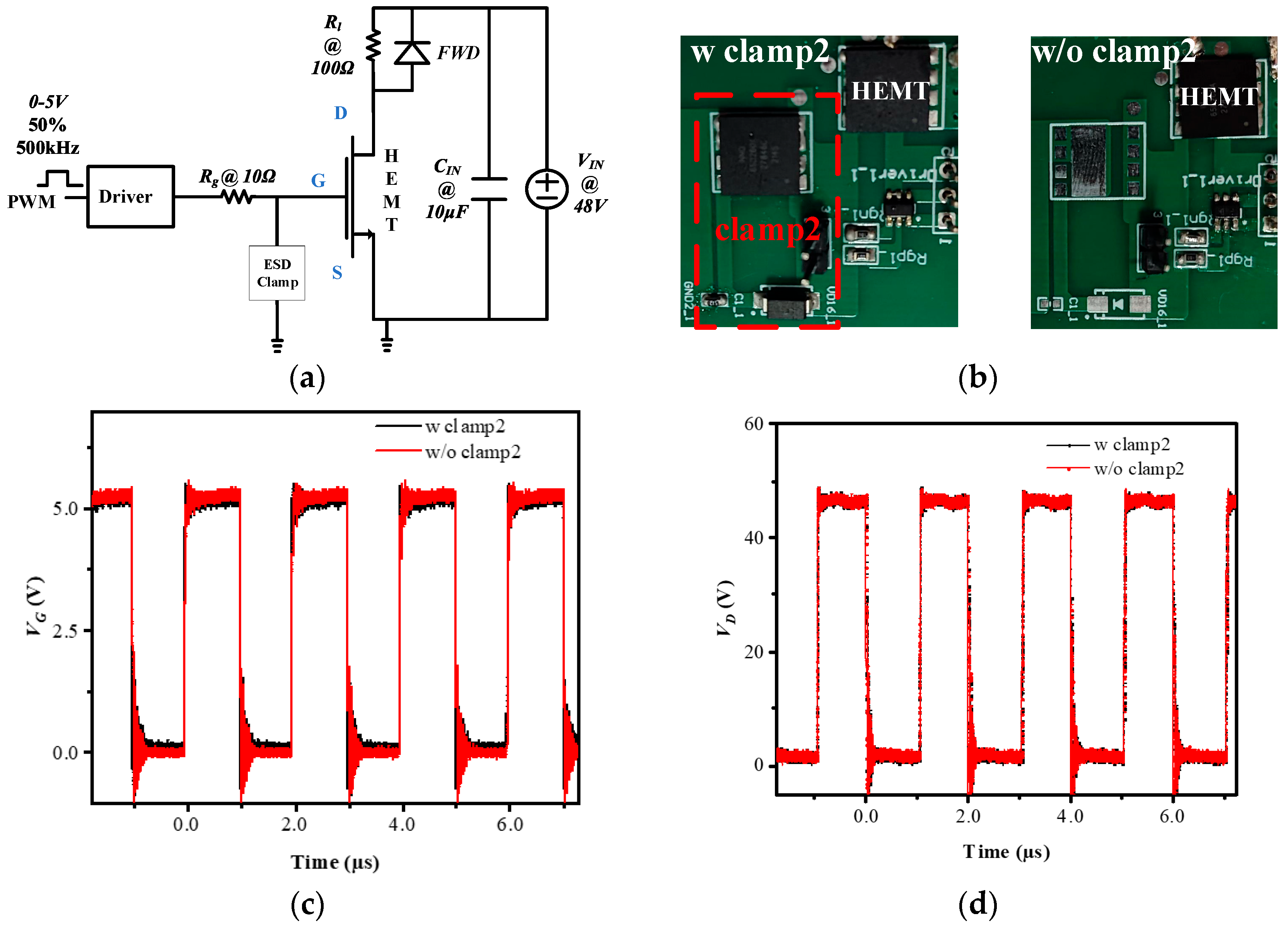

2. Structure and Mechanism

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kuzmík, J.; Pogany, D.; Gornik, E.; Javorka, P.; Kordos, P. Electrostatic discharge effects in AlGaN/GaN high-electron-mobility transistors. Appl. Phys. Lett. 2003, 83, 4655–4657. [Google Scholar] [CrossRef]

- Rossetto, I.; Meneghini, M.; Barbato, M.; Rampazzo, F.; Marcon, D.; Meneghesso, G.; Zanoni, E. Demonstration of Field- and Power-Dependent ESD Failure in AlGaN/GaN RF HEMTs. IEEE Trans. Electron Devices 2015, 62, 2830–2836. [Google Scholar] [CrossRef]

- Shankar, B.; Raghavan, S.; Shrivastava, M. ESD Reliability of AlGaN/GaN HEMT Technology. IEEE Trans. Electron Devices 2019, 66, 3756–3763. [Google Scholar] [CrossRef]

- Xin, Y.; Chen, W.; Sun, R.; Shi, Y.; Liu, C.; Xia, Y.; Wang, F.; Xu, X.; Shi, Q.; Wang, Y.; et al. Electrostatic Discharge (ESD) Behavior of p-GaN HEMTs. In Proceedings of the 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Electr Network, Vienna, Austria, 13–18 September 2020; pp. 317–320. [Google Scholar]

- Canato, E.; Meneghini, M.; Nardo, A.; Masin, F.; Barbato, A.; Barbato, M.; Stockman, A.; Banerjee, A.; Moens, P.; Zanoni, E.; et al. ESD-failure of E-mode GaN HEMTs: Role of device geometry and charge trapping. Microelectron. Reliab. 2019, 100–101, 113334. [Google Scholar] [CrossRef]

- Chen, Y.Q.; Feng, J.T.; Wang, J.L.; Xu, X.B.; He, Z.Y.; Li, G.Y.; Lei, D.Y.; Chen, Y.; Huang, Y. Degradation Behavior and Mechanisms of E-Mode GaN HEMTs with p-GaN Gate Under Reverse Electrostatic Discharge Stress. IEEE Trans. Electron Devices 2020, 67, 566–570. [Google Scholar] [CrossRef]

- Tazzoli, A.; Danesin, F.; Zanoni, E.; Meneghesso, G. ESD robustness of AlGaN/GaN HEMT devices. In Proceedings of the Electrical Overstress/Electrostatic Discharge Symposium, Anaheim, CA, USA, 23–28 September 2007. [Google Scholar]

- Xu, X.B.; Li, B.; Chen, Y.Q.; Wu, Z.H.; He, Z.Y.; Liu, L.; He, S.Z.; En, Y.F.; Huang, Y. Analysis of Trap and Recovery Characteristics Based on Low-Frequency Noise for E-Mode GaN HEMTs Under Electrostatic Discharge Stress. IEEE J. Electron Devices Soc. 2021, 9, 89–95. [Google Scholar] [CrossRef]

- Ker, M.D.; Peng, J.H.; Jiang, H.C. ESD test methods on integrated circuits: An overview. In Proceedings of the 8th IEEE International Conference on Electronics, Circuits and Systems, St Julians, Malta, 2–5 September 2001; pp. 1011–1014. [Google Scholar]

- Stadler, W.; Guggenmos, X.; Egger, P.; Gieser, H.; Musshoff, C. Does the ESD-failure current obtained by transmission-line pulsing always correlate to human body model tests? Microelectron. Reliab. 1998, 38, 1773–1780. [Google Scholar] [CrossRef]

- Xin, Y.; Chen, W.; Sun, R.; Wang, F.; Deng, X.; Li, Z.; Zhang, B. Simulation Study of a High Gate-to-Source ESD Robustness Power p-GaN HEMT with Self-Triggered Discharging Channel. IEEE Trans. Electron Devices 2021, 68, 4536–4542. [Google Scholar] [CrossRef]

- Wang, Z.; Liou, J.J.; Cho, K.-L.; Chiu, H.-C. Development of an Electrostatic Discharge Protection Solution in GaN Technology. IEEE Electron Device Lett. 2013, 34, 1491–1493. [Google Scholar] [CrossRef]

- Yan, X.; Li, W.; Islam, S.; Pourang, K.; Xing, H.G.; Fay, P.; Jena, D. Polarization-induced Zener tunnel diodes in GaN/InGaN/GaN heterojunctions. Appl. Phys. Lett. 2015, 107, 163504. [Google Scholar] [CrossRef]

- Xin, Y.; Chen, W.; Sun, R.; Wang, F.; Liu, C.; Deng, X.; Li, Z.; Zhang, B. Experimental Demonstration of an Integrated Bidirectional Gate ESD Protection Structure for p-GaN Power HEMTs. IEEE Electron Device Lett. 2023, 44, 209–212. [Google Scholar] [CrossRef]

- Lin, S.-Y.; Lin, S.-Y.; Hung, S.-H.; Wang, T.-W.; Li, C.-H.; Go, C.-L.; Huang, S.-C.; Chen, K.-H.; Zheng, K.-L.; Lin, Y.-H. 20.3 A GaN Gate Driver with On-chip Adaptive On-time Controller and Negative Current Slope Detector. In Proceedings of the 2023 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 19–23 February 2023; pp. 306–308. [Google Scholar]

- Zhou, C.; Guan, Y.; Shen, J.; Liao, H.; Zhao, Q.; He, C.; Wu, Y.; Lin, W.; Zhang, T.; Chen, Y.; et al. On-Chip Gate ESD Protection for AlGaN/GaN E-Mode Power HEMT Delivering >2kV HBM ESD. In Proceedings of the 7th Annual IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Raleigh, NC, USA, 29–31 October 2019; pp. 175–176. [Google Scholar]

- Yao, B.; Shi, Y.; Wang, H.; Xu, X.; Chen, Y.; He, Z.; Xiao, Q.; Wang, L.; Lu, G.; Li, H. A novel bidirectional AlGaN/GaN ESD protection diode. Micromachines 2022, 13, 135. [Google Scholar] [CrossRef] [PubMed]

- Liu, C.; Shi, Y.; He, Z.; Cai, Z.; Huang, X.; Chen, Y.; Chen, W.; Sun, R.; Lu, G.; Zhang, B. A GaN Lateral Bidirectional ESD Clamp Based on the Floating-Gate MBS and a Regulating Capacitor. IEEE Trans. Electron Devices 2023, 71, 510–515. [Google Scholar] [CrossRef]

- Lee, J.-H.; Huang, Y.-J.; Hong, L.-Y.; Chen, L.-F.; Jou, Y.-N.; Lin, S.-C.; Wohlmuth, W.; Liao, C.-C.; Li, C.-H.; Huang, S.-C. Incorporation of a simple ESD circuit in a 650V E-mode GaN HEMT for all-terminal ESD protection. In Proceedings of the 2022 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 27–31 March 2022; pp. 2B. 3-1–2B. 3-6. [Google Scholar]

- Lee, J.-H.; Huang, Y.-J.; Hong, L.-Y.; Liao, C.-C.; Lien, B.; Nidhi, K.; Jou, Y.-N.; Chen, K.-H. The Influence of Gate-Series-Resistor on the ESD Protection and Switching Speed for 650V GaNHEMT Circuit. In Proceedings of the 2024 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Singapore, 15–18 July 2024; pp. 1–6. [Google Scholar]

- Wang, W.-C.; Ker, M.-D. Fully Integrated GaN-on-Silicon Power-Rail ESD Clamp Circuit Without Transient Leakage Current During Normal Power-ON Operation. IEEE J. Electron Devices Soc. 2024, 12, 760–769. [Google Scholar] [CrossRef]

- Wang, H.; Wei, J.; Xie, R.; Liu, C.; Tang, G.; Chen, K.J. Maximizing the Performance of 650-V p-GaN Gate HEMTs: Dynamic RON Characterization and Circuit Design Considerations. IEEE Trans. Power Electron. 2017, 32, 5539–5549. [Google Scholar] [CrossRef]

- Rossetto, I.; Meneghini, M.; Hilt, O.; Bahat-Treidel, E.; De Santi, C.; Dalcanale, S.; Wuerfl, J.; Zanoni, E.; Meneghesso, G. Time-Dependent Failure of GaN-on-Si Power HEMTs With p-GaN Gate. IEEE Trans. Electron Devices 2016, 63, 2334–2339. [Google Scholar] [CrossRef]

- Scholz, M.; Linten, D.; Thijs, S.; Sangameswaran, S.; Sawada, M.; Nakaei, T.; Hasebe, T.; Groeseneken, G. ESD On-Wafer Characterization: Is TLP Still the Right Measurement Tool? IEEE Trans. Instrum. Meas. 2009, 58, 3418–3426. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, P.; Yang, C.; Shen, J.; Luo, X.; Deng, G.; Sun, S.; Wei, Y.; Wei, J. Novel Bidirectional ESD Circuit for GaN HEMT. Micromachines 2025, 16, 129. https://doi.org/10.3390/mi16020129

Zhang P, Yang C, Shen J, Luo X, Deng G, Sun S, Wei Y, Wei J. Novel Bidirectional ESD Circuit for GaN HEMT. Micromachines. 2025; 16(2):129. https://doi.org/10.3390/mi16020129

Chicago/Turabian StyleZhang, Pengfei, Cheng Yang, Jingyu Shen, Xiaorong Luo, Gaoqiang Deng, Shuxiang Sun, Yuxi Wei, and Jie Wei. 2025. "Novel Bidirectional ESD Circuit for GaN HEMT" Micromachines 16, no. 2: 129. https://doi.org/10.3390/mi16020129

APA StyleZhang, P., Yang, C., Shen, J., Luo, X., Deng, G., Sun, S., Wei, Y., & Wei, J. (2025). Novel Bidirectional ESD Circuit for GaN HEMT. Micromachines, 16(2), 129. https://doi.org/10.3390/mi16020129