Dynamic Performance Evaluation of Bidirectional Bridgeless Interleaved Totem-Pole Power Factor Correction Boost Converter

Abstract

:1. Introduction

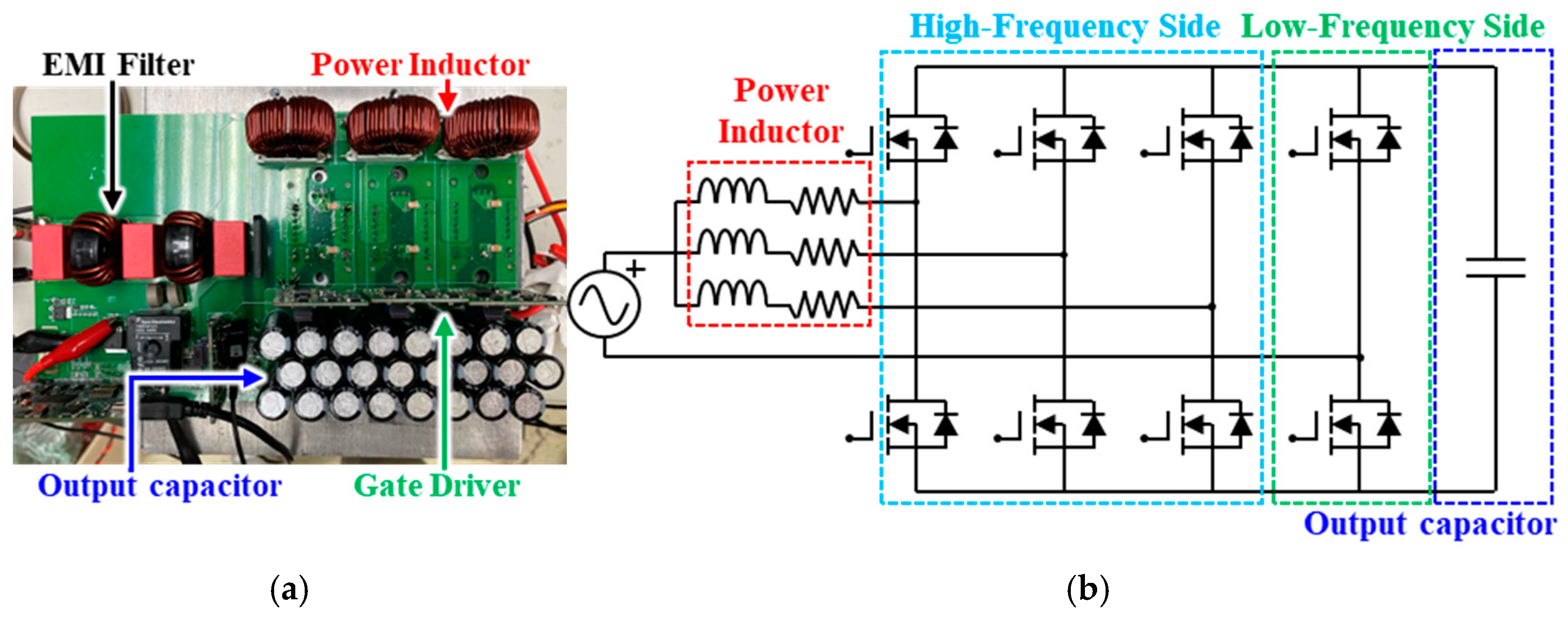

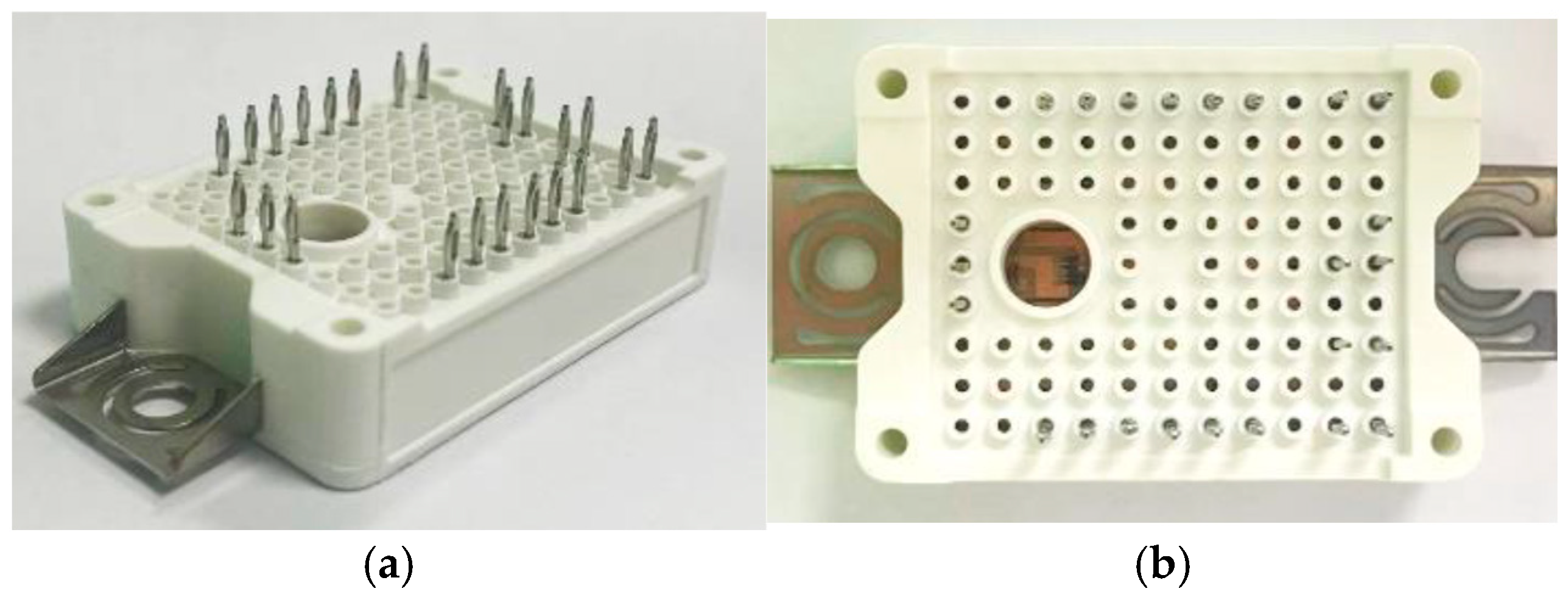

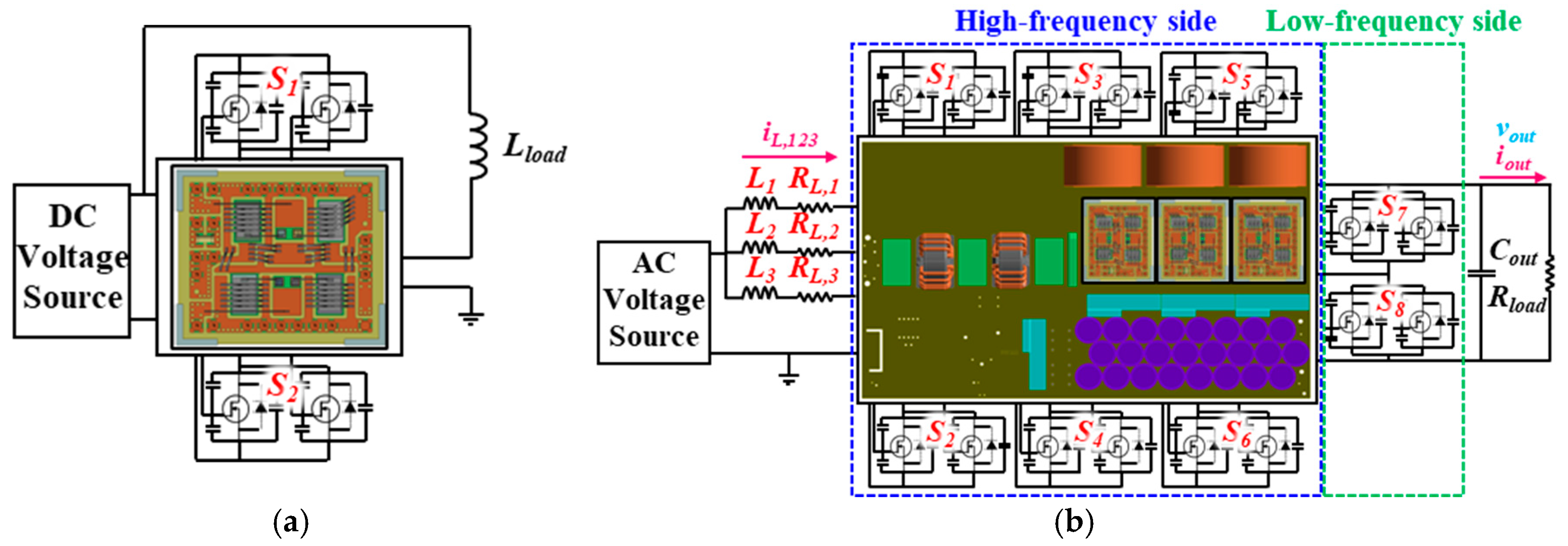

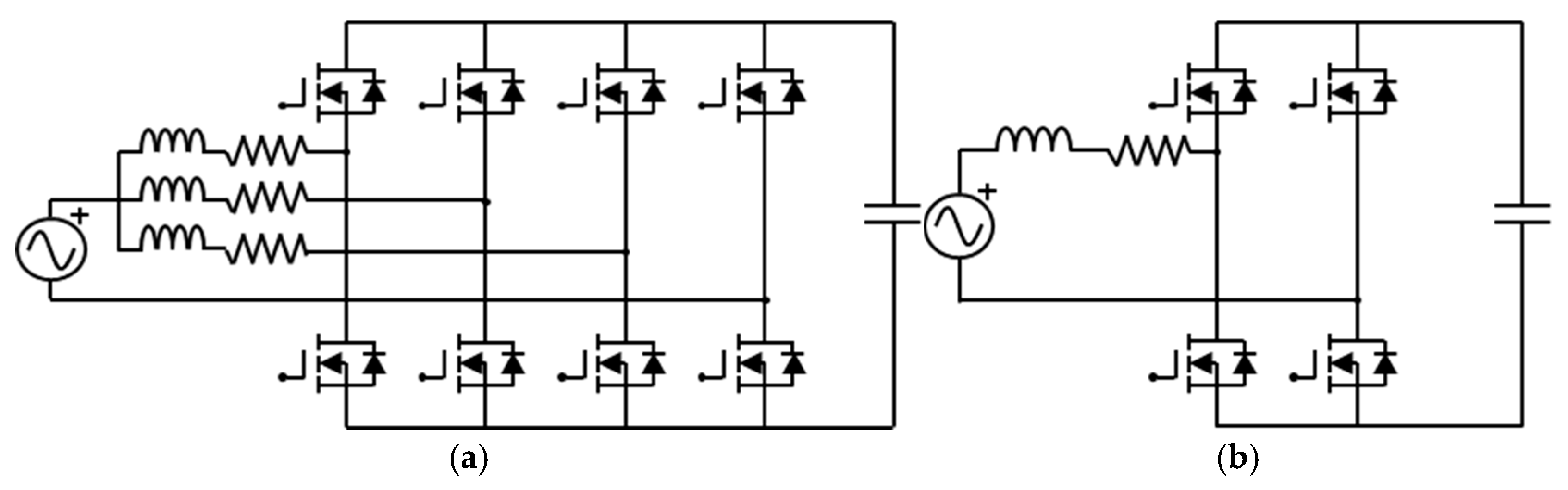

2. SiC MOSFET-Based Bidirectional Bridgeless Interleaved Totem-Pole PFC Boost Converter

3. Experiments

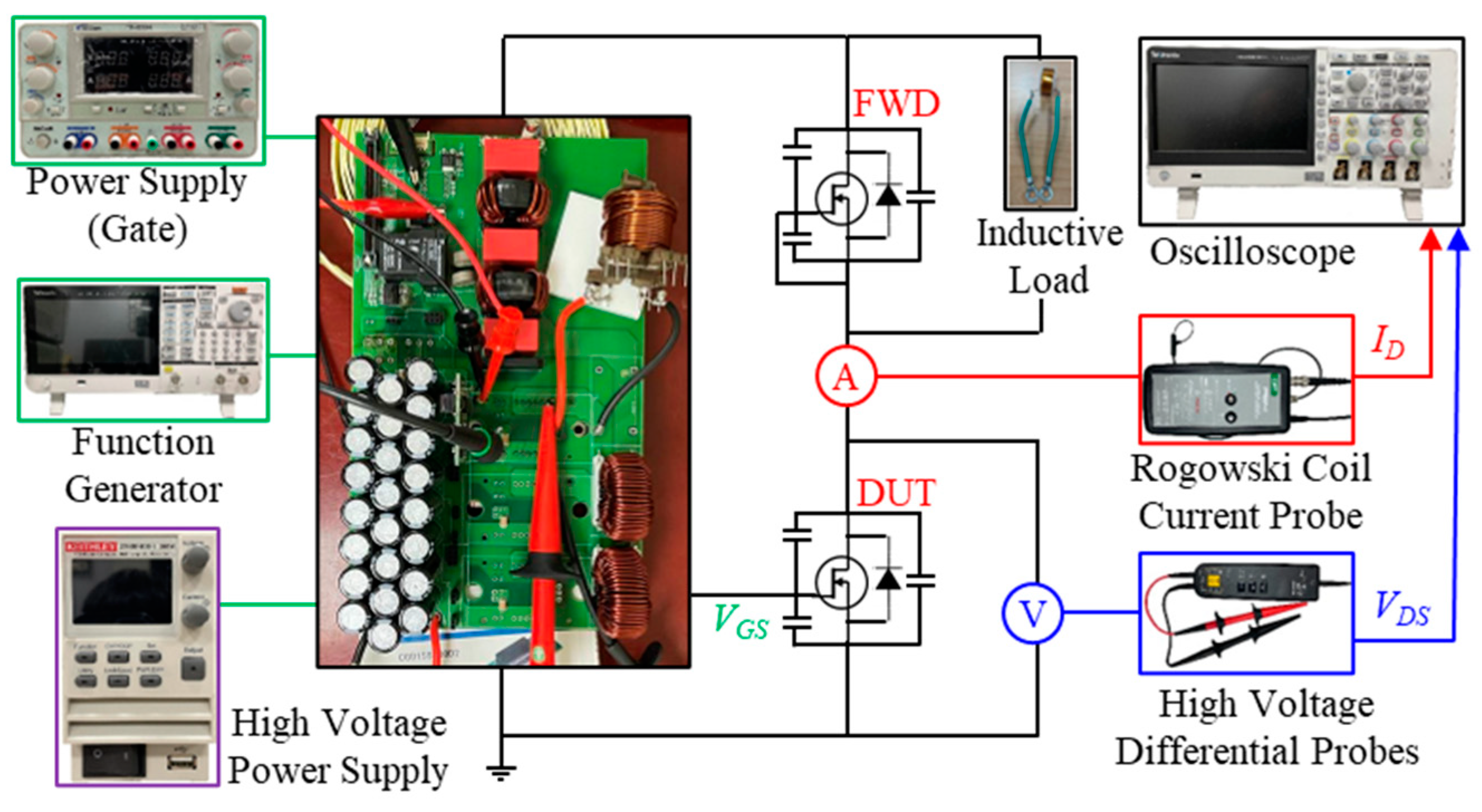

3.1. Double Pulse Test (DPT)

3.2. Closed-Loop Totem-Pole PFC Converter Operation Experiment

4. Theoretical Model

4.1. Definition of Power Factor (PF)

4.2. Power Loss Estimation

5. Numerical Modeling

6. Results and Discussion

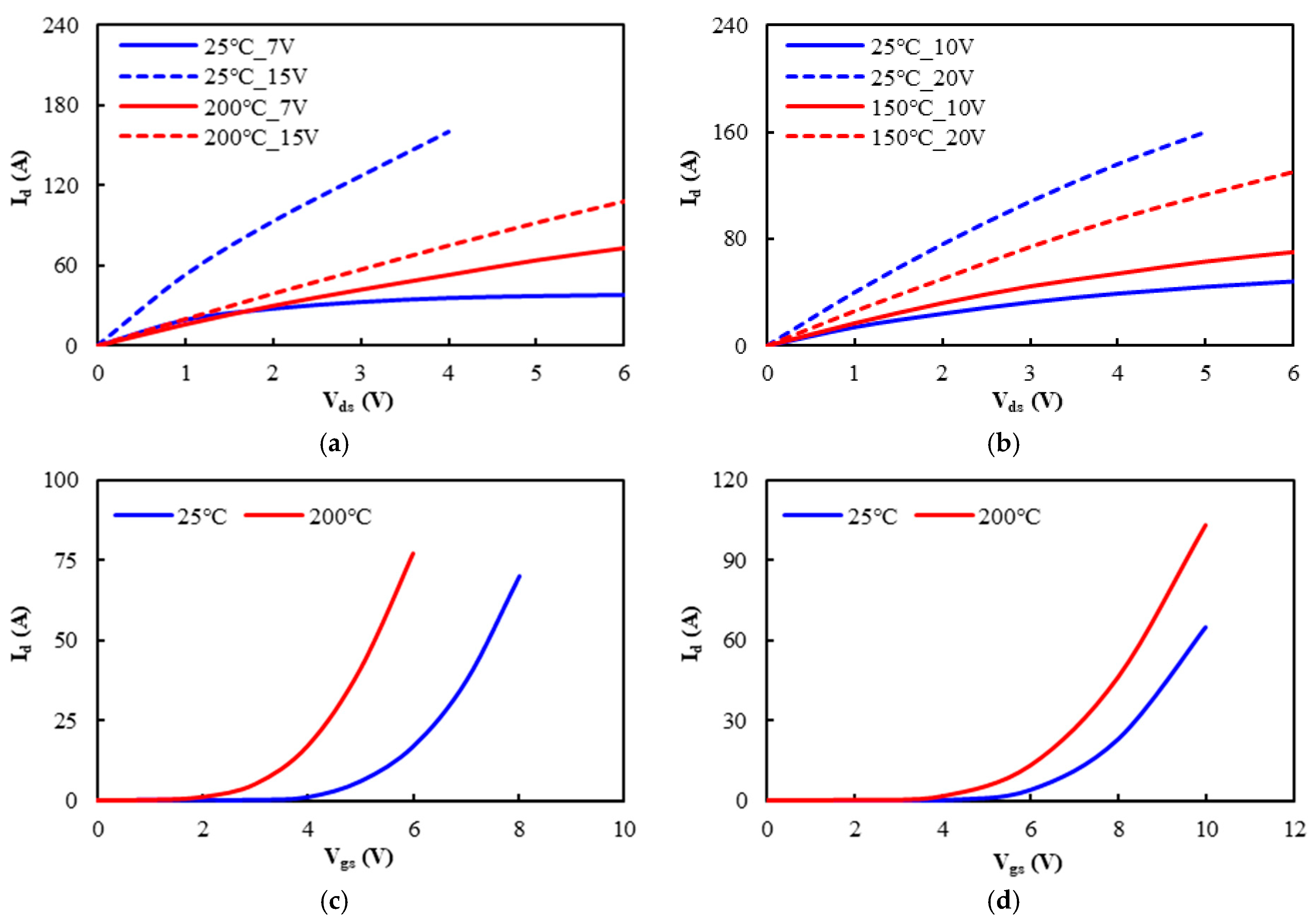

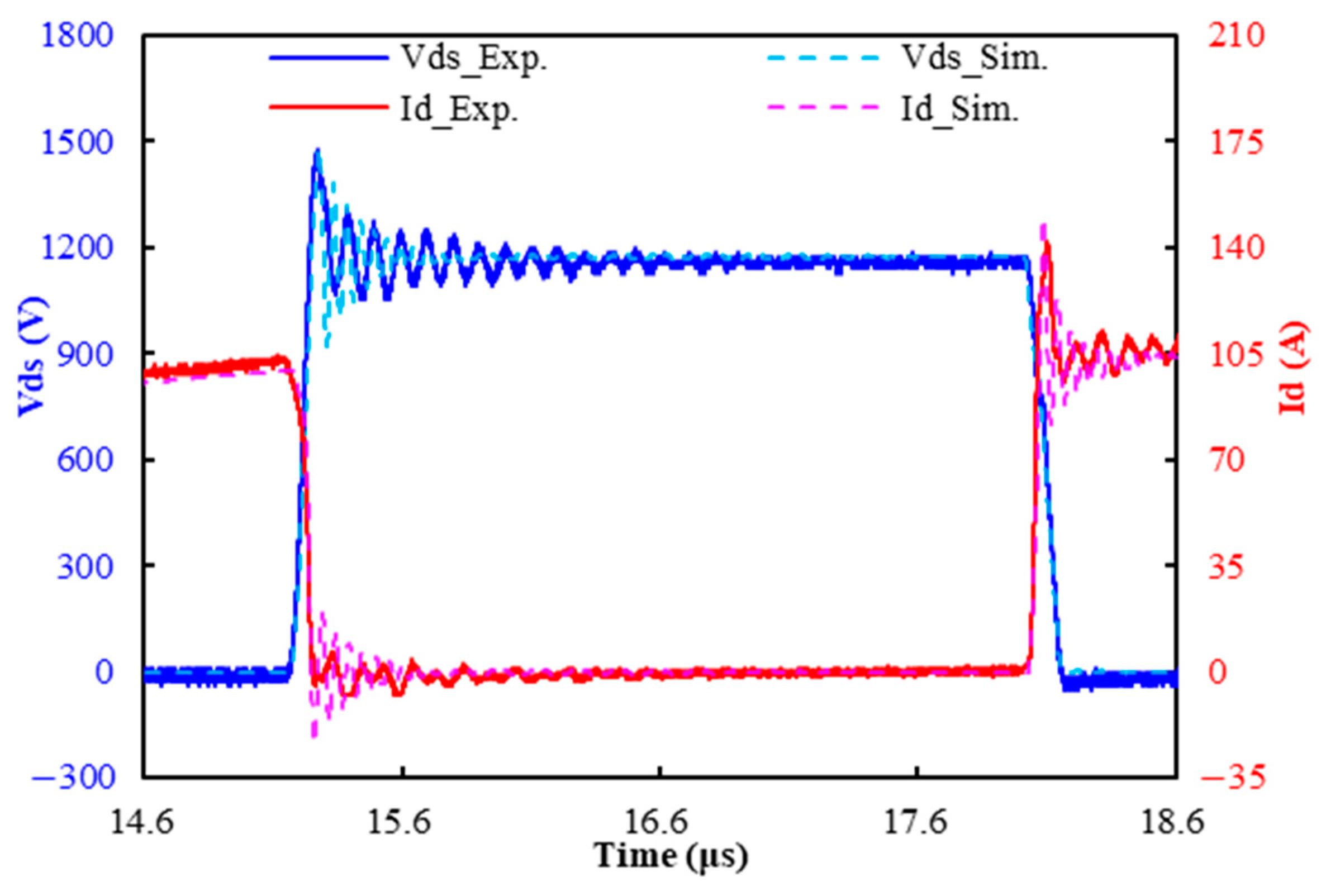

6.1. Characterization of DPT Switching Characteristics

6.2. Comparison of Interleaved and Non-Interleaved Totem-Pole PFC Boost Converters

6.3. Closed-Loop Converter Operation and Power Loss Estimation

6.4. Performance Comparison Between SiC MOSFET-Based and Si IGBT-Based Interleaved PFC Boost Converters

6.5. Parametric Analysis

7. Conclusions

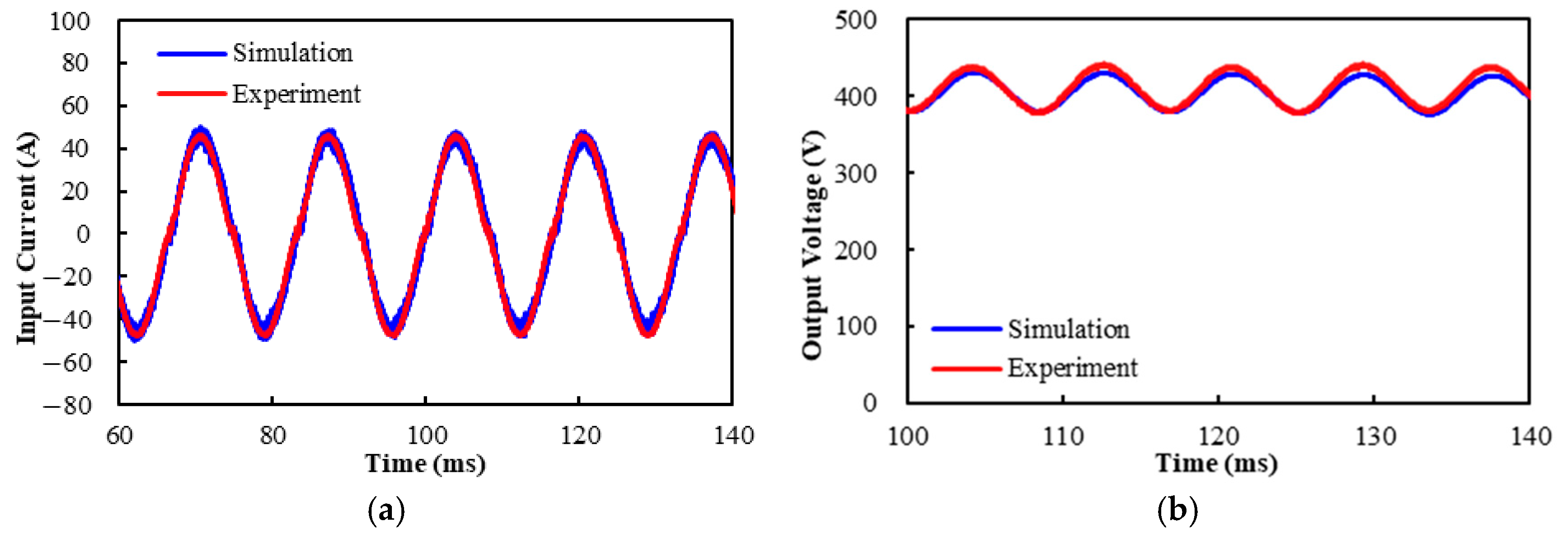

- The simulated switching characteristics and the voltage and current waveforms under closed-loop operation match very well with the experimental results, proving the effectiveness of the proposed ECCS model.

- The three-leg interleaved design offers reduced power loss and improved efficiency compared to the non-interleaved, primarily attributed to the even distribution of the total input current across these three legs. Additionally, the three-leg interleaving achieves a reduced total input current ripple due to the ripple cancellation effect, leading to an improvement in the power factor.

- In the interleaved totem-pole PFC, the power loss of the high-frequency side switches is appreciably higher than those of the low-frequency side switches. This is because the low-frequency side loss is mostly the conduction loss of the power switches, with the switching loss and body diode loss being almost negligible. In contrast, the high-frequency side loss is dominated by the switching loss and the body diode loss of the power switches, arising from the high-frequency switching, potentially leading to a larger reverse recovery loss. Additionally, the conduction loss takes a very small part of the high-frequency side loss during the closed-loop converter operation. This can be attributed to a lower current flowing through these switches and a lower on-state resistance of the SiC MOSFET devices.

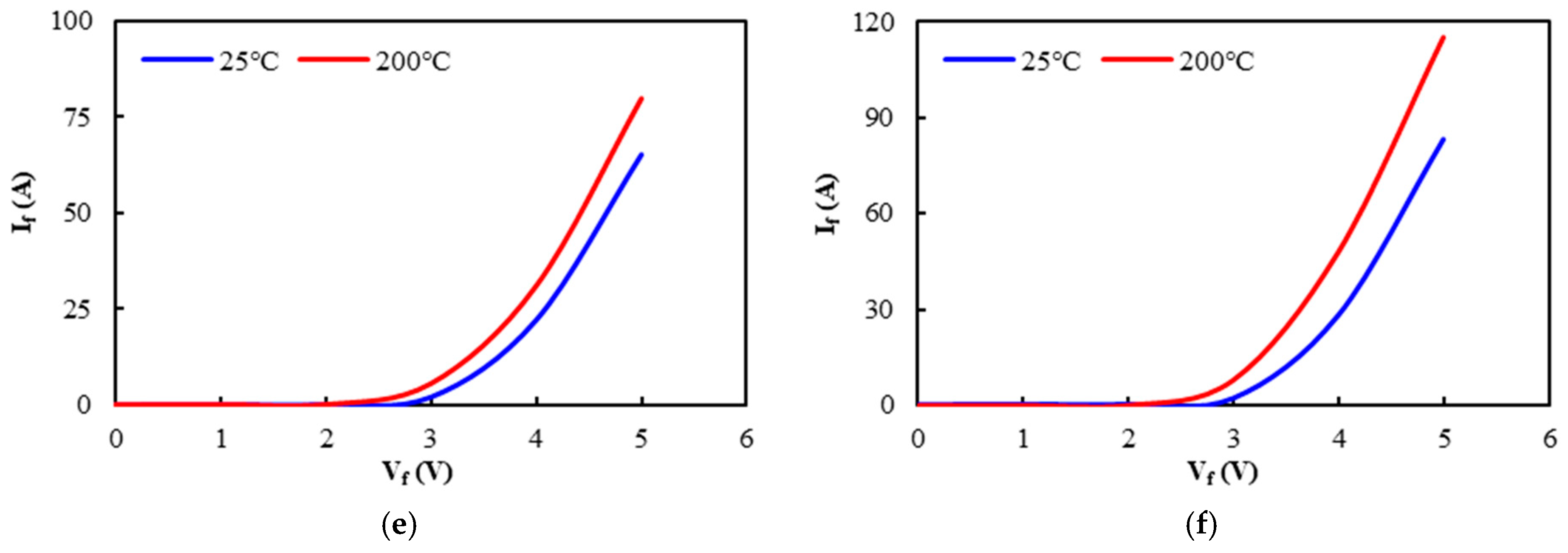

- The conduction loss of the high-frequency side switches increases with the temperature due to the corresponding rise in the on-state resistance. Conversely, the body diode loss decreases with the temperature, because of the negative temperature coefficient of the body diodes. This result offsets the increase in the conduction loss with the temperature, causing a trivial temperature dependence of the high-frequency side loss.

- The performance comparison between the SiC MOSFET-based and the Si IGBT-based PFC boost converter highlights the clear advantages of the SiC MOSFET devices for high-frequency, high-efficiency applications owing to their faster switching speed, lower switching loss, and better body diode performance.

- The parametric analysis shows that increasing the line frequency and power inductor, as well as decreasing the output voltage, can reduce high-frequency side losses. Low-frequency side losses can be reduced by lowering the temperature, and increasing the line frequency and power inductor. Among these, the output voltage has the most significant impact on the Totem-Pole PFC converter losses.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zentani, A.; Almaktoof, A.; Kahn, M.T. A comprehensive review of developments in electric vehicles fast charging technology. Appl. Sci. 2024, 14, 4728. [Google Scholar] [CrossRef]

- Dar, A.R.; Haque, A.; Khan, M.A.; Kurukuru, V.S.B.; Mehfuz, S. On-board chargers for electric vehicles: A comprehensive performance and efficiency review. Energies 2024, 17, 4534. [Google Scholar] [CrossRef]

- Nasr Esfahani, F.; Darwish, A.; Ma, X.; Twigg, P. Non-integrated and integrated on-board battery chargers (iOBCs) for electric vehicles (EVs): A critical review. Energies 2024, 17, 2285. [Google Scholar] [CrossRef]

- Khaligh, A.; Dusmez, S. Comprehensive topological analysis of conductive and inductive charging solutions for plug-in electric vehicles. IEEE Trans. Veh. Technol. 2012, 61, 3475–3489. [Google Scholar] [CrossRef]

- Figueiredo, J.P.M.; Tofoli, F.L.; Silva, B.L.A. A review of single-phase PFC topologies based on the boost converter. In Proceedings of the 9th IEEE/IAS International Conference on Industry Applications, Sao Paulo, Brazil, 8–10 November 2010. [Google Scholar]

- Wang, H.; Dusmez, S.; Khaligh, A. Design and analysis of a full-bridge LLC-based PEV charger optimized for wide battery voltage range. IEEE Trans. Veh. Technol. 2014, 63, 1603–1613. [Google Scholar] [CrossRef]

- Pai, A.P.; Holzmann, L.; Kampl, S. Optimal selection of power semiconductor technology for on-board charger (OBC) applications and experimental verification for a 2.5 kW classical. In Proceedings of the PCIM Europe Digital Days 2020, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremburg, Germany, 7–8 July 2020. [Google Scholar]

- Ishraq, N.; Mallik, A. Design of a 2.5 kW four-level interleaved flying capacitor multilevel totem-pole PFC converter with AC-side passive volume optimization. IEEE Open J. Power Electron. 2024, 5, 214–231. [Google Scholar] [CrossRef]

- Gong, X.; Wang, G.; Bhardwaj, M. 6.6 kW Three-phase interleaved totem pole PFC design with 98.9% peak efficiency for HEV/EV onboard charger. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition, Anaheim, CA, USA, 17–21 March 2019. [Google Scholar]

- Çatlioğlu, E.; Yildirim, D. Performance analysis of power devices for bridgeless totem-pole PFC at different switching frequencies. In Proceedings of the 10th International Conference on Electrical and Electronics Engineering, Istanbul, Türkiye, 8–10 May 2023. [Google Scholar]

- Xi, H.; Li, L.; Xu, G.; Su, M.; Cai, Z. Variable-frequency control for totem-pole bridgeless power factor correction converter to achieve zero-voltage switching without zero-crossing detection circuits. Electronics 2024, 13, 3108. [Google Scholar] [CrossRef]

- Han, J.-K. Efficiency and PF improving techniques with a digital control for totem-pole bridgeless CRM boost PFC converters. Energies 2024, 17, 369. [Google Scholar] [CrossRef]

- Hu, Y.; Liu, I.; Xie, K.; Bhatia, T.; Narain, A. High efficiency and high power density totem-pole PFC with SiC MOSFETs. In Proceedings of the PCIM Europe 2023; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 9–11 May 2023. [Google Scholar]

- Kim, D.-K.; Jeong, Y.; Lim, C.-Y.; Kang, B.; Moon, G.-W. Bidirectional bridgeless PFC with reduced input current distortion and switching loss using gate skipping technique. In Proceedings of the IEEE Transportation Electrification Conference and Expo, Asia-Pacific, Busan, Republic of Korea, 1–4 June 2016. [Google Scholar]

- Fu, H.; Duan, S.; Li, Y.; Li, Q. Improved control strategy for zero-crossing distortion elimination in totem-pole PFC converter with coupled inductor. Energies 2022, 15, 5437. [Google Scholar] [CrossRef]

- Biela, J.; Schweizer, M.; Waffler, S.; Kolar, J.W. SiC versus Si—Evaluation of potentials for performance improvement of inverter and DC–DC converter systems by SiC power semiconductors. IEEE Trans. Ind. Electron. 2011, 58, 2872–2882. [Google Scholar] [CrossRef]

- Rong, J.; Ding, Y.; Zhang, M.; Chen, X. Modeling and simulation of boost hard switching converter in power factor correction circuit. In Proceedings of the 3rd International Conference on Consumer Electronics, Communications and Networks, Xianning, China, 20–22 November 2013. [Google Scholar]

- Lee, G.-Y.; Park, H.-C.; Ji, M.-W.; Kim, R.-Y. Digitalized control algorithm of bridgeless totem-pole PFC with a simple control structure based on the phase angle. Electronics 2023, 12, 4449. [Google Scholar] [CrossRef]

- Reali, A.; Alemanno, A.; Ronchi, F.; Rossi, C.; Florian, C. Development of GaN-based, 6.6 kW, 450 V, bi-directional on-board charger with integrated 1 kW, 12 V auxiliary DC-DC converter with high power density. Micromachines 2024, 15, 1470. [Google Scholar] [CrossRef]

- Kumar, V.; Yi, K. Single-phase, bidirectional, 7.7 kW totem pole on-board charging/discharging infrastructure. Appl. Sci. 2022, 12, 2236. [Google Scholar] [CrossRef]

- Chen, Y.; Mei, Y.-H.; Ning, P.; Lu, G.-Q. Local interconnection degradation of a double-sided cooling SiC MOSFET module under power cycling. IEEE Trans. Compon. Packag. Manuf. Technol. 2024, 14, 832–840. [Google Scholar] [CrossRef]

- Anzola, J.; Sharma, S.; Aizpuru, I.; Bhattacharya, S.; Artal-Sevil, J.S. Performance improvement of a silicon partial power converter over a silicon carbide full power converter. IEEE Trans. Transp. Electrif. 2024, 10, 1680–1691. [Google Scholar] [CrossRef]

- Yasui, K.; Hayakawa, S.; Funaki, T. Reliability improvement of 3.3 kV full-SiC power modules for power cycling tests with sintered copper die attach technology. IEEE Trans. Compon. Packag. Manuf. Technol. 2023, 13, 1476–1485. [Google Scholar] [CrossRef]

- Guo, X.; Xun, Q.; Li, Z.; Du, S. Silicon carbide converters and MEMS devices for high-temperature power electronics: A critical review. Micromachines 2019, 10, 406. [Google Scholar] [CrossRef]

- Xing, Y.; Ren, B.; Li, B.; Chen, J.; Yin, S.; Lin, H.; Liu, J.; Chen, H. Principles and methods for improving the thermoelectric performance of SiC: A potential high-temperature thermoelectric material. Materials 2024, 17, 3636. [Google Scholar] [CrossRef]

- Cheng, H.-C.; Liu, Y.-C. Dynamic modeling framework for evaluating electromagnetic-electro-thermal behavior of power conversion system during load operation. J. Electron. Packag. 2023, 145, 021005. [Google Scholar] [CrossRef]

- Cheng, H.-C.; Liu, Y.-C.; Lin, H.-H.; Chiou, S.-C.; Tzeng, C.-M.; Chang, T.-C. Development and performance evaluation of integrated hybrid power module for three-phase servo motor applications. Micromachines 2023, 14, 1356. [Google Scholar] [CrossRef] [PubMed]

- Cheng, H.-C.; Liu, Y.-C.; Jhu, W.-Y.; Chiu, P.-K.; Chang, T.-C.; Chiang, K.-N. Power loss and electrothermal characterization of hybrid power integrated modules for industrial servo motor drives. Energies 2024, 17, 6036. [Google Scholar] [CrossRef]

- Cheng, H.-C.; Shen, Y.-H.; Chen, W.-H. Parasitic extraction and power loss estimation of power devices. J. Mech. 2020, 37, 134–148. [Google Scholar] [CrossRef]

- Dini, P.; Saponara, S. Electro-thermal model-based design of bidirectional on-board chargers in hybrid and full electric vehicles. Electronics 2022, 11, 112. [Google Scholar] [CrossRef]

- Chen, C.; Chen, Y.; Li, Y.; Huang, Z.; Liu, T.; Kang, Y. An SiC-based half-bridge module with an improved hybrid packaging method for high power density applications. IEEE Trans. Ind. Electron. 2017, 64, 8980–8991. [Google Scholar] [CrossRef]

- Cheng, H.-C.; Syu, J.-Y.; Wang, H.-H.; Liu, Y.-C.; Kao, K.-S.; Chang, T.-C. Power cycling modeling and lifetime evaluation of SiC power MOSFET module using a modified physical lifetime model. IEEE Trans. Device Mater. Rel. 2024, 24, 142–153. [Google Scholar] [CrossRef]

- Li, B.; Yang, K.; Wu, M.; Chen, W. Thermomechanical stress analysis, characterization, and optimization for double-side cooled power modules with ceramic substrate. IEEE Trans. Compon. Packag. Manuf. Technol. 2024, 14, 561–572. [Google Scholar] [CrossRef]

- Su, B.; Lu, Z. An interleaved totem-pole boost bridgeless rectifier with reduced reverse-recovery problems for power factor correction. IEEE Trans. Power Electron. 2010, 25, 1406–1415. [Google Scholar]

- Grazian, F.; Soeiro, T.B.; Bauer, P. Voltage/Current doubler converter for an efficient wireless charging of electric vehicles with 400-V and 800-V battery voltages. IEEE Trans. Ind. Electron. 2023, 70, 7891–7903. [Google Scholar] [CrossRef]

- Hyeon, Y.-J.; Lee, D.-I.; Jeong, S.-W.; Youn, H.-S. A multi-objective PFC boost inductor optimal design algorithm based on Pareto front. Energies 2024, 17, 896. [Google Scholar] [CrossRef]

- IEC 60747-8; International Standard for Semiconductor Devices—Discrete Devices—Part 8: Field-Effect Transistors. IEC: Geneva, Switzerland, 2021.

- Liu, Z.; Huang, Z.; Lee, F.C.; Li, Q. Digital-based interleaving control for GaN-based MHz CRM totem-pole PFC. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 808–814. [Google Scholar] [CrossRef]

- Na, J.; Cheon, J.; Kim, K. 4H-SiC Double trench MOSFET with split heterojunction gate for improving switching characteristics. Materials 2021, 14, 3554. [Google Scholar] [CrossRef] [PubMed]

- Alavi, O.; Abdollah, M.; Viki, A.H. Assessment of thermal network models for estimating IGBT junction temperature of a buck converter. In Proceedings of the 8th Power Electronics, Drive Systems & Technologies Conference, Mashhad, Iran, 14–16 February 2017. [Google Scholar]

- Gupta, S.; Kumar, V.V. Performance analysis and loss estimation of an AC-DC PFC topologies of an EV charger. In Proceedings of the International Conference on Power, Instrumentation, Energy and Control, Aligarh, India, 10–12 February 2023. [Google Scholar]

| (kW) | (V) | (%) | (%) | (kHz) | (Hz) |

| 6.6 | 400 | 5 | 635 | 100 | 60 |

| (μF) | (μH) | (mΩ) | (Ω) | (Ω) | (ns) |

| 900 | 270 | 38 | 3 | 24.2 | 400 |

| Experiment | 158 ns | 250 ns | 6.4 mJ | 2.4 mJ | 1476 V | 142 A |

| Simulation | 164 ns | 247 ns | 5.3 mJ | 2.3 mJ | 1480 V | 150 A |

| Difference | 3.6% | 1.2% | 16.5% | 4.0% | 0.3% | 5.6% |

| Three-Leg Interleaved Design | Non-Interleaved Design | |

|---|---|---|

| High-frequency side loss (W) | 113.41 | 144.91 |

| Low-frequency side loss (W) | 39.17 | 40.25 |

| Power inductor loss (W) | 11.90 | 12.48 |

| Total power loss (W) | 164.48 | 197.64 |

| Efficiency (%) | 96.64 | 94.96 |

| Power factor | 0.996 | 0.987 |

| Switch | Conduction (W) | Switching (W) | Body Diode (W) | Sum (W) | Total (W) |

|---|---|---|---|---|---|

| S1 | 1.386 | 8.178 | 9.354 | 18.918 | 164.477 |

| S2 | 1.393 | 8.186 | 9.298 | 18.877 | |

| S3 | 1.387 | 8.171 | 9.346 | 18.903 | |

| S4 | 1.392 | 8.188 | 9.344 | 18.924 | |

| S5 | 1.386 | 8.158 | 9.322 | 18.866 | |

| S6 | 1.392 | 8.191 | 9.342 | 18.926 | |

| S7 | 19.557 | - | - | 19.557 | |

| S8 | 19.609 | - | - | 19.609 | |

| per leg | |||||

| Inductor | 3.966 | - | - | 11.898 |

| Temp.(°C) | High-Freq. Side Switch (W) | Sum (W) | Low-Freq. Side Switch (W) | Inductor (W) | ||

|---|---|---|---|---|---|---|

| Conduction | Switching | Body Diode | ||||

| 25 | 1.386 | 8.178 | 9.354 | 18.918 | 19.557 | 3.966 |

| 100 | 1.796 | 8.176 | 9.001 | 18.973 | 25.347 | 5.140 |

| 175 | 2.233 | 8.175 | 8.618 | 19.025 | 31.154 | 6.318 |

| SiC MOSFET-Based | Si IGBT-Based | |

|---|---|---|

| High-frequency side loss (W) | 113.41 | 230.55 |

| Low-frequency side loss (W) | 39.17 | 40.28 |

| Power inductor loss (W) | 11.90 | 12.24 |

| Total power loss (W) | 164.48 | 283.07 |

| Efficiency (%) | 96.64 | 92.43 |

| Power factor | 0.996 | 0.990 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cheng, H.-C.; Jhu, W.-Y.; Liu, Y.-C.; Zheng, D.-W.; Liu, Y.-C.; Chang, T.-C. Dynamic Performance Evaluation of Bidirectional Bridgeless Interleaved Totem-Pole Power Factor Correction Boost Converter. Micromachines 2025, 16, 223. https://doi.org/10.3390/mi16020223

Cheng H-C, Jhu W-Y, Liu Y-C, Zheng D-W, Liu Y-C, Chang T-C. Dynamic Performance Evaluation of Bidirectional Bridgeless Interleaved Totem-Pole Power Factor Correction Boost Converter. Micromachines. 2025; 16(2):223. https://doi.org/10.3390/mi16020223

Chicago/Turabian StyleCheng, Hsien-Chie, Wen-You Jhu, Yu-Cheng Liu, Da-Wei Zheng, Yan-Cheng Liu, and Tao-Chih Chang. 2025. "Dynamic Performance Evaluation of Bidirectional Bridgeless Interleaved Totem-Pole Power Factor Correction Boost Converter" Micromachines 16, no. 2: 223. https://doi.org/10.3390/mi16020223

APA StyleCheng, H.-C., Jhu, W.-Y., Liu, Y.-C., Zheng, D.-W., Liu, Y.-C., & Chang, T.-C. (2025). Dynamic Performance Evaluation of Bidirectional Bridgeless Interleaved Totem-Pole Power Factor Correction Boost Converter. Micromachines, 16(2), 223. https://doi.org/10.3390/mi16020223