The Balancing Act in Ferroelectric Transistors: How Hard Can It Be?

Abstract

:1. Introduction

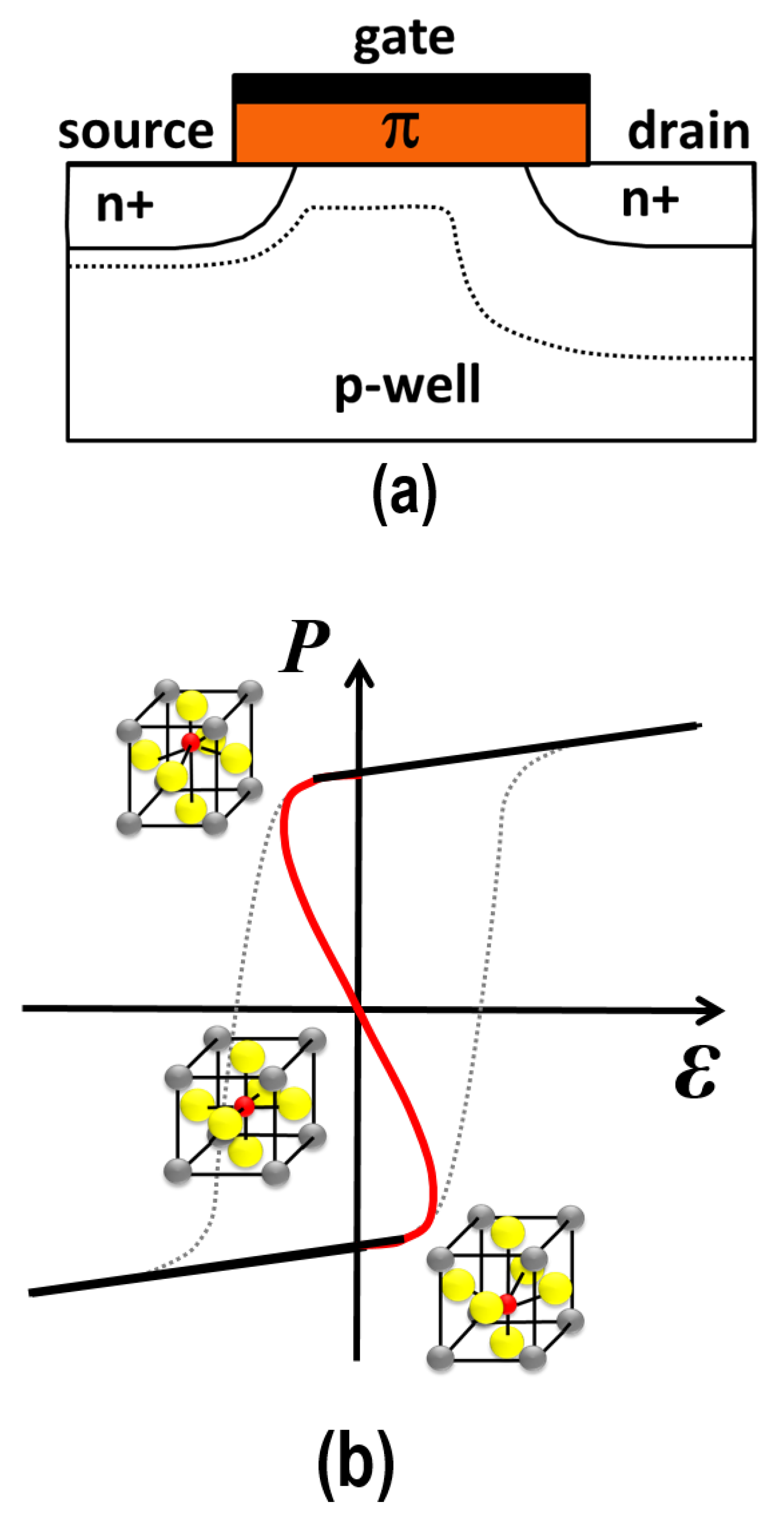

2. The Negative-Capacitance Field-Effect Transistor

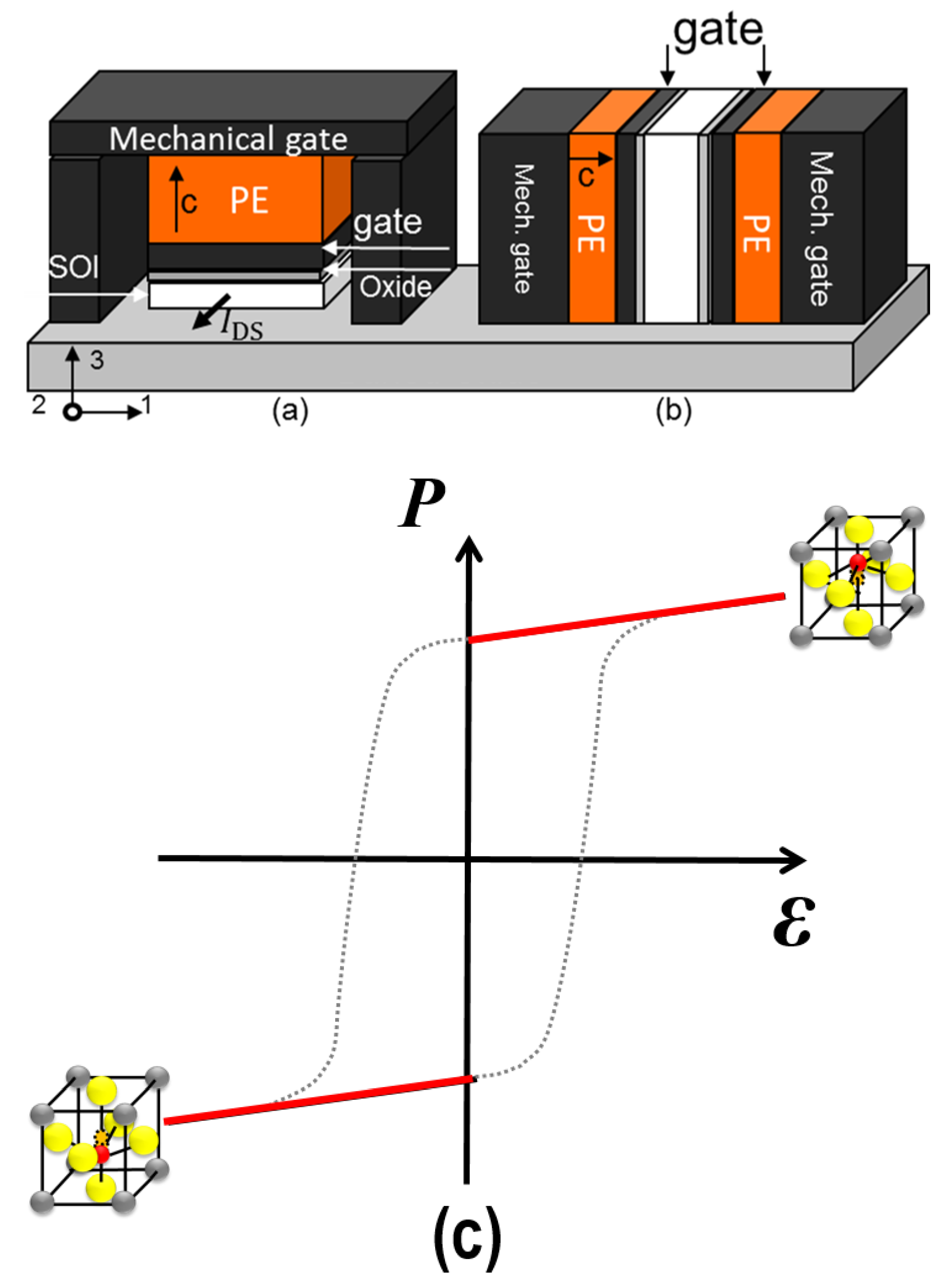

3. The Piezoelectric Field-Effect Transistor

4. Discussion

5. Conclusions

Funding

Acknowledgments

Conflicts of Interest

References

- Moore, G.E. No Exponential is Forever: But “Forever” Can Be Delayed! In Proceedings of the International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13 February 2003; pp. 20–23. [Google Scholar]

- Hisamoto, D.; Lee, W.; Keziekski, J.; Anderson, E.; Takeuchi, H.; Asano, K.; King, T.; Bokor, J.; Hu, C. A Folded-channel MOSFET for Deep-sub-tenth Micron Era. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 6–9 December 1998; pp. 1032–1034. [Google Scholar]

- Saremi, M.; Afzali-Kusha, A.; Mohamadi, S. Ground plane fin-shaped field effect transistor (GP-FinFET): A FinFET for low leakage power circuits. Microelectr. Eng. 2012, 95, 74–82. [Google Scholar] [CrossRef]

- Colinge, J.-P. FinFETs and Other Multi-Gate Transistors; Springer Science+Business Media: New York, NY, USA, 2008. [Google Scholar]

- Faynot, O.; Crisoloveanu, S.; Auberton-Hervé, A.J.; Raynaud, C. Performance and Potential of Ultrathin Accumulation-Mode SIMOX MOSFET’s. EEE Trans. Electr. Dev. 1995, 42, 713–719. [Google Scholar] [CrossRef]

- Welser, J.; Hoyt, J.L.; Gibbons, J.F. Electron mobility enhancement in strained-Si n-type metal-oxide-semiconductor field-effect transistors. IEEE Electr. Dev. Lett. 1994, 15, 100–102. [Google Scholar] [CrossRef]

- Chandrakasan, A.; Brodersen, R. Minimizing power consumption in digital CMOS circuits. Proc. IEEE 1995, 83, 498–523. [Google Scholar] [CrossRef]

- Seabaugh, A.C.; Zhang, Q. Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 2010, 98, 2095–2110. [Google Scholar] [CrossRef]

- Ionescu, A.M.; Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 2011, 479, 329–337. [Google Scholar] [CrossRef] [PubMed]

- Imena Badi, R.M.; Saremi, M.; Vandenberghe, W.G. A Novel PNPN-Like Z-Shaped Tunnel Field-Effect Transistor With Improved Ambipolar Behavior and RF Performance. IEEE Trans. Electr. Dev. 2017, 64, 4752–4758. [Google Scholar] [CrossRef]

- Imena Badi, R.M.; Saremi, M. A Resonant Tunneling Nanowire Field Effect Transistor with Physical Contractions: A Negative Differential Resistance Device for Low Power Very Large Scale Integration Applications. J. Electron. Mater. 2018, 47, 1091–1098. [Google Scholar]

- Gopalakrishnan, K.; Griffin, P.B.; Plummer, J.D. I-MOS: A novel semiconductor device with a subthreshold slope lower than kT/q. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 8–11 December 2002; pp. 289–292. [Google Scholar]

- Salahuddin, S.; Datta, S. Use of Negative Capacitance to Provide Voltage Amplification for Low Power Nanoscale Devices. Nano Lett. 2008, 8, 405–410. [Google Scholar] [CrossRef] [PubMed]

- Salahuddin, S.; Datta, S. Can the subthreshold swing in a classical FET be lowered below 60 mV/decade? In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Van Hemert, T.; Hueting, R.J.E. Active Strain Modulation in Field Effect Devices. In Proceedings of the European Solid-State Device Research Conference (ESSDERC), Bordeaux, France, 17–21 September 2012; pp. 125–128. [Google Scholar]

- Van Hemert, T.; Hueting, R.J.E. Piezoelectric Strain Modulation in FETs. IEEE Trans. Electr. Dev. 2013, 60, 3265–3270. [Google Scholar] [CrossRef]

- Damjanovic, D. Ferroelectric, dielectric and piezoelectric properties of ferroelectric thin films and ceramics. Rep. Prog. Phys. 1998, 61, 1267–1324. [Google Scholar] [CrossRef]

- Setter, N.; Damjanovic, D.; Eng, L.; Fox, G.; Gevorgian, S.; Hong, S.; Kingon, A.; Kohlstedt, H.; Park, N.Y.; Stephenson, G.B.; et al. Ferroelectric thin films: Review of materials, properties, and applications. J. Appl. Phys. 2006, 100, 051606. [Google Scholar] [CrossRef] [Green Version]

- Kimura, M.; Ando, A.; Sakabe, Y. Lead zirconate titanate-based piezo-ceramics. In Advanced Piezoelectric Materials. Science and Technology; Uchino, K., Ed.; Woodhead Publishing Ltd.: Cambridge, UK, 2010; pp. 89–110. [Google Scholar]

- Nguyen, D.M.; Dekkers, J.M.; Houwman, E.P.; Steenwelle, R.J.A.; Wang, X.; Wan, X.; Roelofs, A.; Schmitz-Kempen, T.; Rijnders, A.J.H.M. Misfit strain dependence of ferroelectric and piezoelectric properties of clamped (001) epitaxial Pb(Zr0.52,Ti0.48)O3 thin films. Appl. Phys. Lett. 2011, 99, 252904. [Google Scholar] [CrossRef]

- Landau, L.D.; Khalatnikov, I.M. On the anomalous absorption of sound near a second order phase transition point. Dokl. Akad. Nauk. 1954, 96, 469–472. [Google Scholar]

- Devonshire, A.F. Theory of ferroelectrics. Adv. Phys. 1954, 3, 85–130. [Google Scholar] [CrossRef]

- Khan, A.I.; Bhowmik, D.; Yu, P.; Kim, S.J.; Pan, X.; Ramesh, R.; Salahuddin, S. Experimental evidence of ferroelectric negative capacitance in nanoscale heterostructures. Appl. Phys. Lett. 2011, 99, 11350. [Google Scholar]

- Sze, S.M.; Ng, K.K. Physics of Semiconductor Devices, 3rd ed.; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2007. [Google Scholar]

- Catalan, G.; Jiménez, D.; Gruverman, A. Negative capacitance detected. Nat. Mater. 2015, 14, 137–139. [Google Scholar] [CrossRef] [PubMed]

- Salvatore, G.A.; Bouvet, D.; Ionescu, A.M. Demonstration of Subthreshold Swing Smaller Than 60 mV/decade in Fe-FET with P(VDF-TrFE)/SiO2 Gate Stack. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 14–17 December 2008; pp. 168–170. [Google Scholar]

- Rusu, A.; Salvatore, G.A.; Jiménez, D.; Ionescu, A.M. Metal-ferroelectric-metal-oxide-semiconductor field effect transistor with sub-60 mV/decade subthreshold swing and internal voltage amplification. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 6–8 December 2010; pp. 395–398. [Google Scholar]

- Khan, A.I.; Yeung, C.W.; Hu, C.; Salahuddin, S. Ferroelectric negative capacitance MOSFET: Capacitance tuning & antiferroelectric operation. In Proceedings of the International Electron Device Meeting (IEDM), Washington, DC, USA, 5–7 December 2011; pp. 11.3.1–11.3.4. [Google Scholar]

- Lee, M.H.; Lin, J.-C.; Wei, Y.-T.; Chen, C.-W.; Tu, W.-H.; Zhuang, H.-K.; Tang, M. Ferroelectric Negative Capacitance Hetero-Tunnel Field-Effect-Transistors with Internal Voltage Amplification. In Proceedings of the International Electron Device Meeting (IEDM), Washington, DC, USA, 9–11 December 2013; pp. 104–107. [Google Scholar]

- Cheng, C.H.; Chin, A. Low-Voltage Steep Turn-On pMOSFET Using Ferroelectric High-k Gate Dielectric. IEEE Electr. Dev. Lett. 2014, 35, 274–276. [Google Scholar] [CrossRef]

- Dasgupta, S.; Rajashekar, A.; Majumdar, K.; Agrawal, N.; Razavieh, A.; Trolier-McKinstry, S.; Datta, S. Sub-kT/q Switching in Strong Inversion in PbZr0.52Ti0.48O3 Gated Negative Capacitance FETs. IEEE J. Explor. Solid-State Comput. Devices Circuits 2015, 1, 43–48. [Google Scholar] [CrossRef]

- Li, K.-S.; Chen, P.G.; Lai, T.-Y.; Lin, C.-H.; Cheng, C.-C.; Chen, C.-C.; Wei, Y.-J.; Hou, Y.-F.; Liao, M.-H.; Lee, M.-H.; et al. Sub-60 mV-Swing Negative-Capacitance FinFET without Hysteresis. In Proceedings of the International Electron Device Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 620–623. [Google Scholar]

- Khan, A.I.; Chatterjee, K.; Duarte, J.P.; Lu, Z.; Sachid, A.; Khandelwal, S.; Ramesh, R.; Hu, C.; Salahuddin, S. Negative Capacitance in Short-Channel FinFETs Externally Connected to an Epitaxial Ferroelectric Capacitor. IEEE Electr. Dev. Lett. 2016, 37, 111–114. [Google Scholar] [CrossRef]

- Park, J.H.; Joo, S.K. Sub-kT/q subthreshold slope p-metal-oxide-semiconductor field-effect transistors with single-grained Pb(Zr,Ti)O3 featuring a highly reliable negative capacitance. Appl. Phys. Lett. 2016, 108, 103504. [Google Scholar] [CrossRef]

- Jana, R.J.; Snider, G.L.; Jena, D. On the possibility of sub 60 mV/decade subthreshold switching in piezoelectric gate barrier transistors. Phys. Stat. Sol. 2013, 10, 1469–1472. [Google Scholar] [CrossRef]

- Canon, A.; Jiménez, D. Multidomain ferroelectricity as a limiting factor for voltage amplification in ferroelectric field-effect transistors. Appl. Phys. Lett. 2010, 97, 133509. [Google Scholar] [CrossRef] [Green Version]

- Salahuddin, S. Personal Communication, 2016.

- Rollo, T.; Esseni, D. Influence of Interface Traps on Ferroelectric NC-FETs. IEEE Electr. Dev. Lett. 2018, 39, 1100–1103. [Google Scholar] [CrossRef]

- Hu, C.; Salahuddin, S. 0.2 V Adiabatic NC-FinFET with 0.6 mA/μm ION and 0.1 nA/μm IOFF. In Proceedings of the Berkeley Symp. Energy Efficient Electronic Systems & Steep Transistors Workshop (E3S), Columbus, OH, USA, 21–24 June 2015; pp. 39–40. [Google Scholar]

- Pahwa, G.; Dutta, T.; Agarwal, A.; Chauhan, Y.S. Designing energy efficient and hysteresis free negative capacitance FinFET with negative DIBL and 3.5X ION using compact modeling approach. In Proceedings of the European Solid-State Device Research Conference (ESSDERC), Lausanne, Switzerland, 12–15 September 2016; pp. 41–46. [Google Scholar]

- Auld, B.A. Acoustic Fields and Waves in Solids; Wiley: New York, NY, USA, 1973. [Google Scholar]

- Hueting, R.J.E.; van Hemert, T.; Kaleli, B.; Wolters, R.A.M.; Schmitz, J. On Device Architectures, Subthreshold Swing, and Power Consumption of the Piezoelectric Field-Effect Transistor (π-FET). J. Electr. Dev. Soc. 2015, 3, 149–157. [Google Scholar]

- Starschich, S.; Schenk, T.; Schroeder, U.; Boettger, U. Ferroelectric and piezoelectric properties of Hf1-xZrxO2 and pure ZrO2 films. Appl. Phys. Lett. 2017, 110, 182905. [Google Scholar] [CrossRef]

- Newns, D.; Elmegreen, B.; Liu, X.H.; Martyna, G. A low-voltage high-speed electronic switch based on piezoelectric transduction. J. Appl. Phys. 2012, 111, 084509. [Google Scholar] [CrossRef]

- Synopsys, Inc. Sentaurus Device User Guide; Synopsys, Inc.: Mountain View, CA, USA, 2007. [Google Scholar]

- COMSOL, Inc. Comsol MultiPhysics, 4th ed.; COMSOL, Inc.: Palo Alto, CA, USA, 2011. [Google Scholar]

- Wang, H.; Jiang, X.; Xu, N.; Han, G.; Hao, Y.; Li, S.-S.; Esseni, D. Revised Analysis of Design Options and Minimum Subthreshold Swing in Piezoelectric FinFETs. IEEE Electr. Dev. Lett. 2018, 39, 444–447. [Google Scholar] [CrossRef]

- Kaleli, B.; Hueting, R.J.E.; Nguyen, M.; Wolters, R.A.M. Integration of a Piezoelectric Layer on Si FinFETs for Tunable Strained Device Applications. IEEE Trans. Electr. Dev. 2014, 61, 1929–1935. [Google Scholar] [CrossRef]

- Li, J.; Nagaraj, B.; Liang, H.; Cao, W.; Lee, C.H.; Ramesh, R. Ultrafast polarization switching in thin-film ferroelectrics. Appl. Phys. Lett. 2004, 84, 1174–1176. [Google Scholar] [CrossRef]

- Li, Y.; Yao, K.; Samudra, G.S. Effect of Ferroelectric Damping on Dynamic Characteristics of Negative Capacitance Ferroelectric MOSFET. IEEE Trans. Electr. Dev. 2016, 63, 3636–3641. [Google Scholar] [CrossRef]

- Yuan, Z.C.; Rizwan, S.; Wong, M.; Holland, K.; Anderson, S.; Hook, T.B.; Kienle, D.; Gadelrab, S.; Gudem, P.S.; Vaidyanathan, M. Switching-Speed Limitations of Ferroelectric Negative-Capacitance FETs. IEEE Trans. Electr. Dev. 2016, 63, 4046–4052. [Google Scholar] [CrossRef]

- Kobayashi, M.; Ueyama, N.; Jang, K.; Hiramoto, T. Experimental Study on Polarization-Limited Operation Speed of Negative Capacitance FET with Ferroelectric HfO2. In Proceedings of the 2016 IEEE International Electron Device Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 314–317. [Google Scholar]

- Kirby, P.B.; Su, Q.X.; Komuro, E.; Zhang, Q.; Whatmore, R.W. PZT thin film bulk acoustic wave resonators and filters. In Proceedings of the 2001 IEEE International Frequncy Control Symposium and PDA Exhibition, Seattle, WA, USA, 8 June 2001; pp. 687–694. [Google Scholar]

- Conde, J.; Muralt, P. Characterization of Sol-Gel Pb(Zr0.53Ti0.47)O3 in Thin Film Bulk Acoustic Resonators. IEEE Trans. Ultrason. Ferroelectr. Freq. Cntrol. 2008, 55, 1373–1379. [Google Scholar] [CrossRef] [PubMed]

- Van Hemert, T.; Reimann, K.; Hueting, R.J.E. Extraction of second order piezoelectric parameters in bulk acoustic wave resonators. Appl. Phys. Lett. 2012, 100, 232901. [Google Scholar] [CrossRef]

- Das, S. Two Dimensional Electrostrictive Field Effect Transistor (2D-EFET): A sub-60mV/decade Steep Slope Device with High ON current. Sci. Rep. 2016, 6, 34811. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Nguyen, D.M. Ferroelectric and Piezoelectric Properties of Epitaxial PZT Films and Devices on Silicon. Ph.D. Thesis, University of Twente, Enschede, The Netherlands, 2010. [Google Scholar]

- Jo, J.; Shin, C. Impact of temperature on negative capacitance field-effect transistor. Electr. Lett. 2015, 51, 106–108. [Google Scholar] [CrossRef]

- Nishimura, T.; Xu, L.; Shibayana, S.; Yajima, T.; Misita, S.; Toriumi, A. Ferroelectricity of nondoped thin HfO2 films in TiN/HfO2/TiN stacks. Jpn. J. Appl. Phys. 2016, 55, 08PB01. [Google Scholar] [CrossRef]

| (mV/dec), nMOS | (mV/dec), pMOS | |

|---|---|---|

| Si | 53.1 | 56.9 |

| Ge | 51.3 | 56.5 |

| InSb | 53.1 | 56.4 |

| NC-FET | -FET | |

|---|---|---|

| ++ | + | |

| +/++ | + | |

| ++ | + | |

| - - | - | |

| - - | + |

| NC-FET | -FET | |

|---|---|---|

| Device type | Bulk/Fin*/NW*/2D* | Bulk§/Fin/NW/2D |

| Charge body | required | not important |

| Scaling | very important | important |

| Body/channel type (e.g., Si, Ge, TMD) | important | very important |

| Perovskite ferroics (e.g., PZT) | effective (record) | required |

| “Hard” ferroics (e.g., HfZrO) | effective (concensus) | insufficient |

© 2018 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hueting, R.J.E. The Balancing Act in Ferroelectric Transistors: How Hard Can It Be? Micromachines 2018, 9, 582. https://doi.org/10.3390/mi9110582

Hueting RJE. The Balancing Act in Ferroelectric Transistors: How Hard Can It Be? Micromachines. 2018; 9(11):582. https://doi.org/10.3390/mi9110582

Chicago/Turabian StyleHueting, Raymond J. E. 2018. "The Balancing Act in Ferroelectric Transistors: How Hard Can It Be?" Micromachines 9, no. 11: 582. https://doi.org/10.3390/mi9110582

APA StyleHueting, R. J. E. (2018). The Balancing Act in Ferroelectric Transistors: How Hard Can It Be? Micromachines, 9(11), 582. https://doi.org/10.3390/mi9110582