Architectural and Integration Options for 3D NAND Flash Memories

Abstract

:1. Introduction

- Control gate and channel along the horizontal direction;

- Control gate along the horizontal direction and channel along the vertical direction.

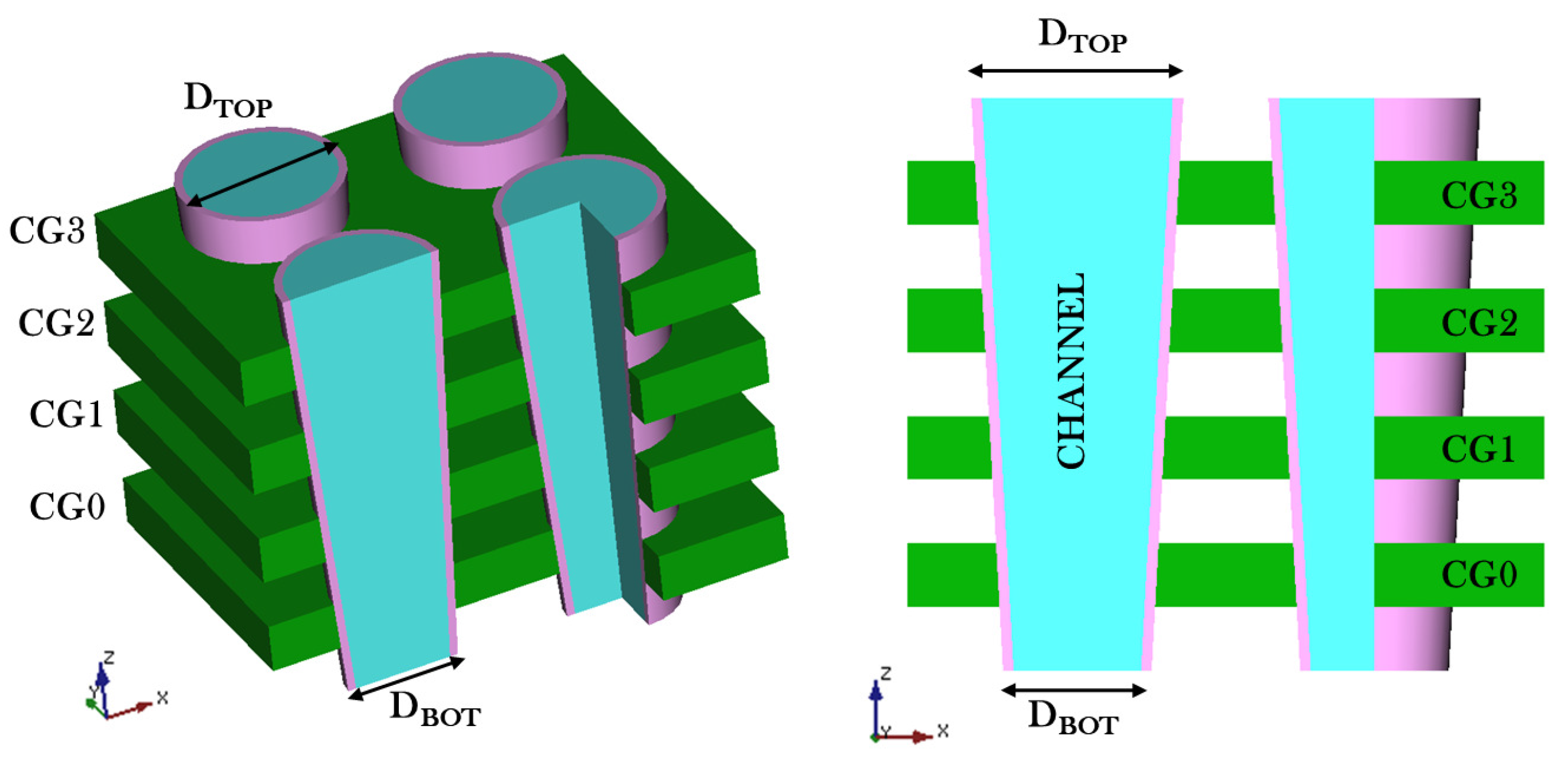

2. 3D Stacked Architecture

3. BiCS Architecture

4. P-BiCS Architecture

- Since SL is located on the stack upper side, it reduces the parasitic resistance and the connection complexity to the metal levels.

- Placing SLS close to the BLS allows controlling accurately the current/voltage characteristics (i.e., especially the cut-off point) of both transistors, improving array functionality.

- Data retention and the threshold voltage margin between the programmed and erased states is enhanced since the fabrication process provides less tunnel oxide degradation.

5. VRAT Architecture

6. VSAT Architecture

7. TCAT Architecture

8. V-NAND Architecture

9. Conclusions

Acknowledgments

Conflicts of Interest

References

- Micheloni, R.; Crippa, L.; Marelli, A. (Eds.) Inside NAND Flash Memories; Springer: Dordrecht, The Netherlands, 2010. [Google Scholar]

- Mizuno, T.; Okumtura, J.; Toriumi, A. Experimental study of threshold voltage fluctuation due to statistical variation of channel dopant number in MOSFET’s. IEEE Trans. Electron Devices 1994, 41, 2216–2221. [Google Scholar] [CrossRef]

- Monzio Compagnoni, C.; Spinelli, A.; Beltrami, S.; Bonanomi, M.; Visconti, A. Cycling Effect on the Random Telegraph Noise Instabilities of NOR and NAND Flash Arrays. IEEE Electron Device Lett. 2008, 29, 941–943. [Google Scholar] [CrossRef]

- Monzio Compagnoni, C.; Spinelli, A.S.; Gusmeroli, R.; Beltrami, S.; Ghetti, A.; Visconti, A. Ultimate Accuracy for the NAND Flash Program Algorithm Due to the Electron Injection Statistics. IEEE Trans. Electron Devices 2008, 55, 2695–2702. [Google Scholar] [CrossRef]

- Whang, S.; Lee, K.; Shin, D.; Kim, B.; Kim, M.; Bin, J.; Han, J.; Kim, S.; Lee, B.; Jung, Y.; et al. Novel 3-dimensional Dual Control-gate with Surrounding Floating-gate (DC-SF) NAND flash cell for 1 Tb file storage application. In Proceedings of the 2010 IEEE International Conference on Electron Devices Meeting (IEDM), San Francisco, CA, USA, 6–8 December 2010; pp. 29.7.1–29.7.4. [Google Scholar]

- Tanaka, T.; Helm, M.; Vali, T.; Ghodsi, R.; Kawai, K.; Park, J.K.; Yamada, S.; Pan, F.; Einaga, Y.; Ghalam, A.; et al. A 768 Gb 3b/cell 3D-floating-gate NAND flash memory. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 31 January–4 February 2016; pp. 142–144. [Google Scholar]

- Park, K.T.; Kang, M.; Hwang, S.; Kim, D.; Cho, H.; Jeong, Y.; Seo, Y.I.; Jang, J.; Kim, H.S.; Lee, Y.T.; et al. A Fully Performance Compatible 45 nm 4-Gigabit Three Dimensional Double-Stacked Multi-Level NAND Flash Memory with Shared Bit-Line Structure. IEEE J. Solid State Circuit 2009, 44, 208–216. [Google Scholar] [CrossRef]

- Fukuzumi, Y.; Katsumata, R.; Kito, M.; Kido, M.; Sato, M.; Tanaka, H.; Nagata, Y.; Matsuoka, Y.; Iwata, Y.; Aochi, H.; et al. Optimal Integration and Characteristics of Vertical Array Devices for Ultra-High Density, Bit-Cost Scalable Flash Memory. In Proceedings of the IEEE International Conference on Electron Devices Meeting (IEDM), Washington, DC, USA, 10–12 December 2007; pp. 449–452. [Google Scholar]

- Tanaka, H.; Kido, M.; Yahashi, K.; Oomura, M.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Sato, M.; Nagata, Y.; Matsuoka, Y.; et al. Bit Cost Scalable Technology with Punch and Plug Process for Ultra High Density Flash Memory. In Proceedings of the 2007 IEEE Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007; pp. 14–15. [Google Scholar]

- Ishiduki, M.; Fukuzumi, Y.; Katsumata, R.; Kito, M.; Kido, M.; Tanaka, H.; Komori, Y.; Nagata, Y.; Fujiwara, T.; Maeda, T.; et al. Optimal device structure for Pipe-shaped BiCS Flash memory for ultra high density storage device with excellent performance and reliability. In Proceedings of the 2009 IEEE International Conference on Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; pp. 1–4. [Google Scholar]

- Katsumata, R.; Kito, M.; Fukuzumi, Y.; Kido, M.; Tanaka, H.; Komori, Y.; Ishiduki, M.; Matsunami, J.; Fujiwara, T.; Nagata, Y.; et al. Pipe-shaped BiCS flash memory with 16 stacked layers and multi-level-cell operation for ultra high density storage devices. In Proceedings of the 2009 Symposium on VLSI Technology, Honolulu, HI, USA, 16–18 June 2009; pp. 136–137. [Google Scholar]

- Im, J.W.; Jeong, W.P.; Kim, D.H.; Nam, S.W.; Shim, D.K.; Choi, M.H.; Yoon, H.J.; Kim, D.H.; Kim, Y.S.; Park, H.W.; et al. A 128 Gb 3b/cell V-NAND flash memory with 1 Gb/s I/O rate. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Kang, D.; Jeong, W.; Kim, C.; Kim, D.H.; Cho, Y.S.; Kang, K.T.; Ryu, J.; Kang, K.M.; Lee, S.; Kim, W.; et al. 256 Gb 3b/cell V-NAND flash memory with 48 stacked WL layers. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 31 January–4 February 2016; pp. 130–131. [Google Scholar]

- Kim, J.; Hong, A.J.; Ogawa, M.; Ma, S.; Song, E.B.; Lin, Y.S.; Han, J.; Chung, U.I.; Wang, K.L. Novel 3-D structure for ultra high density flash memory with VRAT (Vertical-Recess-Array-Transistor) and PIPE (Planarized Integration on the same PlanE). In Proceedings of the 2008 Symposium on VLSI Technology, Honolulu, HI, USA, 17–19 June 2008; pp. 122–123. [Google Scholar]

- Kim, J.; Hong, A.J.; Kim, S.M.; Song, E.B.; Park, J.H.; Han, J.; Choi, S.; Jang, D.; Moon, J.T.; Wang, K.L. Novel Vertical-Stacked-Array-Transistor (VSAT) for ultra-high-density and cost-effective NAND Flash memory devices and SSD (Solid State Drive). In Proceedings of the 2009 Symposium on VLSI Technology, Honolulu, HI, USA, 16–18 June 2009; pp. 186–187. [Google Scholar]

- Jang, J.; Kim, H.S.; Cho, W.; Cho, H.; Kim, J.; Shim, S.I.; Jang, Y.; Jeong, J.H.; Son, B.K.; Kim, D.W.; et al. Vertical cell array using TCAT(Terabit Cell Array Transistor) technology for ultra high density NAND flash memory. In Proceedings of the 2009 Symposium on VLSI Technology, Honolulu, HI, USA, 16–18 June 2009; pp. 192–193. [Google Scholar]

- Micheloni, R. (Ed.) 3D Flash Memories; Springer: Dordrecht, The Netherlands, 2016. [Google Scholar]

- Lai, E.K.; Lue, H.T.; Hsiao, Y.H.; Hsieh, J.Y.; Lu, C.P.; Wang, S.Y.; Yang, L.W.; Yang, T.; Chen, K.C.; Gong, J.; et al. A Multi-Layer Stackable Thin-Film Transistor (TFT) NAND-Type Flash Memory. In Proceedings of the 2006 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [Google Scholar]

- Jung, S.M.; Jang, J.; Cho, W.; Cho, H.; Jeong, J.; Chang, Y.; Kim, J.; Rah, Y.; Son, Y.; Park, J.; et al. Three Dimensionally Stacked NAND Flash Memory Technology Using Stacking Single Crystal Si Layers on ILD and TANOS Structure for Beyond 30 nm Node. In Proceedings of the 2006 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [Google Scholar]

- Suh, K.D.; Suh, B.H.; Um, Y.H.; Kim, J.K.; Choi, Y.J.; Koh, Y.N.; Lee, S.S.; Kwon, S.C.; Choi, B.S.; Yum, J.S.; et al. A 3.3 V 32 Mb NAND Flash Memory with Incremental Step Pulse Programming Scheme. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 15–17 February 1995; pp. 128–129. [Google Scholar]

- Aochi, H. BiCS Flash as a Future 3D Non-Volatile Memory Technology for Ultra High Density Storage Devices. In Proceedings of the IEEE International Memory Workshop, Monterey, CA, USA, 10–14 May 2009; pp. 1–2. [Google Scholar]

- Nishi, Y. (Ed.) Advances in Non-Volatile Memory and Storage Technology; Woodhead Publishing: Cambridge, UK, 2014. [Google Scholar]

- Yanagihara, Y.; Miyaji, K.; Takeuchi, K. Control Gate Length, Spacing and Stacked Layer Number Design for 3D-Stackable NAND Flash Memory. In Proceedings of the IEEE International Memory Workshop, Milan, Italy, 20–23 May 2012; pp. 1–4. [Google Scholar]

- Nitayama, A.; Aochi, H. Bit Cost Scalable (BiCS) flash technology for future ultra high density storage devices. In Proceedings of the VLSI Technology, Systems, and Applications, Hsin Chu, Taiwan, 26–28 April 2010; pp. 130–131. [Google Scholar]

- Komori, Y.; Kido, M.; Kito, M.; Katsumata, R.; Fukuzumi, Y.; Tanaka, H.; Nagata, Y.; Ishiduki, M.; Aochi, H.; Nitayama, A. Disturbless flash memory due to high boost efficiency on BiCS structure and optimal memory film stack for ultra high density storage device. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Maeda, T.; Itagaki, K.; Hishida, T.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Kido, M.; Tanaka, H.; Komori, Y.; Ishiduki, M.; et al. Multi-stacked 1 G cell/layer Pipe-shaped BiCS flash memory. In Proceedings of the 2009 Symposium on VLSI Circuits, Kyoto, Japan, 16–18 June 2009; pp. 22–23. [Google Scholar]

- Hsiao, Y.H.; Lue, H.T.; Chen, W.C.; Tsui, B.Y.; Hsieh, K.Y.; Lu, C.Y. Ultra-High Bit Density 3D NAND Flash-Featuring-Assisted Gate Operation. IEEE Electron Device Lett. 2015, 36, 1015–1017. [Google Scholar] [CrossRef]

- Cho, W.S.; Shim, S.I.; Jang, J.; Cho, H.S.; You, B.K.; Son, B.K.; Kim, K.H.; Shim, J.J.; Park, C.M.; Lim, J.S.; et al. Highly reliable vertical NAND technology with biconcave shaped storage layer and leakage controllable offset structure. In Proceedings of the 2010 Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2010; pp. 173–174. [Google Scholar]

- Elliott, J.; Jung, E.S. Ushering in the 3D Memory Era with V-NAND. In Proceedings of the Flash Memory Summit, Santa Clara, CA, USA, 13–15 August 2013. [Google Scholar]

- Park, K.T.; Byeon, D.S.; Kim, D.H. A world’s first product of three-dimensional vertical NAND Flash memory and beyond. In Proceedings of the 2014 14th Annual Non-Volatile Memory Technology Symposium (NVMTS), Jeju Island, Korea, 27–29 October 2014; pp. 1–5. [Google Scholar]

- Park, K.T.; Nam, S.; Kim, D.; Kwak, P.; Lee, D.; Choi, Y.H.; Choi, M.H.; Kwak, D.H.; Kim, D.H.; Kim, M.S.; et al. Three-Dimensional 128 Gb MLC Vertical nand Flash Memory With 24-WL Stacked Layers and 50 MB/s High-Speed Programming. IEEE J. Solid State Circuit 2015, 50, 204–213. [Google Scholar] [CrossRef]

- Choi, E.S.; Park, S.K. Device considerations for high density and highly reliable 3D NAND flash cell in near future. In Proceedings of the 2012 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 10–13 December 2012; pp. 9.4.1–9.4.4. [Google Scholar]

- Shim, K.S.; Choi, E.S.; Jung, S.W.; Kim, S.H.; Yoo, H.S.; Jeon, K.S.; Joo, H.S.; Oh, J.S.; Jang, Y.S.; Park, K.J.; et al. Inherent Issues and Challenges of Program Disturbance of 3D NAND Flash Cell. In Proceedings of the 2012 4th IEEE International Memory Workshop, Milan, Italy, 20–23 May 2012; pp. 1–4. [Google Scholar]

- Jeong, W.; Im, J.W.; Kim, D.H.; Nam, S.W.; Shim, D.K.; Choi, M.H.; Yoon, H.J.; Kim, D.H.; Kim, Y.S.; Park, H.W.; et al. A 128 Gb 3b/cell V-NAND Flash Memory with 1 Gb/s I/O Rate. IEEE J. Solid State Circuit 2016, 51, 204–212. [Google Scholar]

- Kim, C.; Cho, J.H.; Jeong, W.; Park, I.H.; Park, H.W.; Kim, D.H.; Kang, D.; Lee, S.; Lee, J.S.; Kim, W.; et al. A 512 Gb 3b/cell 64-stacked WL 3D V-NAND flash memory. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 5–9 February 2017; pp. 202–203. [Google Scholar]

| Read | Program | Erase | |

|---|---|---|---|

| BLn | (0.5 V–1 V) | 0/ | Floating |

| BLS (MAT1) | Floating | ||

| Selected WL (MAT1) | 0 V | ||

| Unselected WL (MAT1) | 0 V | ||

| SLS (MAT1) | 0 V | Floating | |

| BLS (MAT2) | 0 V | 0 V | Floating |

| WL (MAT2) | Floating | Floating | Floating |

| SLS (MAT2) | 0 V | 0 V | Floating |

| SL | 0 V | Floating | |

| P-Well | 0 V | 0 V | 18 V–20 V |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Micheloni, R.; Crippa, L.; Zambelli, C.; Olivo, P. Architectural and Integration Options for 3D NAND Flash Memories. Computers 2017, 6, 27. https://doi.org/10.3390/computers6030027

Micheloni R, Crippa L, Zambelli C, Olivo P. Architectural and Integration Options for 3D NAND Flash Memories. Computers. 2017; 6(3):27. https://doi.org/10.3390/computers6030027

Chicago/Turabian StyleMicheloni, Rino, Luca Crippa, Cristian Zambelli, and Piero Olivo. 2017. "Architectural and Integration Options for 3D NAND Flash Memories" Computers 6, no. 3: 27. https://doi.org/10.3390/computers6030027

APA StyleMicheloni, R., Crippa, L., Zambelli, C., & Olivo, P. (2017). Architectural and Integration Options for 3D NAND Flash Memories. Computers, 6(3), 27. https://doi.org/10.3390/computers6030027