Heteroepitaxial Growth of III-V Semiconductors on Silicon

Abstract

:1. Introduction

2. Fundamental Challenges for III-V Heteroepitaxy on Si

2.1. Antiphase Boundary

2.2. Threading Dislocation

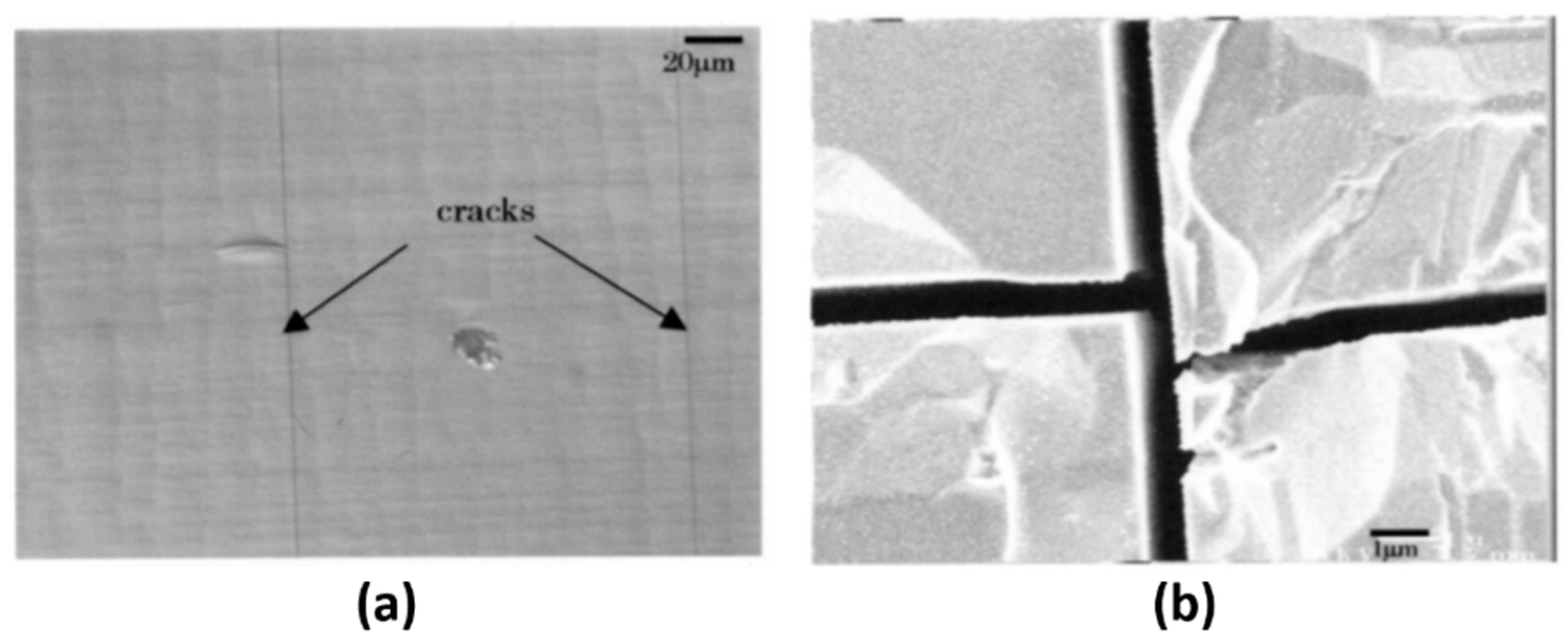

2.3. Thermal Crack

3. Approaches for High-Quality III-V on Silicon

3.1. APB-Free III-V on Silicon

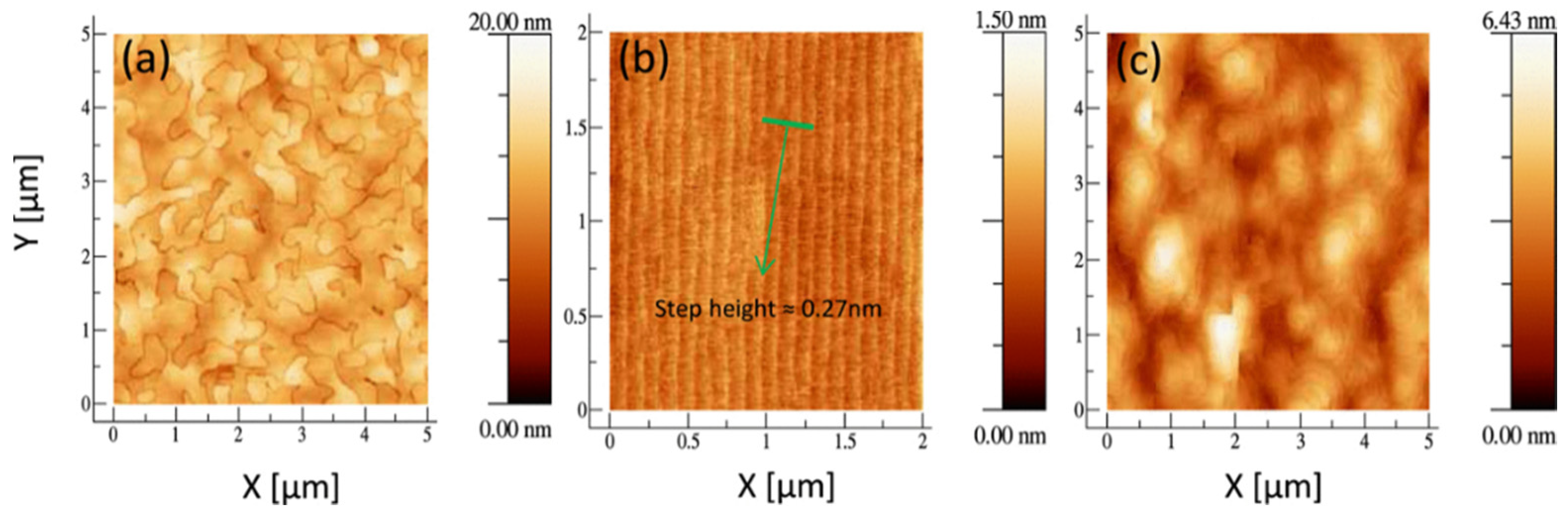

3.1.1. Offcut Silicon Substrates

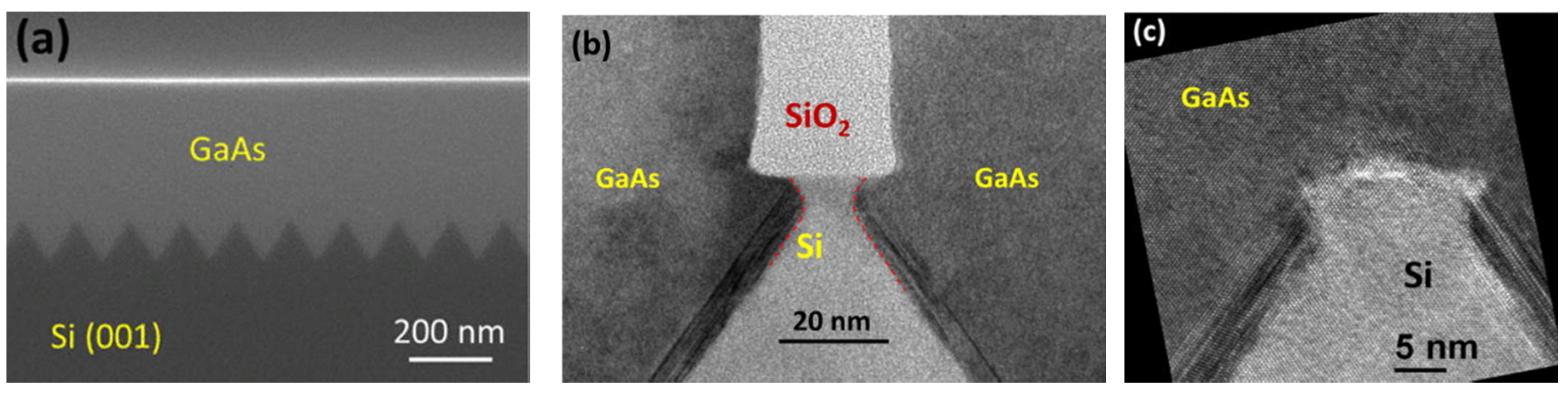

3.1.2. Selective Area Growth

3.1.3. MOCVD/MOVPE-Grown Buffer Layer

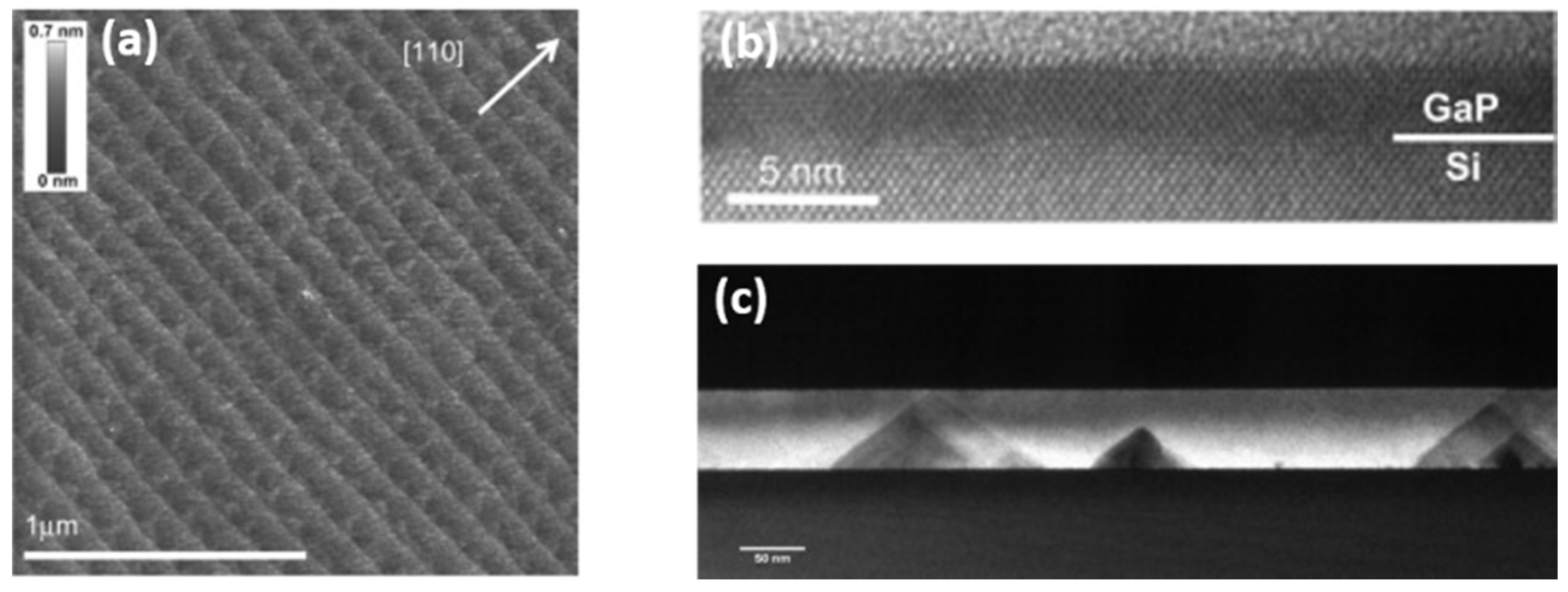

3.1.4. MBE-Grown Buffer Layer

3.2. Reduction of the Dislocations

3.2.1. Nucleation and III-V Buffer Layer

3.2.2. Intermediate Buffer Layer

3.2.3. Epitaxial Lateral Overgrowth

3.2.4. Thermal Annealing

3.2.5. Strained-Layer Superlattices Defect Filter Layer

3.3. Minimizing Thermal Cracks

4. Summary and Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Fisher, G.; Seacrist, M.R.; Standley, R.W. Silicon crystal growth and wafer technologies. Proc. IEEE 2012, 100, 1454–1474. [Google Scholar] [CrossRef]

- Thompson, S.E.; Parthasarathy, S. Moore’s law: The future of Si microelectronics. Mater. Today 2006, 9, 20–25. [Google Scholar] [CrossRef]

- Keyes, R.W. Fundamental limits of silicon. Proc. IEEE 2001, 89, 227–239. [Google Scholar] [CrossRef]

- Shah, A.; Torres, P.; Tscharner, R.; Wyrsch, N.; Keppner, H. Photovoltaic technology: The case for thin-film solar cells. Science 1999, 285, 692–698. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Soref, R. The Past, Present, and Future of Silicon Photonics. IEEE J. Sel. Top. Quantum Electron. 2006, 12, 1678–1687. [Google Scholar] [CrossRef]

- Rong, H.; Liu, A.; Jones, R.; Cohen, O.; Hak, D.; Nicolaescu, R.; Fang, A.; Paniccia, M. An all-silicon Raman laser. Nature 2005, 433, 292–294. [Google Scholar] [CrossRef]

- Rong, H.; Jones, R.; Liu, A.; Cohen, O.; Hak, D.; Fang, A.; Paniccia, M. A continuous-wave Raman silicon laser. Nature 2005, 433, 725–728. [Google Scholar] [CrossRef]

- Hirschman, K.D.; Tsybeskov, L.; Duttagupta, S.P.; Fauchet, P.M. Silicon-based visible light-emitting devices integrated into microelectronic circuits. Nature 1996, 384, 338–341. [Google Scholar] [CrossRef]

- Ng, W.L.; Lourenço, M.A.; Gwilliam, R.M.; Ledain, S.; Shao, G.; Homewood, K.P. An efficient room-temperature silicon-based light-emitting diode. Nature 2001, 410, 192–194. [Google Scholar] [CrossRef]

- Pillai, S.; Catchpole, K.R.; Trupke, T.; Zhang, G.; Zhao, J.; Green, M.A. Enhanced emission from Si-based light-emitting diodes using surface plasmons. Appl. Phys. Lett. 2006, 88, 86–89. [Google Scholar] [CrossRef]

- Zhou, Z.; Yin, B.; Michel, J. On-chip light sources for silicon photonics. Light Sci. Appl. 2015, 4, 1–13. [Google Scholar] [CrossRef]

- Tang, M.; Park, J.S.; Wang, Z.; Chen, S.; Jurczak, P.; Seeds, A.; Liu, H. Integration of III-V lasers on Si for Si photonics. Prog. Quantum Electron. 2019, 66, 1–18. [Google Scholar] [CrossRef]

- Nakamura, S.; Mukai, T.; Senoh, M. High-Power GaN P-N Junction Blue-Light-Emitting Diodes. Jpn. J. Appl. Phys. 1991, 30, L1998–L2001. [Google Scholar] [CrossRef]

- Kneissl, M.; Seong, T.Y.; Han, J.; Amano, H. The emergence and prospects of deep-ultraviolet light-emitting diode technologies. Nat. Photonics 2019, 13, 233–244. [Google Scholar] [CrossRef]

- Kosten, E.D.; Atwater, J.H.; Parsons, J.; Polman, A.; Atwater, H.A. Highly efficient GaAs solar cells by limiting light emission angle. Light Sci. Appl. 2013, 2, 1–6. [Google Scholar] [CrossRef]

- Wu, J.; Chen, S.; Seeds, A.; Liu, H. Quantum dot optoelectronic devices: Lasers, photodetectors and solar cells. J. Phys. D. Appl. Phys. 2015, 48, 363001. [Google Scholar] [CrossRef]

- Mishra, U.K.; Shen, L.; Kazior, T.E.; Wu, Y.F. GaN-based RF power devices and amplifiers. Proc. IEEE 2008, 96, 287–305. [Google Scholar] [CrossRef]

- Asif Khan, M.; Bhattarai, A.; Kuznia, J.N.; Olson, D.T. High electron mobility transistor based on a GaN-AlxGa 1-xN heterojunction. Appl. Phys. Lett. 1993, 63, 1214–1215. [Google Scholar] [CrossRef]

- TANAKA, A. Toxicity of indium arsenide, gallium arsenide, and aluminium gallium arsenide. Toxicol. Appl. Pharmacol. 2004, 198, 405–411. [Google Scholar] [CrossRef]

- Augustin, L.M.; Santos, R.; den Haan, E.; Kleijn, S.; Thijs, P.J.A.; Latkowski, S.; Zhao, D.; Yao, W.; Bolk, J.; Ambrosius, H.; et al. InP-Based Generic Foundry Platform for Photonic Integrated Circuits. IEEE J. Sel. Top. Quantum Electron. 2018, 24, 1–10. [Google Scholar] [CrossRef]

- Smit, M.; Williams, K.; van der Tol, J. Past, present, and future of InP-based photonic integration. APL Photonics 2019, 4, 050901. [Google Scholar] [CrossRef] [Green Version]

- Schaller, R.R. Moore’s law: Past, present and future. IEEE Spectr. 1997, 34, 52–59. [Google Scholar] [CrossRef]

- Kawanami, H. Heteroepitaxial technologies of III-V on Si. Sol. Energy Mater. Sol. Cells 2001, 66, 479–486. [Google Scholar] [CrossRef]

- Li, Q.; Lau, K.M. Epitaxial growth of highly mismatched III-V materials on (001) silicon for electronics and optoelectronics. Prog. Cryst. Growth Charact. Mater. 2017, 63, 105–120. [Google Scholar] [CrossRef] [Green Version]

- Bolkhovityanov, Y.B.; Pchelyakov, O.P. GaAs epitaxy on Si substrates: Modern status of research and engineering. Physics-Uspekhi 2008, 51, 437–456. [Google Scholar] [CrossRef]

- Kunert, B.; Mols, Y.; Baryshniskova, M.; Waldron, N.; Schulze, A.; Langer, R. How to control defect formation in monolithic III/V hetero-epitaxy on (100) Si? A critical review on current approaches. Semicond. Sci. Technol. 2018, 33, 093002. [Google Scholar] [CrossRef]

- Biegelsen, D.K.; Ponce, F.A.; Smith, A.J.; Tramontana, J.C. INITIAL STAGES OF EPITAXIAL GROWTH OF GaAs ON (100) SILICON. Mater. Res. Soc. Symp. Proc. 1986, 67, 45–50. [Google Scholar] [CrossRef]

- Fang, S.F.; Adomi, K.; Iyer, S.; Morkoç, H.; Zabel, H.; Choi, C.; Otsuka, N. Gallium arsenide and other compound semiconductors on silicon. J. Appl. Phys. 1990, 68. [Google Scholar] [CrossRef]

- Strite, S.; Morkoç, H. GaN, AlN, and InN: A review. J. Vac. Sci. Technol. B Microelectron. Nanom. Struct. 1992, 10, 1237. [Google Scholar] [CrossRef]

- Choudhury, D. 3D integration technologies for emerging microsystems. IEEE MTT-S Int. Microw. Symp. Dig. 2010, 1–4. [Google Scholar] [CrossRef]

- Jalali, B.; Fathpour, S. Silicon Photonics. J. Light. Technol. 2006, 24, 4600–4615. [Google Scholar] [CrossRef]

- Hoke, W.E.; Chelakara, R.V.; Bettencourt, J.P.; Kazior, T.E.; LaRoche, J.R.; Kennedy, T.D.; Mosca, J.J.; Torabi, A.; Kerr, A.J.; Lee, H.-S.; et al. Monolithic integration of silicon CMOS and GaN transistors in a current mirror circuit. J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 2012, 30, 02B101. [Google Scholar] [CrossRef]

- Liu, W.K.; Lubyshev, D.; Fastenau, J.M.; Wu, Y.; Bulsara, M.T.; Fitzgerald, E.A.; Urteaga, M.; Ha, W.; Bergman, J.; Brar, B.; et al. Monolithic integration of InP-based transistors on Si substrates using MBE. J. Cryst. Growth 2009, 311, 1979–1983. [Google Scholar] [CrossRef]

- Deshpande, V.; Djara, V.; O’Connor, E.; Hashemi, P.; Morf, T.; Balakrishnan, K.; Caimi, D.; Sousa, M.; Fompeyrine, J.; Czornomaz, L. Three-dimensional monolithic integration of III–V and Si(Ge) FETs for hybrid CMOS and beyond. Jpn. J. Appl. Phys. 2017, 56, 04CA05. [Google Scholar] [CrossRef] [Green Version]

- Kazior, T.E. Beyond Cmos: Heterogeneous integration of III-V devices, RF MEMS and other dissimilar materials/devices with Si CMOS to create intelligent microsystems. Philos. Trans. R. Soc. A Math. Phys. Eng. Sci. 2014, 372. [Google Scholar] [CrossRef] [Green Version]

- Moutanabbir, O.; Gösele, U. Heterogeneous Integration of Compound Semiconductors. Annu. Rev. Mater. Res. 2010, 40, 469–500. [Google Scholar] [CrossRef] [Green Version]

- Roelkens, G.; Van Campenhout, J.; Brouckaert, J.; Van Thourhout, D.; Baets, R.; Romeo, P.R.; Regreny, P.; Kazmierczak, A.; Seassal, C.; Letartre, X.; et al. III-V/Si photonics by die-to-wafer bonding. Mater. Today 2007, 10, 36–43. [Google Scholar] [CrossRef]

- Cheng, Y.T.; Lin, L.; Najafi, K. Localized silicon fusion and eutectic bonding for MEMS fabrication and packaging. J. Microelectromechanical Syst. 2000, 9, 3–8. [Google Scholar] [CrossRef]

- Keyvaninia, S.; Muneeb, M.; Stanković, S.; Van Veldhoven, P.J.; Van Thourhout, D.; Roelkens, G. Ultra-thin DVS-BCB adhesive bonding of III-V wafers, dies and multiple dies to a patterned silicon-on-insulator substrate. Opt. Mater. Express 2013, 3, 35. [Google Scholar] [CrossRef] [Green Version]

- Stankovic, S.; Jones, R.; Sysak, M.N.; Heck, J.M.; Roelkens, G.; Van Thourhout, D. Hybrid III–V/Si Distributed-Feedback Laser Based on Adhesive Bonding. IEEE Photonics Technol. Lett. 2012, 24, 2155–2158. [Google Scholar] [CrossRef] [Green Version]

- Sparks, D.; Queen, G.; Weston, R.; Woodward, G.; Putty, M.; Jordan, L.; Zarabadi, S.; Jayakar, K. Wafer-to-wafer bonding of nonplanarized MEMS surfaces using solder. J. Micromechanics Microengineering 2001, 11, 630–634. [Google Scholar] [CrossRef]

- Pasquariello, D.; Hjort, K. Plasma-assisted InP-to-Si low temperature wafer bonding. IEEE J. Sel. Top. Quantum Electron. 2002, 8, 118–131. [Google Scholar] [CrossRef]

- Yokoyama, M.; Iida, R.; Ikku, Y.; Kim, S.; Takagi, H.; Yasuda, T.; Yamada, H.; Ichikawa, O.; Fukuhara, N.; Hata, M.; et al. Formation of III–V-on-insulator structures on Si by direct wafer bonding. Semicond. Sci. Technol. 2013, 28, 094009. [Google Scholar] [CrossRef]

- Tanabe, K.; Watanabe, K.; Arakawa, Y. III-V/Si hybrid photonic devices by direct fusion bonding. Sci. Rep. 2012, 2, 349. [Google Scholar] [CrossRef]

- Chung, T.R.; Yang, L.; Hosoda, N.; Takagi, H.; Suga, T. Wafer direct bonding of compound semiconductors and silicon at room temperature by the surface activated bonding method. Appl. Surf. Sci. 1997, 117–118, 808–812. [Google Scholar] [CrossRef]

- Ren, B.; Hou, Y.; Liang, Y. Research progress of III–V laser bonding to Si. J. Semicond. 2016, 37, 124001. [Google Scholar] [CrossRef]

- Fang, A.W.; Park, H.; Cohen, O.; Jones, R.; Paniccia, M.J.; Bowers, J.E. Electrically pumped hybrid AlGaInAs-silicon evanescent laser. Opt. Express 2006, 14, 9203. [Google Scholar] [CrossRef]

- Chen, S.; Li, W.; Wu, J.; Jiang, Q.; Tang, M.; Shutts, S.; Elliott, S.N.; Sobiesierski, A.; Seeds, A.J.; Ross, I.; et al. Electrically pumped continuous-wave III-V quantum dot lasers on silicon. Nat. Photonics 2016, 10, 307–311. [Google Scholar] [CrossRef]

- Wang, Y.; Chen, S.; Yu, Y.; Zhou, L.; Liu, L.; Yang, C.; Liao, M.; Tang, M.; Liu, Z.; Wu, J.; et al. Monolithic quantum-dot distributed feedback laser array on silicon. Optica 2018, 5, 528. [Google Scholar] [CrossRef]

- Wan, Y.; Zhang, S.; Norman, J.C.; Kennedy, M.; He, W.; Tong, Y.; Shang, C.; He, J.; Tsang, H.K.; Gossard, A.C.; et al. Directly Modulated Single-Mode Tunable Quantum Dot Lasers at 1.3 µm. Laser Photon. Rev. 2020, 14, 1900348. [Google Scholar] [CrossRef]

- Liu, S.; Wu, X.; Jung, D.; Norman, J.C.; Kennedy, M.J.; Tsang, H.K.; Gossard, A.C.; Bowers, J.E. High-channel-count 20 GHz passively mode-locked quantum dot laser directly grown on Si with 41 Tbit/s transmission capacity. Optica 2019, 6, 128. [Google Scholar] [CrossRef] [Green Version]

- Wu, J.; Tang, M.; Liu, H. III-V Quantum dot Lasers Epitaxially Grown on Si Substrates; Elsevier Inc.: Amsterdam, The Netherlands, 2019; ISBN 9780128141625. [Google Scholar]

- Liao, M.; Chen, S.; Park, J.-S.; Seeds, A.; Liu, H. III–V quantum-dot lasers monolithically grown on silicon. Semicond. Sci. Technol. 2018, 33, 123002. [Google Scholar] [CrossRef]

- Jones, R.; Doussiere, P.; Driscoll, J.B.; Lin, W.; Yu, H.; Akulova, Y.; Komljenovic, T.; Bowers, J.E. Heterogeneously Integrated InP/Silicon Photonics: Fabricating fully functional transceivers. IEEE Nanotechnol. Mag. 2019, 13, 17–26. [Google Scholar] [CrossRef]

- Norman, J.C.; Jung, D.; Wan, Y.; Bowers, J.E. Perspective: The future of quantum dot photonic integrated circuits. APL Photonics 2018, 3, 030901. [Google Scholar] [CrossRef] [Green Version]

- Georgakilas, A.; Stoemenos, J.; Tsagaraki, K.; Komninou, P.; Flevaris, N.; Panayotatos, P.; Christou, A. Generation and annihilation of antiphase domain boundaries in GaAs on Si grown by molecular beam epitaxy. J. Mater. Res. 1993, 8, 1908–1921. [Google Scholar] [CrossRef]

- Ishida, M.; Ueda, T.; Tanaka, T.; Ueda, D. GaN on Si Technologies for Power Switching Devices. IEEE Trans. Electron Devices 2013, 60, 3053–3059. [Google Scholar] [CrossRef]

- Li, G.; Wang, W.; Yang, W.; Lin, Y.; Wang, H.; Lin, Z.; Zhou, S. GaN-based light-emitting diodes on various substrates: A critical review. Reports Prog. Phys. 2016, 79, 056501. [Google Scholar] [CrossRef]

- Krost, A.; Dadgar, A. GaN-based optoelectronics on silicon substrates. Mater. Sci. Eng. B Solid-State Mater. Adv. Technol. 2002, 93, 77–84. [Google Scholar] [CrossRef]

- Volz, K.; Ludewig, P.; Stolz, W. Monolithic integration of lattice-matched Ga(NAsP)-based laser structures on CMOS-compatible Si (001) wafers for Si-photonics applications. In Semiconductors and Semimetals; Elsevier Inc.: Amsterdam, The Netherlands, 2019; Volume 101, pp. 201–227. ISBN 9780128188576. [Google Scholar]

- Kunert, B.; Volz, K.; Stolz, W. Dilute nitride Ga(NAsP)/GaP-heterostructures: Toward a material development for novel optoelectronic functionality on Si-substrate. Phys. Status Solidi 2007, 244, 2730–2739. [Google Scholar] [CrossRef]

- Liebich, S.; Zimprich, M.; Beyer, A.; Lange, C.; Franzbach, D.J.; Chatterjee, S.; Hossain, N.; Sweeney, S.J.; Volz, K.; Kunert, B.; et al. Laser operation of Ga(NAsP) lattice-matched to (001) silicon substrate. Appl. Phys. Lett. 2011, 99, 071109. [Google Scholar] [CrossRef] [Green Version]

- Rolland, A.; Pedesseau, L.; Even, J.; Almosni, S.; Robert, C.; Cornet, C.; Jancu, J.M.; Benhlal, J.; Durand, O.; Corre, A.L.; et al. Design of a lattice-matched III–V–N/Si photovoltaic tandem cell monolithically integrated on silicon substrate. Opt. Quantum Electron. 2014, 46, 1397–1403. [Google Scholar] [CrossRef] [Green Version]

- Jain, N.; Hudait, M.K. III–V Multijunction Solar Cell Integration with Silicon: Present Status, Challenges and Future Outlook. Energy Harvest. Syst. 2014, 1, 121–145. [Google Scholar] [CrossRef]

- Almosni, S.; Robert, C.; Nguyen Thanh, T.; Cornet, C.; Létoublon, A.; Quinci, T.; Levallois, C.; Perrin, M.; Kuyyalil, J.; Pedesseau, L.; et al. Evaluation of InGaPN and GaAsPN materials lattice-matched to Si for multi-junction solar cells. J. Appl. Phys. 2013, 113. [Google Scholar] [CrossRef]

- Wegele, T.; Beyer, A.; Ludewig, P.; Rosenow, P.; Duschek, L.; Jandieri, K.; Tonner, R.; Stolz, W.; Volz, K. Interface morphology and composition of Ga(NAsP) quantum well structures for monolithically integrated LASERs on silicon substrates. J. Phys. D. Appl. Phys. 2016, 49, 075108. [Google Scholar] [CrossRef]

- Ludewig, P.; Reinhard, S.; Jandieri, K.; Wegele, T.; Beyer, A.; Tapfer, L.; Volz, K.; Stolz, W. MOVPE growth studies of Ga(NAsP)/(BGa)(AsP) multi quantum well heterostructures (MQWH) for the monolithic integration of laser structures on (001) Si-substrates. J. Cryst. Growth 2016, 438, 63–69. [Google Scholar] [CrossRef]

- Henini, M. Dilute Nitride Semiconductors; Elsevier: Amsterdam, The Netherlands, 2005; ISBN 9780080445021. [Google Scholar]

- Erol, A. Dilute III-V Nitride Semiconductors and Material Systems; Kakeshita, T., Fukuda, T., Saxena, A., Planes, A., Eds.; Springer Series in Materials Science; Springer: Berlin/Heidelberg, Germany, 2008; Volume 105, ISBN 978-3-642-20942-0. [Google Scholar]

- Kroemer, H. Polar-on-nonpolar epitaxy. J. Cryst. Growth 1987, 81, 193–204. [Google Scholar] [CrossRef]

- Hamers, R.J.; Tromp, R.M.; Demuth, J.E. Scanning tunneling microscopy of Si(001). Phys. Rev. B 1986, 34, 5343–5357. [Google Scholar] [CrossRef]

- Zandvliet, H.J.W.; Elswijk, H.B.; van Loenen, E.J.; Dijkkamp, D. Equilibrium structure of monatomic steps on vicinal Si(001). Phys. Rev. B 1992, 45, 5965–5968. [Google Scholar] [CrossRef] [Green Version]

- Zandvliet, H.J.W.; Elswijk, H.B. Morphology of monatomic step edges on vicinal Si(001). Phys. Rev. B 1993, 48, 14269–14275. [Google Scholar] [CrossRef] [Green Version]

- Chadi, D.J. Stabilities of single-layer and bilayer steps on Si(001) surfaces. Phys. Rev. Lett. 1987, 59, 1691–1694. [Google Scholar] [CrossRef]

- Kunert, B.; Németh, I.; Reinhard, S.; Volz, K.; Stolz, W. Si (001) surface preparation for the antiphase domain free heteroepitaxial growth of GaP on Si substrate. Thin Solid Films 2008, 517, 140–143. [Google Scholar] [CrossRef]

- Matthews, J.W.; Blakeslee, A.E. Defects in epitaxial multilayers: I. Misfit dislocations. J. Cryst. Growth 1974, 27, 118–125. [Google Scholar] [CrossRef]

- Matthews, J.W.; Blakeslee, A.E. Defects in epitaxial multilayers: II. Dislocation pile-ups, threading dislocations, slip lines and cracks. J. Cryst. Growth 1975, 29, 273–280. [Google Scholar] [CrossRef]

- Van Der Merwe, J.H. Crystal Interfaces. Part II. Finite Overgrowths. J. Appl. Phys. 1963, 34, 123–127. [Google Scholar] [CrossRef]

- Stirland, D.J. Quantitative defect etching of GaAs on Si: Is it possible? Appl. Phys. Lett. 1988, 53, 2432–2434. [Google Scholar] [CrossRef]

- Clawson, A. Guide to references on III–V semiconductor chemical etching. Mater. Sci. Eng. R Rep. 2001, 31, 1–438. [Google Scholar] [CrossRef]

- Ayers, J.E. The measurement of threading dislocation densities in semiconductor crystals by X-ray diffraction. J. Cryst. Growth 1994, 135, 71–77. [Google Scholar] [CrossRef]

- Gay, P.; Hirsch, P.; Kelly, A. The estimation of dislocation densities in metals from X-ray data. Acta Metall. 1953, 1, 315–319. [Google Scholar] [CrossRef]

- Oh, S.; Jun, D.H.; Shin, K.W.; Choi, I.H.; Jung, S.H.; Choi, J.H.; Park, W.; Park, Y.; Yoon, E. Control of Crack Formation for the Fabrication of Crack-Free and Self-Isolated High-Efficiency Gallium Arsenide Photovoltaic Cells on Silicon Substrate. IEEE J. Photovolt. 2016, 6, 1031–1035. [Google Scholar] [CrossRef]

- Ye, T.; Suo, Z.; Evans, A.G. Thin film cracking and the roles of substrate and interface. Int. J. Solids Struct. 1992, 29, 2639–2648. [Google Scholar] [CrossRef]

- Griffits, A.A. VI. The phenomena of rupture and flow in solids. R. Soc. 1921, 221, 163–198. [Google Scholar] [CrossRef] [Green Version]

- Yamaguchi, M.; Tachikawa, M.; Sugo, M.; Kondo, S.; Itoh, Y. Analysis for dislocation density reduction in selective area grown GaAs films on Si substrates. Appl. Phys. Lett. 1990, 56, 27–29. [Google Scholar] [CrossRef]

- Sakai, S. New method to relax thermal stress in GaAs grown on Si substrates. Appl. Phys. Lett. 1987, 51, 1069–1071. [Google Scholar] [CrossRef]

- Ayers, J. Heteroepitaxy of Semiconductors; CRC Press: Boca Raton, FL, USA, 2007; ISBN 978-0-8493-7195-0. [Google Scholar]

- Hayafuji, N.; Kizuki, H.; Miyashita, M.; Kadoiwa, K.; Nishimura, T.; Ogasawara, N.; Kumabe, H.; Murotani, T.; Tada, A. Crack Propagation and Mechanical Fracture in GaAs-on-Si. Jpn. J. Appl. Phys. 1991, 30, 459–463. [Google Scholar] [CrossRef]

- Murray, R.T.; Kiely, C.J.; Hopkinson, M. Crack formation in III-V epilayers grown under tensile strain on InP(001) substrates. Philos. Mag. A 1996, 74, 383–393. [Google Scholar] [CrossRef]

- Murray, R.T.; Kiely, C.J.; Hopkinson, M. General characteristics of crack arrays in epilayers grown under tensile strain. Semicond. Sci. Technol. 2000, 15, 325–330. [Google Scholar] [CrossRef]

- Ackaert, A.; Buydens, L.; Lootens, D.; Van Daele, P.; Demeester, P. Crack formation and thermal stress relaxation of GaAs on Si growth by metalorganic vapor phase epitaxy. Appl. Phys. Lett. 1989, 55, 2187–2189. [Google Scholar] [CrossRef]

- Fox, B.A.; Jesser, W.A. Investigation of the asymmetric misfit dislocation morphology in epitaxial layers with the zinc-blende structure. J. Appl. Phys. 1990, 68, 2739–2746. [Google Scholar] [CrossRef]

- Abrahams, M.S.; Blanc, J.; Buiocchi, C.J. Like-sign asymmetric dislocations in zinc-blende structure. Appl. Phys. Lett. 1972, 21, 185–186. [Google Scholar] [CrossRef]

- Yastrubchak, O.; Domagała, J.Z.; Wosiński, T.; Kudła, A.; Regiński, K. Anisotropic strain relaxation in lattice-mismatched III-V epitaxial layers. Phys. status solidi 2005, 2, 1943–1947. [Google Scholar] [CrossRef]

- Olsen, G.H.; Abrahams, M.S.; Zamerowski, T.J. Asymmetric Cracking in III–V Compounds. J. Electrochem. Soc. 1974, 121, 1650. [Google Scholar] [CrossRef]

- Yonenaga, I.; Sumino, K. Behaviour of dislocations in GaAs revealed by etch pit technique and X-ray topography. J. Cryst. Growth 1993, 126, 19–29. [Google Scholar] [CrossRef]

- Yang, V.K.; Groenert, M.; Leitz, C.W.; Pitera, A.J.; Currie, M.T.; Fitzgerald, E.A. Crack formation in GaAs heteroepitaxial films on Si and SiGe virtual substrates. J. Appl. Phys. 2003, 93, 3859–3865. [Google Scholar] [CrossRef]

- Sugo, M.; Uchida, N.; Yamamoto, A.; Nishioka, T.; Yamaguchi, M. Residual strains in heteroepitaxial III-V semiconductor films on Si(100) substrates. J. Appl. Phys. 1989, 65, 591–595. [Google Scholar] [CrossRef]

- Uppal, P.N.; Kroemer, H. Molecular beam epitaxial growth of GaAs on Si(211). J. Appl. Phys. 1985, 58, 2195–2203. [Google Scholar] [CrossRef]

- Kawabe, M.; Ueda, T. Molecular beam epitaxy of controlled single domain gaas on si (100). Jpn. J. Appl. Phys. 1986, 25, L285–L287. [Google Scholar] [CrossRef]

- Morkoc, H.; Peng, C.K.; Henderson, T.; Kopp, W.; Fischer, R.; Erickson, L.P.; Longerbone, M.D.; Youngman, R.C. High-quality GaAs MESFET’s grown on silicon substrates by molecular-beam epitaxy. IEEE Electron Device Lett. 1985, 6, 381–383. [Google Scholar] [CrossRef]

- Wang, W.I. Molecular beam epitaxial growth and material properties of GaAs and AlGaAs on Si (100). Appl. Phys. Lett. 1984, 44, 1149–1151. [Google Scholar] [CrossRef]

- Alerhand, O.L.; Berker, A.N.; Joannopoulos, J.D.; Vanderbilt, D.; Hamers, R.J.; Demuth, J.E. Finite-temperature phase diagram of vicinal Si(100) surfaces. Phys. Rev. Lett. 1990, 64, 2406–2409. [Google Scholar] [CrossRef]

- Pehlke, E.; Tersoff, J. Phase diagram of vicinal Si(001) surfaces. Phys. Rev. Lett. 1991, 67, 1290–1293. [Google Scholar] [CrossRef]

- Akiyama, M.; Kawarada, Y.; Kaminishi, K. Growth of single domain gaas layer on (100)-oriented si substrate by mocvd. Jpn. J. Appl. Phys. 1984, 23, 843–845. [Google Scholar] [CrossRef]

- Kaplan, R. LEED study of the stepped surface of vicinal Si (100). Surf. Sci. 1980, 93, 145–158. [Google Scholar] [CrossRef]

- Akiyama, M.; Kawarada, Y.; Ueda, T.; Nishi, S.; Kaminishi, K. Growth of high quality GaAs layers on Si substrates by MOCVD. J. Cryst. Growth 1986, 77, 490–497. [Google Scholar] [CrossRef]

- Griffith, J.E.; Kubby, J.A.; Wierenga, P.E.; Becker, R.S.; Vickers, J.S. Tunneling microscopy of steps on vicinal Ge(001) and Si(001) surfaces. J. Vac. Sci. Technol. A Vac. Surf. Film. 1988, 6, 493–496. [Google Scholar] [CrossRef]

- Bringans, R.D.; Biegelsen, D.K.; Swartz, L.-E. Atomic-step rearrangement on Si(100) by interaction with arsenic and the implication for GaAs-on-Si epitaxy. Phys. Rev. B 1991, 44, 3054–3063. [Google Scholar] [CrossRef]

- Georgakilas, A.; Papavassiliou, C.; Constantinidis, G.; Tsagaraki, K.; Krasny, H.; Löchtermann, E.; Panayotatos, P. Effects of Si(100) tilting angle and prelayer conditions on GaAs/Si heterostructures. Appl. Surf. Sci. 1996, 102, 67–72. [Google Scholar] [CrossRef]

- Fischer, R.; Morkoç, H.; Neumann, D.A.; Zabel, H.; Choi, C.; Otsuka, N.; Longerbone, M.; Erickson, L.P. Material properties of high-quality GaAs epitaxial layers grown on Si substrates. J. Appl. Phys. 1986, 60, 1640–1647. [Google Scholar] [CrossRef]

- Ting, S.M.; Fitzgerald, E.A. Metal-organic chemical vapor deposition of single domain GaAs on Ge/GexSi1−x/Si and Ge substrates. J. Appl. Phys. 2000, 87, 2618–2628. [Google Scholar] [CrossRef]

- Tromp, R.M.; Hamers, R.J.; Demuth, J.E. Si(001) Dimer Structure Observed with Scanning Tunneling Microscopy. Phys. Rev. Lett. 1985, 55, 1303–1306. [Google Scholar] [CrossRef]

- Paladugu, M.; Merckling, C.; Loo, R.; Richard, O.; Bender, H.; Dekoster, J.; Vandervorst, W.; Caymax, M.; Heyns, M. Site selective integration of III-V materials on Si for nanoscale logic and photonic devices. Cryst. Growth Des. 2012, 12, 4696–4702. [Google Scholar] [CrossRef]

- Han, Y.; Xue, Y.; Lau, K.M. Selective lateral epitaxy of dislocation-free InP on silicon-on-insulator. Appl. Phys. Lett. 2019, 114, 192105. [Google Scholar] [CrossRef]

- Park, J.-S.; Bai, J.; Curtin, M.; Adekore, B.; Carroll, M.; Lochtefeld, A. Defect reduction of selective Ge epitaxy in trenches on Si(001) substrates using aspect ratio trapping. Appl. Phys. Lett. 2007, 90, 052113. [Google Scholar] [CrossRef]

- Li, J.Z.; Bai, J.; Park, J.S.; Adekore, B.; Fox, K.; Carroll, M.; Lochtefeld, A.; Shellenbarger, Z. Defect reduction of GaAs epitaxy on Si (001) using selective aspect ratio trapping. Appl. Phys. Lett. 2007, 91, 1–4. [Google Scholar] [CrossRef]

- Wang, G.; Leys, M.R.; Loo, R.; Richard, O.; Bender, H.; Waldron, N.; Brammertz, G.; Dekoster, J.; Wang, W.; Seefeldt, M.; et al. Selective area growth of high quality InP on Si (001) substrates. Appl. Phys. Lett. 2010, 97, 1–4. [Google Scholar] [CrossRef]

- Fitzgerald, E.A.; Chand, N. Epitaxial necking in GaAs grown on pre-pattemed Si substrates. J. Electron. Mater. 1991, 20, 839–853. [Google Scholar] [CrossRef]

- Orzali, T.; Vert, A.; O’Brien, B.; Herman, J.L.; Vivekanand, S.; Hill, R.J.W.; Karim, Z.; Papa Rao, S.S. GaAs on Si epitaxy by aspect ratio trapping: Analysis and reduction of defects propagating along the trench direction. J. Appl. Phys. 2015, 118, 105307. [Google Scholar] [CrossRef] [Green Version]

- Li, Q.; Jiang, H.; Lau, K.M. Coalescence of planar GaAs nanowires into strain-free three-dimensional crystals on exact (001) silicon. J. Cryst. Growth 2016, 454, 19–24. [Google Scholar] [CrossRef]

- Li, Q.; Ng, K.W.; Lau, K.M. Growing antiphase-domain-free GaAs thin films out of highly ordered planar nanowire arrays on exact (001) silicon. Appl. Phys. Lett. 2015, 106, 072105. [Google Scholar] [CrossRef] [Green Version]

- Zhu, S.; Shi, B.; Li, Q.; Lau, K.M. Room-temperature electrically-pumped 1.5 μm InGaAs/InAlGaAs laser monolithically grown on on-axis (001) Si. Opt. Express 2018, 26, 14514. [Google Scholar] [CrossRef]

- Alcotte, R.; Martin, M.; Moeyaert, J.; Cipro, R.; David, S.; Bassani, F.; Ducroquet, F.; Bogumilowicz, Y.; Sanchez, E.; Ye, Z.; et al. Epitaxial growth of antiphase boundary free GaAs layer on 300 mm Si(001) substrate by metalorganic chemical vapour deposition with high mobility. APL Mater. 2016, 4, 046101. [Google Scholar] [CrossRef] [Green Version]

- Volz, K.; Beyer, A.; Witte, W.; Ohlmann, J.; Németh, I.; Kunert, B.; Stolz, W. GaP-nucleation on exact Si (001) substrates for III/V device integration. J. Cryst. Growth 2011, 315, 37–47. [Google Scholar] [CrossRef]

- Kwoen, J.; Lee, J.; Watanabe, K.; Arakawa, Y. Elimination of anti-phase boundaries in a GaAs layer directly-grown on an on-axis Si(001) substrate by optimizing an AlGaAs nucleation layer. Jpn. J. Appl. Phys. 2019, 58, SBBE07. [Google Scholar] [CrossRef]

- Li, K.; Yang, J.; Lu, Y.; Tang, M.; Jurczak, P.; Liu, Z.; Yu, X.; Park, J.S.; Deng, H.; Jia, H.; et al. Inversion Boundary Annihilation in GaAs Monolithically Grown on On-Axis Silicon (001). Adv. Opt. Mater. 2020, 2000970, 1–8. [Google Scholar] [CrossRef]

- Kwoen, J.; Jang, B.; Watanabe, K.; Arakawa, Y. High-temperature continuous-wave operation of directly grown InAs/GaAs quantum dot lasers on on-axis Si (001). Opt. Express 2019, 27, 2681. [Google Scholar] [CrossRef] [PubMed]

- Sakamoto, T.; Hashiguchi, G. Si(001)-2×1 Single-Domain Structure Obtained by High Temperature Annealing. Jpn. J. Appl. Phys. 1986, 25, L78–L80. [Google Scholar] [CrossRef]

- Liu, Z.; Hantschmann, C.; Tang, M.; Lu, Y.; Park, J.-S.; Liao, M.; Pan, S.; Sanchez, A.; Beanland, R.; Martin, M.; et al. Origin of Defect Tolerance in InAs/GaAs Quantum Dot Lasers Grown on Silicon. J. Light. Technol. 2020, 38, 240–248. [Google Scholar] [CrossRef]

- Shang, C.; Gossard, A.C.; Bowers, J.E.; Wan, Y.; Norman, J.C.; Collins, N.; MacFarlane, I.; Dumont, M.; Liu, S.; Li, Q.; et al. Low-Threshold Epitaxially Grown 1.3- μ m InAs Quantum Dot Lasers on Patterned (001) Si. IEEE J. Sel. Top. Quantum Electron. 2019, 25, 1–7. [Google Scholar] [CrossRef]

- Mori, H.; Tachikawa, M.; Sugo, M.; Itoh, Y. GaAs heteroepitaxy on an epitaxial Si surface with a low-temperature process. Appl. Phys. Lett. 1993, 63, 1963–1965. [Google Scholar] [CrossRef]

- Hashimoto, A.; Sugiyama, N.; Tamura, M. Reduction of Dislocation Density in GaAs on Si Substrate by Si Interlayer and Initial Si Buffer Layer. Jpn. J. Appl. Phys. 1991, 30, L447–L450. [Google Scholar] [CrossRef]

- Bringans, R.D.; Olmstead, M.A.; Ponce, F.A.; Biegelsen, D.K.; Krusor, B.S.; Yingling, R.D. The effect of a Ga prelayer on the beginning of GaAs epitaxy on Si. J. Appl. Phys. 1988, 64, 3472–3475. [Google Scholar] [CrossRef]

- Won, T.; Munns, G.; Houdré, R.; Morkoç, H. Interface charge polarity of a polar on nonpolar semiconductor GaAs/Si with Ga and As prelayers. Appl. Phys. Lett. 1986, 49, 1257–1259. [Google Scholar] [CrossRef]

- Horikoshi, Y.; Kawashima, M.; Yamaguchi, H. Migration-Enhanced Epitaxy of GaAs and AlGaAs. Jpn. J. Appl. Phys. 1988, 27, 169–179. [Google Scholar] [CrossRef]

- Horikoshi, Y.; Yamaguchi, H.; Briones, F.; Kawashima, M. Growth process of III–V compound semiconductors by migration-enhanced epitaxy. J. Cryst. Growth 1990, 105, 326–338. [Google Scholar] [CrossRef]

- Uen, W.Y.; Li, Z.Y.; Huang, Y.C.; Chen, M.C.; Yang, T.N.; Lan, S.M.; Wu, C.H.; Hong, H.F.; Chi, G.C. Heteroepitaxial growth of GaAs on Si by MOVPE using a-GaAs/a-Si double-buffer layers. J. Cryst. Growth 2006, 295, 103–107. [Google Scholar] [CrossRef]

- Hao, M.; Shao, C.; Soga, T.; Jimbo, T.; Umeno, M.; Liang, J.; Zheng, L.; Xiao, Z.; Xiao, J. Characterization and Improvement of GaAs Layers Grown on Si Using an Ultrathin a-Si Film as a Buffer Layer. Jpn. J. Appl. Phys. 1996, 35, L960–L963. [Google Scholar] [CrossRef]

- Hu, H.; Wang, J.; He, Y.; Liu, K.; Liu, Y.; Wang, Q.; Duan, X.; Huang, Y.; Ren, X. Modified dislocation filter method: Toward growth of GaAs on Si by metal organic chemical vapor deposition. Appl. Phys. A Mater. Sci. Process. 2016, 122, 1–7. [Google Scholar] [CrossRef]

- Wang, J.; Ren, X.; Deng, C.; Hu, H.; He, Y.; Cheng, Z.; Ma, H.; Wang, Q.; Huang, Y.; Duan, X.; et al. Extremely Low-Threshold Current Density InGaAs/AlGaAs Quantum-Well Lasers on Silicon. J. Light. Technol. 2015, 33, 3163–3169. [Google Scholar] [CrossRef]

- Yang, J.; Liu, Z.; Jurczak, P.; Tang, M.; Li, K.; Pan, S.; Sanchez, A.; Beanland, R.; Zhang, J.; Wang, H.; et al. All-MBE grown InAs/GaAs quantum dot lasers with thin Ge buffer layer on Si substrates. J. Phys. D. Appl. Phys. 2020, 54, 035103. [Google Scholar] [CrossRef]

- Nozaki, S.; Noto, N.; Egawa, T.; Wu, A.T.; Soga, T.; Jimbo, T.; Umeno, M. Effects of Growth Temperature and V/III Ratio on MOCVD-Grown GaAs-on-Si. Jpn. J. Appl. Phys. 1990, 29, 138–144. [Google Scholar] [CrossRef]

- Wang, Y.; Wang, Q.; Jia, Z.; Li, X.; Deng, C.; Ren, X.; Cai, S.; Huang, Y. Three-step growth of metamorphic GaAs on Si(001) by low-pressure metal organic chemical vapor deposition. J. Vac. Sci. Technol. B 2013, 31, 051211. [Google Scholar] [CrossRef]

- Yamamoto, A.; Uchida, N.; Yamaguchi, M. Optimization of InP / Si heteroepitaxial growth conditions using organometallic vapor phase epitaxy. J. Cryst. Growth 1989, 96, 369–377. [Google Scholar] [CrossRef]

- Wuu, D.S.; Horng, R.H.; Lee, M.K. Indium phosphide on silicon heteroepitaxy: Lattice deformation and strain relaxation. J. Appl. Phys. 1990, 68, 3338–3342. [Google Scholar] [CrossRef]

- Tran, C.A.; Masut, R.A.; Cova, P.; Brebner, J.L.; Leonelli, R. Growth and characterization of InP on silicon by MOCVD. J. Cryst. Growth 1992, 121, 365–372. [Google Scholar] [CrossRef]

- Shi, B.; Klamkin, J. Defect engineering for high quality InP epitaxially grown on on-axis (001) Si. J. Appl. Phys. 2020, 127, 033102. [Google Scholar] [CrossRef]

- Kim, D.K.; Lee, B.-T.; Woo, Y.D.; Kang, T.W.; Paek, M.C. Effects of in-situ thermal annealing on defects associated with GaAs/Ge interface in GaAs/Ge/Si heterostructure. Mater. Lett. 1993, 16, 26–28. [Google Scholar] [CrossRef]

- Buzynin, Y.; Shengurov, V.; Zvonkov, B.; Buzynin, A.; Denisov, S.; Baidus, N.; Drozdov, M.; Pavlov, D.; Yunin, P. GaAs/Ge/Si epitaxial substrates: Development and characteristics. AIP Adv. 2017, 7, 015304. [Google Scholar] [CrossRef] [Green Version]

- Sheldon, P.; Yacobi, B.G.; Jones, K.M.; Dunlavy, D.J. Growth and characterization of GaAs/Ge epilayers grown on Si substrates by molecular beam epitaxy. J. Appl. Phys. 1985, 58, 4186–4193. [Google Scholar] [CrossRef]

- Sheldon, P.; Jones, K.M.; Hayes, R.E.; Tsaur, B.Y.; Fan, J.C.C. Growth and patterning of GaAs/Ge single crystal layers on Si substrates by molecular beam epitaxy. Appl. Phys. Lett. 1984, 45, 274–276. [Google Scholar] [CrossRef]

- Lee, A.D.; Jiang, Q.; Tang, M.; Zhang, Y.; Seeds, A.J.; Liu, H. InAs/GaAs Quantum-Dot Lasers Monolithically Grown on Si, Ge, and Ge-on-Si Substrates. IEEE J. Sel. Top. Quantum Electron. 2013, 19, 1901107. [Google Scholar] [CrossRef]

- Tsuji, T.; Yonezu, H.; Ohshima, N. Selective epitaxial growth of GaAs on Si with strained short-period superlattices by molecular beam epitaxy under atomic hydrogen irradiation. J. Vac. Sci. Technol. B Microelectron. Nanom. Struct. 2004, 22, 1428. [Google Scholar] [CrossRef]

- Takagi, Y.; Yonezu, H.; Kawai, T.; Hayashida, K.; Samonji, K.; Ohshima, N.; Pak, K. Suppression of threading dislocation generation in GaAs-on-Si with strained short-period superlattices. J. Cryst. Growth 1995, 150, 677–680. [Google Scholar] [CrossRef]

- Komatsu, Y.; Hosotani, K.; Fuyuki, T.; Matsunami, H. Heteroepitaxial growth of InGaP on Si with InGaP/GaP step-graded buffer layers. Japanese J. Appl. Phys. 1997, 36, 5425–5430. [Google Scholar] [CrossRef]

- Groenert, M.E.; Leitz, C.W.; Pitera, A.J.; Yang, V.; Lee, H.; Ram, R.J.; Fitzgerald, E.A. Monolithic integration of room-temperature cw GaAs/AlGaAs lasers on Si substrates via relaxed graded GeSi buffer layers. J. Appl. Phys. 2003, 93, 362–367. [Google Scholar] [CrossRef]

- Fitzgerald, E.A.; Xie, Y.-H.; Green, M.L.; Brasen, D.; Kortan, A.R.; Michel, J.; Mii, Y.-J.; Weir, B.E. Totally relaxed Ge x Si 1− x layers with low threading dislocation densities grown on Si substrates. Appl. Phys. Lett. 1991, 59, 811–813. [Google Scholar] [CrossRef]

- Groenert, M.E.; Pitera, A.J.; Ram, R.J.; Fitzgerald, E.A. Improved room-temperature continuous wave GaAs/AlGaAs and InGaAs/GaAs/AlGaAs lasers fabricated on Si substrates via relaxed graded Ge[sub x]Si[sub 1−x] buffer layers. J. Vac. Sci. Technol. B Microelectron. Nanom. Struct. 2003, 21, 1064. [Google Scholar] [CrossRef]

- Sieg, R.M. Toward device-quality GaAs growth by molecular beam epitaxy on offcut Ge/Si[sub 1−x]Ge[sub x]/Si substrates. J. Vac. Sci. Technol. B Microelectron. Nanom. Struct. 1998, 16, 1471. [Google Scholar] [CrossRef]

- Carlin, J.A.; Ringel, S.A.; Fitzgerald, E.A.; Bulsara, M.; Keyes, B.M. Impact of GaAs buffer thickness on electronic quality of GaAs grown on graded Ge/GeSi/Si substrates. Appl. Phys. Lett. 2000, 76, 1884–1886. [Google Scholar] [CrossRef]

- Ting, S.; Bulsara, M.T.; Yang, V.; Groenert, M.; Samavedam, S.; Currie, M.; Langdo, T.; Fitzgerald, E.A.; Joshi, A.M.; Brown, R.; et al. Monolithic integration of III-V materials and devices on silicon. In Proceedings of the SPIE-Silicon-Based Optoelectronics, San Jose, CA, USA, 19 March 1999. [Google Scholar]

- Currie, M.T.; Samavedam, S.B.; Langdo, T.A.; Leitz, C.W.; Fitzgerald, E.A. Controlling threading dislocation densities in Ge on Si using graded SiGe layers and chemical-mechanical polishing. Appl. Phys. Lett. 1998, 72, 1718–1720. [Google Scholar] [CrossRef]

- Richter, M.; Rossel, C.; Webb, D.J.; Topuria, T.; Gerl, C.; Sousa, M.; Marchiori, C.; Caimi, D.; Siegwart, H.; Rice, P.M.; et al. GaAs on 200 mm Si wafers via thin temperature graded Ge buffers by molecular beam epitaxy. J. Cryst. Growth 2011, 323, 387–392. [Google Scholar] [CrossRef]

- Sugo, M.; Takanashi, Y.; Al-Jassim, M.M.; Yamaguchi, M. Heteroepitaxial growth and characterization of InP on Si substrates. J. Appl. Phys. 1990, 68, 540–547. [Google Scholar] [CrossRef]

- Seki, A.; Konushi, F.; Kudo, J.; Kakimoto, S.; Fukushima, T.; Koba, M. MOCVD growth of InP on 4-inch Si substrate with GaAs intermediate layer. Jpn. J. Appl. Phys. 1987, 26, L1587–L1589. [Google Scholar] [CrossRef]

- Horikawa, H.; Kawai, Y.; Akiyama, M.; Sakuta, M. Hetero-epitaxial growth of InP on Si substrates by LP-MOVPE. J. Cryst. Growth 1988, 93, 523–526. [Google Scholar] [CrossRef]

- Kohama, Y.; Kadota, Y.; Ohmachi, Y. Heteroepitaxy of InP on Si Substrates by MOCVD. J. Electrochem. Soc. 1989, 136, 3853–3856. [Google Scholar] [CrossRef]

- Mori, H.; Sugo, M.; Itoh, Y. Heteroepitaxy of InP on Si substrates. Adv. Mater. 1993, 5, 208–209. [Google Scholar] [CrossRef]

- Zhu, S.; Shi, B.; Lau, K.M. Electrically pumped 1.5 μm InP-based quantum dot microring lasers directly grown on (001) Si. Opt. Lett. 2019, 44, 4566. [Google Scholar] [CrossRef]

- Sugo, M.; Yamaguchi, M. Buffer layer effects on residual stress in InP on Si substrates. Appl. Phys. Lett. 1989, 54, 1754–1756. [Google Scholar] [CrossRef]

- Sugo, M.; Yamaguchi, M.; Al-Jassim, M.M. Heteroepitaxial growth of InP on Si substrates. J. Cryst. Growth 1990, 99, 365–370. [Google Scholar] [CrossRef]

- Kohama, Y.; Kadota, Y.; Ohmachi, Y. Inp grown on si substrates with gap buffer layers by metalorganic chemical vapor deposition. Jpn. J. Appl. Phys. 1989, 28, 1337–1340. [Google Scholar] [CrossRef]

- Quitoriano, N.J.; Fitzgerald, E.A. Relaxed, high-quality InP on GaAs by using InGaAs and InGaP graded buffers to avoid phase separation. J. Appl. Phys. 2007, 102, 033511. [Google Scholar] [CrossRef]

- Sun, Y.; Dong, J.; Yu, S.; Zhao, Y.; He, Y. High quality InP epilayers grown on GaAs substrates using metamorphic AlGaInAs buffers by metalorganic chemical vapor deposition. J. Mater. Sci. Mater. Electron. 2017, 28, 745–749. [Google Scholar] [CrossRef]

- Go, R.; Krysiak, H.; Fetters, M.; Figueiredo, P.; Suttinger, M.; Leshin, J.; Fang, X.M.; Fastenau, J.M.; Lubyshev, D.; Liu, A.W.K.; et al. InP-based quantum cascade lasers monolithically integrated onto Si and GaAs Substrates. Opt. Express 2018, 26, 22389–22393. [Google Scholar]

- Kohen, D.; Nguyen, X.S.; Made, R.I.; Heidelberger, C.; Lee, K.H.; Lee, K.E.K.; Fitzgerald, E.A. Preventing phase separation in MOCVD-grown InAlAs compositionally graded buffer on silicon substrate using InGaAs interlayers. J. Cryst. Growth 2017, 478, 64–70. [Google Scholar] [CrossRef]

- Chang, Y.S.; Naritsuka, S.; Nishinaga, T. Optimization of growth condition for wide dislocation-free GaAs on Si substrate by microchannel epitaxy. J. Cryst. Growth 1998, 192, 18–22. [Google Scholar] [CrossRef]

- Ujiie, Y.; Nishinaga, T. Epitaxial Lateral Overgrowth of GaAs on a Si Substrate. Jpn. J. Appl. Phys. 1989, 28, L337–L339. [Google Scholar] [CrossRef]

- Sakawa, S.; Nishinaga, T. Effect of Si Doping on Epitaxial Lateral Overgrowth of GaAs on GaAs-Coated Si Substrate. Jpn. J. Appl. Phys. 1992, 31, L359–L361. [Google Scholar] [CrossRef]

- Tsaur, B.; McClelland, R.W.; Fan, J.C.C.; Gale, R.P.; Salerno, J.P.; Vojak, B.A.; Bozler, C.O. Low-dislocation-density GaAs epilayers grown on Ge-coated Si substrates by means of lateral epitaxial overgrowth. Appl. Phys. Lett. 1982, 41, 347–349. [Google Scholar] [CrossRef]

- Huang, W.; Nishinaga, T.; Naritsuka, S. Microchannel Epitaxy of GaAs from Parallel and Nonparallel Seeds. Jpn. J. Appl. Phys. 2001, 40, 5373–5376. [Google Scholar] [CrossRef]

- Hsu, C.-W.; Chen, Y.-F.; Su, Y.-K. Nano epitaxial growth of GaAs on Si (001). Appl. Phys. Lett. 2011, 99, 133115. [Google Scholar] [CrossRef]

- Nishinaga, T. Microchannel epitaxy: An overview. J. Cryst. Growth 2002, 237–239, 1410–1417. [Google Scholar] [CrossRef]

- Chang, Y.S.; Naritsuka, S.; Nishinaga, T. Effect of dislocation density on microchannel epitaxy of GaAs on GaAs/Si substrate. J. Cryst. Growth 2010, 312, 629–634. [Google Scholar] [CrossRef]

- Zytkiewicz, Z.R. Epitaxial Lateral Overgrowth of GaAs: Principle and Growth Mechanism. Cryst. Res. Technol. 1999, 34, 573–582. [Google Scholar] [CrossRef]

- He, Y.; Wang, J.; Hu, H.; Wang, Q.; Huang, Y.; Ren, X. Coalescence of GaAs on (001) Si nano-trenches based on three-stage epitaxial lateral overgrowth. Appl. Phys. Lett. 2015, 106, 202105. [Google Scholar] [CrossRef]

- Chang, Y.S.; Naritsuka, S.; Nishinaga, T. Effect of growth temperature on epitaxial lateral overgrowth of GaAs on Si substrate. J. Cryst. Growth 1997, 174, 630–634. [Google Scholar] [CrossRef]

- Sugai, M.; Kochiya, T.; Oyama, Y.; Nishizawa, J.-I. Selective epitaxy of InP on Si(100) substrates prepared by liquid-phase epitaxy. J. Phys. Chem. Solids 2008, 69, 411–414. [Google Scholar] [CrossRef]

- Naritsuka, S.; Nishinaga, T. Spatially resolved photoluminescence of laterally overgrown InP on InP-coated Si substrates. J. Cryst. Growth 1997, 174, 622–629. [Google Scholar] [CrossRef]

- Naritsuka, S.; Nishinaga, T. Epitaxial lateral overgrowth of InP by liquid phase epitaxy. J. Cryst. Growth 1995, 146, 314–318. [Google Scholar] [CrossRef]

- Kochiya, T.; Oyama, Y.; Kimura, T.; Suto, K.; Nishizawa, J. Dislocation-free large area InP ELO layers by liquid phase epitaxy. J. Cryst. Growth 2005, 281, 263–274. [Google Scholar] [CrossRef]

- Yan, Z.; Hamaoka, Y.; Naritsuka, S.; Nishinaga, T. Coalescence in microchannel epitaxy of InP. J. Cryst. Growth 2000, 212, 1–10. [Google Scholar] [CrossRef]

- Olsson, F.; Xie, M.; Lourdudoss, S.; Prieto, I.; Postigo, P.A. Epitaxial lateral overgrowth of InP on Si from nano-openings: Theoretical and experimental indication for defect filtering throughout the grown layer. J. Appl. Phys. 2008, 104, 093112. [Google Scholar] [CrossRef] [Green Version]

- Naritsuka, S.; Nishinaga, T.; Tachikawa, M.; Mori, H. InP Layer Grown on (001) Silicon Substrate by Epitaxial Lateral Overgrowth. Jpn. J. Appl. Phys. 1995, 34, L1432–L1435. [Google Scholar] [CrossRef]

- Sun, Y.; Rodríguez Messmer, E.; Söderström, D.; Jahan, D.; Lourdudoss, S. Temporally resolved selective area growth of InP in the openings off-oriented from [110] direction. J. Cryst. Growth 2001, 225, 9–15. [Google Scholar] [CrossRef]

- Sun, Y.-T.; Lourdudoss, S. Effect of growth conditions on epitaxial lateral overgrowth of InP on InP/Si (001) substrate by hydride vapor phase epitaxy. In Proceedings of the SPIE-Photonics Packaging and Integration III, San Jose, CA, USA, 30 May 2003. [Google Scholar]

- Metaferia, W.; Junesand, C.; Gau, M.-H.; Lo, I.; Pozina, G.; Hultman, L.; Lourdudoss, S. Morphological evolution during epitaxial lateral overgrowth of indium phosphide on silicon. J. Cryst. Growth 2011, 332, 27–33. [Google Scholar] [CrossRef]

- Hayafuji, N.; Miyashita, M.; Nishimura, T.; Kadoiwa, K.; Kumabe, H.; Murotani, T. Effect of Employing Positions of Thermal Cyclic Annealing and Strained-Layer Superlattice on Defect Reduction in GaAs-on-Si. Jpn. J. Appl. Phys. 1990, 29, 2371–2375. [Google Scholar] [CrossRef]

- Yamaguchi, M.; Tachikawa, M.; Itoh, Y.; Sugo, M.; Kondo, S. Thermal annealing effects of defect reduction in GaAs on Si substrates. J. Appl. Phys. 1990, 68, 4518–4522. [Google Scholar] [CrossRef]

- Yamaguchi, M.; Yamamoto, A.; Tachikawa, M.; Itoh, Y.; Sugo, M. Defect reduction effects in GaAs on Si substrates by thermal annealing. Appl. Phys. Lett. 1988, 53, 2293–2295. [Google Scholar] [CrossRef]

- Jung, D.; Callahan, P.G.; Shin, B.; Mukherjee, K.; Gossard, A.C.; Bowers, J.E. Low threading dislocation density GaAs growth on on-axis GaP/Si (001). J. Appl. Phys. 2017, 122, 225703. [Google Scholar] [CrossRef] [Green Version]

- Sasaki, T.; Arafune, K.; Lee, H.S.; Ekins-Daukes, N.J.; Tanaka, S.; Ohshita, Y.; Yamaguchi, M. Effects of thermal cycle annealing on reduction of defect density in lattice-mismatched InGaAs solar cells. Phys. B Condens. Matter 2006, 376–377, 626–629. [Google Scholar] [CrossRef]

- Yamaguchi, M. Dislocation density reduction in heteroepitaxial III-V compound films on Si substrates for optical devices. J. Mater. Res. 1991, 6, 376–384. [Google Scholar] [CrossRef]

- Shang, C.; Selvidge, J.; Hughes, E.; Norman, J.C.; Taylor, A.A.; Gossard, A.C.; Mukherjee, K.; Bowers, J.E. A Pathway to Thin GaAs Virtual Substrate on On-Axis Si (001) with Ultralow Threading Dislocation Density. Phys. status solidi 2020, 2000402, 2000402. [Google Scholar] [CrossRef]

- Ayers, J.E.; Schowalter, L.J.; Ghandhi, S.K. Post-growth thermal annealing of GaAs on Si(001) grown by organometallic vapor phase epitaxy. J. Cryst. Growth 1992, 125, 329–335. [Google Scholar] [CrossRef]

- Xu, H.Y.; Guo, Y.N.; Wang, Y.; Zou, J.; Kang, J.H.; Gao, Q.; Tan, H.H.; Jagadish, C. Effects of annealing and substrate orientation on epitaxial growth of GaAs on Si. J. Appl. Phys. 2009, 106, 083514. [Google Scholar] [CrossRef] [Green Version]

- Li, W.; Chen, S.; Tang, M.; Wu, J.; Hogg, R.; Seeds, A.; Liu, H.; Ross, I. Effect of rapid thermal annealing on threading dislocation density in III-V epilayers monolithically grown on silicon. J. Appl. Phys. 2018, 123, 215303. [Google Scholar] [CrossRef]

- Mori, H.; Sugo, M.; Tachikawa, M.; Itch, Y.; Yamaguchi, M. Heteroepitaxy of Inp on Si for Optical Devices. MRS Proc. 1990, 198, 119. [Google Scholar] [CrossRef]

- Ababou, Y.; Desjardins, P.; Chennouf, A.; Leonelli, R.; Hetherington, D.; Yelon, A.; L’Espérance, G.; Masut, R.A. Structural and optical characterization of InP grown on Si(111) by metalorganic vapor phase epitaxy using thermal cycle growth. J. Appl. Phys. 1996, 80, 4997–5005. [Google Scholar] [CrossRef]

- Matthews, J.W.; Blakeslee, A.E.; Mader, S. Use of misfit strain to remove dislocations from epitaxial thin films. Thin Solid Films 1976, 33, 253–266. [Google Scholar] [CrossRef]

- Tischler, M.A.; Katsuyama, T.; El-Masry, N.A.; Bedair, S.M. Defect reduction in GaAs epitaxial layers using a GaAsP-InGaAs strained-layer superlattice. Appl. Phys. Lett. 1985, 46, 294–296. [Google Scholar] [CrossRef]

- Bedair, S.M.; Humphreys, T.P.; El-Masry, N.A.; Lo, Y.; Hamaguchi, N.; Lamp, C.D.; Tuttle, A.A.; Dreifus, D.L.; Russell, P. Defect reduction in GaAs grown by molecular beam epitaxy using different superlattice structures. Appl. Phys. Lett. 1986, 49, 942–944. [Google Scholar] [CrossRef]

- Osboum, G.C.; Gourley, P.L.; Fritz, I.J.; Biefeld, R.M.; Dawson, L.R.; Zipperian, T.E. Principles and Applications of Semiconductor Strained-Layer Superlattices. Semicond. Semimetals 1987, 24, 459–503. [Google Scholar] [CrossRef]

- El-Masry, N.; Hamaguchi, N.; Tarn, J.C.L.; Karam, N.; Humphreys, T.P.; Moore, D.; Bedair, S.M.; Lee, J.W.; Salerno, J. Defect Reduction in GaAs Epilayers on Si Substrates Using Strained Layer Superlattices. MRS Proc. 1987, 91, 99. [Google Scholar] [CrossRef]

- Hamaguchi, N.; Humphreys, T.P.; Moore, D.J.; Parker, C.A.; Bedair, S.M.; Tarn, J.C.L.; Jiang, B.L.; El-Masry, N.; Radzimski, Z.J.; Rozgonyi, G.A. Dislocation interactions in strained-layer structures grown on GaAs and Si substrates. J. Cryst. Growth 1988, 93, 449–458. [Google Scholar] [CrossRef]

- Fritz, I.J.; Gourley, P.L.; Dawson, L.R.; Schirber, J.E. Electrical and optical studies of dislocation filtering in InGaAs/GaAs strained-layer superlattices. Appl. Phys. Lett. 1988, 53, 1098–1100. [Google Scholar] [CrossRef]

- Yamaguchi, M.; Nishioka, T.; Sugo, M. Analysis of strained-layer superlattice effects on dislocation density reduction in GaAs on Si substrates. Appl. Phys. Lett. 1989, 54, 24–26. [Google Scholar] [CrossRef]

- Yamaguchi, M.; Sugo, M.; Itoh, Y. Misfit stress dependence of dislocation density reduction in GaAs films on Si substrates grown by strained-layer superlattices. Appl. Phys. Lett. 1989, 54, 2568–2570. [Google Scholar] [CrossRef]

- Sharan, S.; Narayan, J.; Fan, J.C.C. Dislocation density reduction in GaAs epilayers on Si using strained layer superlattices. J. Electron. Mater. 1991, 20, 779–784. [Google Scholar] [CrossRef]

- Tang, M.; Chen, S.; Wu, J.; Jiang, Q.; Dorogan, V.G.; Benamara, M.; Mazur, Y.I.; Salamo, G.J.; Seeds, A.; Liu, H. 1.3-μm InAs/GaAs quantum-dot lasers monolithically grown on Si substrates using InAlAs/GaAs dislocation filter layers. Opt. Express 2014, 22, 11528. [Google Scholar] [CrossRef]

- Tang, M.; Wu, J.; Chen, S.; Jiang, Q.; Seeds, A.J.; Liu, H.; Dorogan, V.G.; Benamara, M.; Mazur, Y.; Salamo, G. Optimisation of the dislocation filter layers in 1.3-μm InAs/GaAs quantum-dot lasers monolithically grown on Si substrates. IET Optoelectron. 2015, 9, 61–64. [Google Scholar] [CrossRef]

- Tang, M.; Chen, S.; Wu, J.; Jiang, Q.; Kennedy, K.; Jurczak, P.; Liao, M.; Beanland, R.; Seeds, A.; Liu, H. Optimizations of Defect Filter Layers for 1.3-μm InAs/GaAs Quantum-Dot Lasers Monolithically Grown on Si Substrates. IEEE J. Sel. Top. Quantum Electron. 2016, 22, 50–56. [Google Scholar] [CrossRef] [Green Version]

- Zhu, S.; Shi, B.; Li, Q.; Lau, K.M. 1.5 μ m quantum-dot diode lasers directly grown on CMOS-standard (001) silicon. Appl. Phys. Lett. 2018, 113, 221103. [Google Scholar] [CrossRef]

- Dotor, M.L.; González, L.; Briones, F.; Gómez, D.; Golmayo, D.; González, Y. Low temperature InP/Si technology: From Si substrate preparation to epitaxial growth. Electron. Lett. 1994, 30, 269–271. [Google Scholar] [CrossRef]

- Megalini, L.; Brunelli, S.T.Š.; Charles, W.O.; Taylor, A.; Isaac, B.; Bowers, J.E.; Klamkin, J. Strain-compensated InGaAsP superlattices for defect reduction of InP grown on exact-oriented (001) patterned Si substrates by metal organic chemical vapor deposition. Materials (Basel) 2018, 9, 337. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Crumbaker, T.E.; Lee, H.Y.; Hafich, M.J.; Robinson, G.Y. Growth of InP on Si substrates by molecular beam epitaxy. Appl. Phys. Lett. 1989, 54, 140–142. [Google Scholar] [CrossRef]

- Samonji, K.; Yonezu, H.; Takagi, Y.; Iwaki, K.; Ohshima, N.; Shin, J.K.; Pak, K. Reduction of threading dislocation density in InP-on-Si heteroepitaxy with strained short-period superlattices. Appl. Phys. Lett. 1996, 69, 100–102. [Google Scholar] [CrossRef]

- Itakura, H.; Suzuki, T.; Jiang, Z.K.; Soga, T.; Jimbo, T.; Umeno, M. Effect of InGaAs/InP strained layer superlattice in InP-on-Si. J. Cryst. Growth 1991, 115, 154–157. [Google Scholar] [CrossRef]

- Yang, J.; Bhattacharya, P.; Mi, Z. High-performance In0.5Ga0.5As/GaAs quantum-dot lasers on silicon with multiple-layer quantum-dot dislocation filters. IEEE Trans. Electron Devices 2007, 54, 2849–2855. [Google Scholar] [CrossRef]

- Shi, B.; Li, Q.; Lau, K.M. Self-organized InAs/InAlGaAs quantum dots as dislocation filters for InP films on (001) Si. J. Cryst. Growth 2017, 464, 28–32. [Google Scholar] [CrossRef]

- Shi, B.; Li, Q.; Lau, K.M. Epitaxial growth of high quality InP on Si substrates: The role of InAs/InP quantum dots as effective dislocation filters. J. Appl. Phys. 2018, 123, 193104. [Google Scholar] [CrossRef] [Green Version]

- Saravanan, S.; Hayashi, Y.; Soga, T.; Jimbo, T.; Umeno, M.; Sato, N.; Yonehara, T. Growth and characterization of GaAs epitaxial layers on Si/porous Si/Si substrate by chemical beam epitaxy. J. Appl. Phys. 2001, 89, 5215–5218. [Google Scholar] [CrossRef]

- Nishimura, T.; Kadoiwa, K.; Miyashita, M.; Kumabe, H.; Murotani, T. Crack-free and low dislocation density GaAs-on-Si grown by 2-reactor MOCVD system. J. Cryst. Growth 1991, 112, 791–796. [Google Scholar] [CrossRef]

- Takano, Y.; Kururi, T.; Kuwahara, K.; Fuke, S. Residual strain and threading dislocation density in InGaAs layers grown on Si substrates by metalorganic vapor-phase epitaxy. Appl. Phys. Lett. 2001, 78, 93–95. [Google Scholar] [CrossRef]

- Saravanan, S.; Adachi, M.; Satoh, N.; Soga, T.; Jimbo, T.; Umeno, M. Stress reduction and structural quality improvement due to In doping in GaAs/Si. Mater. Sci. Eng. B Solid-State Mater. Adv. Technol. 2000, 68, 166–170. [Google Scholar] [CrossRef]

- Van Der Ziel, J.P.; Chand, N.; Weiner, J.S. Elimination of thermally induced biaxial stress in GaAs on Si layers by post-growth patterning. J. Appl. Phys. 1989, 66, 1195–1198. [Google Scholar] [CrossRef]

- Huang, H.; Ren, X.; Lv, J.; Wang, Q.; Song, H.; Cai, S.; Huang, Y.; Qu, B. Crack-free GaAs epitaxy on Si by using midpatterned growth: Application to Si-based wavelength-selective photodetector. J. Appl. Phys. 2008, 104, 113114. [Google Scholar] [CrossRef]

- Wei, W.-Q.; Wang, J.-H.; Zhang, B.; Zhang, J.-Y.; Wang, H.-L.; Feng, Q.; Xu, H.-X.; Wang, T.; Zhang, J.-J. InAs QDs on (111)-faceted Si (001) hollow substrates with strong emission at 1300 nm and 1550 nm. Appl. Phys. Lett. 2018, 113, 053107. [Google Scholar] [CrossRef]

- Marzegalli, A.; Cortinovis, A.; Basso Basset, F.; Bonera, E.; Pezzoli, F.; Scaccabarozzi, A.; Isa, F.; Isella, G.; Zaumseil, P.; Capellini, G.; et al. Exceptional thermal strain reduction by a tilting pillar architecture: Suspended Ge layers on Si (001). Mater. Des. 2017, 116, 144–151. [Google Scholar] [CrossRef]

- Ballabio, A.; Bietti, S.; Scaccabarozzi, A.; Esposito, L.; Vichi, S.; Fedorov, A.; Vinattieri, A.; Mannucci, C.; Biccari, F.; Nemcsis, A.; et al. GaAs epilayers grown on patterned (001) silicon substrates via suspended Ge layers. Sci. Rep. 2019, 9, 1–8. [Google Scholar] [CrossRef]

- Zhang, J.-Y.; Wei, W.-Q.; Wang, J.-H.; Cong, H.; Feng, Q.; Wang, Z.-H.; Wang, T.; Zhang, J.-J. Epitaxial growth of InAs/GaAs quantum dots on {113}-faceted Ge/Si (001) hollow substrate. Opt. Mater. Express 2020, 10, 1045. [Google Scholar] [CrossRef]

- Falub, C.V.; von Kanel, H.; Isa, F.; Bergamaschini, R.; Marzegalli, A.; Chrastina, D.; Isella, G.; Muller, E.; Niedermann, P.; Miglio, L. Scaling Hetero-Epitaxy from Layers to Three-Dimensional Crystals. Science 2012, 335, 1330–1334. [Google Scholar] [CrossRef] [Green Version]

- Bietti, S.; Scaccabarozzi, A.; Frigeri, C.; Bollani, M.; Bonera, E.; Falub, C.V.; von Känel, H.; Miglio, L.; Sanguinetti, S. Monolithic integration of optical grade GaAs on Si (001) substrates deeply patterned at a micron scale. Appl. Phys. Lett. 2013, 103, 262106. [Google Scholar] [CrossRef]

- Kohen, D.; Bao, S.; Lee, K.H.; Lee, K.E.K.; Tan, C.S.; Yoon, S.F.; Fitzgerald, E.A. The role of AsH3 partial pressure on anti-phase boundary in GaAs-on-Ge grown by MOCVD – Application to a 200mm GaAs virtual substrate. J. Cryst. Growth 2015, 421, 58–65. [Google Scholar] [CrossRef]

- Yang, J.; Jurczak, P.; Cui, F.; Li, K.; Tang, M.; Billiald, L.; Beanland, R.; Sanchez, A.M.; Liu, H. Thin Ge buffer layer on silicon for integration of III-V on silicon. J. Cryst. Growth 2019, 514, 109–113. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, J.-S.; Tang, M.; Chen, S.; Liu, H. Heteroepitaxial Growth of III-V Semiconductors on Silicon. Crystals 2020, 10, 1163. https://doi.org/10.3390/cryst10121163

Park J-S, Tang M, Chen S, Liu H. Heteroepitaxial Growth of III-V Semiconductors on Silicon. Crystals. 2020; 10(12):1163. https://doi.org/10.3390/cryst10121163

Chicago/Turabian StylePark, Jae-Seong, Mingchu Tang, Siming Chen, and Huiyun Liu. 2020. "Heteroepitaxial Growth of III-V Semiconductors on Silicon" Crystals 10, no. 12: 1163. https://doi.org/10.3390/cryst10121163

APA StylePark, J.-S., Tang, M., Chen, S., & Liu, H. (2020). Heteroepitaxial Growth of III-V Semiconductors on Silicon. Crystals, 10(12), 1163. https://doi.org/10.3390/cryst10121163